# Hardware/Software Co-Simulation of SPI enabled ASICs and

# **Software Drivers for Fault Injection and Regression Tests**

Elias Kyrlies-Chrysoulidis, Andreas Plange, Thomas Guertler, Matthias Auerswald Continental AG, Division Powertrain, Nuremberg, Germany

> Josef Schmid iSyst GmbH, Nuremberg, Germany

> > Early

Integration

### **INTRODUCTION & MOTIVATION**

#### KEY market demands

Increasing safety level requested from OEMs

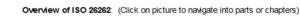

ISO26262 standard up to ASIL-D

•Risk of product recall due to safety weakness

More complex HW/SW automotive systems

**OBJECTIVES**

HW/SW-Cosimulation

• Early verification of HSI interface (e.g. SPI)

Time to market

4-5 months earlier

less ASIC redesign

cycles

#### **Problem Areas**

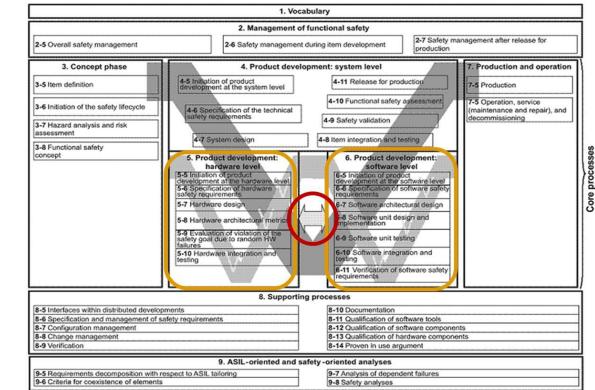

late verification of SW driver interface to ASIC design can lead to ASIC redesign iterations

late verification of safety architecture

fault injection only theoretically

late verification of HSI (e.g. SPI)

only possible with the first ASIC samples

| ault        | Fault<br>modeling | <ul> <li>Verification of functional safety concepts<br/>(system architecture)</li> <li>Regression testing</li> </ul>                      | <ul> <li>Robust design</li> <li>quality improvement</li> </ul> |

|-------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| M<br>L<br>3 | Re-use            | <ul> <li>of HW tool chain and system models (VHDL-AMS/VHDL/C++)</li> <li>of SW tool chain and driver libs (compiler, debugger)</li> </ul> | <ul> <li>No additional invest</li> </ul>                       |

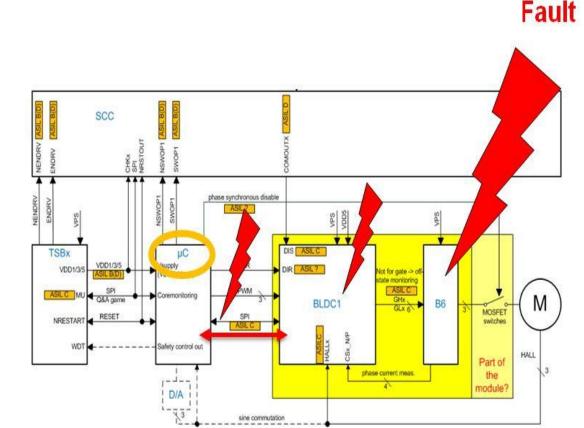

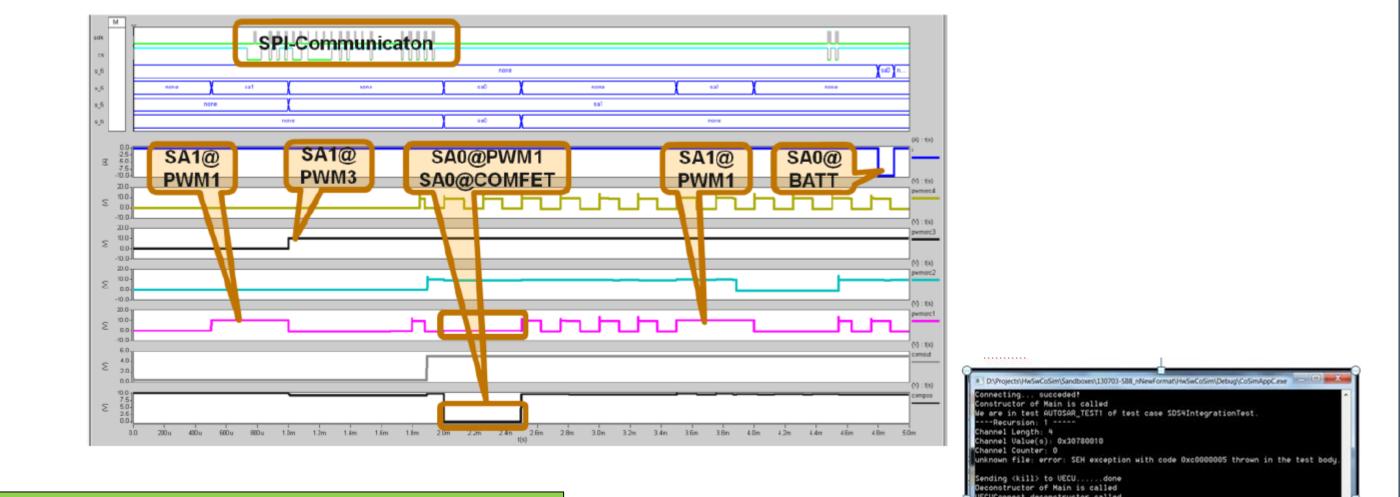

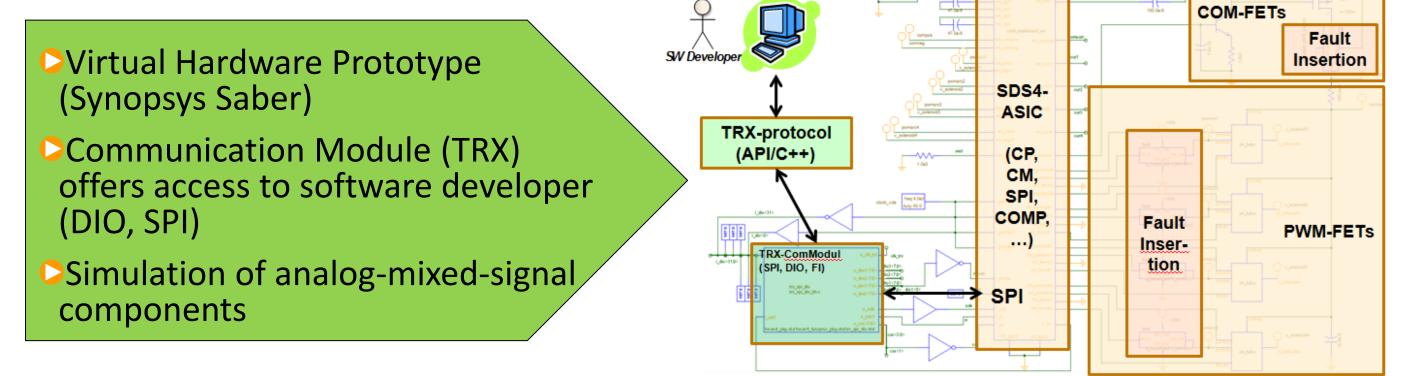

### **RESULTS-1: Virtual HW-Prototype & Software Environment**

## **RESULTS-2: HW/SW Co-Simulation & Fault Injection**

- Automatic tests with Google Test framework

- Software Development in Visual Studio

- Fault Insertion in SW and HW

| r a al ≥ 19 (3 ty nor s a).<br>entité internet les Core :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | VECUConnect deconstructor called<br>[closeUesLib succeded<br>[ FASLED ] SDS4TntegrationTest.AUTOSAR_TEST1 (1676 ms)<br>[] 13 tests from SDS4IntegrationTest (1007354 ms total)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| <pre>/*! vectors Nose /*! Creaters I Nose /*! Creaters I Nose /*! Creatigneration: Nose /*! Configuration: Nose /*! Configuration: Nose /*! Configuration: Nose /*! Configuration if (Configuration: Aux_PR) {     ulat# device_mr;     ulat# figuration     for initialize the configuration     Sole_Mandra.config.pr = (Sole     Sole_Mandra.config.press } </pre> | <pre>Status and status 'Sole of continue<br/>strentar's<br/>continue and status 'Sole excelling='VIF-4'):<br/>continue and status 'Sole of continue<br/>strentar and status 'Sole of continue<br/>continue and 'Sole of Sole of Sole</pre> |  |  |

# **CONCLUSIONS**

## **REFERENCES**

| Validation of<br>ASIC/HW<br>Specification | <ul> <li>Alignment with virtual models (VHDL, VHDL-<br/>AMS)</li> <li>Verification of HW/SW interface (e.g. SPI, DIO)</li> </ul> |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| <b>Regression Test</b>                    | <ul> <li>VHDL-Test benches for ASIC (HW)</li> <li>SW unit testing</li> </ul>                                                     |

| Fault Insertion                           | <ul> <li>Multiple and sequential failures (HW, CRC)</li> <li>SW faults (incomplete messages, wrong timing)</li> </ul>            |

[1] A. Plange, E. Kyrlies-Chrysoulidis, J. Schmid, T. Gürtler, HW/SW-Cosimulation of ASICs and SW Drivers for Fault Analysis and Regression Tests, CSC-2013 (Continental SW Conference), Timisoara, Romania

[2] On/Offline Fault Insertion & Analysis in a Virtual ASIC System Simulation Environment; J.

Schmid, M. Eckl, iSyst GmbH; M. Arabackyj, A. Plange, Continental AG (Division Powertrain); 26.

ITG/GI/GMM-Workshop TuZ-2014, Kloster Banz, Germany

[3] J. Schmid, B. von Edlinger, A. Plange, F. Lehmann, Automotive System Verification using Saber/Modelsim Cosimulation in Conjunction with ISO 26262, SNUG-2012, Munich

[4] ISO 262672, Road vehicles - Functional safety, http://www.iso.org/iso/search.htm?qt=26262&published=on

[5] VHDL-AMS, analog-mixed-signal extention of VHDL, http://en.wikipedia.org/wiki/VHDL-AMS

[6] Saber/SaberRD, Synopsys, www.synopsys.com/Systems/Saber

[7] ModelSim, Mentor Graphics, http://model.com/

| & Analysis               | <ul> <li>Verification of functional safety concepts</li> </ul>                                               | [6 | 5] |

|--------------------------|--------------------------------------------------------------------------------------------------------------|----|----|

| Early HSI<br>Integration | <ul> <li>Virtual prototype of ASIC for SW unit test</li> <li>Early SW driver development possible</li> </ul> | [7 | 7] |

The work was done within a internal innovation project of Continental AG and supported by José A. Avila, Executive Board Member, and responsible for the Automotive Division Powertrain. Special thanks for contribution, comments and review to

Michal Pluska, Marta Giribet, Sida Xu, Michael Eckl, Eric Taistra, and Marc Arabackyj

### © Accellera Systems Initiative