## Hardware Emulation: ICE vs Virtual A Mano-a-Mano Duel for Supremacy

# Lauro Rizzatti Hardware Emulation Consultant

- Hardware Emulation Timeline

- Hardware Emulation Evolution

- The Objectives, The Modes, The Targets

- The Usage

- The Technology

- ICE versus Virtual

- In-Circuit-Emulation (ICE) Mode

- What is it?

- Why Customers use ICE?

- Virtual (or Acceleration) Mode

- What is it?

- Why Customers use Virtual Mode?

- Advantages and Disadvantages

### **Hardware Emulation Timeline**

| FPGA-Based                                                                  | FPGA-Based & Custom                                                                                                                                 | FPGA-Based & Custom                                                |

|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| In-Circuit-Emulation (ICE)                                                  | ICE & HDL Acceleration                                                                                                                              | ICE, All Types of Acceleration                                     |

| <ul><li>Zycad (1981)</li><li>Ikos (1984)</li><li>Quickturn (1987)</li></ul> | <ul> <li>Meta-Systems (Mentor)</li> <li>Cadence (Quickturn)</li> <li>Mentor (Ikos)</li> <li>Akis Systems (Verisity/Cadence)</li> <li>EVE</li> </ul> | <ul><li> Mentor</li><li> Cadence</li><li> Synopsys (EVE)</li></ul> |

| • PiE (1990)                                                                |                                                                                                                                                     |                                                                    |

## DESIGN AND VERIFICATION Hardware Emulation: **Objectives, Modes, Targets**

#### **Early Years**

- One Verification Objective

- HW Functional Verification

- One Deployment Mode

- In-Circuit-Emulation (ICE)

- One Target Industry

- CPU/Graphics (largest designs in 1985-1995)

#### **Today**

- Multiple Verification Objectives

- HW Functional Verification, HW/SW Integration, SW Validation, Power Domain Verification, Power Estimation, Performance Characterization,...

- **Multiple** Deployment Modes

- ICE, Acceleration, Virtualization,...

- Multiple Target Industries

- CPU/Graphics, Mobile, Video, Networking, Storage,...

### **Hardware Emulation: Usage**

#### **Early Years**

- One User

- Local Resource

- No Remote Access

- **Unfriendly** to use

#### **Today**

- Multiple Users (> 100)

- **Central** Resource

- Remote Access

- Easy to use

### **Hardware Emulation: Technology**

#### **Early Years**

- Commercial FPGA based

- Design Capacity: **330K**gates/Box<sup>(1)</sup>

- Setup Time: **Several Months**

- Compilation Time: Days

- Design Debug: Partial Visibility

- Cost: ~ **<u>5\$</u>**/gate<sup>(1,2)</sup>

- Volume: **6,000mm**<sup>3</sup>/gate

- Weight: 2gr/gate

- Power: **50mWatt**/gate

- Reliability: < One Day</li>

#### **Today**

- <u>Custom</u> silicon or <u>Commercial</u>

<u>FPGA</u> based

- Design Capacity: > 250Mgates/Box

- Setup Time: < One Week</li>

- Compilation Time: Hours

- Design Debug: 100% Visibility

- Cost: < 1cents/gate

- Volume: < 5mm³/gate

- Weight: < 2mgr/gate

- Power: < 5uWatt/gate

- Reliability: > One Months

- (1): Quickturn Enterprise System (1992)

- (2): Readjusted for inflation

- (3): In the FPGA-based emulator the compilation time is adversely affected by the FPGA PAR time and the 100% visibility compromises significantly the speed of execution

### **Hardware Emulation: The Future**

#### **Hardware**

- Two basic architectures:

- Commercial FPGA based

- Custom Silicon based

- Capacity: several billion gates

- Smaller

- Faster

- Cheaper

- Highly reliable

#### **Supporting Software**

- Setup Time: ~ one day

- Compilation Time: less than one hour

- Integrated in a continuum of verification engines, sharing GUI and design database

- Access offered via datacenters

- ICE, acceleration, system validation, functional coverage, SVA, low-power verification, power estimation, DFT and test vector verification, performance characterization

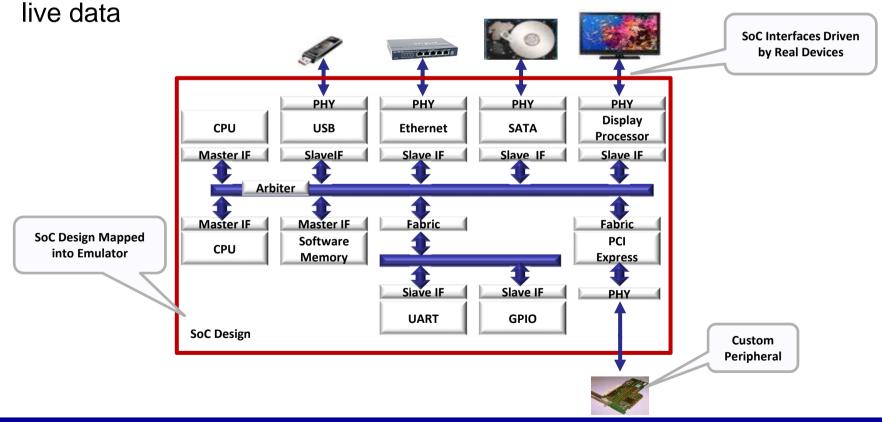

#### ICE Mode: What Is It?

In ICE mode, the emulator is plugged into a socket on the physical target system in place of a yet-to-be-built chip to support exercising and debugging the design-under-test (DUT) mapped inside the emulator with

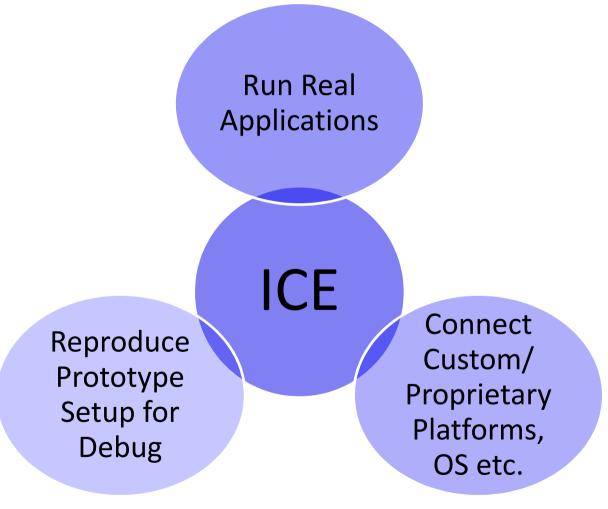

### **Why Customers Use ICE**

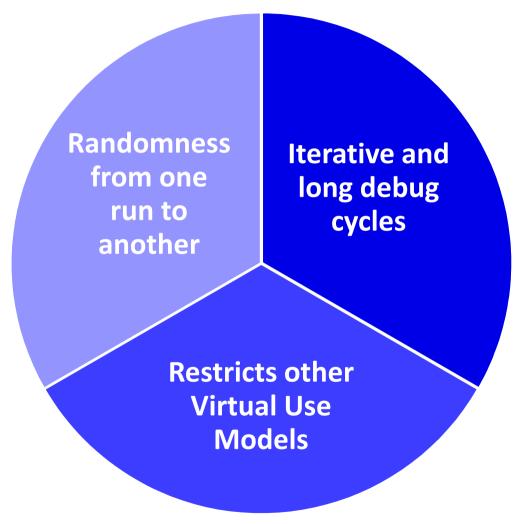

### **Challenges using ICE**

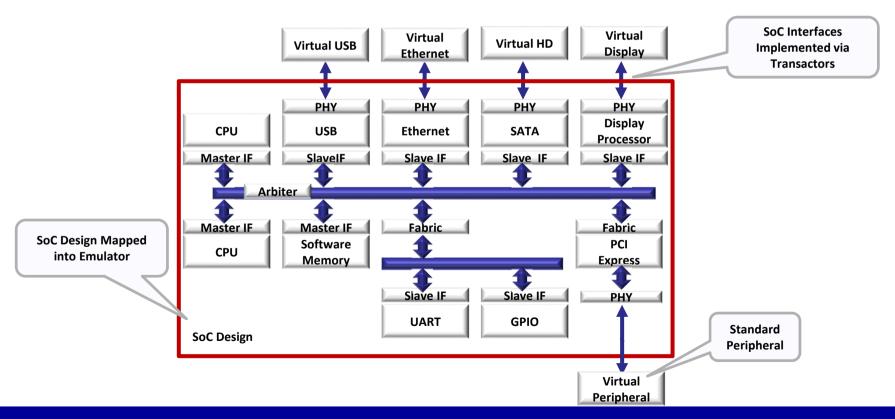

#### Virtual Mode: What Is It?

In Virtual mode, the test environment is modeled in software at high-level of abstraction and connected to the design-under-test (DUT) mapped inside the emulator via a set of transaction-based interfaces

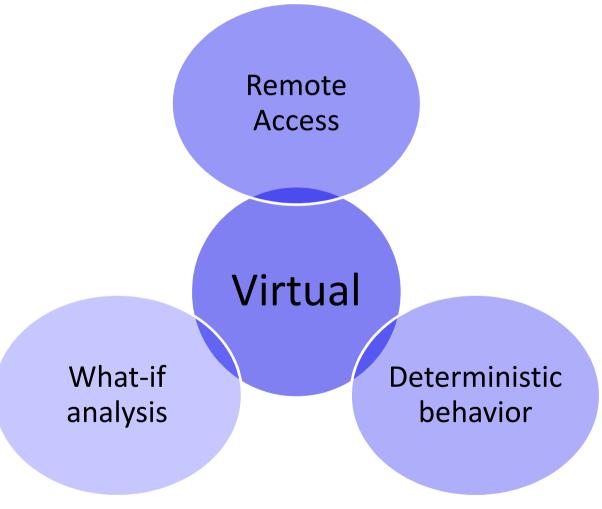

### **Why Customers Use Virtual Mode**

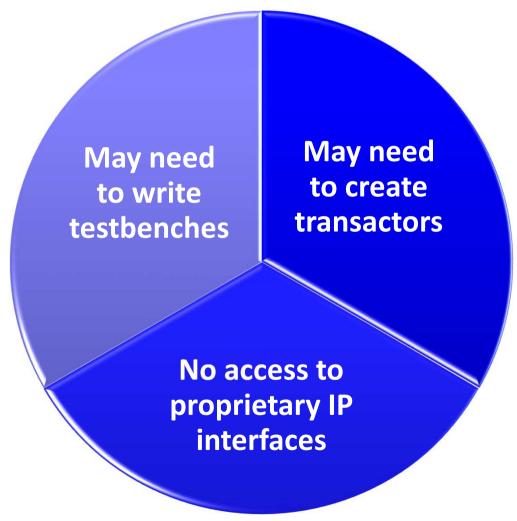

### **Challenges using Virtual Mode**

| Criteria                                | ICE                                                                                                                                                                                                                                                                                                                                       | Virtual                                                                                                                                                                                                                                                                                                                 |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Testbench Type                          | <ul> <li>Physical Target System</li> <li>Run real applications or real traffic</li> </ul>                                                                                                                                                                                                                                                 | Virtual Target System                                                                                                                                                                                                                                                                                                   |

| Testbench Creation                      | <ul> <li>No need to create testbenches; they are the target system</li> </ul>                                                                                                                                                                                                                                                             | <ul> <li>Necessary to create tesbenches, a time-<br/>consuming, error-prone process</li> </ul>                                                                                                                                                                                                                          |

| Interface between Target System and DUT | <ul> <li>Requires speed adapters to target system for each interface protocol</li> <li>Significant H/W dependencies (reset circuitry, noise)</li> <li>Board completion is in critical path; emulation cannot begin until board is ready</li> <li>Lab setup becomes a bottleneck</li> <li>Power hungry</li> <li>Additional cost</li> </ul> | <ul> <li>Requires transactors for each interface protocol</li> <li>No H/W dependencies</li> <li>Completion of S/W development is not in critical path; can begin with existing testbench and emulate parts of design incrementally</li> <li>No power consumption</li> <li>Less expensive than speed adapters</li> </ul> |

| Customization                           | <ul> <li>ICE is critical for customized interfaces</li> <li>Fidelity of the model</li> <li>Non-standard interface</li> <li>Knowledge (IP) can't be shared outside the company</li> <li>Development platforms can be supplied by OEM vendors to early adopters</li> <li>Reproduce FPGA Prototype Setup for Complete Debug</li> </ul>       | Custom virtual interface protocols can be built<br>but require unusual expertise not readily<br>available                                                                                                                                                                                                               |

| Criteria            | ICE                                                             | Virtual                                                           |

|---------------------|-----------------------------------------------------------------|-------------------------------------------------------------------|

| Flexibility         | <ul> <li>Inflexible, difficult to modify</li> </ul>             | <ul> <li>Flexible, easier to modify S/W than H/W</li> </ul>       |

|                     | Restrict emulation access                                       | <ul> <li>Ideal from remote access</li> </ul>                      |

| Reusability         | <ul> <li>Limited reuse; if next design has different</li> </ul> | <ul> <li>Highly reusable; transactors are written once</li> </ul> |

|                     | interfaces, new board design required                           | and used many times                                               |

| <b>Productivity</b> | Hinders productivity                                            | <ul> <li>Increases productivity</li> </ul>                        |

| Reliability         | <ul> <li>Complex, potentially not reliable</li> </ul>           | <ul> <li>No HW means highly reliable</li> </ul>                   |

| <b>Design Debug</b> | Not deterministic                                               | Deterministic                                                     |

|                     | <ul> <li>Randomness from one run to another</li> </ul>          | <ul> <li>Repeatable behavior</li> </ul>                           |

| Performance         | Run at maximum emulation speed                                  | May run at maximum emulation speed                                |

#### Conclusion

- ICE and Virtual are not necessarily replacement for one another

- ICE is best to test the DUT with real traffic, and when proprietary interfaces are required

- Virtual is best for remote access, deterministic behavior, and what-if-analysis

### Hardware Emulation: ICE vs Virtual **User Experiences**

Alex Starr, AMD

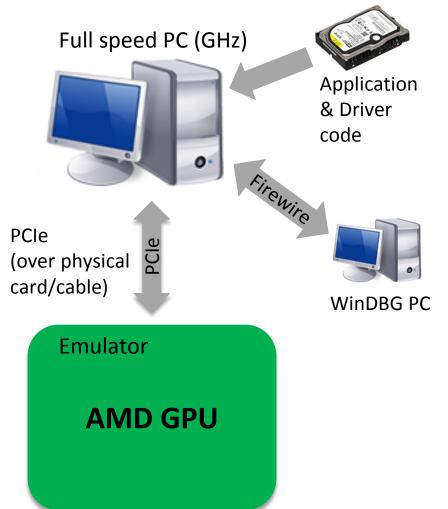

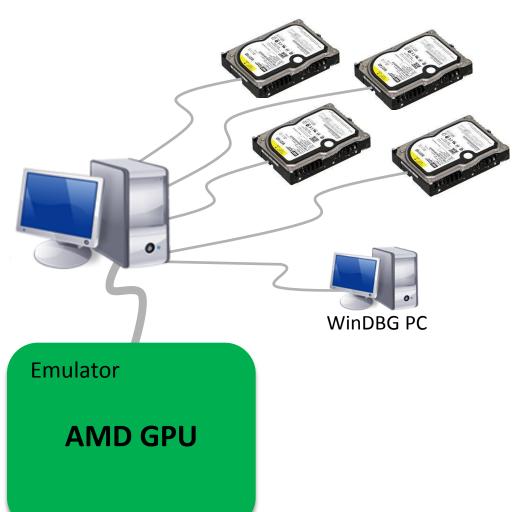

### **Traditional GPU Emulation Solution**

- ICE: In-circuit emulation

- PCIe rate adaptor connects 'Test PC' to emulator

- Hard disk provides software

- Windows software debug done via additional PC running WinDBG

- Three main classes of testing done

- Traditional Verification work

- Linux Based

- Bring up and initialization

- Low level feature testing

- OS Driver & User level code

- Windows Based (Software Team)

- Real Kernel Mode Driver

- Feature/System diagnostics

- Memory coherence

- Power Gating

- Early silicon bring up work

### **In-Circuit Challenges**

- Efficiency, productivity and reliability challenges

- Physical disk swapping

- Ethernet controlled disk switchers

- Complex target cabling a reliability problem

- Custom hardware for "Test PC"

- No save and restore

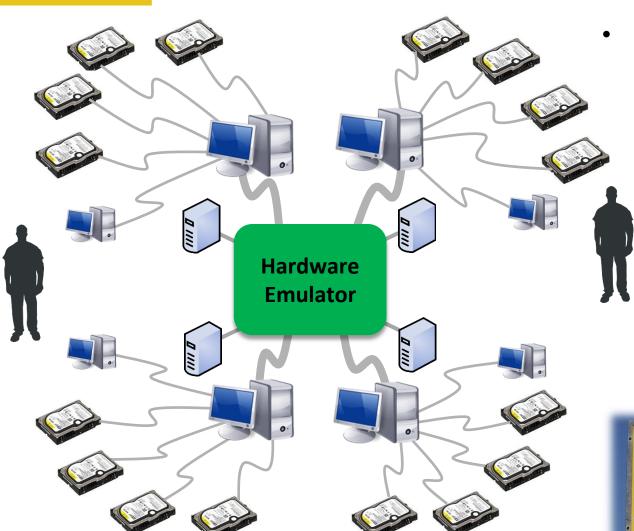

### **Multi-setup Complexity**

- Efficiency, productivity and reliability challenges

- Multiple setups increase complexity

- Specific target hardware for each setup limits flexibility

- On a single emulator and across sites

- Humans cause problems!

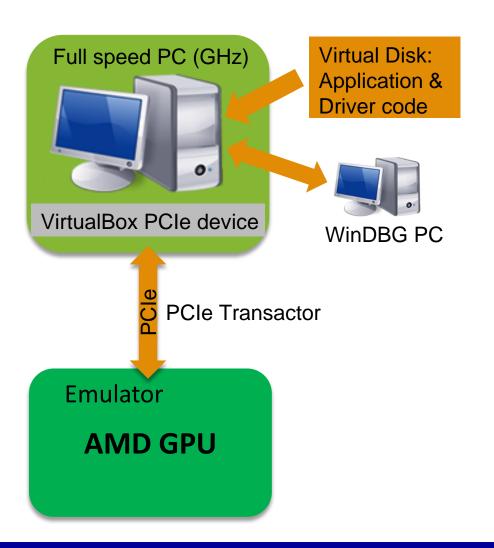

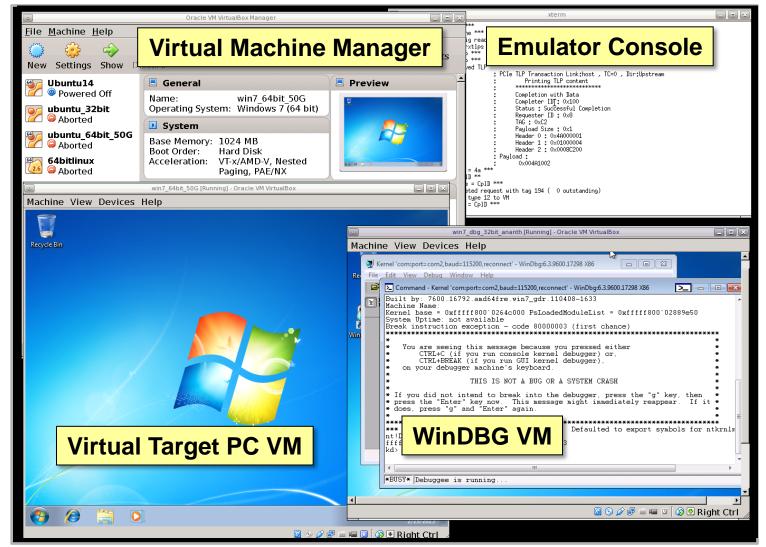

### Virtual Target Solution

- Enable connection to virtualized host machines

- PCIe transactor connects from the host workstation to the emulation hardware

- No in-circuit PCIe connection

- Removal of all in-circuit target devices

- Virtual disks allow images to be used by the VM: no physical disk swapping

- Disk images can be prepared offline in standalone VM

- WinDBG host connection maintained for software debug

### **Virtual Targets: Reduced Complexity**

| Challenge Area                         | Traditional ICE Solution                                  | Virtual Solution                                          |

|----------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------|

| 'Test PC' hard disk changes            | Physical Disk Swapping Ethernet Controlled Disk Switchers | Eliminated: VM disk image selection                       |

| Save/Restore                           | Not possible                                              | Possible (untested)                                       |

| Cabling Complexity                     | Complex Target/Test PC cabling                            | Just single cable to workstation                          |

| "Test PC" custom hardware requirements | Custom hardware for "Test PC" required                    | Generic workstation, unless specific new silicon required |

| Data Center Compatibility              | "High touch"                                              | "No touch"                                                |

| Flexibility                            | Physical target/emulator board constraints                | Dynamically reconfigurable targets via VM                 |

3/22/2016 Alex Starr - AMD

### End User Experience

### **Advanced Virtual Options**

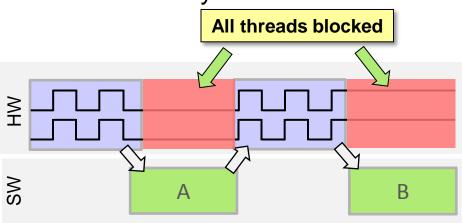

#### Coupled

- Deterministic

- Typically reduced throughput

- Emulator clocks stop to maintain determinism

- Great for debugging

- Keeps Verification engineers warm and cozy!

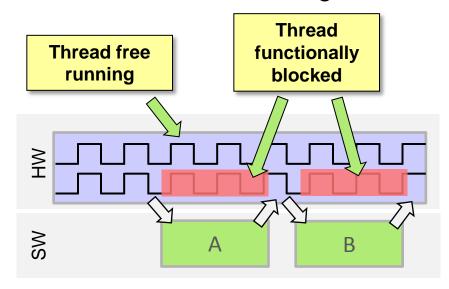

#### **Decoupled**

- Non-deterministic

- Full speed

- Same performance as ICE

- Streaming unidirectional monitors

- Can scare Verification engineers!

### **ICE + Virtual Combination?**

- Get the benefits of ICE and transactors

- Decouple transactors from ICE clock domains

- Concept: Controlled vs Uncontrolled clock domains

- "ICA": In-Circuit Acceleration

- Don't stop those clocks with dynamic targets attached

### **Disclaimer & Attribution**

The information presented in this document is for informational purposes only and may contain technical inaccuracies, omissions and typographical errors.

The information contained herein is subject to change and may be rendered inaccurate for many reasons, including but not limited to product and roadmap changes, component and motherboard version changes, new model and/or product releases, product differences between differing manufacturers, software changes, BIOS flashes, firmware upgrades, or the like. AMD assumes no obligation to update or otherwise correct or revise this information. However, AMD reserves the right to revise this information and to make changes from time to time to the content hereof without obligation of AMD to notify any person of such revisions or changes.

AMD MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE CONTENTS HEREOF AND ASSUMES NO RESPONSIBILITY FOR ANY INACCURACIES, ERRORS OR OMISSIONS THAT MAY APPEAR IN THIS INFORMATION.

AMD SPECIFICALLY DISCLAIMS ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR ANY PARTICULAR PURPOSE. IN NO EVENT WILL AMD BE LIABLE TO ANY PERSON FOR ANY DIRECT, INDIRECT, SPECIAL OR OTHER CONSEQUENTIAL DAMAGES ARISING FROM THE USE OF ANY INFORMATION CONTAINED HEREIN, EVEN IF AMD IS EXPRESSLY ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

#### <u>ATTRIBUTION</u>

© 2016 Advanced Micro Devices, Inc. All rights reserved. AMD, the AMD Arrow logo and combinations thereof are trademarks of Advanced Micro Devices, Inc. in the United States and/or other jurisdictions. Other names are for informational purposes only and may be trademarks of their respective owners.

VirtualBox Virtual Machine: Oracle. [Online] www.virtualbox.org