# **Guaranteed Vertical Reuse – C Execution In a UVM Environment**

Rachida EL IDRISSI, ST-Ericsson, Rabat, Morocco,

Phone: 00 212 5 37 67 86 71

Email: rachida.el-idrissi@stericsson.com

# Introduction

At ST-Ericsson Rabat, Morocco, we develop hardware design IP and related driver software for wireless mobile platforms created elsewhere within the company. Our verification team has to achieve high levels of quality and provide verification deliverables that can be reused by integration teams to make their work more effective.

We recently adopted the Universal Verification Methodology (UVM) since it provides an opensource, vendor-independent, consistent architecture that allows us to share verification components and stimulus throughout the company. This paper describes a C-API package built on top of the UVM that allows us to develop software early in the life of a design IP. Our results are twofold: first, we are able to deliver software tests that can be reused by hardware integration and verification teams; second, we are able to deliver fully functional driver code to software developers early in the overall project cycle.

### **Project background**

We developed the C-API package during development of new design IP for the MIPI Low Latency Interface (LLI). The LLI allows two chips to share resources over a point-to-point high-speed interface.

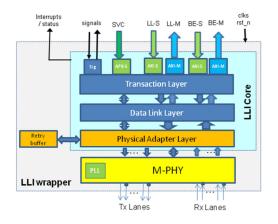

The LLI architecture is described in figure 1.

Our UVM verification environment was used to meet an exhaustive verification plan for the LLI design IP using sequence-based stimulus. The environment is comprehensive and allowed us to use multi-channel constrained random stimulus combined with scoreboarding and functional Alain GONIER, Mentor Graphics, France

Phone: 00 33 1 40 94 7452

Email: alain\_gonier@mentor.com

coverage analysis that checked each physical and logical layer of the LLI protocol.

## Figure 1- LLI logical layers

One of our required deliverables was a set of test cases that could be run as software by platform integration teams. ST-Ericsson has a SoC software framework that defines how these test cases should work and their interfaces. We realised that we could reuse the UVM environment to develop these test cases by developing an API package based on the use of the SystemVerilog Direct Programming Interface (DPI).

# The LLI UVM verification architecture

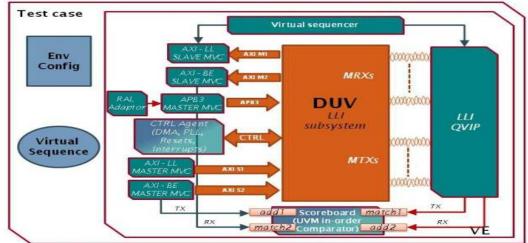

The LLI DUV has several standard interfaces, some of which are design specific. The standard interfaces are the AMBA APB3 and AXI3, together with the MIPI LLI physical interface. The designspecific interfaces concern low-level control and interrupts.

The APB3 interface is used to program the registers within the LLI subsystem. A UVM register model was developed to abstract sequence-based register stimulus.

The AXI interfaces are used for data transfer between the two sides of the LLI. The LLI subsystem has four physical channels that are used for this purpose: a low latency (LL) master interface; a LL slave interface; a best effort (BE) master interface; and a BE slave interface. Each interface was connected to a master or slave AXI3 Questa Verification IP (QVIP) in order to source or sink data transfer across the LLI link as shown in figure 2

Figure 2- UVM Testbench architecture

A LLI QVIP connected to the PHY signals was used to represent the behaviour of a partner LLI device. The QVIP supports a transactional interface that makes it straightforward to configure and send different types of LLI traffic, including sourcing and sinking LL and BE data transfers. Both the LLI subsystem and the LLI QVIP could be configured as a master or a slave LLI device.

Scoreboards and functional coverage monitors were developed that used the different transaction types available within the environment to check for correct device behaviour and to collect functional coverage.

## C-API integration with the UVM environment

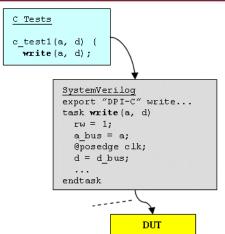

To support the use of a C-API, an optional layer was created for the UVM testbench. This was implemented as the lli\_c\_api SystemVerilog package. The C-API layer is implemented using the SystemVerilog DPI, which allows a number of SystemVerilog tasks and functions to be made available to C programs and executed as depicted in the Figure 3- SystemVerilog DPI mechanism.

Figure 3- SystemVerilog DPI mechanism

Furthermore, you can refer to Mentor Graphics Verification Academy located at http://verificationacademy.com/uvmovm/CBasedStimulus for a detailed description of C/UVM tests integration principles.

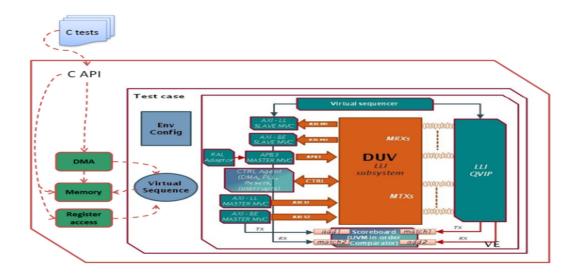

In our environment, the exposed API provides access to four main areas of functionality as shown in Figure 4 below.

# Figure 4- C API access block diagram

The package implements the testbench side of the API as either DUT-centric (by configuring hardware registers via an APB3 QVIP and sending data traffic using DMA via the AXI3 QVIPs), or as LLI QVIPcentric (by configuring the QVIP and streaming data traffic through it to emulate DMA transfers). C test cases were developed using this API using a runtime parameter to determine which side of the test bench the stimulus was directed to.

The 4 main areas are:

- Register reads and writes using an address map implemented in the package.

- a. DPI\_HAL\_READ32 ()

- b. DPI\_HAL\_WRITE32 ()

- DMA Controller API, used for setting up a DMA transfer between the DUV and the LLI QVIP on LL and BE channels. The list of functions used are below

- a. DPI\_dmac\_drv\_enable

- b. DPI\_dmac\_drv\_disable

- c. DPI\_dmac\_drv\_is\_dma\_enabled

- d. DPI\_dmac\_drv\_get\_dma\_enable

d channels

- e. DPI\_dmac\_drv\_start\_channel

- f. DPI\_dmac\_drv\_is\_channel\_done

- g. DPI\_dmac\_drv\_clear\_channel\_d one

- h. ...

A code snippet below shows how one function is implemented:

functionautomaticbyteDPI\_dmac\_drv\_is\_dma\_enabled(device\_type\_edevice);return DMAC[device].get\_dma\_enable();endfunction:DPI\_dmac\_drv\_is\_dma\_enabled

It is then exported in the IIi C API package as shown below and thus callable by the C test

// DMA Functionality DPI Method Exports: export "DPI-C" function DPI\_dmac\_drv\_enable; export "DPI-C" function DPI\_dmac\_drv\_disable; export "DPI-C" function DPI\_dmac\_drv\_is\_dma\_enabled;

- Memory block functions, used for setting up and checking areas of memory used by the DMA controller.

- a. DPI\_init\_mem

...

b. DPI\_get\_mem

A code snippet below shows how one function is implemented:

function automatic int **DPI\_get\_mem**(device\_type\_e device, int addr); `uvm\_info("get\_mem",\$sformatf("%s get\_mem at @:%08x START ... \n",device,addr), UVM\_MEDIUM) if( (addr >= `LMI\_MEMORY\_BASE\_ADDRESS) && (addr <= (`LMI\_MEMORY\_BASE\_ADDRESS + `LMI\_MEM\_RANGE))) return LMI[device].get(addr);//local LMI memory init else if ((addr >= `EMI\_MEMORY\_BASE\_ADDRESS) && (addr <= (`EMI\_MEMORY\_BASE\_ADDRESS + `EMI\_MEM\_RANGE))) return EMI[device].get(addr);//local EMI memory init else//anything else is just stored temporarly into a "virtual" memory return mem[device].get(addr); endfunction: **DPI\_get\_mem**

### 4. Delay functions.

the main goal of those functions is to insert some delays in ns or us and also to establich the synchronisation between the C and SV domains.

- a. wait\_n\_ns

- b. wait\_n\_us

- c. esw\_sync

A code snippet below shows how one function is implemented:

```

task automatic wait_n_ns(int n);

time p;

p = 1ns;

p = p * n;

#p;

endtask: wait_n_ns

```

To link the DPI functions/tasks to the C test, during compilation a header file is automatically

generated declaring all exported/imported functions prototypes to be use either from SV to C or from C to SV. In our case the generated file is called lli\_c\_api.h. and contains the few functions detailed previously.

### C test execution example

We will take a concrete example to illustrate a C test/UVM testbench interaction. As an example, one of our tests generates LL channel traffic concurrently on both the DUT and TB side to check that the link is working properly. Note, except during the initial setup process, both the DUT and the TB side are generally running the same SW.

In that test, on the DUT and TB side, a call to the API will be done to request an LL channel transfer. The C test will call the API function DPI\_HAL\_READ32 through the DPI, requesting a 32-bit read access in the range of the LL channel to happen in the UVM TB.

A code snippet of that API function is shown below:

task automatic DPI\_HAL\_READ32(input device\_type\_e device, input int address, output int data);

```

// Anything else:

if(device == DUT)

```

end

apb\_read(device, address[15:0], data);

else begin

....

//decode QVIP read access to local/remote registers

`uvm\_info("DPI\_HAL\_READ32",\$sformatf("%s: HAL READ %0h @ %0h COMPLETED \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\n", device, data, address),UVM\_LOW); endtask: **DPI\_HAL\_READ32**

As we can see in the code above, the call to the API function by the DUT translates into a call to do\_ll\_be\_read with parameter device=DUT, channel=LL, size=32 and address equal to the address location to be read; data will return the read value. Whilst a call by the TB will call the

same function but with the device parameter set to TB.

The code below shows the function do\_ll\_be\_read:

task automatic do\_ll\_be\_read(input device\_type\_e device,input rw\_seq\_channel\_t channel, input int size, input int address, output int data);

```

lli_ll_be_seq_base

Il_rd_seq;//base class for LL/BE transfer

Ili_Il_be_read_DUT_seq II_rd_seq_DUT= lli_ll_be_read_DUT_seq::type_id::create("II_rd_seq_DUT");

Ili_Il_be_read_TB_seq

Il_rd_seq_TB= lli_ll_be_read_TB_seq::type_id::create("ll_rd_seq_TB");

//specialized sequence depending on initiator

case(device)

DUT: $cast(II_rd_seq,II_rd_seq_DUT);

TB $cast(Il_rd_seq,Il_rd_seq_TB);

endcase

//setup transaction -> AXI request if DUT and QVIP LL request if TB

constrain transfer size to "size" bits

//

if

(!ll_rd_seq.randomize() with

ll rd seq.addr

== address;

transfer_byte_size

== (local::size/8);

}

)

.....

II rd seq.transfer channel

= channel;

II_rd_seq.start(v_sqr);

.....

data = II rd seq.data[0];

endtask: do II be read

generating an LL read transaction of the LL AXI

Eventually, the C test call to DPI_HAL_READ32 is

interface.

```

translated into a UVM sequence generating the appropriate read transaction. If the function is called by the DUT, it will translate into a sequence

The code below shows the DUT LL sequence:

// DUT->TB LL/BE READ REQ

class lli\_ll\_be\_read\_DUT\_seq extends lli\_ll\_be\_DUT\_seq\_base;

.....

task body;

axi\_atomic\_read\_seq read\_seq = axi\_atomic\_read\_seq::type\_id::create("read\_seq");

```

super.body();

if (!read_seq.randomize() with

{

addr == local::this.addr;

transfer_byte_size==local::this.transfer_byte_size;

}

)

```

# read\_seq.start(transfer\_channel\_sqr[transfer\_channel]);

```

endtask: body

endclass: lli_ll_be_read_DUT_seq

```

In the case of the TB, it will translate into a sequence generating an LL read transaction but on the QVIP LLI LL interface.

The code below shows the sequence generating the TB LL sequence:

```

// TB->DUT LL/BE READ REQ

class lli_ll_be_read_TB_seq extends lli_ll_be_TB_seq_base;

```

task body();

.....

....

# lli\_atomic\_read\_t read\_seq=lli\_atomic\_read\_t::type\_id::create("read\_seq");

int j=0;

```

super.body();

```

```

if

(!read_seq.randomize() with

{

Addr == local::this.addr;

transfer_byte_size== local::this.transfer_byte_size;

}

)

case(transfer_channel)

LL: read_seq.m_ch_id_user = MGC_LLI_CH_LL_REQ;

BE: read_seq.m_ch_id_user = MGC_LLI_CH_BE_REQ;

endcase

read_seq.start(v_sqr.lli_sqr);

....

//fill in data

data[j] = '0;

foreach(read_seq.m_read_data[i])

begin

data[j] = data[j] | (read_seq.m_read_data[i]<< ( (i % (AXI_LL_MASTER_PARAMS::AXI_WDATA_WIDTH/8))*8));

if((i+1) % (AXI_LL_MASTER_PARAMS::AXI_WDATA_WIDTH/8) == 0)

begin

j++;//go to next data word

```

data[j] = '0;//initialize data word

end

end

endtask: body

endclass: llih\_II\_be\_read\_TB\_seq

In order to start the C program, DPI tasks need to be called from SystemVerilog start\_DUT\_c\_code() and start\_TB\_c\_code(); task run phase(uvm phase phase);

phase.raise\_objection(this); //specific C test sequences to be launched

//launch both SW and response sequence for QVIP LL/BE requests

fork

start\_DUT\_c\_code();

start\_TB\_c\_code();

be\_slave\_seq.start(m\_env.v\_sequencer.axi\_II\_slave\_sqr);//slave sequence to get QVIP->DUT BE req LLI->AXI

II\_slave\_seq.start(m\_env.v\_sequencer.axi\_be\_slave\_sqr);//slave sequence to get QVIP->DUT LL req LLI->AXI

join

phase.drop\_objection(this);

endtask: run\_phase

In the C code, we need to implement a function

call with the same name,

int start\_DUT\_c\_code()

{

set\_hal\_mode(DUT);

//-- Initialize LLI Driver

Ili\_test\_initialize(&lli\_local, INSTANCE\_NAME, 0, INSTANCE\_MPHY, INSTANCE\_REF\_CLK);

//-- Run Test

run\_test(&lli\_local);

printf(" \*\*\*\*\*\*\*\*\*\* %s Test Done ! \*\*\*\*\*\*\*\*\*\*\n", INSTANCE\_NAME);

return(0); }

```

int start_TB_c_code()

{

set_hal_mode(TB);

//-- Initialize LLI Driver

Ili_test_initialize(&Ili_local,INSTANCE_NAME, LLI_SVC_BASE_ADDRESS,INSTANCE_MPHY, INSTANCE_REF_CLK);

//-- Run Test

run_test(&Ili_local);

printf(" ********* %s Test Done ! ********\n", INSTANCE_NAME);

return(0);

}

```

The UVM testbench should call the above functions during an active UVM phase such as the

run\_phase; in our case, in order to start C execution.

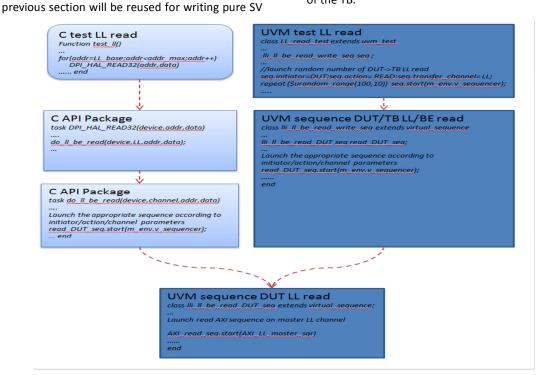

Horizontal reuse across UVM tests and C tests

The overhead to execute a C test is limited, only residing in writing the C API package defining the

DPI tasks. The UVM sequences described in the provinces centring must for writing must SV.

# Figure 5- C vs. UVM test reuse

### C tests contribution to coverage

Since we are running the C tests on a SV UVM testbench containing our coverage model, we can measure the coverage contribution of our C test suite and more importantly, check which functionalities are covered and which are not by the test suite. It is then up to the verification team to choose to address the coverage holes using a C test or a SV test.

| Verification Management Tracker :     |                              |

|---------------------------------------|------------------------------|

| Sec# Testplan Section / Coverage Link | Coverage Coverage graph Goal |

| 0 🖃 🔆 testplan                        | 84.44%                       |

| 1 🛓 🔆 Introduction                    | 100%                         |

| 2 🚊 🔆 Transfers                       | 65% 1009                     |

| 2.0 🕞 🔆 Transfer direction            | 100% 1009                    |

| 2.0 😟 🔆 Transfer with no wait states  | 100% 100%                    |

| 2.0 🕞 🔆 Transfer with wait states     | 20% 1009                     |

| 2.1 🗼 🔆 Write transfers               | 60% 1009                     |

| 2.2 🗼 🔆 Read transfers                | 60% 1005                     |

| 2.3 🗄 🔆 Error response                | 50% 1009                     |

| 3 🚊 🔆 Operating States                | 100% 100%                    |

| 3.1 🕢 🖈 Operating States              | 100% 100%                    |

| 4 😑 🔆 AMBA 3 APB signals              | 91.66%                       |

|                                       | 1009 1009                    |

tests and generate traffic on the different

interfaces. The result, depicted below with an example of C test and SV test both initiating LL

Figure 6- Functional coverage snapshot

For instance, the snapshot above shows the coverage contribution of one C test on the APB3 interface protocol test plan. We can see that almost 85% of the protocol is covered running that single test. Other C tests—for instance setting LL/BE transfers—will contribute to the coverage of the AXI protocol as it is the interface used for the transfer.

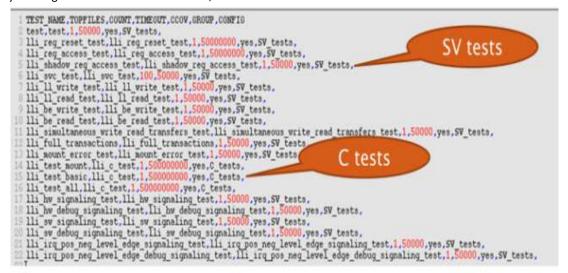

### C/SV tests regression system

Our regression system is using a text file as an input to define the regression test suite to be run. By adding a new attribute "GROUP," it was adapted to allow users to choose between running UVM sequence based tests and/or C-based tests.

### Figure 7- Regression suite input

For compilation we have a top makefile that takes care of SV compilation and calls another dedicated makefile that handles C compilation (tests and driver).

The top makefile has a C\_TESTNAME variable that can be overridden at invocation to define the C test name to be compiled. If we run an SV test, we can omit C\_TESTNAME:

<command>if ((%GROUP%) == "C\_tests") then</command>

<command>make -f (%MAKE\_COMPILE%) all C\_TESTNAME=(%TEST\_NAME%) QUESTA\_MVC\_HOME=(%QUESTA\_MVC\_HOME%) </command>

<command>else </command>

<command>make -f (%MAKE\_COMPILE%) all QUESTA\_MVC\_HOME=(%QUESTA\_MVC\_HOME%) </command>

<command>endif </command>

In the case of a C test, C\_TESTNAME will be passed to the C compilation makefile and thus create the according .so files to be loaded at simulation.

In the simulation phase, to run a C test we need to load the shared object for both DUT and TB threads. We rely on the new attribute "GROUP" to add adequate options for the simulation, such as the .so file to be loaded according to the test we are running.

<command>if ((%GROUP%) == "C\_tests") then</command>

<command>setenv **VE\_SIM\_OPTS** "-mvchome (%QUESTA\_MVC\_HOME%) +UVM\_TESTNAME=(%TOPFILES%) -L dut\_lib -L tb\_lib -L qvl\_lib -t 1ps -64 -suppress 8683 -L qvl\_lib

-L mtiUvm -sv\_lib \$QUESTA\_HOME/uvm-1.1a/linux\_x86\_64/uvm\_dpi -sv\_lib ./Tests\_obj/main\_(%TEST\_NAME%)\_DUT -sv\_lib ./Tests\_obj/main\_(%TEST\_NAME%)\_TB "</command>

<command>else </command>

<command>setenv **VE\_SIM\_OPTS** "-mvchome (%QUESTA\_MVC\_HOME%) +UVM\_TESTNAME=(%TOPFILES%) -L dut\_lib -L tb\_lib -L qvl\_lib -t 1ps -64 -suppress 8683 -L qvl\_lib -L mtiUvm -sv\_lib \$QUESTA\_HOME/uvm-1.1a/linux\_x86\_64/uvm\_dpi "</command>

<command>endif </command>

For SV simulation, there is no need for shared objects.

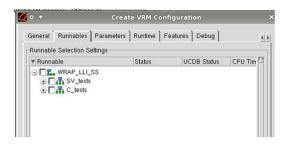

In the regression tool, we also use the attribute "GROUP" to distinguish between C regression test and SV regression:

Figure 8- Regression run cockpit snapshot

And the user can choose the relevant test to run as shown in the Figure 9.:

|        | eatures Debug |         |

|--------|---------------|---------|

|        |               |         |

| Status | UCDB Status   | CPU Tim |

|        |               |         |

|        |               |         |

|        |               |         |

|        |               |         |

| 0.55   |               | 77.0    |

|        | -             |         |

|        |               |         |

| 100    | 122           |         |

|        | 0.777.0       |         |

|        |               | 77.1    |

|        |               |         |

|        | 1223          |         |

|        |               |         |

|        |               |         |

|        |               |         |

Figure 9- Regression run cockpit snapshot

#### Summary and results

We achieved our goal of vertical reuse.

At the IP level, using the C-API package we were able to develop 10 test cases written in C that checked the main LLI functionality using the same UVM environment that we used to verify the design.

We have developed testcases only necessary for SoC integration and for the SW driver, as the exhaustive verification will be completed by SV scenarios.

We were also able to develop a software driver for the LLI IP block.

At the SoC level, the integration team was able to reuse our C tests with no modification and the software development team was able to use our LLI driver with only minimal changes.

The software reuse was made possible thanks to guidance (SW framework cookbook) agreed and deployed within STEricsson.

Modularity of this framework allows maximum reuse of existing code and portability between platforms with minimum coding and debugging effort. The software stack as described in figure 10, is made of four main elements:

- Common modules exportable and reusable through all platforms

- IPs modules, including IP, drivers, interfaces and tests

- Framework or platform-specific drivers and their interfaces

- Project-specific elements, including SoC test bench maps and global test runners

|                     | Proj                                                   | ect (SoC) IP X integ               | ration test runners                  |              |               | a           |

|---------------------|--------------------------------------------------------|------------------------------------|--------------------------------------|--------------|---------------|-------------|

|                     |                                                        |                                    | IP X integration tests               |              |               | interface   |

| SOC and TB          | Layer 1 TB IF                                          | Layer 1 SOC IF                     | Layer 1 CORE IF                      | IP driver IF | VIP driver IF | lite        |

| mapping definitions | Project specific implementation of L1 (mapping to IPs) |                                    |                                      |              |               |             |

|                     | Other VIP drivers<br>(TB_IOLAYER, TAI)                 | Other IP drivers<br>(GPIOs, PRCMU) | Other IP drivers<br>(INTC,DMA,TIMER) | IP X driver  | VIP X driver  | ig and test |

|                     | Other VIP REG IFs                                      | Other IP REG IFs                   | Other IP REG IFs                     | IP X REG IF  | VIP X REG IF  | 夏           |

|                     | HAL interface                                          |                                    |                                      |              |               | Reporting   |

|                     |                                                        | Commor                             | nmon implementation of HAL           |              |               | ſ₽2         |

# Figure 10- Software modular architecture

In the light of our experience, we are now refining the technique to improve performance through the use of interrupts (instead of wait function) and reduce the size of the driver code.

# **References:**

- 1. UVM 1.1a

- ST-Ericsson Alliance Software framework SW structure v1.5

- 3. <u>http://verificationacademy.com/uvm-ovm/CBasedStimulus</u>

# Acknowledgements:

We would like to thank the following colleagues for their contributions to the development of the C-API technique: Jamal EL-HAITOUT and Youssef BAKRIM from ST-Ericsson; Mark PERYER, and Yassine LAHLOU from Mentor Graphics.