# Functional-Coverage Sampling in UVM RAL: Use of 2 Obscure Methods

Muneeb Ulla Shariff, Mirafra Technologies Pvt Ltd, Bangalore

Ravi Reddy, Roche Sequencing Solutions, Santa Clara

## Agenda

- UVM RAL (Register Abstraction Layer)

- UVM RAL Functional Coverage

- Implementation

- Prediction

- Auto Prediction

- Explicit Prediction

- Role of Register Code Generator

- Comparison

- Results

DESIGN AND VERIE

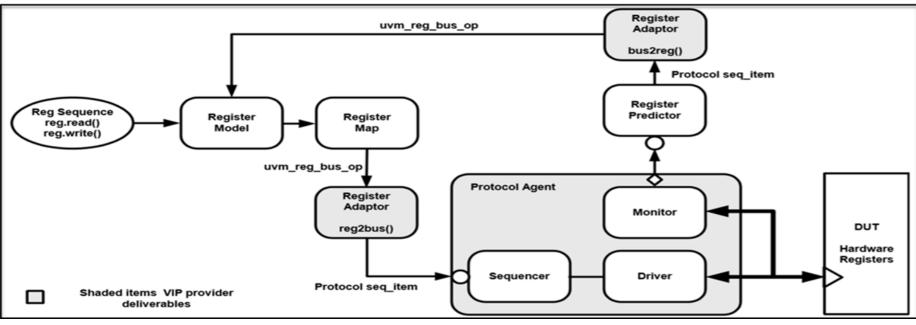

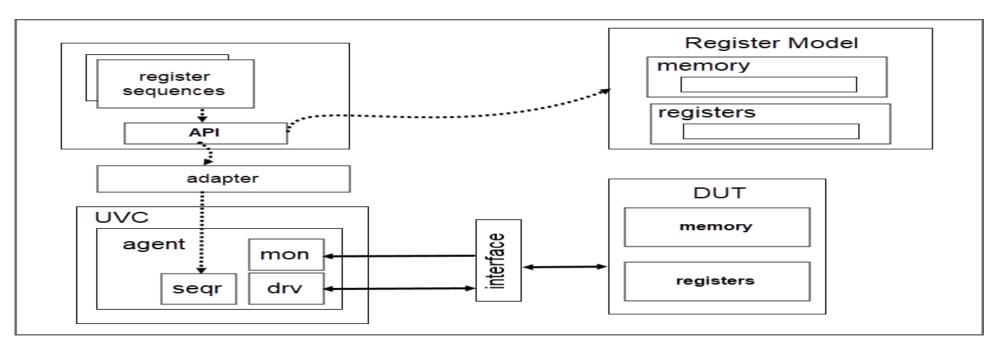

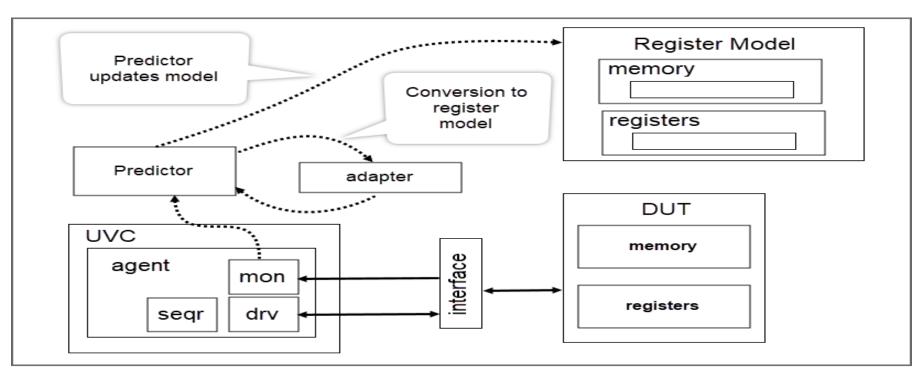

### UVM RAL

- Mimics the design hardware register contents at the TestBench (TB) side.

- Provides the abstract accesses to registers and memories.

Figure 1. UVM Register Model Integration [1]

DESIGN AND VERIFICATION

### **UVM RAL Functional Coverage**

- Functional Coverage is a measure of what functionalities/features of the design have been exercised by the stimulus/tests.

- UVM RAL Functional Coverage is helpful in providing the metrics used for gauging all register accesses including individual register bits.

## UVM RAL Functional Coverage (contd..)

- The functional coverage of the RAL model is usually created by the register model generators. However, the sampling of the covergroup requires attentive work.

- sample() and sample\_values() methods are used for sampling.

• Due to the lack of information about these methods, they are rarely and improperly used.

#### **Implementation Steps**

1. The covergroup and coverpoints must be defined. This is done using the register assistant tools.

```

class dp_deac_enginel_thresh1 extends uvm_reg;

`uvm_object_utils(dp_deac_enginel_thresh1)

uvm_reg_field reserved; // Reserved

rand uvm_reg_field vote_thresh;

rand uvm_reg_field compb_thresh;

rand uvm_reg_field compa_thresh;

// Function: coverage

covergroup cg_vals;

vote_thresh : coverpoint vote_thresh.value[7:0];

compb_thresh : coverpoint compb_thresh.value[8:0];

compa_thresh : coverpoint compa_thresh.value[8:0];

endgroup

```

Figure 2. Covergroup definition

DESIGN AND VE

2. The coverage model needs to be constructed conditionally.

```

// Function: new

function new(string name = "dp_deac_engine1_thresh1");

super.new(name, 32, build_coverage(UVM_CVR_FIELD_VALS));

add_coverage(build_coverage(UVM_CVR_FIELD_VALS));

if(has_coverage(UVM_CVR_FIELD_VALS)) begin

cg_vals = new();

cg_vals.set_inst_name(name);

end

endfunction

```

Figure 3. Covergroup construction [2]

DESIGN AND VER

3. Before building the reg model, we need to set the include\_coverage(...) to indicate which models to be constructed.

```

// Building the register model

If(fpgadp_regs == null) begin

// Specify which coverage model that must be included in various blocks,

// register or memory abstraction class instances.

uvm_reg::include_coverage("*",UVM_CVR_ALL);

this.fpgadp_regs = fpgadp_register_pkg_uvm::fpgadp_cfg::type_id::create("fpgadp_regs",this);

fpgadp_regs.build();

// Enables sampling of coverage

fpgadp_regs.set_coverage(UVM_CVR_ALL);

fpgadp_regs.lock_model();

end

```

Figure 4. Enabling building and sampling of coverage [2]

DESIGN AND VE

Eventually, you need to tell the compiler to enable coverage collection (The below options qualifies for Cadence Incisive Simulator)

-uvm -write\_metrics -covfile cov\_config\_file -coverage All

# cov config file

set\_covergroup -per\_instance\_default\_one

5. Finally we need to sample the coverage using the 2 methods, uvm\_reg::sample() and uvm\_reg::sample\_values().

• We need prediction to update the RAL model.

Based on either auto-prediction mode or explicit-prediction mode, the sample() or sample\_values() methods are used and implemented.

#### **UVM RAL Prediction**

- In UVM Register Modelling, a prediction is an art of keeping the Register Model up-to-date with expected results for the design registers.

- This allows us to compare the expected results from the Register Model with actual register values from the DUT.

- There are 2 modes:

- Auto-Prediction Mode

- Explicit-Prediction Mode

#### **Auto-Prediction Mode**

• In this prediction mode, the sequences using the UVM register API update the RAL model automatically.

Figure 5. Auto-Prediction Model

DESIGN AND VERIEIC

### Auto-Prediction Mode (contd..)

• On every register access, the uvm\_reg::sample() method is called.

```

if (system_map.get_auto_predict()) begin

uvm_status_e status;

if (rw.status != UVM_NOT_OK) begin

sample(value, -1, 0, rw.map);

m_parent.XsampleX(map_info.offset, 0, rw.map);

end

status = rw.status; // do_predict will override rw.status, so we save it here

do_predict(rw, UVM_PREDICT_WRITE);

rw.status = status;

end

```

Figure 6. uvm\_reg::sample() function call

DESIGN AND VE

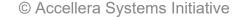

#### Auto-Prediction Mode (contd..)

• The default uvm\_reg::sample() function is empty.

| protected virtual function void samp | le(uvm_reg_data_t_data, |

|--------------------------------------|-------------------------|

| uvm_reg_data                         | _t_byte_en,             |

| bit is_re                            | ad,                     |

| uvm_reg_map                          | map);                   |

| endfunction                          |                         |

Figure 7. uvm\_reg::sample() function definition

DESIGN AND VERI

### Auto-Prediction Mode (contd..)

• Thus, to sample the coverage after each register access we need to implement the uvm\_reg::sample() function.

Figure 8. uvm\_reg::sample() function implementation

DESIGN AND VER

### **Explicit-Prediction Mode**

• This prediction mode updates the register model on all monitored transactions. It uses a predictor component and the UVC adapter.

Figure 9. Explicit Prediction Model

### Explicit-Prediction Mode (contd..)

- With an explicit predictor, when register access is performed, the monitor sends out a transaction to the analysis port which is connected to uvm\_reg\_predictor and this triggers uvm\_reg\_predictor::write()

- This method updates the RAL model. After the update, we can explicitly call the uvm\_reg::sample\_values() method.

- The default uvm\_reg::sample\_values() function is empty.

// Function: sample\_values

virtual function void sample\_values();

endfunction

### Explicit-Prediction Mode (contd..)

• Thus, in-order to sample the coverage we need to implement the uvm\_reg::sample\_values() function.

// Function: sample\_values

virtual function void sample\_values();

super.sample\_values();

if (get\_coverage(UVM\_CVR\_FIELD\_VALS))

cg\_vals.sample();

endfunction

Figure 10. uvm\_reg::sample\_values() function implementation

#### **Explicit-Prediction Mode Example**

class uvm\_reg\_predictor\_custom #(type BUSTYPE=int) extends uvm\_reg\_predictor #(BUSTYPE); 'uvm component param utils(uvm reg predictor#(BUSTYPE)) // Function : new function new (string name, uvm\_component parent); super.new(name, parent); endfunction // Function : write // Over-riding the function to explicitly call the sample values method virtual function void write(BUSTYPE tr); uvm\_reg rg; uvm\_reg\_bus\_op rw; // Calling the parent function super.write(tr); // Getting the register handle adapter.bus2reg(tr, rw); rg = map.get\_reg\_by\_offset(rw.addr, (rw.kind == UVM\_READ)); // Sampling the coverage rg.sample\_values(); endfunction endclass

DESIGN AND VERIFICATION

### Role Of Register Model Generators

- The sample() and sample\_values() method implementations could be done by the register model generators.

- If the generator is unable to do so, the user can write a wrapper script to include the implementations.

- Since the sample() is implicitly called, the user doesn't have to do anything

## Role Of Register Model Generators (contd..)

However, the sample\_values() method has to be called explicitly by the user.

This is imperative because the place at which to call the sample\_values() method is based on the user's need, hence this cannot be generalized and included by the register generators.

#### Comparison

| sample() method                            | sample_values() method           |

|--------------------------------------------|----------------------------------|

| Protected virtual function                 | Virtual function                 |

| Cannot be called explicitly                | Can be called explicitly         |

| Called implicitly on every register access | User has to call it explicitly   |

| Rigid                                      | Convenient and Flexible          |

| Used in auto-prediction mode               | Used in explicit-prediction mode |

DESIGN AND VERIEICATION"

### Results

Without the implementation of either uvm\_reg::sample() or uvm\_reg::sample\_values() the RAL functional coverage will only be created but not sampled.

| 🖌 👔 Instances                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 19.2%       | 23980 / 1058123 ( |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------|

| 👔 userwave_pkg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 15/3        | 0 / 0 (n/a)       |

| a 👔 uvm pkg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 100 446     | 0 / 558 (0%)      |

| 🕨 👔 uwm test top                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 10%         | 0 / 2 (0%)        |

| Set uvm_test_top.fpga_base_reg_test:fpga_base_test:m_env.fpgadp_regs.DP_FPGA_ID.cg_vals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0%          | 0 / 56 (0%)       |

| Iven_test_top.fpga_base_reg_test:fpga_base_test: m_env.fpgalvds_regs.LVDS_BANK_ENABLE0.cg_vals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0%          | 0 / 64 (0%)       |

| Suvm_test_top.fpga_base_reg_test:fpga_base_test: m_env fpgalvds_regs.UVDS_BANK_ENABLE1.cg_vals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1096        | 0 / 64 (0%)       |

| Iven_test_top.fpga_base_reg_test::fpga_base_test::m_env.fpgalvds_regs.LVDS_ISERDES2_RESET0.cg_vals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1076        | 0 / 64 (0%)       |

| ▶ 🍟 uvm_test_top.fpga_base_reg_test:fpga_base_test: m_env.fpgalvds_regs.LVDS_ISERDES2_RESET1_rg_vals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 10%         | 0 / 64 (0%)       |

| In the state of | 100%        | 0 / 64 (0%)       |

| Sum_test_top.fpga_base_reg_test:fpga_base_test: m_env.fpgalvds_regs.LVDS_ISERDES2_BITSLIP1.cg_vals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 100%        | 0/64 (0%)         |

| wm_test_top.fpga_base_reg_test:fpga_base_test: m_env.fpgalvds_regs.LVDS_IDELAYE2_CNT_VM     reg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | vals ICO 0% | 0 / 32 (0%)       |

| Wm_test_top.fpge_bes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1 0%        | 0 / 64 (0%)       |

| RAL Registers Coverage Collected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0%          | 0 / 20 (0%)       |

| DUESTA_MVC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 11/3        | 0 / 0 (m/a)       |

| I mvc.pkg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | n/a         | 0 / 0 (n/a)       |

#### Results

Thus, we need to implement the uvm\_reg::sample() for auto-prediction and uvm\_reg::sample\_values() for explicit-prediction in order to sample the coverage successfully.

| e View An   | alysis Help           |                        |                |                 |       |

|-------------|-----------------------|------------------------|----------------|-----------------|-------|

| Con         | text Source<br>fo Map | All_Metrics            |                | n li ≪at cPo •  | -     |

| Conte       | xt                    | Views                  | Able to sample | the coverage    |       |

| T: Verif    | ication Hie           | rarchy                 |                |                 |       |

| Es UNI Name |                       |                        |                |                 |       |

|             |                       |                        |                |                 | Statu |

|             |                       | (no filter)            | (no fi         | (no filter)     |       |

|             |                       | _iserdes2_bitslip1     | 3.12%          | 2 / 64 (3.12%)  | n/a   |

|             |                       | _idelaye2_cnt_value_in | 10%            | 0 / 32 (0%)     | n/a   |

|             |                       | _idelaye2_cnt_load0    | 10%            | 0 / 64 (0%)     | n/a   |

|             |                       | _idelaye2_cnt_load1    | ! <b></b> 0%   | 0 / 64 (0%)     | n/a   |

|             | Ivds                  | _frame_err0            | 3.12%          | 2 / 64 (3.1.2%) | n/a   |

|             | P P lods              | _frame_errl            | 3.12%          | 2 / 64 (3.1.2%) | n/a   |

|             | F Plvds               | control0               | 53.57%         | 8 / 16 (50%)    | n/a   |

|             | P P lvds              | _frame_window          | 1.56%          | 2 / 128 (1.56%) | n/a   |

|             | P P Ivds              | _idle_sync_pattern     | 1.56%          | 1 / 64 (1.56%)  | n/a   |

|             | P 🔐 Ivds              | _header_sync_pattern   | 1.56%          | 1 / 64 (1.56%)  | n/a   |

| 1           | ► 🔐 Ivds              | _dbg_ctl               | 10%            | 0 / 196 (0%)    | 11/18 |

|             | P P Ivds              | _dbg_data              |                | 0 / 64 (0%)     | n/a   |

| 1           | Ivds                  | chip_ctl1              | 50%            | 1/2 (50%)       | n/a   |

|             | ► 🔐 Ivds              | dma_ctl                | 51.56%         | 4 / 66 (6.06%)  | n/a   |

|             | E Studie              | timestamp_I            |                | 0 / 64 (0%)     | n/a   |

|             | F P Ivds              | timestamp h            | 10%            | 0 / 64 (0%)     | n/a   |

|             | ▶ 🔗 Ivds              | record map ctil        | 40.94%         | 7 / 196 (3.57%) | n/a   |

|             |                       | dma desc ctl           | 67.71%         | 6 / 68 (8.82%)  | ~/m   |

|             |                       | dma desc wr addr I     | 4.69%          | 3 / 64 (4.69%)  | 0.50  |

|             |                       | dma desc wr addr h     | 1.56%          | 1 / 64 (1.56%)  | n/a   |

© Accellera Systems Initiative

### Conclusion

- Since the user is oblivious of the 2 obscure methods, uvm\_reg::sample() and uvm\_reg::sample\_values(), they are rarely used.

- Here, we have shown how to use these methods, along with their implementations, when to use them and their effect on coverage sampling.

#### References

M. Peryer, D. Aerne, "A New Class Of Registers," -DVCon US 2016

1) Verification Academy Coverage Cookbook: https://verificationacademy.com/cookbook/coverage

© Accellera Systems Initiative

#### Questions?