## Introduction

The recent edition of IEEE 1801 specifies

- □ The power state table (PST) construct should be phased out as legacy, and

- □ Replaced by the new semantics of the 'add\_power\_state' UPF command.

This new construct allows

- Incremental refinement of Power states for

- Power domains and

- Its associated supply sets.

- □ This feature provides a way to model any possible combination of power states for a power domain and its available supply sets,

- □ As well allowing modification of these defined power states to accommodate the same UPF construct for different design abstraction levels.

- Consequently such features serve the purpose of the legacy PST, but in more complete and controllable ways.

#### The New Power State Constructs

Power State of Supply Set and Power Domain

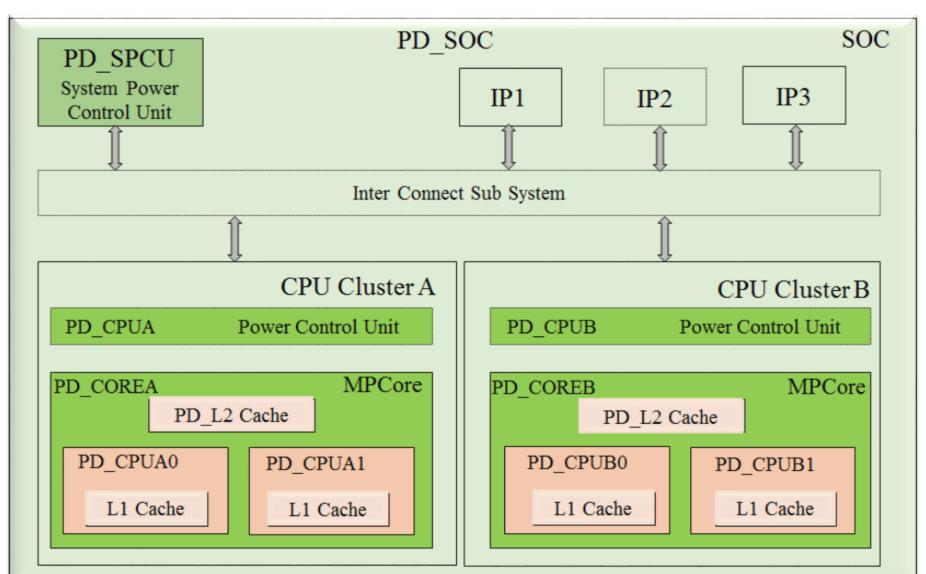

Figure 1. Example of a Complex SoC (Courtesy: ARM SOC)

#### Power States of a Supply Set

```

add_power_state PD_CPUA0.primary

-state {ON -simstate NORMAL -logic_expr {pwr_ctrl==1}

-supply_expr {power=={FULL_ON,1.0} &&

ground=={FULL_ON,0}} }

```

Power States of a Power Domain add\_power\_state PD\_CPUA0 -state {ON -logic\_expr{PD\_CPUA0.retention ==ON && nRETCPU0==1 && PD\_CPUA0.*primary*==ON}}

```

Example of the roots of fundamental power states

of an object (i.e. power domain PD_CPUA0)

add_power_state PD_CPUA0 -domain \

-state {UNDEFINED -logic_expr {PD_CPUA0 != RUN &&

PD_CPUA0 != SHD} } \

-state {RUN –logic_expr {primary == ON} } \

-state {SHD –logic_expr {primary == OFF} } \

-state {ERROR -logic_expr {PD_CPUA0 == RUN && PD_CPUA0

```

# Free Yourself from the Tyranny of Power State Tables with Incrementally Refinable UPF Progyna Khondkar, Ping Yeung, Gabriel Chidolue, Joe Hupcey, Rick Koster and Madhur Bhargava

Mentor Graphics Corporation, Fremont, CA.

# Limitations of Legacy PST

Power states may also represented by the states of a power state tables (PST),

## - add\_port\_state, add\_pst\_state, and create\_pst.

These commands are legacy in UPF 2.1 LRM.

- Because of their limitations to coordinate with supply sets; specifically PST states are defined based on the supply net only, and supply nets are usually available after the synthesis and postlayout levels of design abstraction.

- □ There are no UPF methodologies for PST states to refine states.

- Dependency on upfront information of supply ports and supply nets severely delays the point at which power aware verification can start.

# • Other known limitations

- PST states defined on supply net state only

- Logic net states cannot be used

- No logical view of the system states

- Power domain states cannot be specified

- Complex PST composition is not possible

- No support for hierarchical reference to state

- Reduction of states is not possible

The New Concept of Fundamental Power States

□ The fundamental power state refinement concept extends the UPF specification and associated PA verification boundary to early stages of RTL design and allows verification virtually at any level of design abstraction.

Definite Power State

- Defining –logic\_expr contains only operators == and &&

- Refers only to other Definite states (of same or dependent objects)

- Refined by derivation or branching

- Deferred Power State

- A Definite State that is not yet fully defined

- No defining expression (i.e. no –*logic\_expr*{})

- Refined in place (actually through –*update*)

# □ Indefinite Power State

- Defining –*logic\_expr* contains !, !=, or ||

- Refers to an Indefinite state of a dependent object

- Not refinable (UNDEFINED state)

- But not a misnomer; Usable for don't care

states!

# Refinement by Derivative for Definite States

Example of Definite Power States add\_power\_state PD\_COREA -domain \ -state {RUN –logic\_expr {primary == ON}} \ -state {SHD –logic\_expr {primary == OFF}}

Definite Power States Refinement by Derivatives

add\_power\_state PD\_COREA -domain –update \ -state NEW\_RUN {-logic\_expr \  $\{(power == \{FULL_ON, 1.1\}) \&\& (ground == \{FULL_ON, 0.0\})\}\}$

☐ A new power state, with a new -state name and updated -*logic\_expr*, based on the original power state

## **Refinement In Place for Deferred States**

□ Example of Deferred Power States

add\_power\_state PD\_COREA.primary \ -state ON {-logic\_expr {In3 == 1} -simstate NORMAL} \ -state SHD {-logic\_expr {In3 == 0} -simstate CORRUPT}

Deferred Power States Refinement in Place

add\_power\_state PD\_COREA -domain -update \ -add\_power\_state PD\_COREA.primary -supply -update -state {RUN –logic\_expr {nPWRUP\_CON==1'b0}} {*FULL\_ON*, 0.0})}}

□ Refinements through –*update* implies that it actually modifies the original definition rather than creating a new definition or a new power state.

### Advantages of Definite and Deferred States

- □ Allows to model UPF, i.e. power management architecture from very early stage of design.

- □ Allows to integrate design IP any time in the power management architecture.

- Allows to analyze and validate UPF strategy requirements.

- □ Allows to compute accurate state transition coverage information through interdependent states and

- Prevent intermediate state transitions of definite and deferred power states during refinement.

|   |                             | UF<br>De                                               |

|---|-----------------------------|--------------------------------------------------------|

|   | -st<br>-st<br>ad<br>-st     | d_p<br>tate<br>d_p<br>tate<br>tate                     |

|   |                             | Sta                                                    |

|   | Sou                         | urce<br>To<br>1.1<br>To                                |

|   | anc                         | s <b>sib</b><br>1 nei <sup>-</sup><br>01_tc            |

|   |                             | Isc<br>set<br>UP                                       |

|   | •                           | Cc<br>Tra                                              |

|   | TYI<br>Sta                  | F OE<br>PE: \$<br>bir<br>Powe<br>bir                   |

|   |                             | Cc<br>thr<br><b>dc</b>                                 |

|   | TYI<br>/cpi<br>/cpi<br>/cpi | F OE<br>PE:  <br>u_te:<br>u_te:<br>u_te:<br>wer<br>bir |

| I |                             |                                                        |

|   |                             | PS<br>str                                              |

|   |                             | Bu<br>me<br>toc                                        |

|   |                             | Be<br>po<br>es:<br><i>ref</i>                          |

# **Case Studies**

PF Strategies Analysis and Validation through efinite Power States

power\_state PD\_CPUA0.primary \ e ON {-*logic\_expr* {ln3 == 0} -*simstate* NORMAL} \ e OFF {-*logic\_expr* {In3 == 1} -*simstate* CORRUPT} power\_state PD\_COREA.primary \ e ON {-*logic\_expr* {ln3 == 1} -*simstate* NORMAL} \ e OFF {-*logic\_expr* {ln3 == 0} -*simstate* CORRUPT}

## tatic Analysis Report

power domain: ~/PD\_CPUA0 to Sink power domain: ~/PD\_COREA. otal 3 Missing isolation cells [Total Crossings: 3, Shared Crossings: 0] . Source port: ~/q\_A [LowConn] to Sink port: ~/q\_A [HighConn], width:1 otal 1 Missing isolation cells [Total Crossings: 1, Shared Crossings: 0] 1.1.1. Inferred type: ISO\_MISSING, count: 1 **ble reason**: 'Isolation is required from (~/PD\_CPUA0)=>(~/PD\_COREA) ither isolation strategy nor isolation cell is present in design' Analysis link:

o\_PD2].

olation analysis and validation done without **\_isolation** strategy definition or implementation 'F at a very early stage of design abstraction.

overage Computation of Power Stateansition through **describe\_state\_transition**

| OBJECT                                                    | Metric   | Goal             | Status |         |  |  |

|-----------------------------------------------------------|----------|------------------|--------|---------|--|--|

| : SUPPLY SET /cpu_tester/dut/PD_CPUA0.primary<br>Coverage |          |                  |        |         |  |  |

| wer State PD_CPUA0_low_volt                               |          | 100.0%           | 100    | Covered |  |  |

| bin ACTIVE                                                | 3        | 1 Cove           | red    |         |  |  |

| wer State PD_CPUA0_moderate_vo<br>bin ACTIVE              | olt<br>1 | 100.0%<br>1 Cove | ~      | Covered |  |  |

overage Computation of Power State-Transition rough describe\_state\_cross\_coverage omains {PD\_COREA} -depth 3 ..... etc.

| DBJECT                                                                                  | Metric | Goal           | Status        |                        |

|-----------------------------------------------------------------------------------------|--------|----------------|---------------|------------------------|

| <b>POWER STATE CROSS</b><br>ester/dut/PD_COREA(ID:PD1),                                 |        |                |               |                        |

| ester/dut/PD_CPUA0(ID:PD2),<br>ester/dut/PD_L2(ID:PD3)<br>r <b>State Cross Coverage</b> |        | 33.3%<br>33.3% | 100           | Uncovered<br>Uncovered |

| in \PD1:SLEEP-PD2:PD_CPUA<br>D1:RUN-PD2:PD_CPUA0_on-P                                   |        |                | _off 01<br>21 | ZERO<br>Covered        |

### Conclusions

ST replacement with **add\_power\_state** is raightforward and simple

ut the change will impact the power specification ethodologies, power aware verification algorithms, ols, techniques and the entire design, verification nd implementation flow.

ecause definite (indefinite as well) and deferred ower states provides the intrinsic flexibility, ssential controllability and the gifted features of *refinement* options.