# Extending Proven Digital Verification Techniques for Mixed-Signal SoCs with VCS AMS

Helene Thibieroz, Synopsys Adiel Khan, Synopsys Pierluigi Daglio, STMicroelectronics Gernot Koch, Micronas

# Agenda

This tutorial includes:

- Introduction to VCS AMS mixed-signal verification solution

- Technical presentation of AMS Testbench

- STMicroelectronics highlights their usage of VCS AMS to accelerate mixed-signal verification using Save and Restore

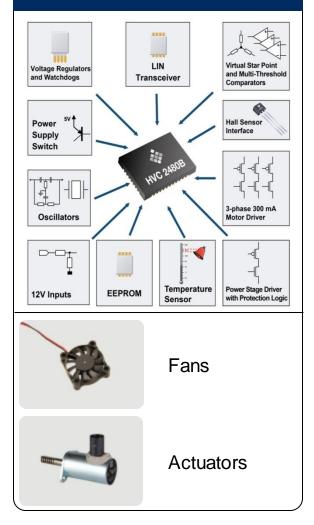

- Micronas describes their usage of VCS AMS behavioral modeling capabilities for their validation methodology of mixed-signal sensor-based applications.

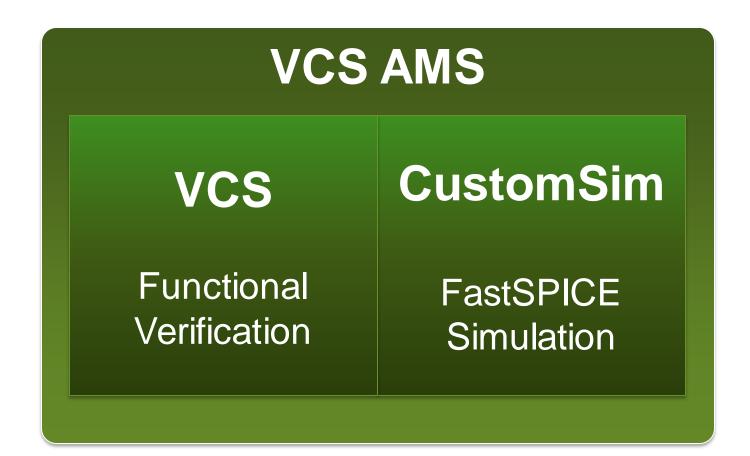

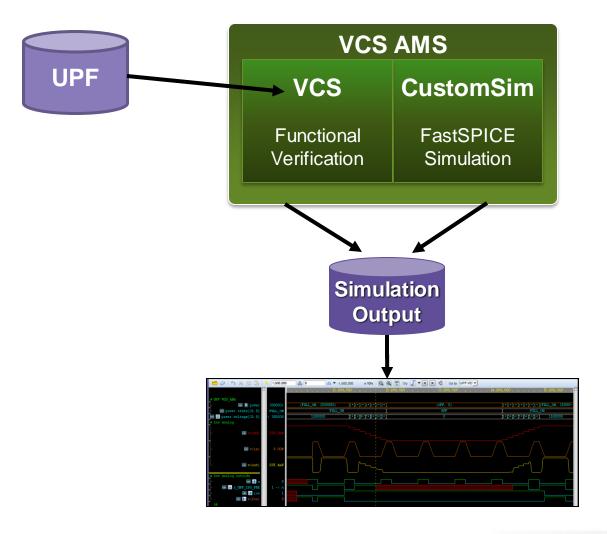

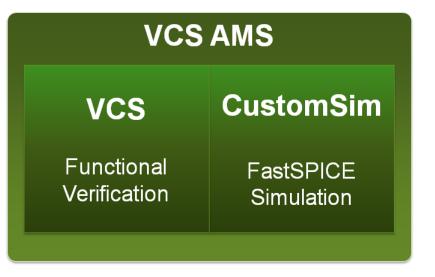

### **VCS AMS**

### Mixed-signal Verification Solution

Helene Thibieroz Product Marketing Synopsys

### Introducing VCS AMS

Mixed-signal Verification Solution

### **VCS AMS – Technologies**

SYNOPSYS<sup>®</sup> Accelerating Innovation

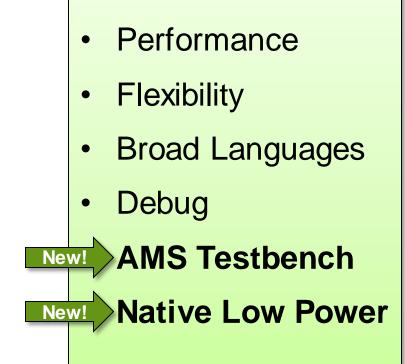

## **VCS AMS – Performance**

Best Performance with Transistor-level Accuracy

SYIIUF

Innovation

### VCS AMS – Flexibility

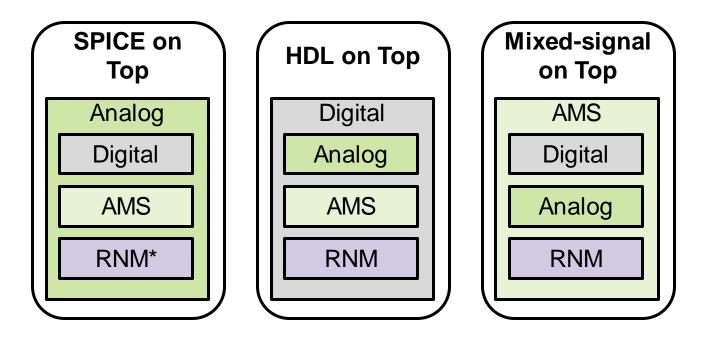

Multiple Topologies Offered for Complex SoCs

Multiple Topologies and Configurations

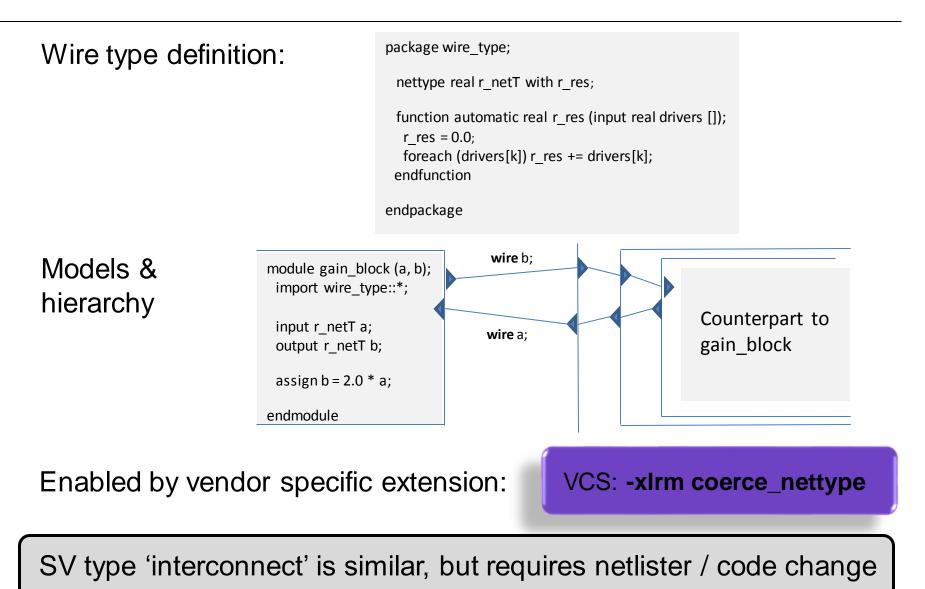

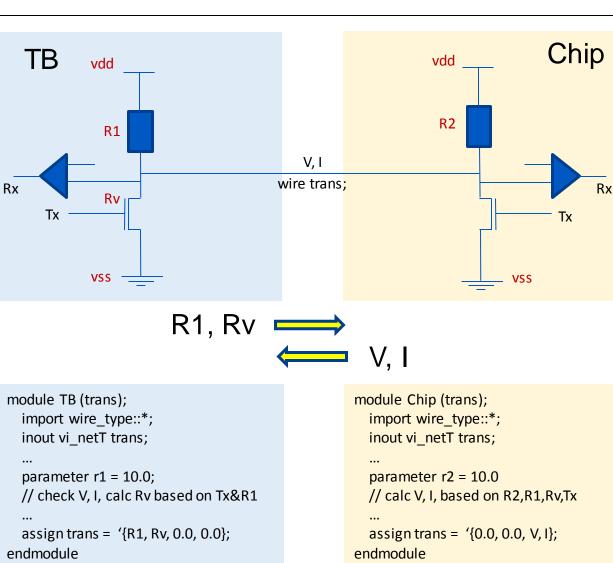

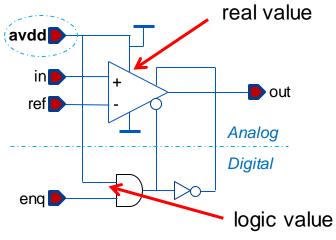

\* Real Number Modeling

## VCS AMS – Broad Language Support

Enables Complex Integration Schemes for Mixed-signal SoCs

| Analog          | Digital         | Mixed-signal             |

|-----------------|-----------------|--------------------------|

| SPICE           | Verilog         | Verilog-AMS              |

| Verilog-A       | VHDL            | Real Number Model        |

| SPEF, DSPF, DPF | SystemVerilog   | SystemVerilog<br>nettype |

|                 | SystemC, Matlab |                          |

# VCS AMS – Debug

Assisted Setup and Debugging

- Easy configuration

- VCS use model

- Netlist driven

- Automated insertion of A/D interface elements

- Optimized for speed and accuracy

- Connectivity reports

- Interface elements

- Port mapping

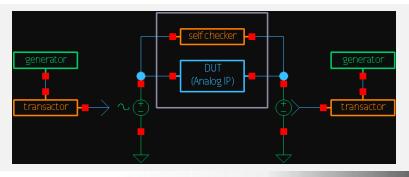

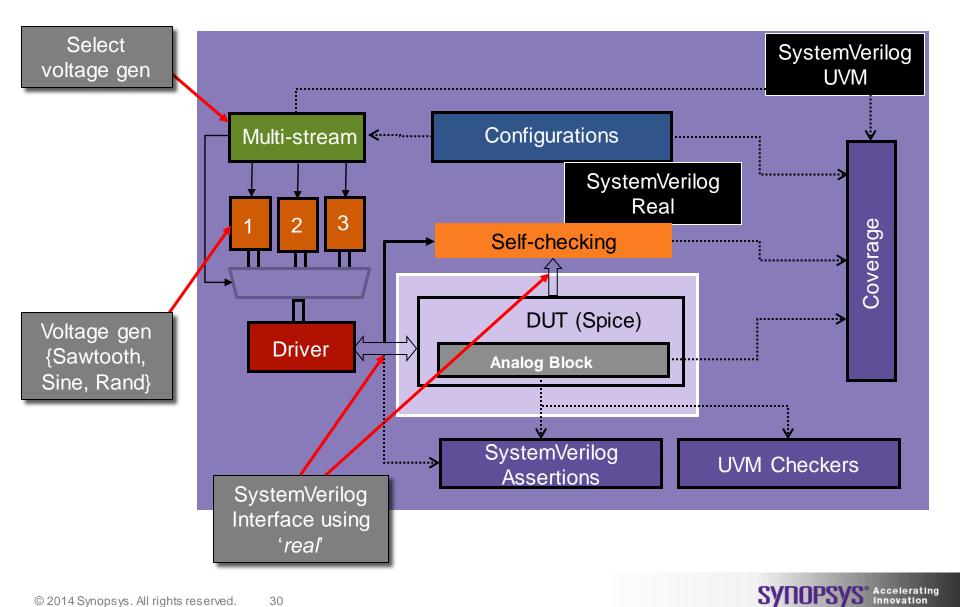

# VCS AMS – AMS Testbench

Expanding UVM Methodology for Analog

**Rapid Development with Lower Risk**

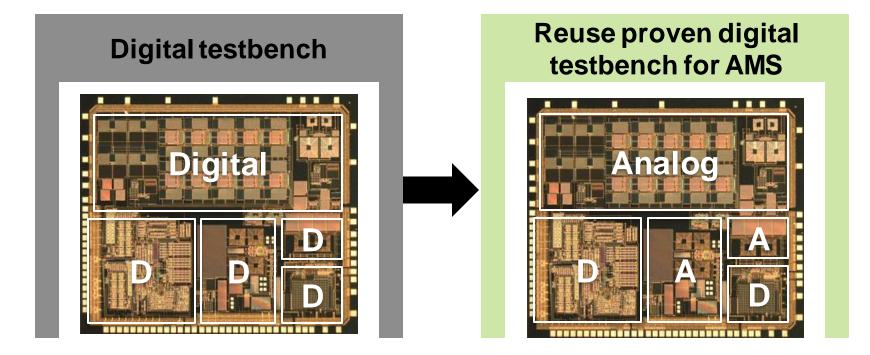

## VCS AMS – AMS Testbench

Digital Verification Techniques for Mixed-signal SoCs

#### **Metric-driven**

AMS assertions AMS constrained-random stimulus AMS checkers SystemVerilog real number modeling

### Self-checking

AMS testbench environment AMS source generators AMS functional coverage

Assertion

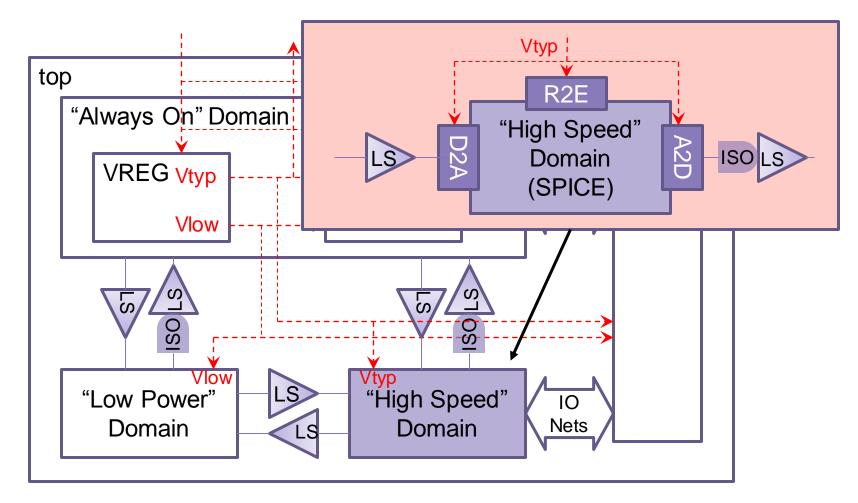

### **VCS AMS – Low Power Verification**

VCS AMS with Native Low Power

## **VCS AMS – Low Power Verification**

Introducing UPF-based Mixed-signal Verification

## VCS AMS – Low Power Verification

Static Checking with Circuit Check (CCK)

#### Missing Level Shifter Check high V domain Level Shifter #2 (Low -> High) mp21 out low V domain wina from 0 to hiah V n32 in inb swing from 0 to low\_V

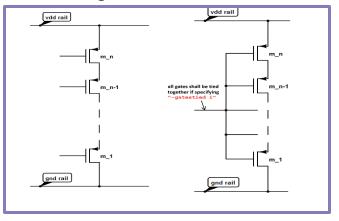

#### Stacking MOSFET between Rails

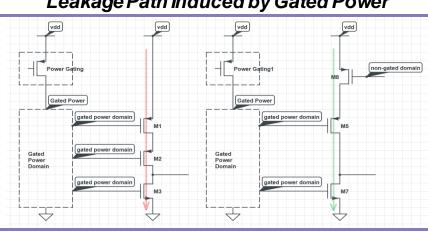

#### Leakage Path Induced by Gated Power

### VCS AMS – Summary

SYNOPSYS<sup>®</sup> Accelerating Innovation

### **AMS Testbench**

### Extending Digital Verification to Analog

Adiel Khan Helene Thibieroz

### Overview

**Technical features**

Demo

Q&A

SYNOPSYS<sup>®</sup> Accelerating Innovation

### **AMS Testbench**

### Overview

### What is AMS Testbench?

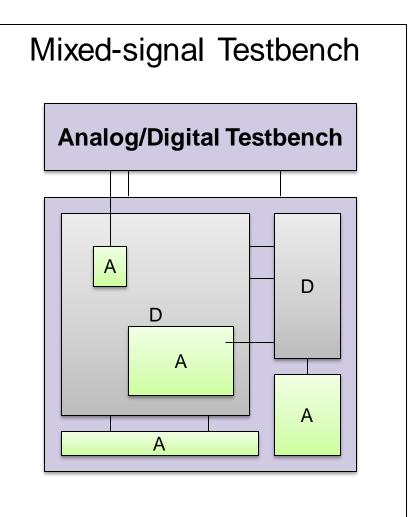

- AMS Testbench refers to Synopsys proprietary analog extensions to the UVM standard

- Extension of UVM-based techniques for mixed-signal verification

# Why AMS Testbench?

- Top-level verification required for mixed-signal SoCs

- Increasing IP Integration

- More complex interaction between analog and digital

AMS Testbench is Synopsys solution for mixed-signal coverage-driven verification methodology

analog block characterization is enough

- High risk of design re-spins

- Flow automation needed to include analog in full-chip verification planning strategy

.

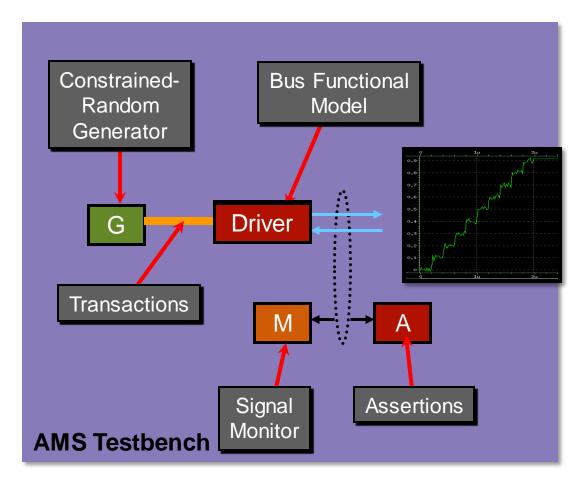

# **VCS AMS for Regression**

Digital Verification Techniques for Mixed-signal SoCs

#### **Metric-driven**

AMS assertions AMS constrained-random stimulus AMS checkers SystemVerilog real number modeling

### Self-checking

AMS Testbench environment AMS source generators AMS functional coverage

Assertion

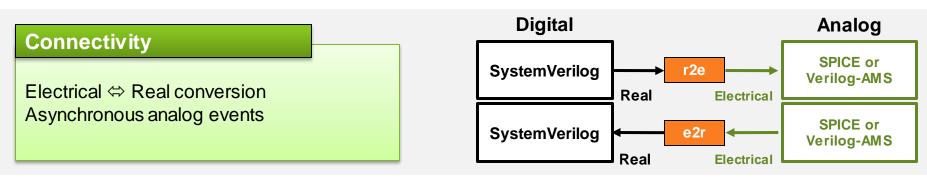

### **AMS Testbench**

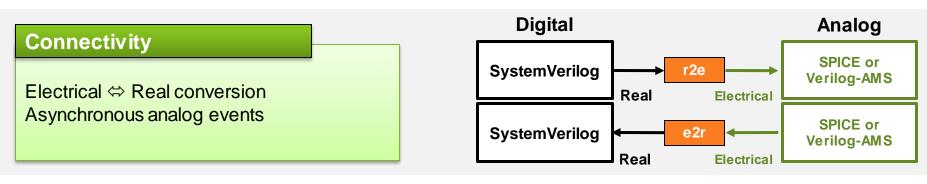

### Digital Verification Techniques - Connectivity

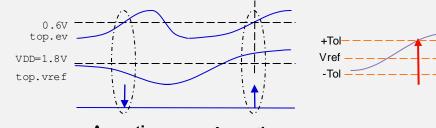

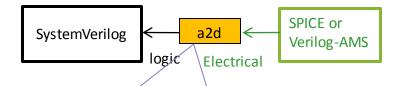

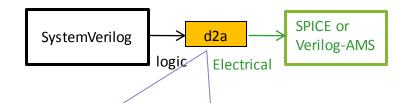

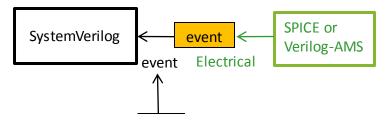

## Logic⇔Analog Conversion

Automatic insertion of a2d connect models between SystemVerilog and SPICE

User can redefine the threshold

### Example:

```

assign verilog_wire =

top.i1.i2.x1.clk;

initial begin

verilog_reg =

top.i1.i2.x1.strb;

```

Automatic insertion of d2a connect models between SystemVerilog and SPICE

User can redefine the threshold

#### Example:

```

reg rst_reg;

assign top.il.i2.x1.rst = rst_reg;

initial begin

...

rst_reg = 1'b0;

#5 rst_reg = 1'b1;

...

end

```

SYLIUF

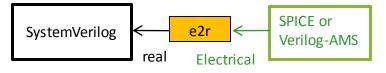

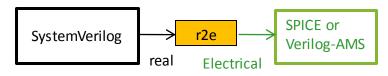

## **Real⇔Analog Conversion**

Easy XMR read access to internal analog signal voltage and current

```

$snps_get_volt(anode)

$snps_get_port_current(anode)

anode: full hierarchical analog node name

```

### Example:

```

real r;

```

always @(posedge clk)

```

r <=$snps_get_volt(top.i1.ctl);</pre>

```

Easy XMR write access to internal analog signal voltage.

\$snps\_force\_volt(anode,val|real)

\$snps\_release\_volt(anode)

anode: full hierarchical analog node name val/real: absolute value or real variable

### Example:

```

real r;

```

initial

```

$snps_force_volt(top.i1.ctl,0.0);

```

```

always @(posedge clk) begin

r <= r+0.1;

$snps_force_volt(top.i1.ctl,r);</pre>

```

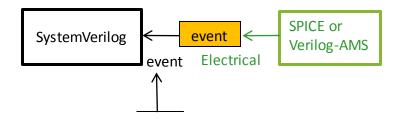

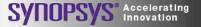

## **Asynchronous Analog Events**

\$snps\_cross(aexpr[,dir[,time

\_tol [,expr\_tol]]]);

aexpr. analog expression based on

system function

### Example:

always

```

@(snps_cross($snps_get_volt(t

op.i1.ctl)-0.6,1))

```

begin

```

$display("Signal ctl is raising

above 0.6V");

```

\$snps\_above(aexpr[,time\_tol

[,expr\_tol]]]);

*aexpr*: analog expression based on system function

### Example:

always

@(snps\_above(\$snps\_get\_volt(t

op.il.ctl)-0.6))

begin

\$display("Signal ctl is above

0.6V");

SYLIUF

### **AMS Testbench**

### Digital Verification Techniques – Assertions and Checkers

### **Immediate Assertions**

### **AMS Testbench Checkers**

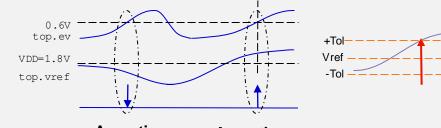

| Checkers                 |                                                                                                                                                 |                      |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| sv_ams_threshold_checker | Checks that analog signal<br>remains within a given high and<br>low threshold.<br>Can perform this check<br>synchronously or asynchronously     | High                 |

| sv_ams_stability_checker | Checks that analog signal<br>remains below or above a given<br>threshold.<br>Can perform this check<br>synchronously or asynchronously          | +Tol<br>Vref<br>-Tol |

| sv_ams_slew_checker      | Checks that analog signal<br>rises/falls with a given slew<br>rate(+/- tolerance).<br>Can perform this check<br>synchronously or asynchronously | dV/dt                |

| sv_ams_frequency_checker | Checks that analog signal frequency is within a given tolerance                                                                                 | Vmin Vmin            |

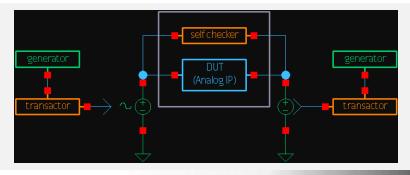

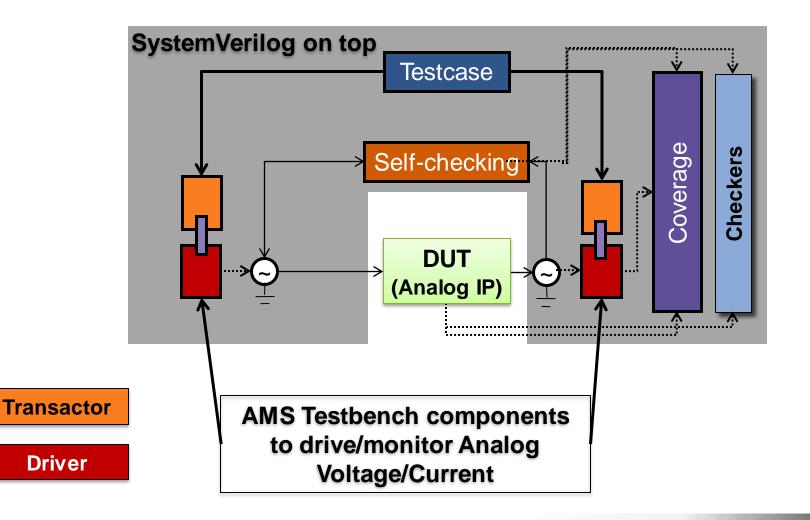

### **AMS Testbench**

### Digital Verification Techniques – Self-checking

### **AMS Testbench Architecture**

# **Analog IP Early Verification**

Possible Usage Before SoC Integration

S<sup>®</sup> Accelerating

SALINAZA

### **AMS Testbench Components**

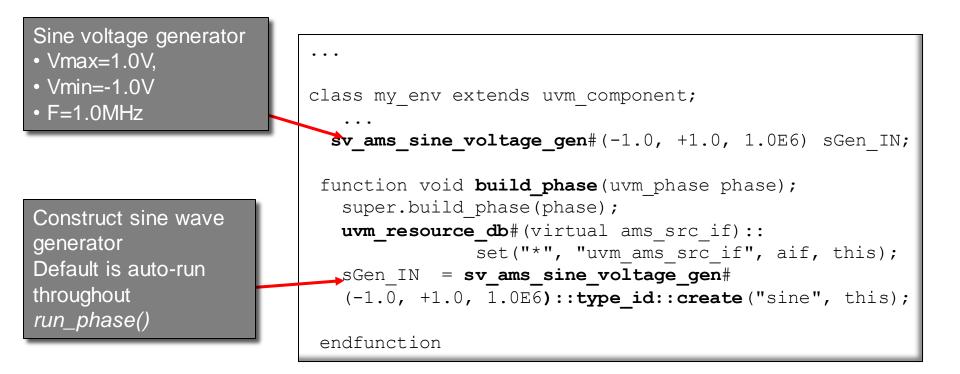

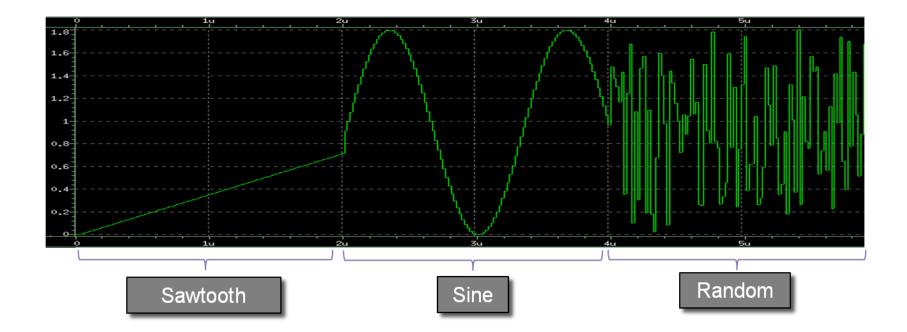

#### **AMS Testbench Generators**

- Sine voltage generator

- Sawtooth voltage generator

- Square voltage generator

- Fully customizable

#### **AMS Testbench Checkers**

SALIGE2

S<sup>®</sup> Accelerating Innovation

- Threshold

- Stability

- Window

- Slew Rate

- Frequency

### **AMS Testbench Generators**

| Checkers                    |                                                                                                       |                 |

|-----------------------------|-------------------------------------------------------------------------------------------------------|-----------------|

| class sv_ams_generic_src    | Provides base class<br>infrastructure for building voltage<br>generators                              |                 |

| sv_ams_sawtooth_voltage_gen | Base class aimed at generating<br>sawtooth waveforms with<br>minimum/maximum voltage and<br>frequency | Orong         Q |

| sv_ams_sine_voltage_gen     | Base class aimed at generating<br>sine waveforms with<br>minimum/maximum voltage and<br>frequency     |                 |

| sv_ams_rand_voltage_gen     | Base class aimed at generating<br>random waveforms with<br>minimum/maximum random<br>voltage sweep    | Group<br>1      |

### **AMS Testbench Generators**

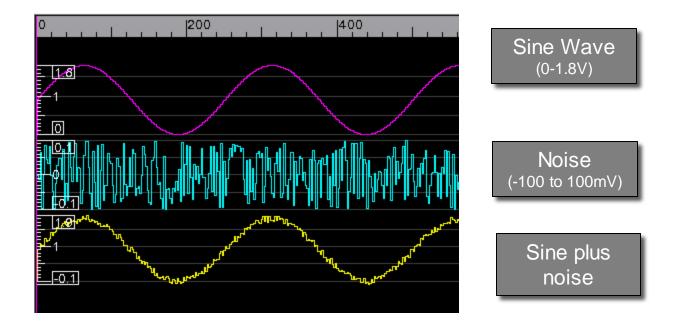

# **Example 1 - Noise Simulation**

Noise Injection into Mixed-signal Simulation

### Random Noise Injected Using Sine Source

SYNOPSYS<sup>®</sup> Accelerating Innovation

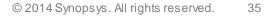

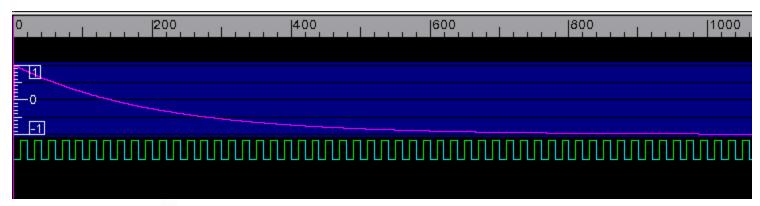

### **Example 2 - RC Voltage Generator**

Can Be Used Within Testbench to Drive Analog Nodes

### This custom source generator:

Vmin=-1V, VMax=1V, Freq=1MHz, RC=200ns

# **Example 3: Custom Voltage Generator**

Different Source Types Can Be Combined

SYNOPSYS<sup>®</sup> Accelerating Innovation

# **AMS Functional Coverage**

Analog and Digital Coverage in Same Verification Plan

| -                       | 1              |                |                        | Wend   | i;vdCover | age:1> |      |        |         |          |         |         |

|-------------------------|----------------|----------------|------------------------|--------|-----------|--------|------|--------|---------|----------|---------|---------|

| Eii                     | e <u>P</u> lan | Exclusion Viev | v Tools <u>W</u> indow | Help   |           |        |      |        |         | 1        |         | 12 -    |

|                         | 3 13           | 000            | × 🔒 🝙                  | 3 3    | 28        |        |      |        |         |          |         | -       |

| C                       | ovDetail       |                |                        |        |           |        |      |        |         |          | 18      | - 0     |

| •                       | Cover G        | roup item      | *                      | Score  |           | т      | U    | Goal   | Weight  | AtLeast  | Perinst | Overlap |

| 🗄 🚰 tb::ana_cov::cg_vin |                |                |                        | 52.78% | 67        | 36     | 100% | 1      | 1       | 0        | 1       |         |

| 🚾 cp_vi                 |                |                |                        | 1      | 93.75%    | 16     | 1    | 100%   | 1       | 1        |         | 1       |

| - 💁 cp_vmax             |                |                |                        |        | 33.33%    | З      | 2    | 100%   | 1       | 1        |         | 1       |

|                         |                | CC .           |                        |        | 31.25%    | 48     | 33   | 100%   | 1       | 1        |         |         |

| •                       |                | 10             | 11                     |        |           |        |      |        | 8       |          | ÷       |         |

| •                       | Status         | cp_vmax        | cp_vi                  |        |           |        | Туре | At Lea | st Size | Hit Coun | t       |         |

|                         | ~              | VNOM           | R_0_1                  |        |           |        | Auto |        | 1 1     |          | 6       |         |

|                         | 4              | VNOM           | R_1_2                  |        |           |        | Auto |        | 1 1     |          | 7       |         |

|                         | 1              | VNOM           | R 2 3                  |        |           |        | Auto |        | 1 1     |          | 3       |         |

By clearly referencing both analog and digital coverage groups, both domains can be verified together

SYNOPSYS<sup>®</sup> Accelerating Innovation

# **AMS Testbench - Summary**

# Functional verification methodology for mixed-signal SoC

- Extends SystemVerilog Testbench Environment to mixed-signal domain

- Provide mixed-signal coverage in SystemVerilog testbench

UVM

# **VCS AMS in STMicroelectronics**

#### **Pierluigi Daglio**

AMS Design Verification Flows Manager SPA - TR&D Smart Power Design Enablement

#### Mauro Scandiuzzo

Field Application Engineer AMS & IPG Marketing & Applications

DVCon Europe - Munich 14<sup>th</sup> October 2014

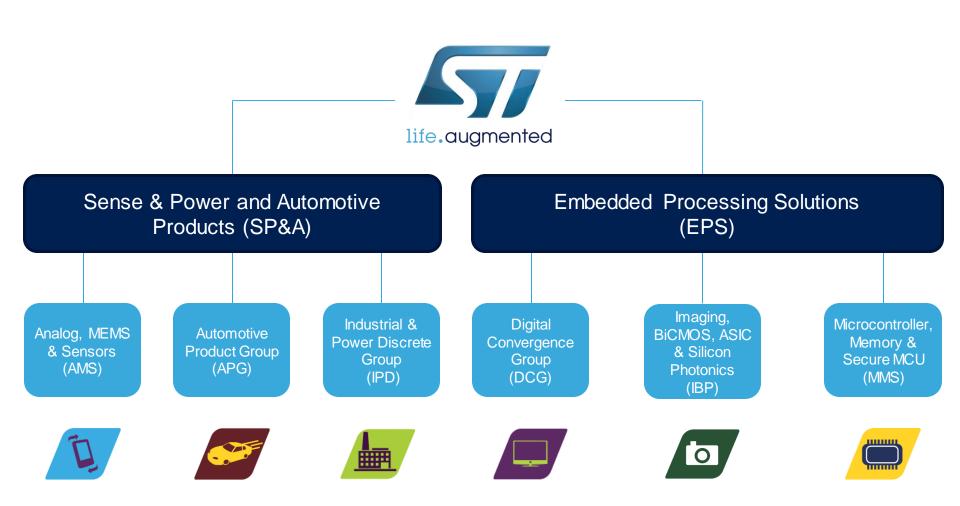

#### Outline 41

- STMicroelectronics Product Segments

- STMicroelectronics Analog/Mixed-Signal Scenario

- Verification flow and purpose

- The application

- Design and process

- Usage of Unique VCS AMS Features for Superior Productivity

- Assertions

- Save and Restore

#### Conclusions

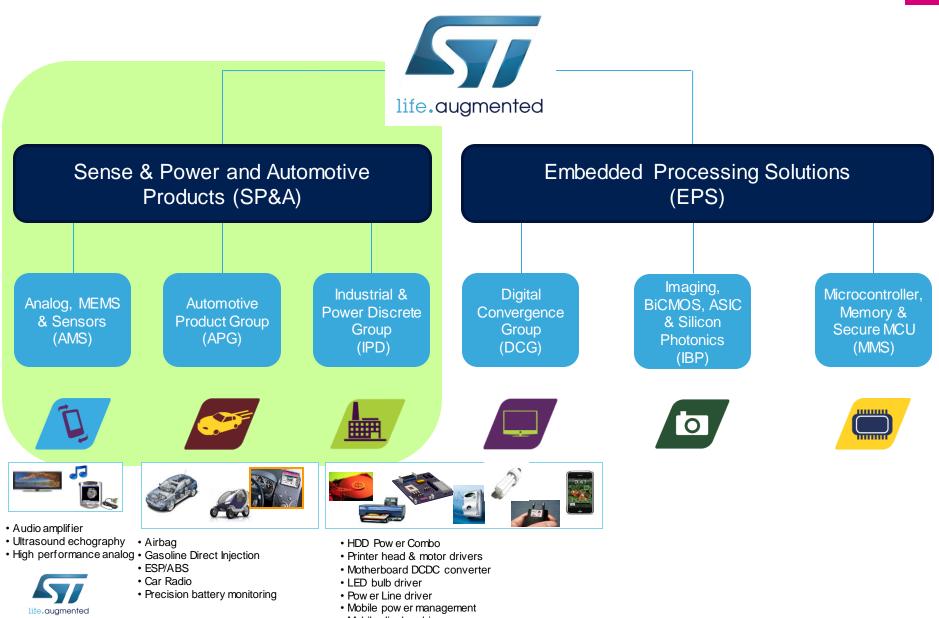

### Product Segments 42

### **Smart Power Product Segments**

Mobile display drivers

43

#### **Smart Power Application Fields**

by Technology Platform Segment

5

life.gugmented

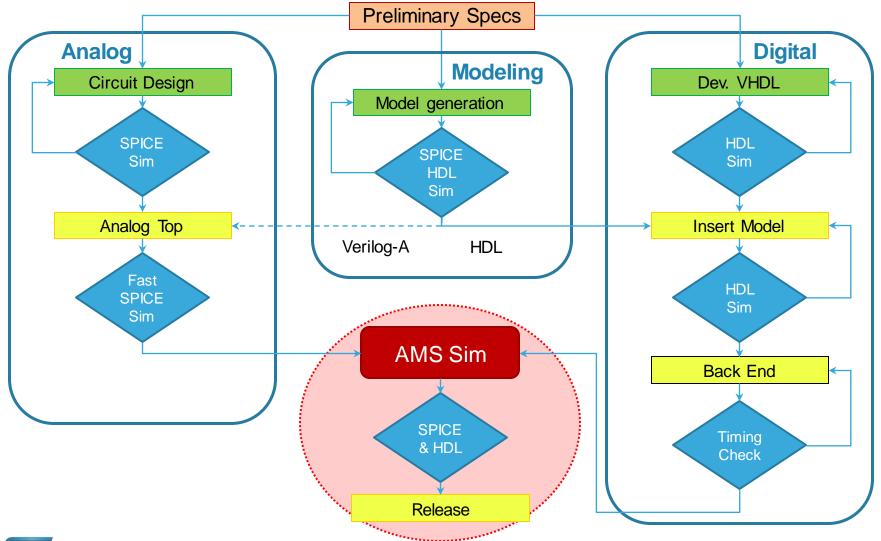

# ST Analog/Mixed-Signal Scenario

Simulation and verification of large IPs and macro-cells

- Transistor-level simulation

- Static and dynamic electrical rule checks (ERC)

- Safe operating area (SOA)

- Analog behavioral languages (Verilog-A)

- Simulation and verification of A/M-S systems

- System-level analog/digital co-simulation

- Digital test benches

- Fast and reliable simulation (speed & accuracy)

- HDL languages and analog behavioral languages

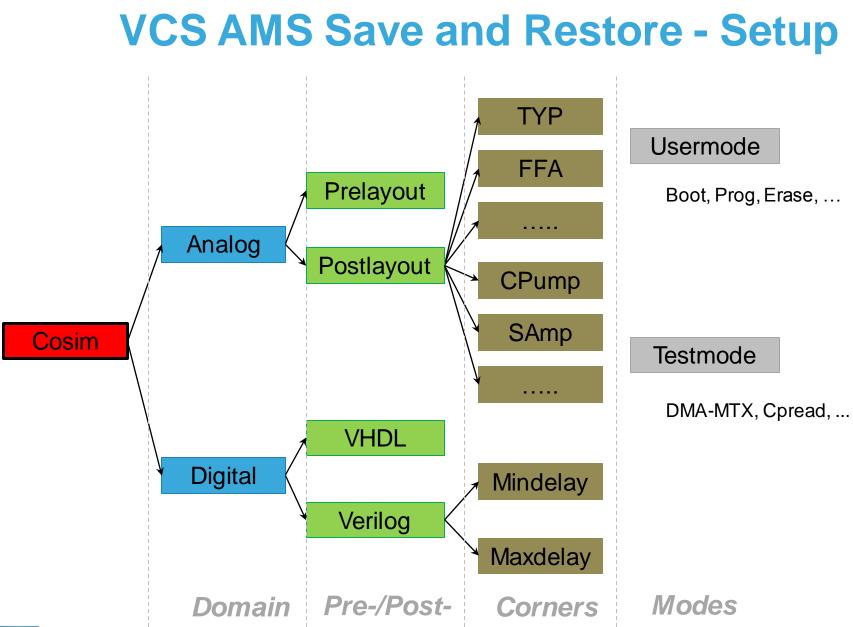

### AMS Verification Flow

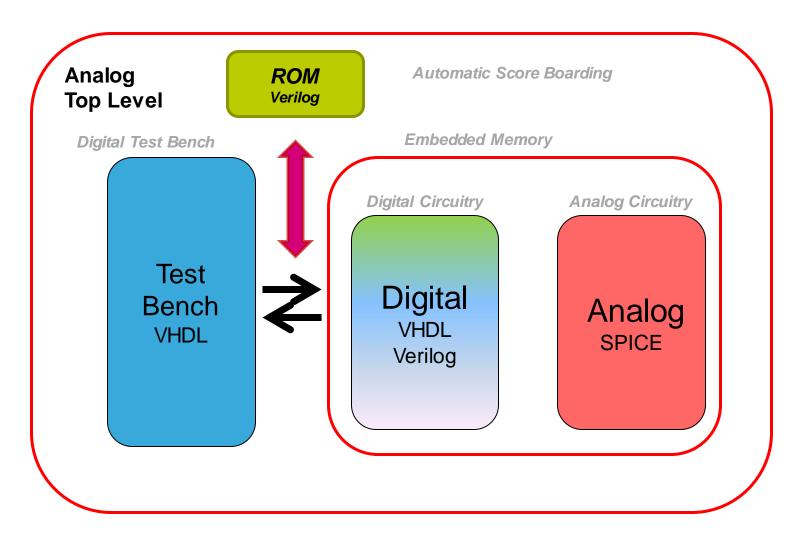

# **AMS Verification Purpose**

Purpose: Verify complex designs at top-level both with digital and analog parts

• It is possible to verify complex designs mixing among ...

#### netlist configurations

- *digital*: VHDL or Verilog post synthesis

- <u>analog</u>: pre-layout or post-layout (trade-off simulation time)

#### operation conditions

- *digital*: for Verilog (min & max delay)

- <u>analog</u>: TYP, SSA, FFA, ....

#### modes

- <u>Usermode</u>: boot, read, erase, prog with algorithm, ... (user set of operations)

- <u>Testmode</u>: DMA MTX\_CELL, DMA REF\_CELL, Erase Reference matrix (IP validation)

# **AMS Verification - The Application**

# **AMS Verification Design and Process**

#### **Design Complexity**

- Memory Size 136KB Single Module

- Organized into 3\*32KB-sector, 5\*8KB and 1\*TF sector (8KB)

- Double Voltage Supply

- Analog supply: 1.62V-3.6V

- Digital supply: 1.08V-1.32V

- x32-bit Reading (internally, 32b + 1b Redundancy) and Writing (internally, 2 bits by 2)

- Embedded Program/Erase Code

#### Technology

- Low Power: Double Poly, Triple-Well

- Differential Oxide: GO1-LV, GO2-MV, HV

- Low Power Consumption

- MIM Capacitors

- High Resistivity Poly1 Resistors Available

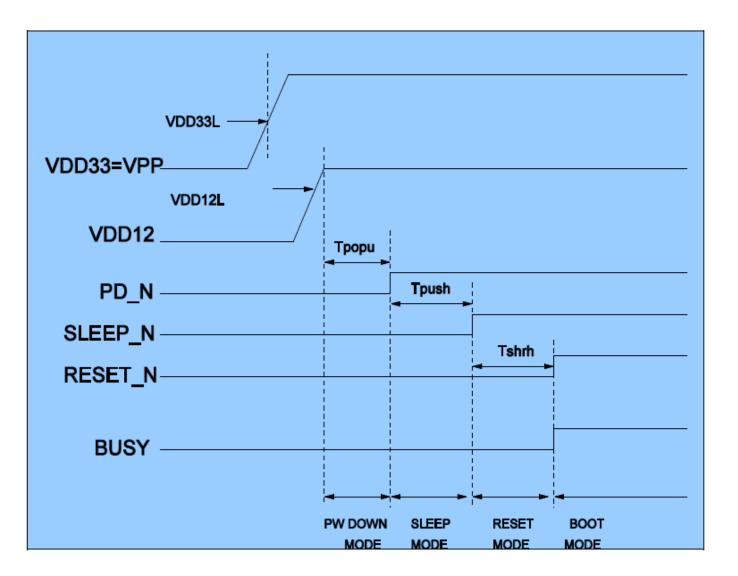

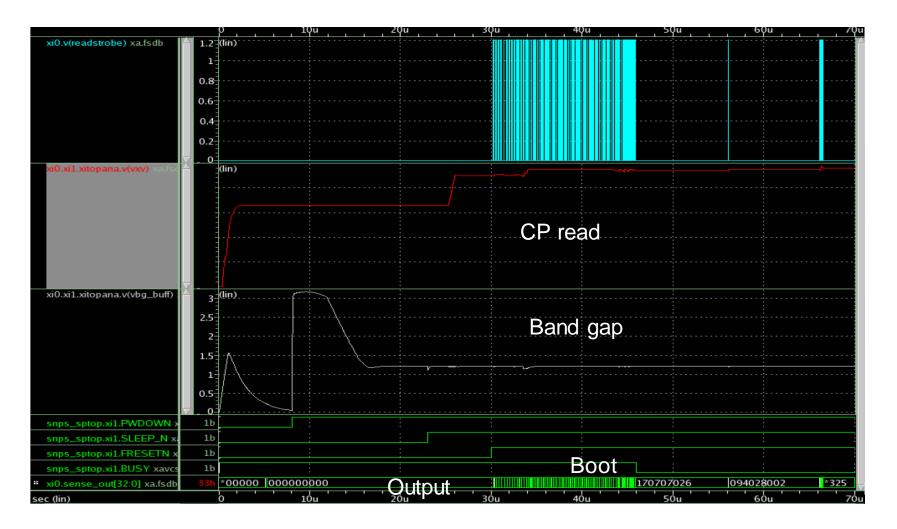

### Power-up Sequence 11

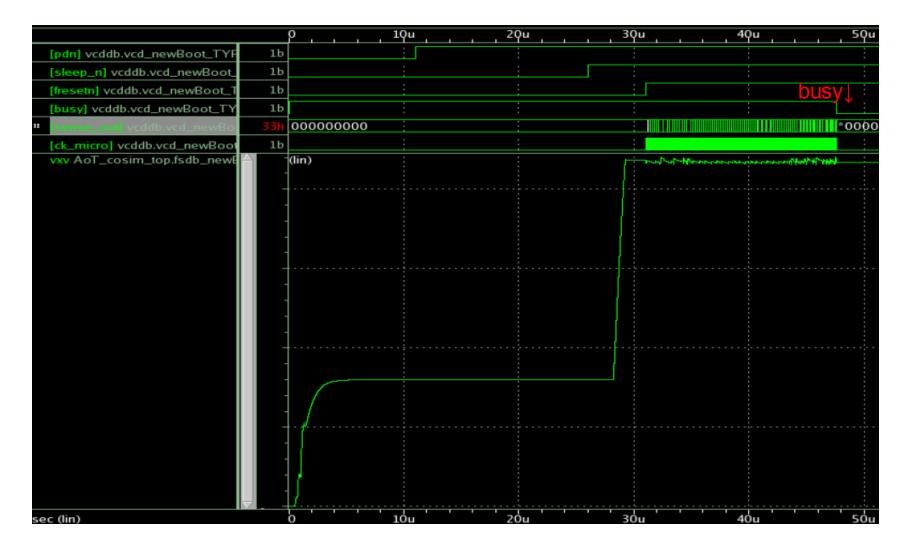

### Waveforms - Boot Operations 12

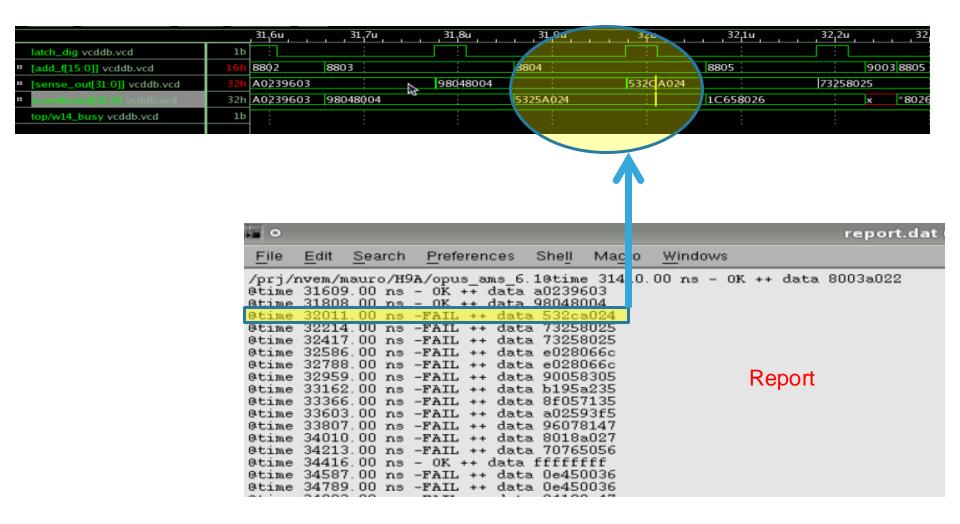

# Boot Trimming - Sense Out Details 13

|                                  |          | <b>0</b>                                                     | 1Qu , ,          | 2Qu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 30u         |                                   | Qu       | _ 50u               |

|----------------------------------|----------|--------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------------------------|----------|---------------------|

| top/w57_fresetn vc               | 1b       |                                                              |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |                                   |          |                     |

| top/w15_busy vcdd                | 1b       |                                                              |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |                                   |          |                     |

| " [sense_out[32:0]] v            | 33h      | 000000000                                                    |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |                                   |          | *0000               |

| <pre>" [add_f] vcddb.vcd_i</pre> | 16h      | FFFF                                                         |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |                                   |          | FFFF                |

| [latch_dig] vcddb.ve             | 1b       |                                                              |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |                                   |          |                     |

| " [trim_iref] vcddb.vci          | 4h       | F                                                            |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |                                   |          |                     |

| Itrim_latch] vcddb.v             | 6h       | 00                                                           |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             | 37                                |          | 07                  |

| Itrim_neg] vcddb.vd              | 3h       | 7                                                            |                  | and the second sec |             |                                   |          |                     |

| " [trim_osc] vcddb.vd            | 4h       | F                                                            |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |                                   | 7        |                     |

| " [trim_osc_vxr] vcdo            | 4h       | F                                                            |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |                                   | 0        |                     |

| " [trim_vbl] vcddb.vcd           | 4h       | F                                                            |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             | ````````````````````````````````` |          |                     |

| " [trim_vo] vcddb.vcd            | 3h       | 7                                                            |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |                                   |          |                     |

| " [trim_vreg] vcddb.v            | 3h       | 7                                                            |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |                                   |          |                     |

| " [trim_vxr] vcddb.vco           | 6h       | 23                                                           |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |                                   |          |                     |

| " [trim_xv] vcddb.vcd            | 4h       | 7                                                            |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             | F                                 | : `      |                     |

| " [trim_eq] vcddb.vcd            | 8h       | 00                                                           |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |                                   | 30       |                     |

| " [trim_ev] vcddb.vcd            | 6h       | co                                                           |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |                                   | 17       | 07                  |

|                                  |          |                                                              |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |                                   |          |                     |

|                                  |          |                                                              | 1,3u , , , , , ; | 31,4u , 31,5u                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | , , , 31,6u | 31,7u                             | 31,8u 31 | . <sub>1</sub> 9u _ |

| latch_dig vcddb.vd               |          | 1b                                                           |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |                                   |          |                     |

| [add_f[15:0]] vcdd               |          | 16h         8800         8801           32h         94028002 |                  | 8802<br>003A022                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | A0239603    | 8803                              | 8804     |                     |

| [sense_out[31:0]]                | vcaab.vc | 3211 94028002                                                | 6                | 005A022                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | A0239603    | 9                                 | 8048004  |                     |

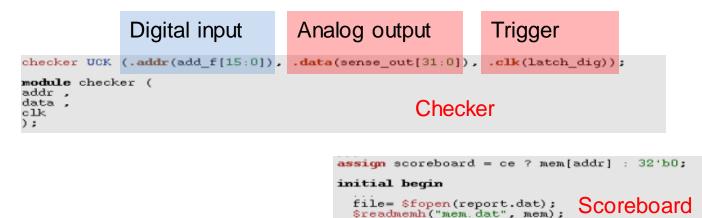

### VCS AMS Automatic Checks w/Assertions 14

end

### Assertions Simulation Results 15

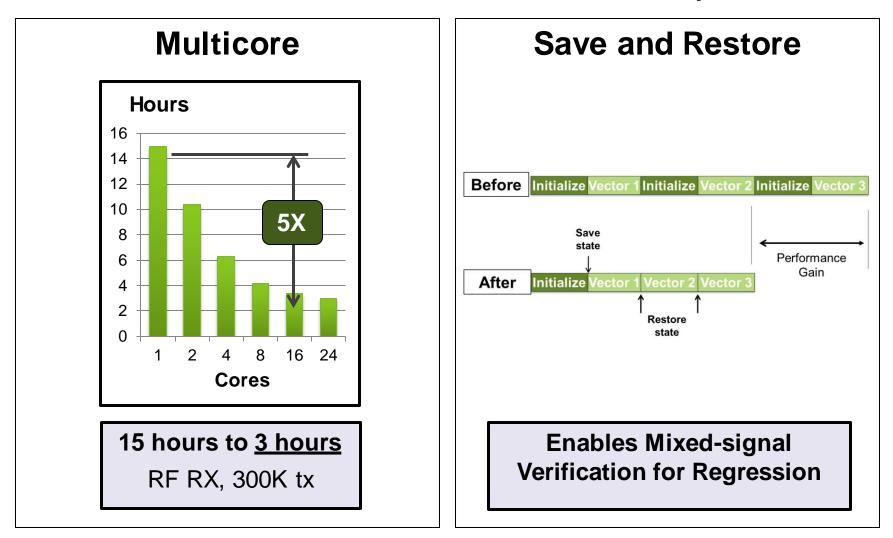

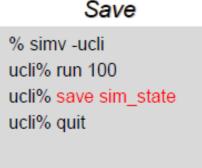

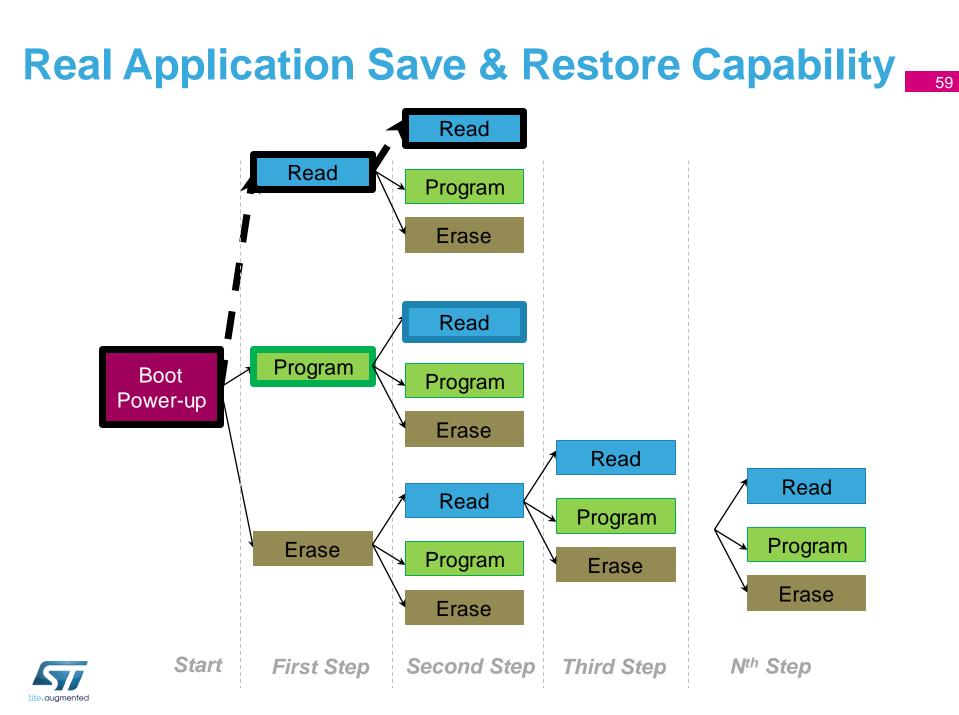

# VCS AMS Save and Restore Capability

- A "memory image" of the simulation can be saved and restored at a later time

- At restore time, the netlist and the simulation set-up cannot be changed

- Typically used for running many functional simulations on the same design after the power-up

#### Restore

% simv -ucli ucli% restore sim\_state ucli% run

# VCS AMS Save and Restore Performance 57

- · Multiple runs can be executed by forcing a test selector variable

- A run is chosen by forcing the test selector via UCLI

100usec

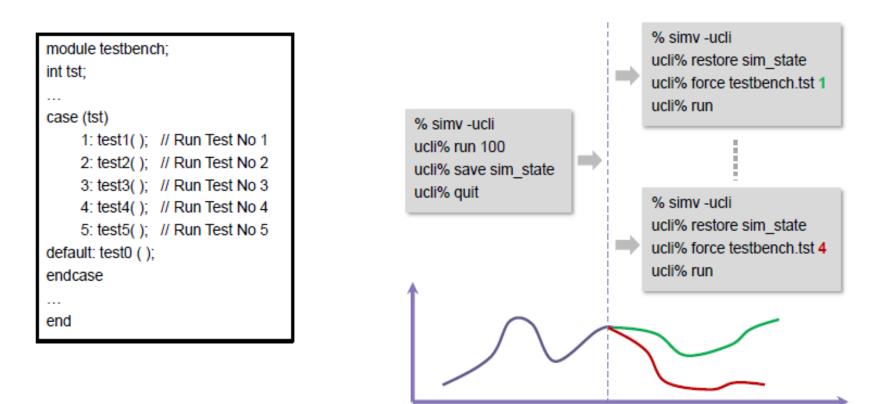

# Multi-Mode Approach w/Save and Restore

### Save and Restore - Boot & Multiple Read

```

REPORT "*** INFO: Boot User Mode";

fresetn <= '1';

WAIT FOR 1*UsrPeriod;

IF busy='1' THEN

Testbench

WAIT UNTIL busy='0';

REPORT "*** INFO: Boot Completed";

ELSE.

REPORT "*** ERROR: Busy has not started" SEVERITY ERROR;

END IF;

uRead(X"9003", i_data); -- read status

ASSERT (i data = c B6) REPORT "*** ERROR: Flash is not ready for read (SR: 0x" & hex image(i data) & ")" SEVERITY ERROR;

case for MultiTest validation

WAIT FOR 10 us;

case SEL is

when "01" => fREAD(X"0000",i data);

when "10" => fREAD(X"1FFF",i_data);

--when "11" => fREAD(X"0000", i data);

when others => fREAD(X"1111",i_data);

end case;

WAIT FOR 10 us;

case SEL is

when "01" => fREAD(X"0000",i_data);

when "10" => fREAD(X"1FFF",i_data);

--when "11" => fREAD(X"0000", i_data);

when others => fREAD(X"1111",i data);

end case;

run restore.csh

vcs restore.ucli

fRead(X"0000", i_data); -- just to trigger a read from Flash and chang

fRead(X"0004", i_data); -- read from Flash

fRead(X"0000", i_data); -- just to trigger a read from Flash and chang

fRead(X"0004", i_data); -- read from Flash

dump -file xavcsmx.vpd -type vpd

dump -autoflush on -fid VPDO

dump -add * -depth 4

WAIT FOR 5000+UsrPeriod; -- Off Time and Power Supply Ramping

restore save_start

force snps_sptop.xil.SEL 01

run 15us

Restore

save sim read1

Run

/simv -ucli -do vcs_restore.ucli -l simv_restore.loc

dump -file xavcsmx.vpd -type vpd

dump -autoflush on -fid VPDO

Restore 2

dump -add * -depth 4

restore sim read1

# Run

./simv -ucli -do vcs restore 2.ucli -l simv restore.log

force snps sptop.xil.SEL 10

run 20us

quit

```

# Save and Restore - Simulation Results

- Power up simulation takes 1h 30m

- Read operation takes 10m

- Power up + first read operation = 1h 40m

- ✓ With the Save and Restore capability in this case we save 1h 30m at the first operation then we save 1h 40m at the second operation, and so on...

- $\checkmark$  With more complex operations like program and erase we can save much more time

### Power-up & Multiple Read Operations 62

### Power-up Details 63

| v(vdd33) xa.fsdb                      | 0<br>3_((i             | 10u                                     | 2Qu     | <u>3</u> Qu | 4 <u>0u , 50</u> u |

|---------------------------------------|------------------------|-----------------------------------------|---------|-------------|--------------------|

|                                       | 2                      | Power s                                 | unnlies |             |                    |

| v(vdd12) xa.fsdb                      | 0.8                    |                                         | appnee  |             |                    |

| xi0.v(readstrobe) xa.fsdb             | 0.8<br>0.4             | in).                                    |         |             |                    |

| xi0.xi1.xitopana.v(vxv) xa.fsdb       |                        | in)                                     |         | CP read     |                    |

| xi0.xi1.xitopana.v(vbg_buff) xa       | 3-0i<br>2-<br>1-<br>0- | in)                                     | Ban     | d gap       |                    |

| snps_sptop.xi1.PWDOWN xav             | 1b                     |                                         |         |             | :                  |

| snps_sptop.xi1.SLEEP_N xav            | 1b                     |                                         |         |             | :                  |

| <pre>snps_sptop.xi1.FRESETN xav</pre> | 1b                     |                                         |         |             |                    |

| snps_sptop.xi1.BUSY xavcsm            | 1b                     |                                         |         |             |                    |

| xi0.sense_out[32:0] xa.fsdb           | 33h 0                  | 000000000000000000000000000000000000000 | Output  |             | 170707026          |

| • xi0.trim_eq[7:0] xa.fsdb            | 8h 0                   | 0                                       |         |             | 30                 |

| xi0.trim_ev[7:0] xa.fsdb              | 8h 0                   | 0                                       |         |             | 17                 |

| • xi0.trim_iref[3:0] xa.fsdb          | 4h F                   |                                         |         | 7           |                    |

| xi0.trim_neg[2:0] xa.fsdb             | 3h 7                   |                                         |         | 4           |                    |

| xi0.trim_osc[3:0] xa.fsdb             | 4h F                   |                                         |         |             | C                  |

| xi0.trim_osc_vxr[3:0] xa.fsdb         | 4h F                   |                                         | Trimmin |             | 6                  |

| xi0.trim_vbl[3:0] xa.fsdb             | 4h F                   |                                         |         | y           |                    |

| <pre>xi0.trim_vo[2:0] xa.fsdb</pre>   | 3h 7                   |                                         |         | 3           |                    |

| • xi0.trim_vreg[2:0] xa.fsdb          | 3h 7                   |                                         |         |             |                    |

| • xi0.trim_vxr[5:0] xa.fsdb           | 6h 2                   | 3                                       |         |             |                    |

| " xi0.trim_vxv[3:0] xa.fsdb           | 4h 7                   |                                         |         |             |                    |

| sec (lin)                             | 0                      | 10u                                     | 20u     | 30u         | 40u 50u            |

### First Read Operation After Boot 64

|                                                                  |                     | 56.05u   | 56,1u     | 56.15u | 56 <sub>1</sub> 2u |

|------------------------------------------------------------------|---------------------|----------|-----------|--------|--------------------|

| xi0.v(readstrobe) xa.fsdb                                        | 1.2 (lin)           |          |           |        |                    |

|                                                                  | 1                   |          |           |        |                    |

|                                                                  | 0.8                 |          |           |        |                    |

|                                                                  | 0.6                 |          |           |        |                    |

|                                                                  | 0.4                 |          |           |        |                    |

|                                                                  | -                   |          |           |        |                    |

|                                                                  | 0.2                 |          |           |        |                    |

| xi0.xi1.xitopana.v(vxv) xa.fsc                                   | <u>- 0</u><br>(lin) |          |           |        |                    |

|                                                                  |                     |          |           |        |                    |

|                                                                  |                     |          |           |        |                    |

|                                                                  |                     |          | CP r      | ead    |                    |

|                                                                  |                     |          |           |        |                    |

|                                                                  |                     |          |           |        |                    |

|                                                                  |                     |          |           |        |                    |

| xi0.xi1.xitopana.v(vbg_buff) :                                   |                     |          |           |        |                    |

|                                                                  |                     |          |           |        |                    |

|                                                                  | 2.5                 |          |           |        |                    |

|                                                                  | 2                   |          |           |        |                    |

|                                                                  | 1.5                 |          | Ban       | id gap |                    |

|                                                                  | 1                   |          |           |        |                    |

|                                                                  | 0.5                 |          |           |        |                    |

|                                                                  | v <u> </u>          |          |           |        |                    |

| snps_sptop.xi1.PWDOWN >                                          | 1b                  |          |           |        |                    |

| snps_sptop.xi1.SLEEP_N x                                         | 1b                  |          |           |        |                    |

| snps_sptop.xi1.FRESETN x                                         | 1b<br>1b            |          |           |        |                    |

| <pre>snps_sptop.xi1.BUSY xavcs xi0.sense_out[32:0] xa.fsdb</pre> | 33h 170707026       |          | 094028002 |        |                    |

| sec (lin)                                                        |                     | 56.05u 💦 | 56.1u     |        | 56.2u              |

### Five Further Reads After Save & Restore 65

|                                                     |                          | 65,8    | Bu e | 56u      | 66.2u       | 66,4u                                   | 66,6u       |

|-----------------------------------------------------|--------------------------|---------|------|----------|-------------|-----------------------------------------|-------------|

| xi0.v(readstrobe) xa.fsdb                           | 1.2 (lin                 | )       |      |          |             |                                         |             |

|                                                     | 1                        |         |      |          |             | ••••••••••••••••••••••••••••••••••••••• |             |

|                                                     | 0.8                      |         |      |          |             |                                         |             |

|                                                     | 0.6                      |         |      |          |             |                                         |             |

|                                                     |                          |         |      |          |             |                                         |             |

|                                                     | 0.4                      |         |      |          |             |                                         |             |

|                                                     | 0.2                      |         |      |          |             |                                         |             |

| xi0.xi1.xitopana.v(vxv) xa.fsc                      | ∑ <u>_ 0<sup>‡</sup></u> |         |      |          |             |                                         |             |

|                                                     |                          | ·       |      |          |             |                                         |             |

|                                                     |                          |         |      |          |             |                                         |             |

|                                                     |                          |         |      | ······C  | P read      |                                         |             |

|                                                     |                          |         |      |          |             |                                         |             |

|                                                     |                          |         |      |          |             |                                         |             |

|                                                     |                          |         |      |          |             |                                         |             |

|                                                     |                          |         |      |          |             |                                         |             |

| xi0.xi1.xitopana.v(vbg_buff) :                      | 3- <sup>((in</sup>       | )       |      |          |             |                                         |             |

|                                                     | 2.5                      |         |      |          |             |                                         |             |

|                                                     | 2                        |         |      |          |             |                                         |             |

|                                                     |                          |         |      |          | Band gap    |                                         |             |

|                                                     | 1.5                      |         |      |          |             |                                         |             |

|                                                     | 1                        |         |      |          |             |                                         |             |

|                                                     | 0.5                      |         |      |          |             |                                         |             |

|                                                     | 1.                       |         |      | <u> </u> |             |                                         |             |

| snps_sptop.xi1.PWDOWN x<br>snps_sptop.xi1.SLEEP_N x | 1b<br>1b                 |         |      |          |             |                                         |             |

| snps_sptop.xi1.SLEEP_N x                            | 1b<br>1b                 |         |      |          |             |                                         |             |

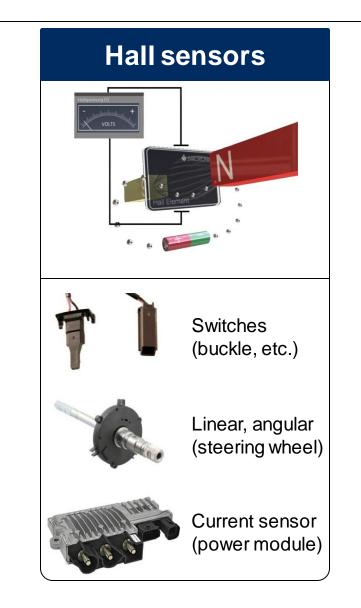

| snps_sptop.xi1.BUSY xavcs                           | 1b                       |         |      |          |             |                                         |             |