## Equivalence Validation of Analog Behavioral Models

Manish Kumar Karna\*, Hardik Parekh\*, Mohit Jain\*, Atul Pandey+, Sandeep Mittal++ \*ST Microelectronics Pvt. Ltd., Greater Noida, India (manish.karna, hardik.parekh, mohit-jain.crd)@st.com +Mentor Graphics, Munich, Germany, ++Mentor Graphics, Noida, India {atul\_pandey, sandeep\_mittal}@mentor.com

#### Overview

- Behavioral Models are used in verification to increase coverage on mixed signal SoCs.

- Behavioral abstract models capture functional features of analog behavior in event-driven HDL languages.

- Behavioral Models are orders of magnitude faster than simulating SPICE view of analog IP

- o Critical to ensure equivalence between behavioral models and implementation (SPICE)

#### Framework components

#### **Analog behavioral model validation Environment**

- Specification document for models

- Verification Plan

- TestPlan

- Verification environment

- Equivalence validation component(EqVC)

- Equivalence check Report

- Exception Waivers

# Validation Exception/Waivers Component

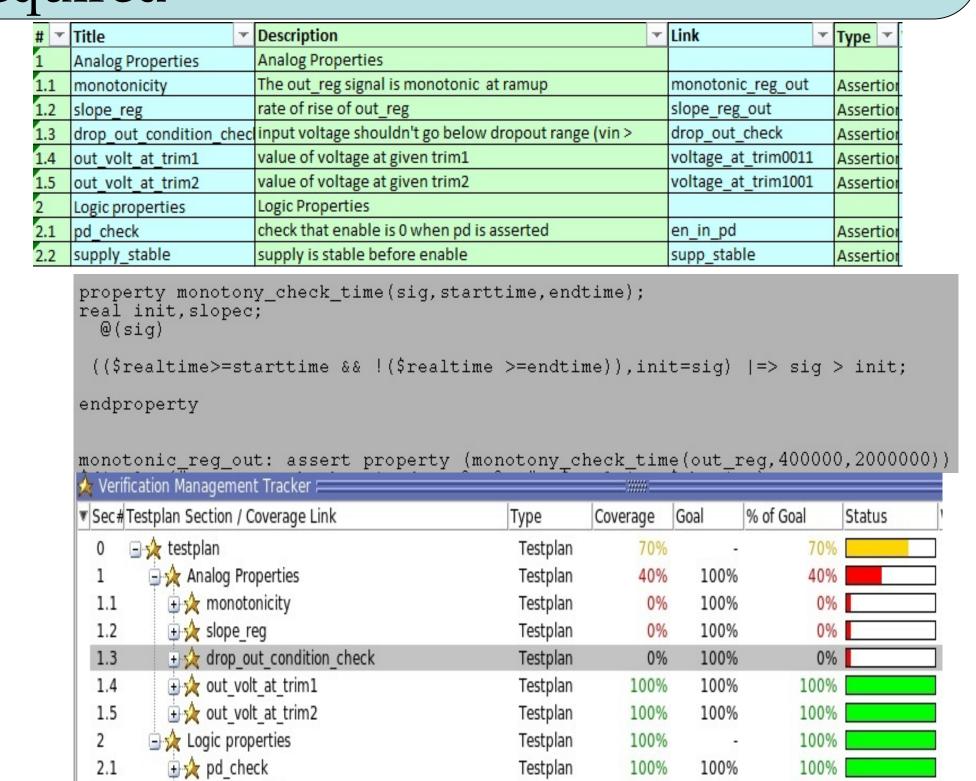

#### Verification Planning and TestPlan

Verification Plan document contains:

- List of features of the analog behavioral model to be validated.

- A list of test to verify those features.

- o To test each feature, a list of checks (coverage) are specified in TestPlan.

- Equivalence Validation method used and data organization.

- o Criterion for validation closure.

- Method of Review, Reporting and Exception handling.

BAIS\_UNIT

Naveforms to compare Analog

12/3/2013 Time

BIAS\_UNIT

eq\_check\_hdmi/bmode

I\_BIAS\_UNIT:compout1v0

Digital signal name

I\_BIAS\_UNIT:vbgout

**BMODE**

hparikh

I\_BIAS\_UNIT:xicalib:ipoly50ua1 I\_BIAS\_UNIT:xicalib:ipoly50ua1

:I\_BIAS\_UNIT:xicalib:irext45ua1:I\_BIAS\_UNIT:xicalib:irext45u

analog\_simulation\_wdb BIAS\_UNIT\_Top\_Simulation\_Analog.wdb

BIAS UNIT:compout1v0

I\_BIAS\_UNIT:xicalib:ipoly50ua1

BIAS UNIT:xicalib:irext45ua1

I\_BIAS\_UNIT:vbgout

Digital voltage/curefDelay fixedthres start end xTol yTo

5.10E-05 20u

4.50E-05 5u

0.5 lower 0.2 thre

Report

voltage

current

current

testDelay 0

250.0000u

11:34:21

1 \*acceptable

1 \*acceptable

2 \* time delay effect.OK

2 \* time delay effect.OK

#### **Equivalence Validation Components**

- Simulation environment consist of Testbench, DUV and equivalence components (EqVC)

- Same test is applied to Model and netlist DUV

- EqVC chosen according to skillset and effort

| Quick Start                                                                                                                          | Assertion based<br>Verification                                                                                                                                          | Advanced<br>Verification                                                                                        | Efficient                                 |

|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| <ul> <li>Waveform         compare</li> <li>Low setup         effort</li> <li>Sufficient for         simple         models</li> </ul> | <ul> <li>Assertion based         Property Checkers         and Monitors         Medium setup         effort         Library of         checkers/monitors     </li> </ul> | <ul> <li>UVM-AMS</li> <li>Advanced verification expertise</li> <li>Reusable verification environment</li> </ul> | Wave Compare<br>+ Assertions<br>+ UVM-AMS |

<u>→</u> ★ supply\_stable

### Verification closure, Report and Review

- Results generated from simulations for all tests and captured in eqVCs are compared to TestPlan to generate PASS/FAIL report

- The difference arise from electrical effects inbuilt in SPICE views and abstracted in behavioral model

- Exception/Mismatches are reviewed and "Waiver" issued and recorded in closure report

Figure 2: Equivalence validation component (EqVC) types

## Waveform comparison method Continuous waveform comparison Quick setup time Works for both AoT and DoT verification TestPlan specifies signals to compare and tolerances Report generated and exception/waivers captured #Compact report generated by report\_gen.tcl script

design unit name

testname name

verification directory

I\_BIAS\_UNIT:compout1v0

Analog signal name

I\_BIAS\_UNIT:vbgout

user name

## Assertion based verification method

- A Library of SystemVerilog Assertions

- Assertions work on both Model and netlist

- Expertise in assertions language and ABV required

Testplan

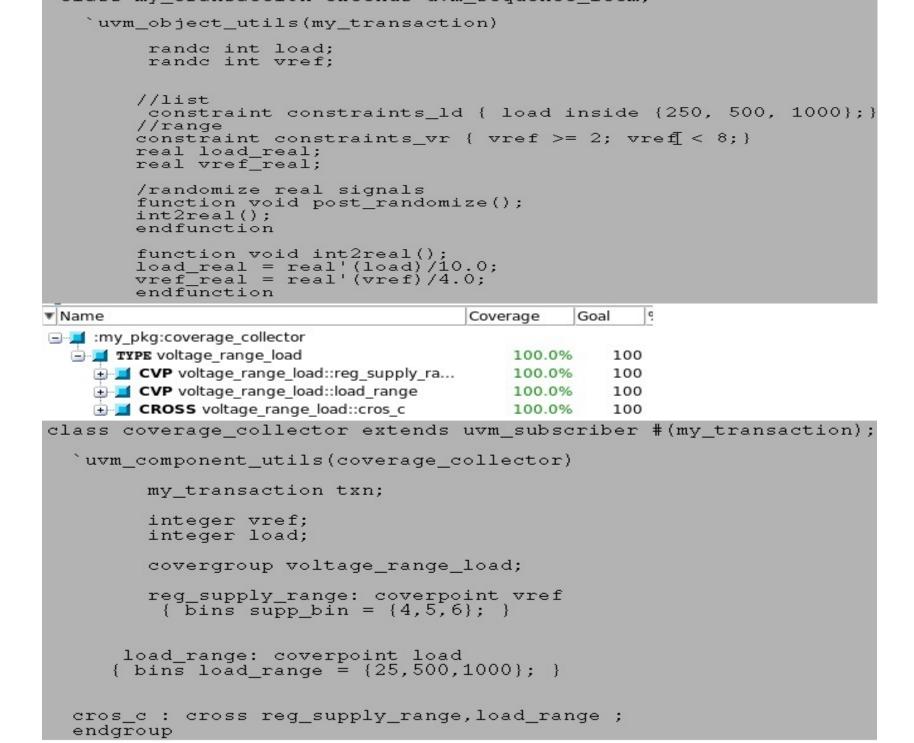

## Advanced Verification

- UVM constrained random stimulus for analog properties.

- Increased verification coverage

- Compatible with ABV