# Enriching UVM in SystemC with AMS extensions for randomization and functional coverage

Thilo Vörtler, Thomas Klotz, Karsten Einwich, Yao Li, Zhi Wang, Marie-Minerve Louërat, Jean-Paul Chaput, François Pêcheux, Ramy Iskander, Martin Barnasconi

- Motivation

- UVM for SystemC and SystemC-AMS

- Randomization

- Coverage

- Summary

- Motivation

- UVM for SystemC and SystemC-AMS

- Randomization

- Coverage

- Summary

## Motivation (1)

UVM is currently being available for SystemC-AMS

The UVM methodology relies heavily on the use of randomization of sequences and functional coverage collection

Randomization and coverage APIs are not defined in UVM but inherited from System Verilog

## Motivation (2)

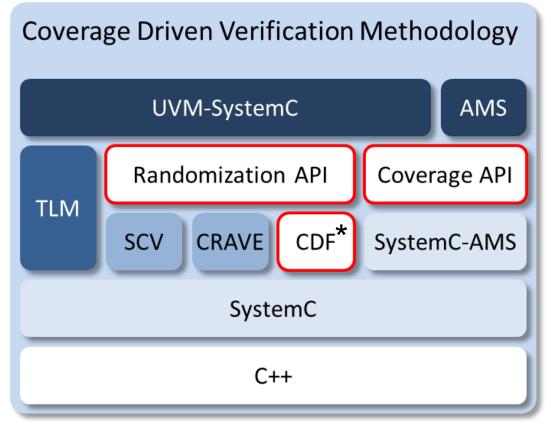

→ Goal: Definition of randomization and coverage API for UVM in SystemC/AMS

\*continuous distribution functions

- Motivation

- UVM for SystemC and SystemC-AMS

- Randomization

- Coverage

- Summary

## **UVM for SystemC-AMS**

Requirements for randomization and coverage API:

- Current available SystemC libraries don't offer a simple API that is familiar to UVM users

- Extensions for dealing with real values needed for AMS verification are needed

→ Proposal for an SCV extension (scvx) for further standardization within Accellera

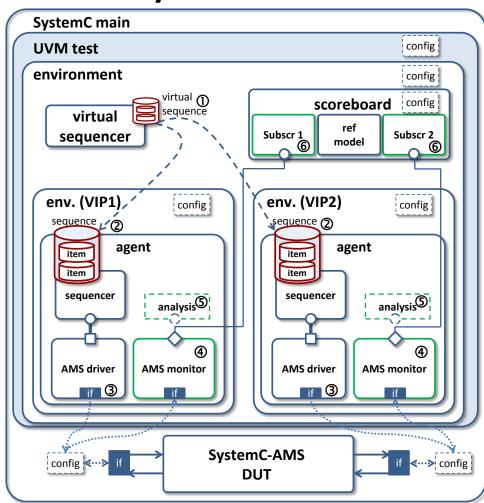

## UVM for SystemC/AMS

- Sequences that drive stimulus to the DUT are randomized

- Coverage is used in monitors and scoreboards to check the progress of the verification process

- Motivation

- UVM for SystemC and SystemC-AMS

- Randomization

- Coverage

- Summary

## Randomization (1)

#### Supported constructs (CRAVE 1.0 as backend)

| Functionality                           | SystemVerilog     | UVM-SystemC (scvx) |  |

|-----------------------------------------|-------------------|--------------------|--|

| Random variable declaration             | rand T            | scvx_rand <t></t>  |  |

| Enable or disable random variable       | rand_mode()       | rand_mode()        |  |

| Constraint block declaration            | constraint        | scvx_constraint    |  |

| Enable or disable constraint            | constraint_mode() | constraint_mode()  |  |

| Randomization container object          | -                 | scvx_rand_object   |  |

| Randomize method                        | randomize()       | randomize()        |  |

| Randomize method with inline constraint | randomize() with  | randomize_with( )  |  |

## Randomization (2)

```

1 class simplesum : public

scvx::scvx_rand_object

3

public :

5

scvx::scvx_rand< int > x, y, z ;

scvx::scvx_constraint c1, c2, c3;

simplesum( scvx::scvx_name name )

: x("x"), y("y"), z("z"),

c1("c1"), c2("c2"), c3("c3")

10

11

c1(z() == x() + y());

c2(x() == 5);

12

13

c3(y() > 0 & y() < 10);

14

void print_result() const

16

17

cout << name() << " : " << z << " == "

18

<< x << " + " << y << endl;

19

20 \rightarrow; \tag{// class simplesum}

```

```

21 int sc_main(int, char*[])

22

simplesum s("simplesum");

24

bool result = s.randomize();

25

if (result) s.print_result();

26 l

else cout << "No solution found." << endl;</pre>

s.c2.constraint_mode( false );

result = s.randomize_with( s.x() == 10 );

29

30

if (result) s.print_result();

else cout << "No solution found." << endl;</pre>

33 l

s.y.rand_mode( false );

34

result = s.randomize();

35

if (result) s.print_result();

36 l

37 l

else cout << "No solution found." << endl;</pre>

38

return 0;

39 | }

```

## Randomization (3)

Console output:

```

$ ./simplesum.exe

constraint c1 registered.

constraint c2 registered.

constraint c3 registered.

simplesum: 13 == 5 + 8

constraint c2 disabled.

in-line constraint ci_0 applied (disabled after use)

simplesum: 13 == 10 + 3

random variable 'y' made inactive (value remains 3).

simplesum: 33556493 == 33556490 + 3

```

#### Randomization (4)

Analog extensions (C++11 based solver)

| Distribution function                               | UVM-SystemC (scvx)                             |

|-----------------------------------------------------|------------------------------------------------|

| Normal distribution                                 | scvx_normal_distribution                       |

| Uniform distribution                                | scvx_uniform_real_distribution                 |

| Bernoulli distribution                              | scvx_bernoulli_distribution                    |

| Piece-wise linear probability distribution function | scvx_piecewise_linear_probability_distribution |

| Discretized probability distribution function       | scvx_discrete_probability_distribution         |

```

scvx::scvx_rand<real> a

a.set_distribution( dist_type(dist_params) );

```

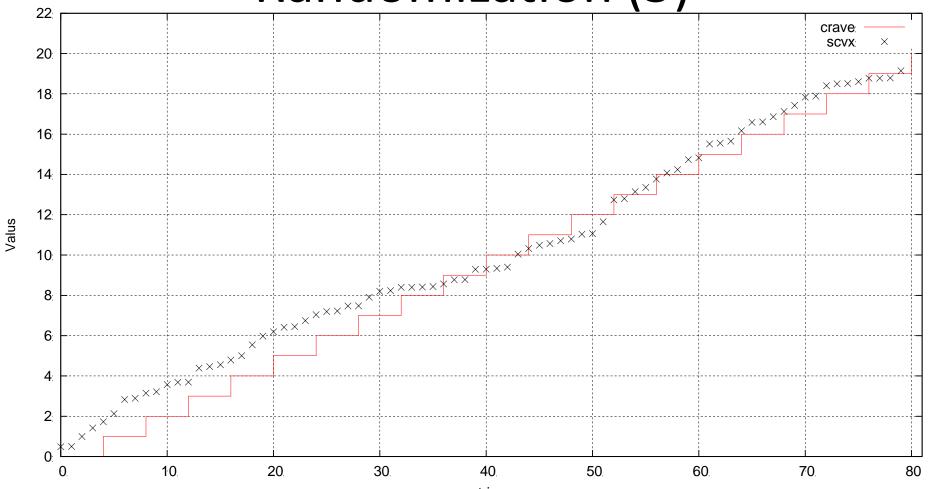

Randomization (5)

Uniform distribution example using scvx\_uniform\_real\_distribution

- Motivation

- UVM for SystemC and SystemC-AMS

- Randomization

- Coverage

- Summary

# Coverage (1)

#### Supported features

| Functionality       | SystemVerilog | UVM-SystemC (scvx) |

|---------------------|---------------|--------------------|

| Coverage model      | covergroup    | scvx_covergroup    |

| Coverage points     | coverpoint    | scvx_coverpoint    |

| Coverage state bins | bins          | bins()             |

| Illegal bins        | illegal_bins  | illegal_bins()     |

| Ignore bins         | ignore_bins   | ignore_bins()      |

| Coverage options    | option        | option             |

## Coverage (2)

```

class cg: public scvx::scvx_covergroup

2

{

3

public:

scvx::scvx_coverpoint cp_m;

scvx::scvx_coverpoint cp_n;

cg( scvx::scvx_name name, int& m, int& n)

: cp_m( "cp_m", m ),

cp_n( "cp_n", n )

10

option.auto_bin_max = 16;

cp_m.bins("bin_a") =

11

12

scvx::list_of(4, 0, 1, 2, 3);

13

cp_m.bins("bin_b", scvx::SINGLE_BIN) =

scvx::list_of(4, 4, 5, 6, 7);

14

15

cp_m.ignore_bins("ignore_bins") = 6;

16

cp_n.ignore_bins("ignore_bins") = 13;

17

18

};

```

```

int sc_main(int, char*[])

19

20

21

int m; // variable to be covered

int n; // variable to be covered

22

23

int stimuli_m[] =

{ 3, 5, 6, 5, 3, 6, 5, 5, 3, 3 };

24

int stimuli_n[] =

25

{ 13, 1, 6, 3, 16, 12, 8, 3, 13, 3 };

26

cg cg_inst("cg_inst", m, n);

27

28

for ( int i = 0; i < 10; i++ )

29

30

m = stimuli m[i]:

31

n = stimuli_n[i];

32

cg_inst.sample();

33

34

cg_inst.report();

return 0;

35

36

```

## Coverage (3)

- Coverage statistics are printed at the end of the simulation

- When covering real values ranges are used to identify bins

- Support of Unified Coverage Interoperability Standard (UCIS) under discussion

| •                   |            |      |      |     |         |

|---------------------|------------|------|------|-----|---------|

| \$ ./test           | .exe       |      |      |     |         |

| Covergro            | up: cg_ins | st   |      |     |         |

| VARIABLE            | Expe       | cted | Cove | red | Percent |

| cp_m                |            | 7    |      | 2   | 28.57   |

| cp_n                |            | 15   |      | 5   | 33.33   |

| TOTAL:              |            | 22   |      | 7   | 31.82   |

|                     |            |      |      |     |         |

| coverpoi            | nt: cp_m   |      |      |     |         |

| Name                | Percent    | Hit  | rate |     |         |

| bin_a[0]            | 0          |      | 0    |     |         |

| bin_a[1]            | 0          |      | 0    |     |         |

| <pre>bin_a[2]</pre> | 0          |      | 0    |     |         |

| bin_a[3]            | 100        |      | 4    |     |         |

| bin_b[4]            | 0          |      | 0    |     |         |

| bin_b[5]            |            |      | 4    |     |         |

| bin_b[7]            | 0          |      | 0    |     |         |

|                     |            |      |      |     |         |

- Motivation

- UVM for SystemC and SystemC-AMS

- Randomization

- Coverage

- Summary

#### Summary

Currently UVM for SystemC is discussed as being a standard in SystemC Verification Working Group, however the standard doesn't describe an coverage and randomization API

- Randomization and coverage API with extensions to real values described. However, constrained randomization for real values is hard!

- API will be submitted to Accellera for standardization

## Acknowledgements

The development of the UVM-SystemC methodology and library has been supported by the European Commission as part of the Seventh Framework Programme (FP7) for Research and Technological Development in the project 'VERIFICATION FOR HETEROGENOUS RELIABLE DESIGN AND INTEGRATION' (VERDI). The research leading to these results has received funding from the European Commission under grand agreement No 287562.

## Questions