Design & Verification Conference & Exhibition

## Easier SystemVerilog with UVM: Taming the Beast

#### John Aynsley, Doulos

# The language of choice

# supported by all tool vendors

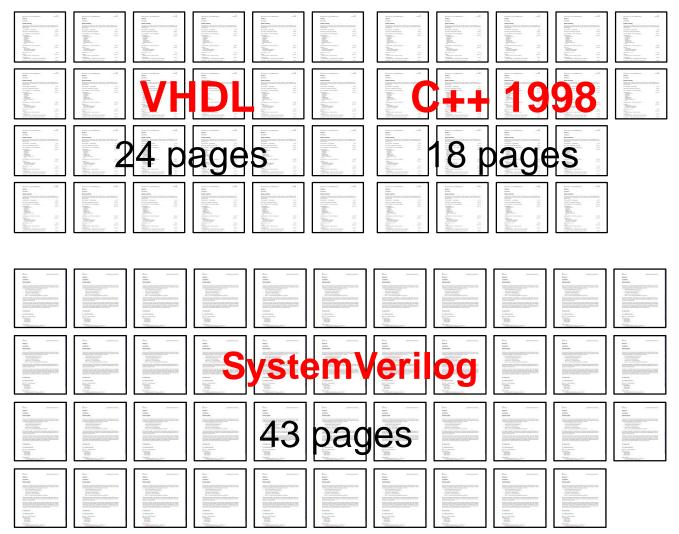

# Large and complex

# Not simple, orthogonal, or consistent

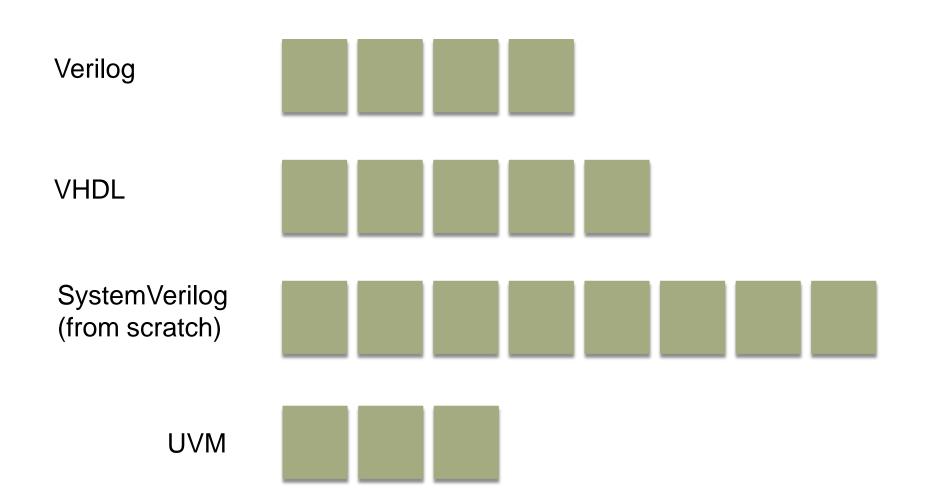

#### **Several Languages in One?**

#### Includes features from

- Verilog

- VHDL

- PSL

- Superlog

- OpenVera

- C

- C++

- Java

## **Differences between implementations**

and don't blame the vendors

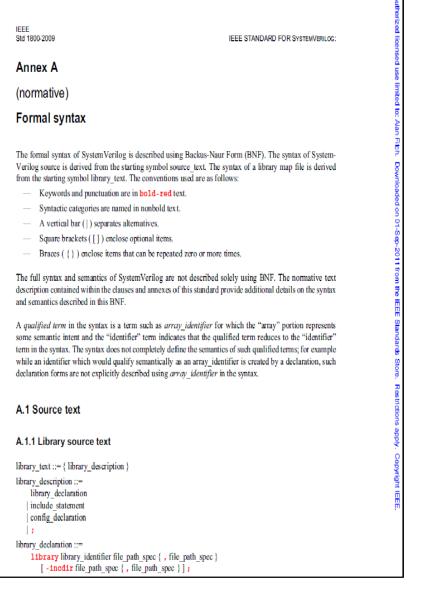

## Syntax Definition - VHDL

| IEEE STANDARD VHDL LANGUAGE REFERENCE MANUAL                                                                                                                                            | IEEE<br>Std 1076-2008 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Annex C                                                                                                                                                                                 |                       |

| (informative)                                                                                                                                                                           |                       |

| Syntax summary                                                                                                                                                                          |                       |

| This annex provides a summary of the syntax for VHDL. Productions ar<br>hand nonterminal name. The number listed to the right indicates the<br>production is given.                     |                       |

| absolute_pathname ::= . partial_pathname                                                                                                                                                | [§ 8.7]               |

| abstract_literal ::= decimal_literal   based_literal                                                                                                                                    | [§ 15.5.1]            |

| access_type_definition ::= access subtype_indication                                                                                                                                    | [§ 5.4.1]             |

| actual_designator ::=<br>[inertial] expression<br>  signal_name<br>  variable_name<br>  file_name<br>  subtype_indication<br>  subprogram_name<br>  instantiated_package_name<br>  open | [§ 6.5.7.1]           |

| actual_parameter_part ::= parameter_association_list                                                                                                                                    | [§ 9.3.4]             |

| actual_part ::=<br>actual_designator<br>  <i>function_name</i> ( actual_designator )<br>  type_mark ( actual_designator )                                                               | [§ 6.5.7.1]           |

| adding_operator ::= +   -   &                                                                                                                                                           | [§ 9.2]               |

| aggregate ::=<br>( element_association { , element_association } )                                                                                                                      | [§ 9.3.3.1]           |

| alias_declaration ::=<br>alias alias_designator [ : subtype_indication ] is name [ signature ] ;                                                                                        | [§ 6.6.1]             |

| alias_designator ::= identifier   character_literal   operator_symbol                                                                                                                   | [§ 6.6.1]             |

#### **Syntax Definition - VHDL**

## **Syntax Definition - SystemVerilog**

Design & Verification Conference & Exhibition

## **Syntax Definition - SystemVerilog**

#### **Syntax Definition**

#### Hard to Learn

# Enter UVM

# Taming the Beast

#### UVM

- Enables verification IP reuse & captures best practice

- Supported by all major vendors

- Increased confidence to adopt SystemVerilog

- Implementations now mutually consistent

- Still need to avoid remaining pitfalls...

## Easier SystemVerilog Approach

#### Do use

- Verilog

- Concise RTL, for hardware synthesis

- Features used by UVM OOP and C-like

- Features for constrained random verification

- Features for interfacing test bench to DUT

#### Don't use

Features which are not portable

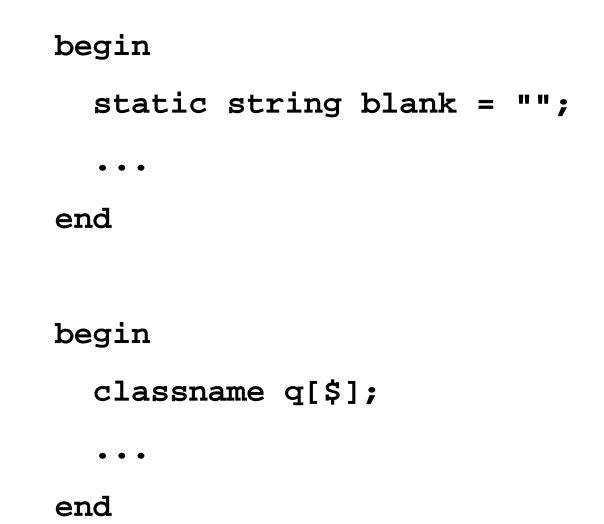

## Used by the UVM BCL

#### Packages

- All the class syntax (almost)

- typedef, 2-state types, enums, (some) structs in classes

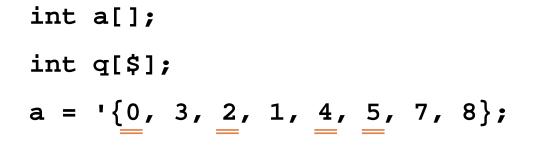

- Strings, queues, associative and dynamic arrays

- C-like procedural statements in methods

- fork-join in methods

#### class C #(type T = int) extends BASE #(T);

begin

#### classname::typename::method();

classname #(typename)::method();

end

#### if (\$cast(to\_handle, from\_handle))

• • •

#### void'( obj.method() );

#### typedef enum bit { lit1 = 0, lit2 = 1 } name;

#### for (int i = 0; i < n; i++)

• • •

#### foreach (array[i])

• • •

#### -> assoc\_array[index].named\_event;

#### function void f (

## ref uvm\_component comps[\$], input uvm\_component comp = null, string arg = "");

## **Used by UVM Applications**

- interface

- clocking

- modport

- virtual interface

- Handle in module scope

Module-class communication

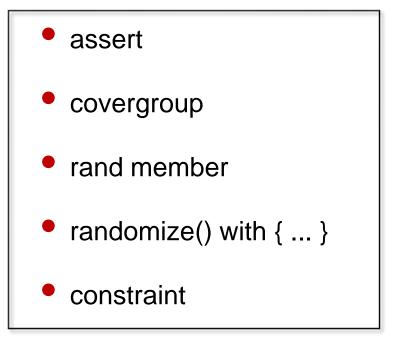

Constrained random

Array manipulation methods

Verilog!

# Pitfalls

#### **Pitfalls**

Many features robust and portable

- Remaining pitfalls cannot be simply described

- UVM BCL side-steps some pitfalls

- List of pitfalls is now short and getting shorter!

- Areas where the vendors have not converged?

## **Continuous Assignment to Handle**

class C; ... endclass

module top;

C handle1 = new;

C handle2;

assign handle2 = handle1;

#### **Handles as Ports**

class C; ... endclass

module child1 (input C p, output C q);

module child2 (ref C p, ref C q);

#### **Hierarchical Reference to Handle**

class C; ... endclass

module top;

modu inst ();

initial

inst.handle = new;

endmodule

module modu;

C handle;

endmodule

#### **Hierarchical Reference to Parameter**

interface iface;

```

parameter int p = 8;

```

endinterface

module top;

iface iinst();

bit [iinst.p-1:0] vec;

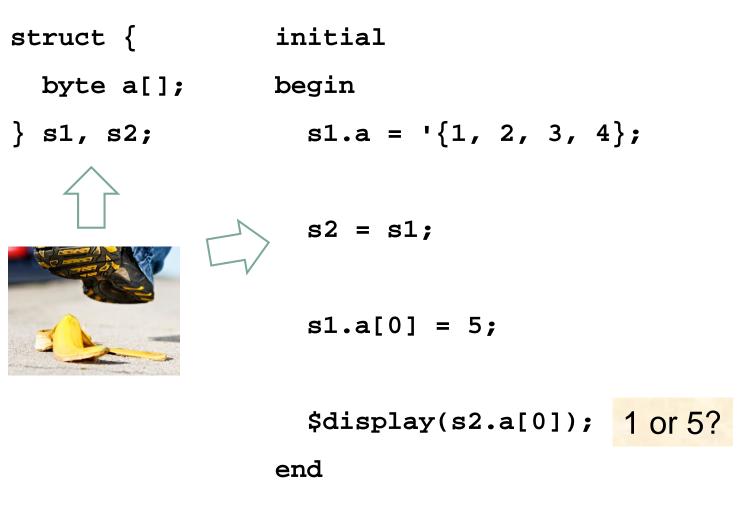

#### **Objects as Struct Members**

#### **Unpacked Unions**

```

typedef struct

{

bit a;

byte b;

} T1;

typedef struct

{

byte c;

bit d;

} T2;

```

```

typedef union

{

T1 p;

T2 q;

} U;

```

### **Bitstream Casting**

```

typedef struct

module top;

bit a;

T1 s1;

byte b;

T2 s2;

} T1;

initial

typedef struct

begin

s1 = '{1, 1};

byte c;

bit d;

s2 = T2'(s1);

} T2;

```

Copyright © 2012 by Doulos. All rights reserved.

### **Type Parameter Substitution**

class C #(type T = ...);

typedef T::T2 T3;

static const int d = T::c; endclass

class D; typedef C #(C1) T; static const int e = T::d;

### **Protected Constructor**

#### protected function new;

• • •

#### endfunction

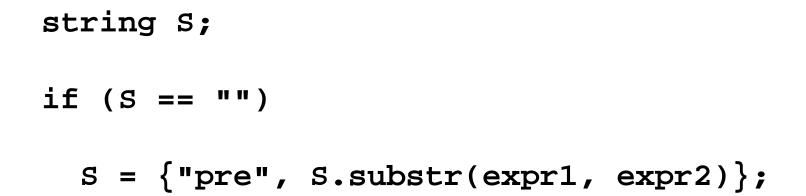

### **Array-to-Queue Assignment**

begin int da[]; int q[\$]; da =  $\{1, 2, 3, 4\};$ q = da;

`define UVM\_DA\_TO\_QUEUE(Q,DA)\

foreach (DA[idx]) Q.push\_back(DA[idx]);

### **Iterator Index Query**

q = a.find with ( item == item.index );

### **Statement Labels**

initial

blk: begin

loop: repeat (8);

end: blk

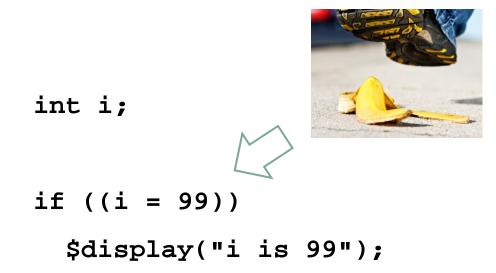

### **Assignment as Side Effect**

### final

#### final

\$display("The End at ", \$time);

### wait fork

begin fork #44; fork #125; #14; join\_none #2; join\_none wait fork;

\$display(\$time); 44 or 125?

end

#### initial

#### \$display( \$get\_coverage );

# **Empty Coverpoint**

#### rand longint data;

endgroup

### std::randomize

begin

byte unsigned a, b, c; assert( randomize(a, b, c) );

assert( std::randomize(a, b, c) );

# **Prototype in modport**

modport mp (import function void hello());

modport mp (import hello);

### Keep modules and classes separate?

• No need for unpacked structs, unions, or arrays (other than Verilog memories)?

### Conclusions

### Do use

- Verilog!

- Synthesis-friendly RTL features

- Classes (from UVM)

- C-like features: data types and statements (from UVM)

- Interfaces, virtual interfaces, clocking blocks

- Assertions, coverage, constraints

# UVM has tamed the beast!