## Introduction

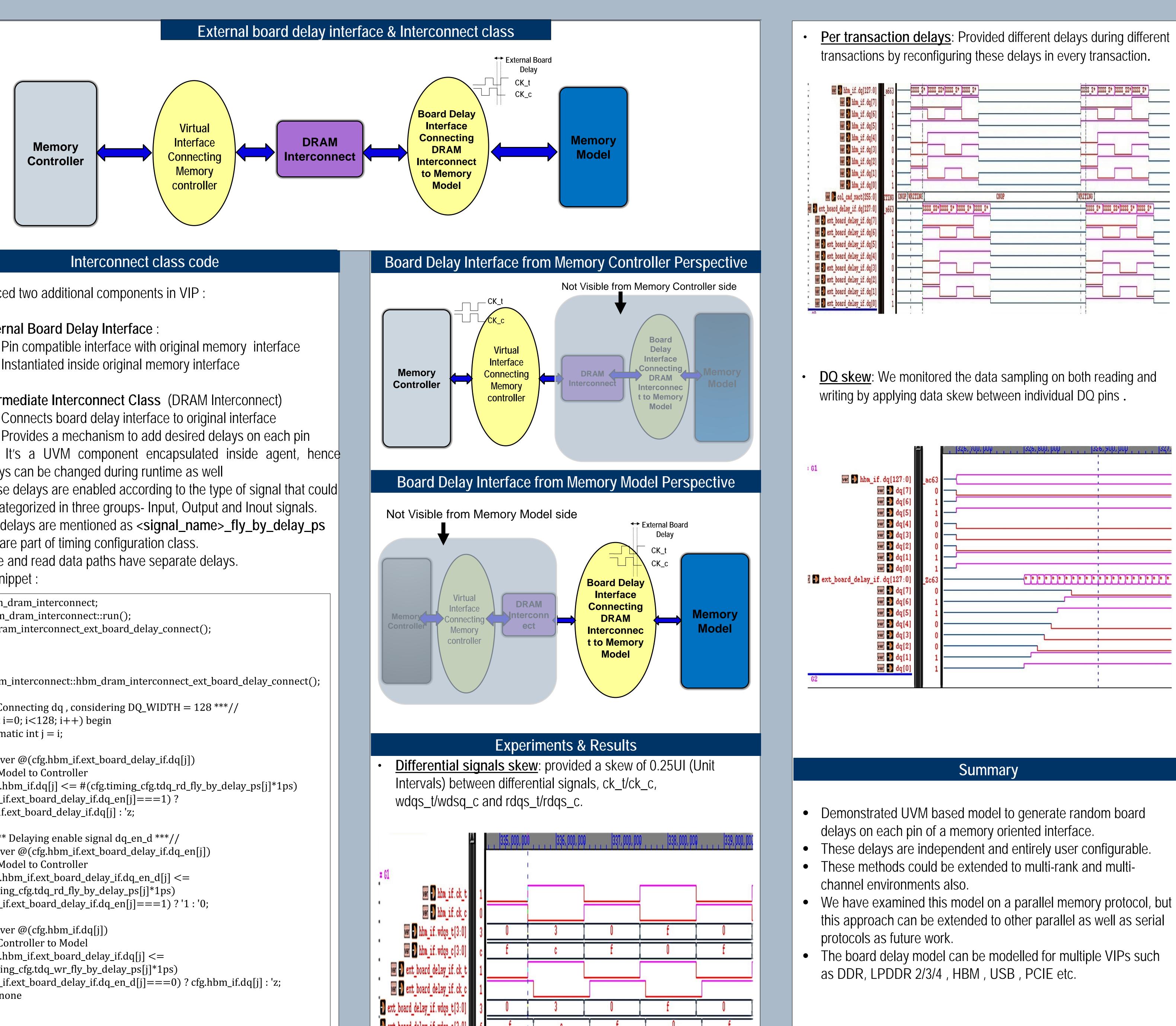

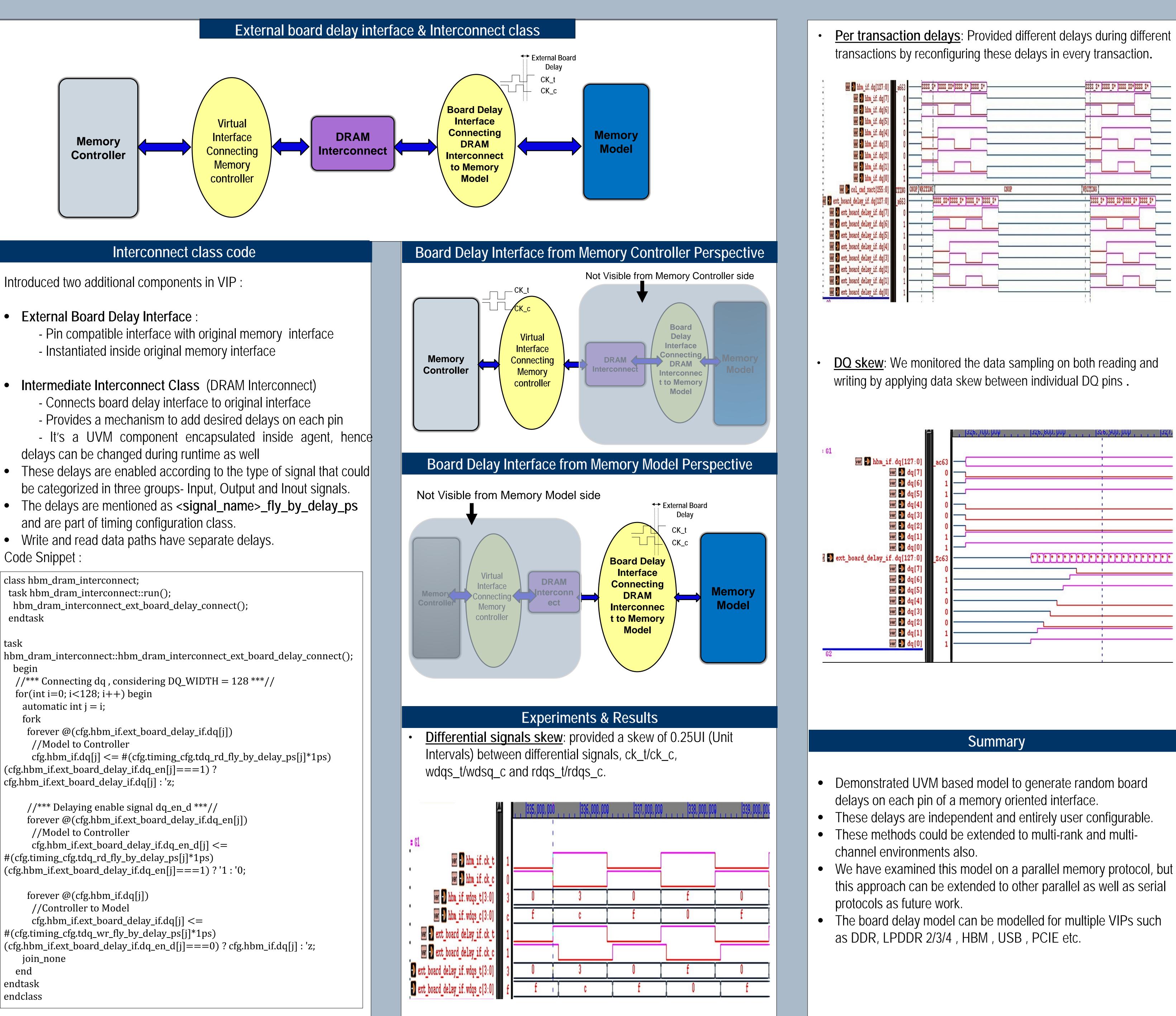

A typical SoC has different electrical delays. Their cumulative electrical delay can result in a liner shift within each system signal, Which can be combined to model as **Board Delays**. This presentation focusses on

- Modeling external board delays using UVM (Universal) Verification Methodology) for single and multi-channel environment.

- Multiple approaches :- fixed board delays, configurable board delays & randomized external board delays modelling.

- Demonstration of external board delay modeling using LPDDR (Low Power DRAM) and HBM (High Bandwidth Memory)

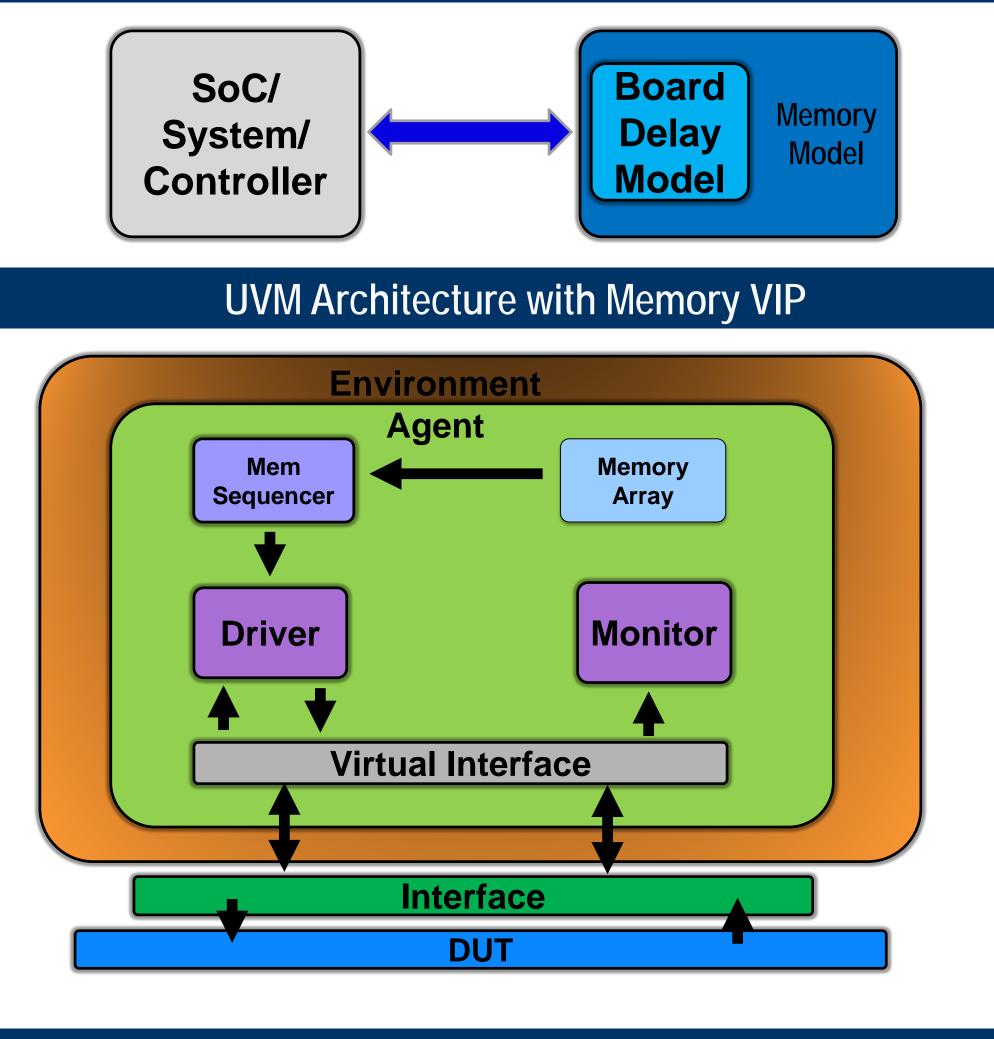

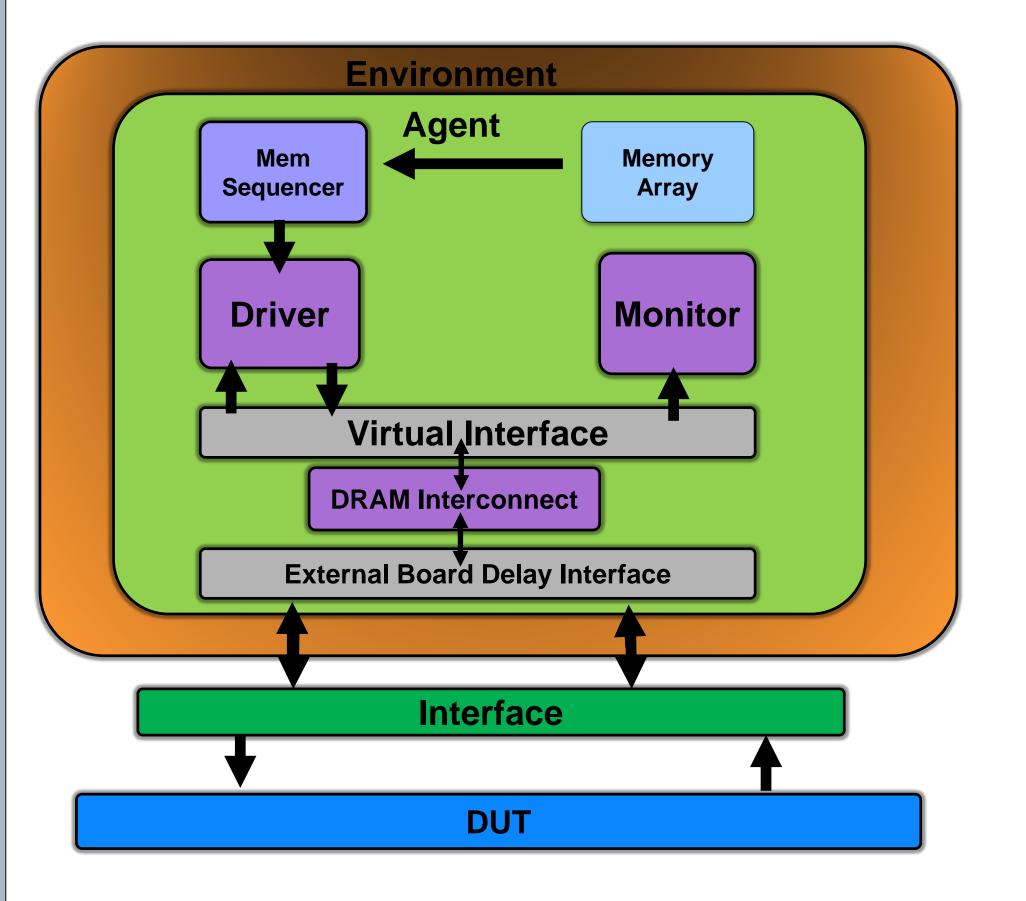

### Board Delay Model Encapsulated within Memory System

Board delay architecture with UVM approach

# Don't delay catching bugs : Using UVM based architecture to model external board delays Amit Paunikar, Saurabh Arya, Vikas Makhija & Shaily Khare Synopsys India Pvt. Ltd.