#### Coherency Verification & Deadlock Detection Using Perspec/Portable Stimulus

Moonki Jang – Samsung Electronics Co.,Ltd. Phu Huynh – Cadence Design Systems, Inc

cādence<sup>®</sup>

### Agenda

- Why coherency and deadlock detection verification

- Requirements & description of our verification environment

- Using Perspec and PSS to create reusable test suite

## Trends

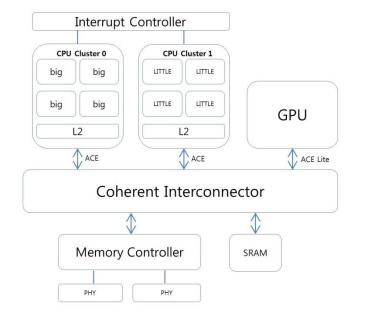

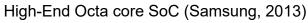

Latest automotive & mobile SoCs need higher performance and incorporation of additional functionality

#### Latest ADAS reference platform (ARM,2018)

# Side effects

- The need for higher performance and additional functionality has increased the complexity of coherency networks every year

- Increased complexity always causes unexpected problems like resource conflicts between multiple coherent masters when working concurrently

## Agenda

- Why coherency and deadlock detection verification

- Requirements & description of our verification environment

- Using Perspec and PSS to create reusable test suite

# Requirements

- Reasons why it is important to detect deadlock-related coherency issues at the pre-silicon level:

- Hard to reproducing deadlock on silicon environment

- Transaction flow tracking is impossible

- Root cause analysis will be extremely difficult on silicon

# Considerations

- Reasons why coherency issue detection is difficult at the pre-silicon level:

- Slow simulation speeds make it difficult to perform complex scenarios

- For reproducing the specific target conditions, pre-silicon scenarios should narrow down the scenario scope.

- It requires much effort and time to create such a complex scenarios

- PSS(Portable Stimulus Standard) verification environment was introduced to solve these issues

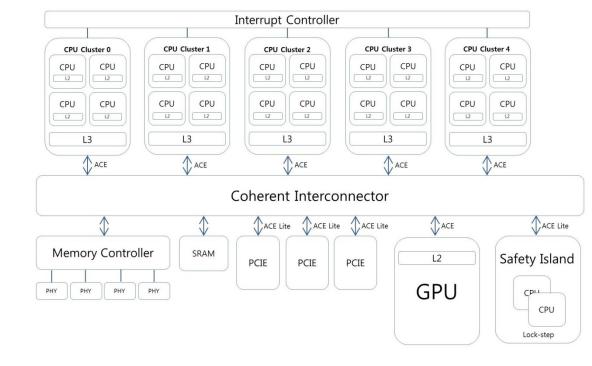

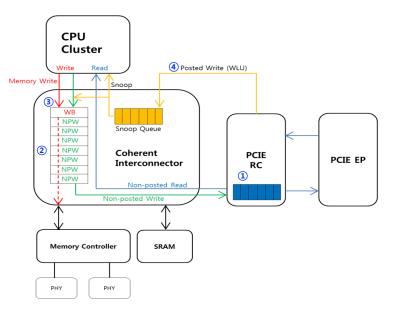

# PCIe deadlock verification

- The following two blocking conditions cause a PCIe deadlock

- ACE (AXI Coherency Extensions) master blocking condition

- ACE master might have to complete a WriteBack transaction of a similar operation before it can respond to a snoop request

- PCIe blocking condition

- A PCIe bridge can stall reads and PCIe configuration writes on its AXI slave interface when write transactions from its AXI master interface is stalled

# PCIe deadlock verification

- Reproducing scenario should make below conditions

- 1. Fill up the PCIe RC request queue using a non-posted read from CPU

- 2. After RC request queue is full, additional non-posted write should block the write channel

- 3. CPU will generate WriteBack for address A

- 4. PCIe EP will generate WLU for address A

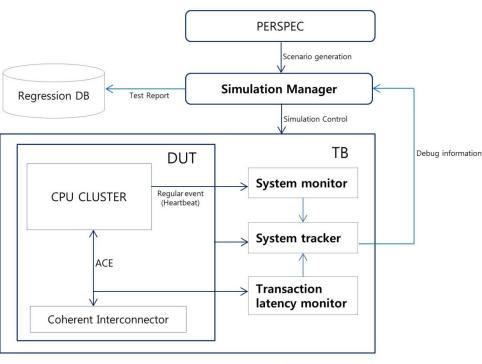

• Our test suite can detect deadlock and gather system information

DUT : Design Under Test TB : Test Bench - System Monitor System status check using 'heartbeat response'

- Transaction Latency Monitor Records the latency of all transactions originating from the CPU(s)

#### - System Tracker

Gathers the system information for root cause analysis and generates log files

#### - Simulation Manager

Manages the whole process of creating and executing the Perspec scenarios for simulation and analyzes the results

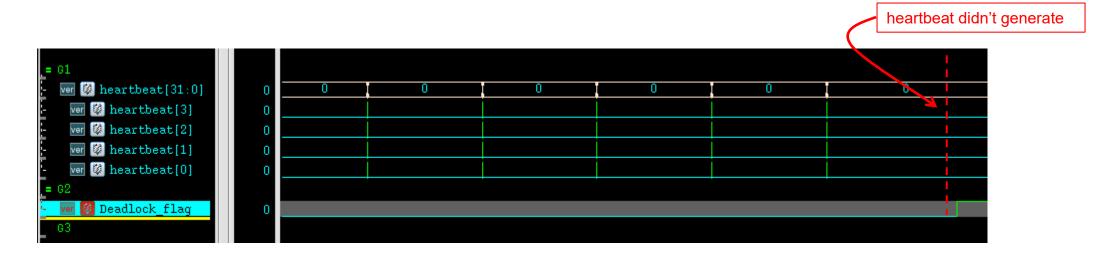

- System Monitor

- Each core generates a heartbeat to the system monitor

- If system monitor does not detect the heartbeat in the expected period, it assumes that the system has fallen into a deadlock state.

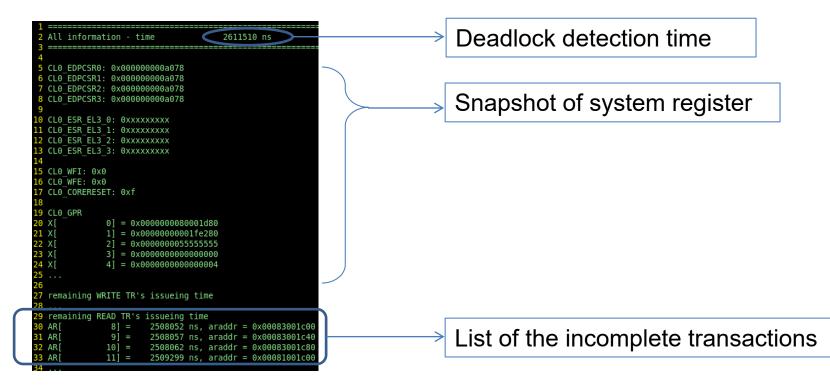

- System Tracker & Transaction Latency Monitor

- When deadlock is detected, system tracker will collect the system information from the latency monitor and system monitor.

- Simulation Manager

- If deadlock is reported in the log, simulation will be re-launched to get a dump file through regression manager's post processing

- At this time, the system information result that is generated in the system tracker can be used to specify the dump period

| 218 | #postrun                                                                 |

|-----|--------------------------------------------------------------------------|

| 219 | if(! -e ./dump_gen ) then                                                |

| 220 | if( -e ./sim.log ) then                                                  |

| 221 | if(`found_match.pl -s ./sim.log -m 'TEST FAILED'` == 'found_match') then |

| 222 | run-with_fsdb                                                            |

| 223 | endif                                                                    |

| 224 | endif                                                                    |

### Agenda

- Why coherency and deadlock detection verification

- Requirements & description of our verification environment

- Using Perspec and PSS to create reusable test suite

# **Coherency Verification**

- Perspec and PSS simplifed and shortened our verification tasks

- Basic (PSS) actions are provided by Perspec libraries

- Coherency test suite is also provided

- Coverage models are part of the Perspec libraries

- Overall verification process:

- Create model of the compute (processor-memory) subsystem

- Run sanity memory R/W tests

- Run coherency test suite provided by Perspec library

- Develop additional corner cases & stress test scenarios

#### **Create Processor-Memory model**

• Processor Info table

| Processor | Info  |          |             |          |                  |

|-----------|-------|----------|-------------|----------|------------------|

| #tag      | #kind | #cluster | #cluster_id | #core_id | #coherency_level |

| M0        | MO    | MO       | 0           | 0        | FULI             |

| M1        | MO    | MO       | 0           | 1        | FULI             |

| M2        | MO    | MO       | 0           | 2        | FUL              |

| M3        | MO    | MO       | 0           | 3        | FUL              |

| A0        | AP    | AP       | 1           | 4        | FUL              |

| A1        | AP    | AP       | 1           | 5        | FUL              |

| A2        | AP    | AP       | 1           | 6        | FUL              |

| A3        | AP    | AP       | 1           | 7        | FUL              |

| BO        | A72   | A72      | 2           | 8        | FUL              |

| B1        | A72   | A72      | 2           | 9        | FUL              |

| B2        | A72   | A72      | 2           | 10       | FUL              |

| B3        | A72   | A72      | 2           | 11       | FUL              |

### **Create Processor-Memory model**

• Memory Info table

| Memory Info |          |            |           |

|-------------|----------|------------|-----------|

| #mem_block  | #enabled | #base_addr | #end_addr |

| DDRO        | TRUE     | 0x80000000 | 0x9FFFFFF |

| DDR1        | TRUE     | 0xA000000  | OxBFFFFFF |

| DDR2        | TRUE     | 0xC0000000 | OxFFFFFFF |

• Page Table

| #va        | #pa        | #size      | #secure | #shareable      |

|------------|------------|------------|---------|-----------------|

| 0x80000000 | 0x8000000  | 0x20000000 | TRUE    | outer_shareable |

| 0xA000000  | 0xA000000  | 0x20000000 | TRUE    | outer_shareable |

| 0xC0000000 | 0xC0000000 | 0x4000000  | TRUE    | non_shareable   |

# Memory R/W Test - PSS

};

- Sanity test to ensure that basic processor-memory paths are working.

- Atomic actions provided by Perspec library:

- -write\_data

- copy\_data

- read\_check\_data

- sml processor tag e

• Built-in data type:

accellera

SYSTEMS INITIATIVE

```

action pss wr_cp_rc {

rand sml processor_tag_e proc_tag_l;

activity {

sequence {

do sml sw ops c::write data with {

proc tag == proc tag 1;

};

do sml sw ops c::copy data with {

proc tag == proc tag 1;

};

do sml sw ops c::read check data with {

proc tag == proc tag 1;

};

};

};

```

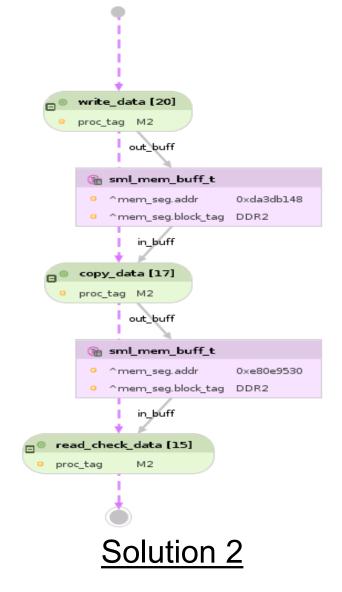

# **Memory R/W Test - Solutions**

- Tests generated from

previous PSS code

- Solution 1: uses core A2

- Solution 2: use core M2

- Memory blocks are also selected randomly by Perspec

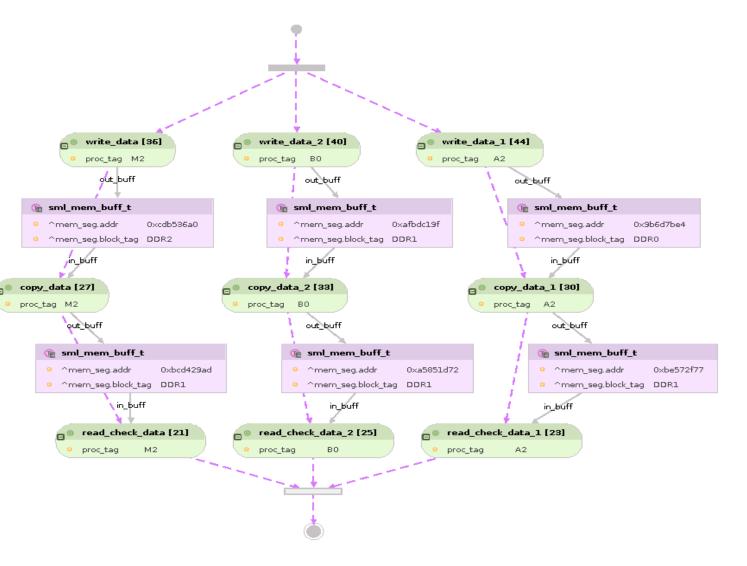

# Multi-core Memory R/W - PSS

- Three processor cores doing memory R/W test in parallel

- Verify inter-processor(mailbox) communication

- Show how previous compound action (pss\_wr\_cp\_rc) is used to build more complex PSS scenario

```

action pss wr cp rc 3cores {

pss wr cp rc chain1, chain2, chain3;

activity {

parallel {

chain1;

chain2 with {

proc tag l != chain1.proc tag l;

};

chain3 with {

proc tag l != chain1.proc tag l;

proc tag l != chain2.proc tag l;

};

};

};

```

## **Multi-core Memory R/W - Solution**

- In this solution, cores M2, B0, A2 were selected

- Different memory blocks (DDR0, DDR1, DDR2) were also selected randomly

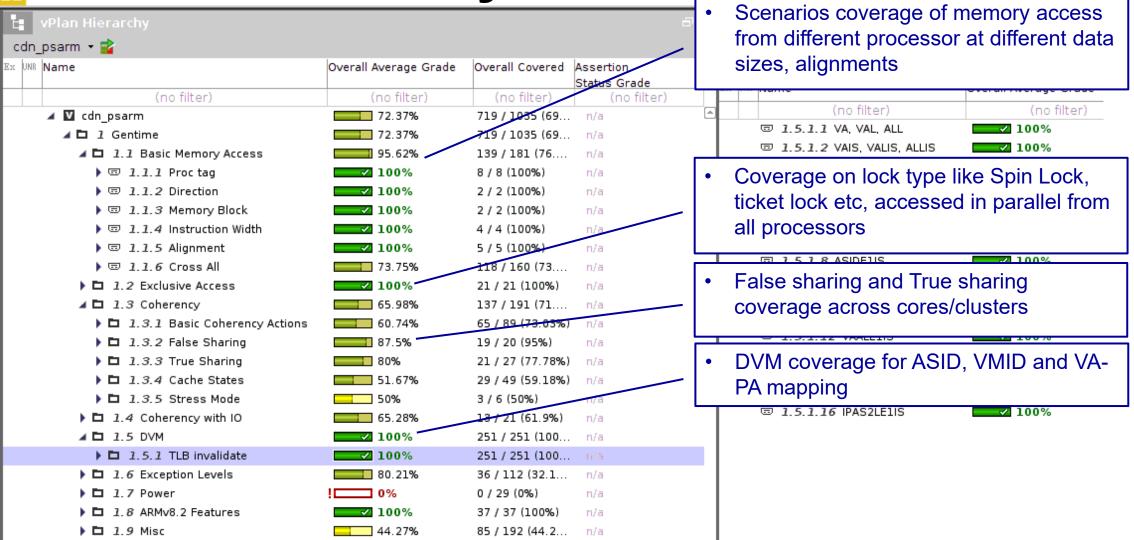

# **Coherency Test Suite**

- Perspec library includes a verification plan and a suite of tests

- Focus on memory access, coherency, and low-power

- Verification Plan Outline:

- Basic Memory Access

- Exclusive Accesses

- Coherency: basic coherency actions, false-sharing, true-sharing, cache states

- Coherency with IO

- DVM

- others

# **Coherency Test Suite**

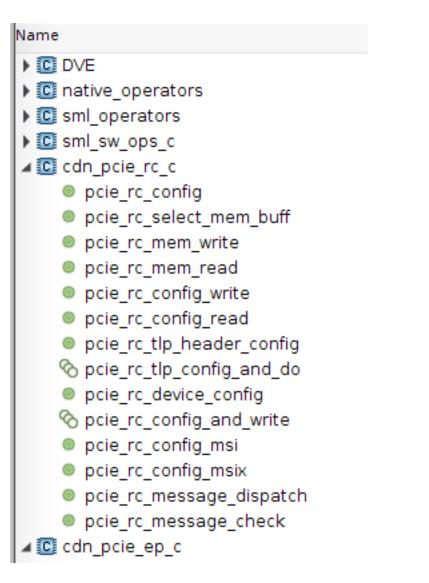

## PCIe Library – RC & EP Actions

| Name                            |  |

|---------------------------------|--|

| ▶ C DVE                         |  |

| Inative_operators               |  |

| Image: Sml_operators            |  |

| Image: Sml_sw_ops_c             |  |

| C cdn_pcie_rc_c                 |  |

| cdn_pcie_ep_c                   |  |

| pcie_ep_config                  |  |

| pcie_ep_select_mem_buff         |  |

| pcie_ep_mem_write               |  |

| pcie_ep_mem_read                |  |

| pcie_ep_config_write            |  |

| pcie_ep_vip_reg_write           |  |

| pcie_ep_tlp_header_config       |  |

| ☆ pcie_ep_tlp_config_and_do     |  |

| pcie_ep_message_dispatch        |  |

| pcie_ep_msi_int_generate        |  |

| pcie_ep_msix_int_generate       |  |

| pcie_ep_ats_translation_request |  |

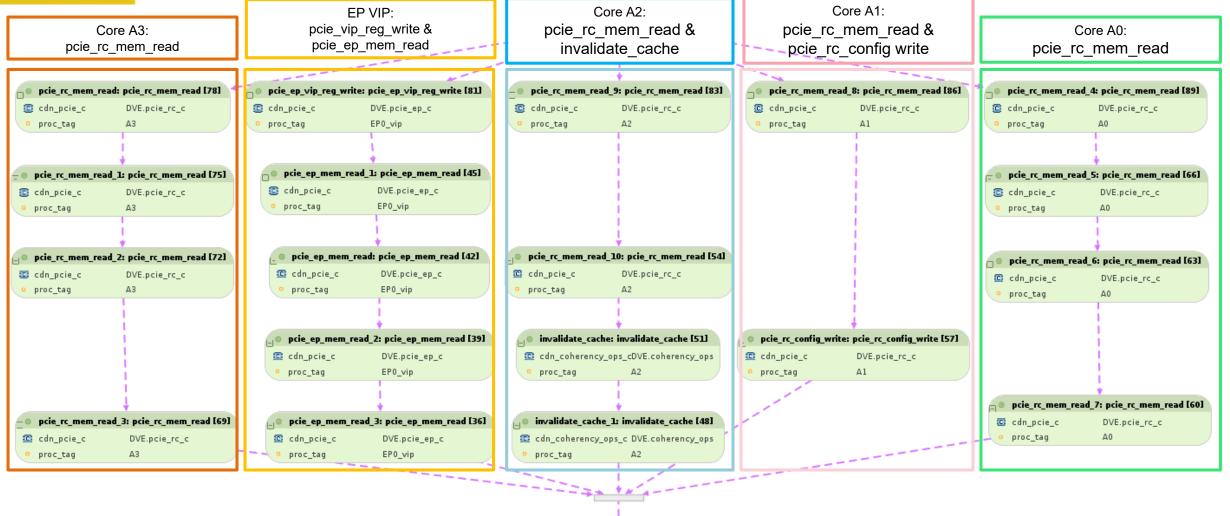

#### **Deadlock Verif Scenario – Pseudo Code**

//Setup step: setup PCIe RC and PCIe EP ...

```

//...

```

parallel { //randomly pick a core to do the following actions

do pcie\_rc\_mem\_read multiple times in sequence; //core A3 in Fig 7

do pcie\_rc\_mem\_read multiple times in sequence; //core A0

do pcie\_rc\_mem\_read and invalidate\_cache; //core A2

do pcie\_rc\_mem\_read and pcie\_config\_write; //core A1

//PCIE EP

```

sequence {

```

};

do pcie\_ep\_vip\_reg\_write;

do pcie\_ep\_mem\_read multiple times;

};

#### **Deadlock Verif Scenario – Solution**

# **Conclusions & Lessons Learned**

- Writing PSS scenarios were much simpler than writing C tests manually

- Library actions allow us to work at a higher-level of abstraction

- Inter-processor communication is handled automatically by Perspec

- Resource allocation is also handled automatically

- Project-to-project reuse requires more than PSS; need:

- Libraries

- Reuse methodology

# **Conclusions & Lessons Learned**

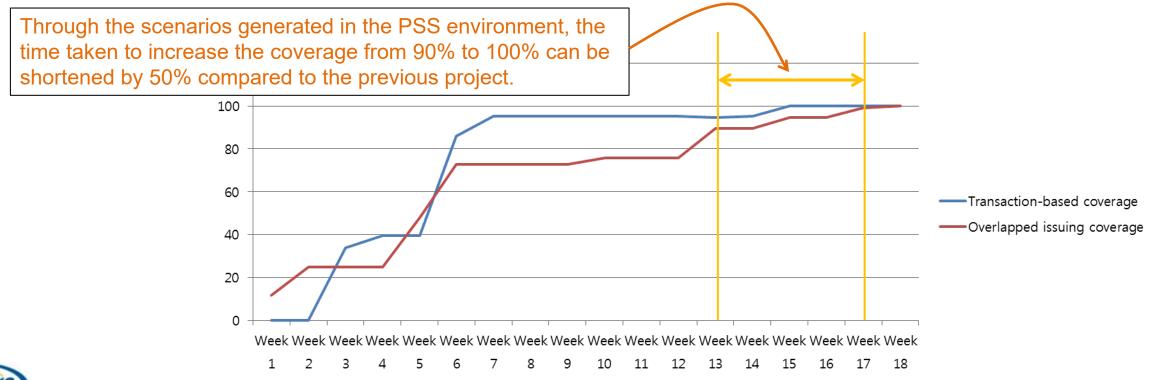

- PSS and Perspec helped shorten our design verification

- Below chart shows our coherency coverage closure status of recent project.

# **BACK-UP Slides**

# **DVCon Slide Guidelines**

- Use Arial or Helvetica font for slide text

- Use Courier-new or Courier font for code

- First-order bullets should be 24 to 28 point

- Second-order bullets should be 24 to 26 point

- Third-order bullets should be 22 to 24 point

- Code should be at least 18 point

- Your presentation will be shown in a very large room

- These font guidelines will help ensure everyone can read you slides!

#### **Code and Notes**

Informational boxes should be 18pt Arial-bold, or larger (using a background color is optional)