# Cleaning Out Your Pipes - Pipeline Debug in UVM Testbenches

Rich Edelman Mentor, A Siemens Company 46871 Bayside Parkway, Fremont, CA 94538 Neil Bulman Arm Limited 110 Fulbourn Road, Cambridge, UK CB1 9NJ

Abstract- Debugging SystemVerilog[1] UVM[2] Testbenches can be challenging. This paper will discuss some tips and tricks for debugging specific problems with a UVM Testbench for a pipelined design. These techniques can be used with any debugger, but are sometimes difficult to use without a roadmap. We'll describe and discuss a roadmap for doing high level UVM Testbench debug.

### I. INTRODUCTION

Debug can be the mundane day-to-day work that is consuming more and more time. Using advanced debug techniques can help speed up bug finding and improve quality.

In a modern UVM Testbench, there is usually a collection of code from many different places – different design and verification teams, various verification IP, automatically generated stimulus generators, automatically generated coverage collectors, and many constraints. Most verification engineers are likely only familiar with a small part of this code. Good debug means good visibility.

In this paper, better debug is achieved through better visibility and better analysis – even for simple things like waveform debug. We'll show how to instrument sections of code to provide better visibility - for example using transaction recording and transaction debug.

The following categories of problems and solutions will be discussed in this paper.

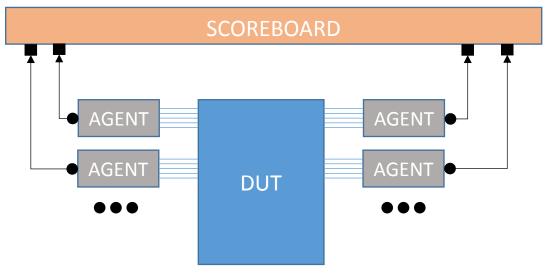

#### II. EXAMPLE

The motivation and example used for this paper was a sub-section of an Arm® Cortex-M33, which was announced October 2016. It shares characteristics with the Cortex-M4 plus TrustZone security and 3-stage instruction pipeline. The design code consist of 62 files containing a total of about 100,000 lines of code. The testbench code consists of 95 files containing about 12,000 lines of code. A typical test runs in about a minute and the tests use random seeds. The basic block diagram for the test environment is in Figure 1.

Figure 1 - Basic Testbench Architecture

# III. TESTBENCH DEBUG

#### Data structures

A testbench typically will use many types of SystemVerilog data structures, including dynamic arrays, associative arrays and queues. It will contain lists of lists and arrays of arrays and arrays of lists. The job of the scoreboard is to keep track of things (make lists) and to model behavior (both with code and with data structures).

A pipeline scoreboard might have queues of expected items that are in the pipeline. The model needs to be kept consistent with the hardware. Pipeline items can be put in the wrong pipeline queue or duplicated, or not put in at all. Each of these issues – wrong place, duplicated and missing must be debugged. Who put it in the wrong place and why? Who duplicated it and why? And worst of all – who did NOT put it in the right place. Debugging things that happened and are incorrect is hard. Debugging things that didn't happen is even harder. We don't have an automatic answer for any of it, but by combining the techniques below debug can be made easier.

#### Coding Styles

Testbench scoreboards written in SystemVerilog may have a combination of UVM calls, macros, threads, if-thenelse and case statements. The code is usually written at a "higher abstraction" level: pushing and popping a queue and comparing the items from two different queues. Or interpreting instructions streams to make an accurate replica of registers and memory. The best debug is writing clear and small code. Large nested if-then-else and multiple page function calls are ripe for big problems. Write simply.

## IV. USE \$DISPLAY

"I just use \$display". That's a common way to do debug, and often the fastest way to figure out what is going on. But on a real design with lengthy compile, optimization, elaboration and simulation times, it is hard to repeatedly add \$display in each new place it is needed.

But by all means use \$display. But then don't forget to take them all out again. A simple way to take them in and out is with some kind of macro (like VERBOSE below).

```

`ifdef VERBOSE

$display("Debug: %0d", loop_count);

`endif

```

Use your debug tool when possible to see values. \$display is a last resort.

#### V. USE FANCY \$DISPLAY WITH %P

Using \$display can be cumbersome and time-consuming when printing a complex object, list a class or an array. Use the %p format type. SystemVerilog will auto-format the object, including arrays and class objects.

```

int gid;

class base;

int id;

int x;

function new();

id = gid++;

endfunction

endclass

class extended extends base;

int x;

int y;

int z;

base b;

int my_queue[$];

int my_associative_array[int];

```

```

function void print();

b = new();

$display("This = %p", this);

$display("B = %p", b);

$display("Queue = %p", my_queue);

$display("Associative Array = %p", my_associative_array);

endfunction

```

The print() routine will produce the output below, printing a two classes, a queue and an associative array.

VI. EVEN FANCIER \$DISPLAY - STYLIZED WATCH WINDOW

Problem: A collection of variables should have consistent values. After some simulation they become inconsistent (they diverge). Keep an eye on those variables. Testbenches and designs are getting more complicated. When a test fails it may not be immediately obvious whether the design or testbench is at fault, being able to compare the testbench expected view of state can help quickly determine which is at fault and direct the next stage of debug.

A watch window is called for in your debug tool. Or you can have a "watch()" function defined which prints the "interesting" variables when called. Call this watch() function when things change or on every clock edge, or at regular times.

Output Result:

This is a simple list of variables with header and time. Fancier "blocks" of information could be printed, like a collection of registers or memory locations. Arguments could be passed in, either with the variables to be printed or object handles to use to reference the desired variables.

## VII. BREAKPOINT

Problem: Testbench code is doing something wrong. Set a breakpoint to figure out how it got there. What the control conditions were. Use the debugger software to set a breakpoint. If you don't have a breakpoint capability, use a \$stop. Using SystemVerilog code, we could insert code such as

| BP1: begin |

|------------|

| \$stop;    |

| end        |

|            |

A Regular Breakpoint

Many debug tools have breakpoints. They are easy to specify using a syntax like

```

bp <FILE> <LINENUMBER>

```

If no debug tool with breakpoints are available, you can use \$stop on the line you want to stop on.

VIII. CONDITIONAL BREAKPOINT

Problem: A breakpoint can be set, but we only want to stop at the breakpoint under certain conditions. For example, in a class, a breakpoint on a line might only apply to a certain instance of that class – we only want to stop in one particular instance of the class. In addition, other conditions can be tested when a breakpoint is hit, for example, if we are not in "reset mode", or if the number of items processed has reached 10000, or if 10 reads and 10 writes have happened.

Using SystemVerilog code, we could insert code such as

```

BP2: begin

if ( !reset_mode && nreads > 10 && nwrites > 10) $stop;

end

```

## IX. BREAKPOINTS WITH A COUNT

Problem: Sometimes a problem occurs in a testbench at a certain line, but only after the breakpoint has been hit hundreds or thousands of times. Using a counter allows the breakpoint to be skipped until the counter is reached. Using SystemVerilog code, we could insert code such as

```

BP3: begin

if ( counter++ > LIMIT) $stop;

end

```

## X. BREAK IN A SPECIFIC INSTANCE

Problem: Only one particular instance of a class object is having a problem. Break on a line in just that one instance. There are many ways to specify an instance, perhaps the easiest is with the "name". Stop when the name matches.

```

BP4: begin

if(get_full_name() == "uvm_test_top.i2_ ... .ggp_seq_A2.gp_seq.p_seq.A_seq")

$stop;

end

```

# XI. BREAK ON CHANGE - DETECTING A VARIABLE CHANGE

Problem: A class member variable is being changed, but the source of the change cannot be determined by code inspection. For example, a status register, an event trigger or a configuration field could be getting updated incorrectly. The source of the change must be found. In a microprocessor it may be possible for a general purpose register to be updated for many reasons: instruction execution, entering an interrupt hander, returning from an interrupt handler, external debug access, testbench initialization stimulus. If a number of these happen close together it can be difficult to track the order which the testbench modelled these. Using break-on-change in conjunction with a call stack can quickly show why the updates happened and the order the testbench handled them.

Use the debug tool to set a break-on-change. Run simulation until the break. The "change" is happening at the break spot. Now, debug can determine how and why this change is happening. If your debug tool doesn't have break-on-change, then using SystemVerilog code it is quite easy to stop after detecting a change in class member variable.

```

`define STOP_ON_CHANGE(obj,name) \

fork \

forever begin \

@(obj.name); \

$display("Stopping. Object Member Variable Changed"); \

$stop; \

end \

join none

```

In the testbench, execute the follow code, which creates a "stop-on-change" monitor.

This macro adds a powerful debug aid. It waits for a class member to change, from some specific class. When it changes, then a message is printed and simulation stops.

## XII. BREAK ON CHANGE - DYNAMIC ARRAY OR QUEUE CHANGE

Stopping on a variable change is important, but sometimes those variables are arrays, queues, dynamic arrays or associative arrays. This can add some complexity. When one of these dynamic elements changes size, it is important for debug. When one of the elements in one of these dynamic elements changes, it is important for debug. In both cases, an update has been made, and could be important for debug. The change is important, but more important is "who did it".

Many kinds of fancy checks can be implemented using SystemVerilog. In the case below, the check is to wait for the size of the queue to change. After five monitoring events, stop monitoring.

```

task wait_all_q();

forever begin

int size;

size = all_q.size();

wait (all_q.size() != size);

$display("STOPONQUEUE: Size changed. size=%0d, q=%p", all_q.size(), all_q);

if (count++ > 5) break; // Stop monitoring after 5 alerts

end

...

endtask

...

task run_phase(...);

fork

wait_all_q();

join

...

endtask

```

#### **OUTPUT FILE:**

```

# STOPONQUEUE: Size changed. size=1, q='{@sequence_item_A@3}

# STOPONQUEUE: Size changed. size=2, q='{@sequence_item_A@7,

@sequence_item_A@3}

# STOPONQUEUE: Size changed. size=3, q='{@sequence_item_A@11,

@sequence_item_A@7, @sequence_item_A@3}

# STOPONQUEUE: Size changed. size=4, q='{@sequence_item_A@15,

@sequence_item_A@11, @sequence_item_A@7, @sequence_item_A@3}

```

#### XIII. STACKS AND THREADS AND SEQUENCES

Problem: Setting breakpoints and single stepping is too low level. We want to see sequences get created and watch any patterns form with long or short lives. Additionally, we want to debug threads they may spawn.

Closing coverage can be a time consuming part of a project, which can have an impact on either project delivery with additional time needed to close coverage, or project quality, with fixed deadlines and coverage holes.

Being able to visualize the coordination of sequences can help in being able debug why the expected tests are not producing the expected results in a more time efficient manner. Many debug tools have the ability to record transactions. Transactions can be placed in any part of the testbench or design. [3]

| Transaction         |                          |                                         |            | Transaction    |                                         |               |

|---------------------|--------------------------|-----------------------------------------|------------|----------------|-----------------------------------------|---------------|

| _top.e0.a.sqr.vseq1 | e9c9553fa378e88104da46f  | V                                       | seq1       |                |                                         |               |

| _top.e0.a.sqr.vseq2 | a9deebec86ffec98f8ea923d |                                         | vseq       | 2              |                                         |               |

| _top.e0.a.sqr.vseq3 | 85f56aad6e23f200769aded  |                                         | Vs         | eq3            |                                         |               |

| _top.e0.a.sqr.vseq4 | 16ec050fa001ec744c79cf62 | vs*                                     |            | v seq4         |                                         |               |

| memory_if.memory_if | <pre>memory_if(2)</pre>  |                                         |            |                |                                         |               |

| _top.e0.a.sqr.wdata | wdata(0)                 | <mark>@``@``@``@``</mark>               |            |                |                                         |               |

| st_top.e0.a.sqr.wid | wid(0)                   | <b>₩*₩</b> ₩                            |            |                |                                         |               |

| _top.e0.a.sqr.rdata | rdata(2)                 |                                         |            | <del>2)</del>  | 🐝 🔿                                     | 😁             |

| test_top.e0.a.d.vif | /top/memory_if           |                                         | /          | top/memory_if  |                                         |               |

| m_test_top.e0.a.d.t | @transaction_read@57     | @t*/@%@*/@*/@*////@tra                  | nsaction_w | transaction_   | re%)%tr                                 | ansaction*@tr |

| top.e0.a_config.d.t | @transaction_write@348   | @transaction* <b>10</b> @tra            | nsaction_w | Øtransactio    | n_ <b>j0</b> @tra                       | nsaction_wait |

| fig.d.t.m_leaf_name | WRITE                    | WAIT_FOR_INT*                           |            |                | TE W                                    | AIT_FOR_INTER |

| .t.m_transaction_id | 1                        | 2 10                                    | 2          | 1)(2           |                                         | 2             |

| g.d.t.stream_handle | 0                        | 0 )                                     |            | 1              | )                                       |               |

| onfig.d.t.tr_handle | 0                        | 0 )                                     |            | 6              |                                         |               |

| nfig.d.t.begin_time | 57cb0                    | 53570                                   | 56662      | 57fb2          | _%                                      | 596f0         |

| config.d.t.end_time | 57cb0                    | 54b00 💆 fff                             | ****       |                | ffi                                     | ******        |

| nfig.d.t.m_recorder | <null></null>            |                                         |            | <null></null>  |                                         |               |

| g.d.t.m_sequence_id | 209                      | 1f0 🗰                                   | 208        | <b>2</b> 0е    |                                         | 214           |

| t.m_parent_sequence | @c_seq@116               | @c_seq@112 🚺 @c                         | _seq@114   | 0 @c_seq@11    | 7 XX                                    | @c_seq@120    |

| fig.d.t.m_sequencer | @sequencer@2             | @sequencer@2                            |            | @seque         | ncer@2                                  |               |

| .e0.a_config.d.t.id | 1                        | 6 <b>X</b>                              | 8          | O <b>K</b> ( 5 |                                         | 5             |

| .t.transaction_type | WRITE                    | WAIT_FOR_INT*                           | _FOR_INTER | WAIT_FOR_IN    | TE W                                    | AIT_FOR_INTER |

| onfig.d.t.type_name | transaction              |                                         |            | transaction    |                                         |               |

| onfig.d.t.type_name | transaction_rw           | //////////////////////////////////////  |            |                | /////////////////////////////////////// |               |

| onfig.d.t.type_name | transaction_write        | /////////////////////////////////////// |            |                | [[]]                                    |               |

| .a_config.sqr.caddr | caddr(3)                 |                                         | caddr(2)   | ¢              |                                         |               |

| e0.a_config.sqr.cgo | cgo(1)                   | ¢                                       | cgo(3)     | 🗰 cgo(4)       | *                                       | cgo(2)        |

Figure 2 - Classes and Transactions In A Wave Window

# XIV. CLASSES IN THE WAVE WINDOW

Problem: Seeing a class object with values at a current time is valuable, but seeing ALL the values of a class object across time is more valuable. Especially in post simulation. Use the debug tool to examine classes in the wave window over time.

Classes in the wave window are useful in two ways. Seeing a variable 't' change over time shows objects "passing through".

```

my_transaction t;

forever begin

seq_item_port.get_next_item(t);

...

end

```

The "contents" of 't' – the class member variables is also important to see. For example in a transaction going through the driver, seeing the packet priority or source and destination addresses might be a useful debug capability.

| agentA.driver.t             | A_fa@230  | <u>)                                    </u>                       |

|-----------------------------|-----------|--------------------------------------------------------------------|

| A.driver.t.delay            | 6         | )()(9)6)8)(6)(9)2)()(4)8)7                                         |

| tA.driver.t.g_id            | de1       | <b>]{[]}}},;(d);(d);(d);(();();();();();();();();();();();();(</b> |

| entA.driver.t.id            | de1       | ))))d* <mark>d*d*))d*))e*)e*)))/e*/e*/e*</mark> (                  |

| +-ver.t.loop_count          | 3         | ))))2 <mark>,3)0))</mark> 2))0)1))))0)1)2)                         |

| tA.driver.t.addr            | 81a       |                                                                    |

| tA.driver.t.data            | f0000000  | ))))2* <mark>f*}e*})}f*))1*)2*)()b*}f*}2*)</mark>                  |

| entA.driver.t.rw            | 0         |                                                                    |

| <pre>tA.driver.t.bits</pre> | 2         | XXX4 <mark>3</mark> X6XX0X(1X7XXX2X4X1X                            |

| iver.t.type_name            | e_item_A  |                                                                    |

| iver.t.type_name            | .tem_A_fa | ///seque*//s*//sequ*///seque*/                                     |

| iver.t.type_name            |           | s*////////////////////////////////////                             |

Figure 3 - Debugging Class Member Variables in a Wave Window

```

class sequence_item_A extends uvm_sequence_item;

`uvm_object_utils(sequence_item_A)

rand bit   rw ;

rand bit [31:0]addr;

rand bit [31:0]data;

struct packed {

...

} bits;

```

# XV. COLOR HIGHLIGHTS

As debug shows more and more values, it's handy to be able to color values that are found. For example, '58' is an important value in the display below.

| •          | top.e    | ed@1 |                                            | @extended@1                             |

|------------|----------|------|--------------------------------------------|-----------------------------------------|

| <b>0</b> - | top.e.id | 1    |                                            | 1                                       |

| ₽          | top.e.I  | 4    | 2 3 4 5 6 6 0 1 2 3 4                      | \ <u>5</u> \\.0\1\2\3\4\5\              |

| ₽-         | top.e.N  | 7    |                                            | 7                                       |

| <b>0</b> - | top.e.R  | 58   | <b>57 \ 46 \ 57 \ 5a \ 36 \ \)\\\\\\\\</b> | 580000000000000000000000000000000000000 |

| <b>0</b> - | top.e.x  | 3    |                                            | 3                                       |

| ₽-         | top.e.y  | 1    |                                            | 1                                       |

| ₽-         | top.e.z  | 3    |                                            | 3                                       |

#### Figure 4 - Coloring Values

Every place that '58' occurs has been colored RED.

## XVI. MONITORING RAM USAGE - MEMORY HOGS

Problem: A testbench that runs at a block level may suddenly consume all RAM when reused up in a larger block or system. Why? Who has a handle to my object? Or "Why is memory filling up?"

A UVM Testbench writer may create objects and store their handles for later processing. This happens in most scoreboards, stimulus generators and drivers. It is a common pattern. As the objects are created, they consume memory. When the handles are stored (for example in a queue), that space cannot be returned to the operating system – it is "kept" by the simulation. As more and more handles are allocated more and more space is consumed. The memory consumed by testbenches fluctuates over time growing and shrinking as tests complete. Occasionally, through coding errors and typos the allocated object handles are never removed from the storage place (from the queue). This causes the queue to grow quite large, and for the overall simulation memory requirement to increase. The space for the constructed objects is not being "free'd".

An interesting side note is that a testbench which has these "memory hogging" characteristics may run just fine at a block or sub-system level, since there are few objects allocated during the tests. When the testbench is reused in the system or at the chip level, suddenly memory requirements are out of control, and all RAM is consumed and the tests fail or crash. Without support for this feature in the debugger, a slightly different technique can help.

Usually, this accumulation of "non-free'd" objects also has a side-effect – very large dynamic data structures. Very long queues or large dynamic or associative arrays. By tracking array sizes, any large array can be flagged.

Any addition to a queue (or other memory element) could be annotated to check the size. If the size is above some threshold, then there may be a problem. For example if your scoreboard has a queue and is checking transactions pairwise in-order, there is no reason for the queue to grow beyond single digits. Certainly a queue size above 10,000 is likely a bug.

```

`define Q_PUSH_FRONT(q, item) \

if (q.size() > Q_SIZE_LIMIT) begin \

```

```

... \

end \

q.push front(item);

```

Using the new "push" functionality means change q.push\_front(item) to `Q\_PUSH\_FRONT(q, item).

```

begin

`Q_PUSH_FRONT(egress_q, transaction_h)

...

end

```

If your debug tool has the ability to track "un-free'd" handles, use it. Otherwise, you can track dynamic storage sizes using the technique above.

#### XVII. TRANSACTION DEBUG

Problem: Waves and Classes are too low level. Visualizing transactions can help the eye see key patterns. Using transactions allows the eye to see large patterns.

Transactions are like candy. The more you have, the more you want. Transactions come natively with the UVM (with limited functionality), and can be added to any testbench, whether it is a UVM testbench or otherwise. Transaction recording is really nothing more than a fancy \$display() statement. Anyplace you can put a \$display() statement, you can annotate with transaction recording.

Using transaction recording APIs is beyond the scope of this paper. Searching the literature will yield many useful references.

|   | Signal Name            | Values-C1  | 1850                       | 1900                     | 1950                     | 2000                        | 2050 2100                     | 2150         | 2200 225                     |

|---|------------------------|------------|----------------------------|--------------------------|--------------------------|-----------------------------|-------------------------------|--------------|------------------------------|

|   | Transaction            |            |                            |                          |                          |                             |                               |              |                              |

| ÷ | mm[0].mm.trans_stream1 | ority:3'h1 | trans* t                   | trans_st                 | eam1                     | trans_stream1               | trans_strea                   | mi tra       | ns_stream1                   |

| Ð | mm[1].mm.trans_stream1 | ority:3'h0 | rans_stre                  | trans_st                 | ream1 <mark>tra</mark>   | un*trans_str <mark>t</mark> | rans_stre* tran               | s_stream1 t  | rans_stream1                 |

| Ð | mm[2].mm.trans_stream1 | ority:3'h1 | t trans_s                  | tream1 tr                | ans* tr*                 | trans_stre                  | trans_stream1                 | t* trans     | _ <mark>st'</mark> trans_str |

| ÷ | mm[3].mm.trans_stream1 | ority:3'h1 | tra* trans                 | _stream:L                | trans_s'                 | trans_stream:               | 1 trans_stream                | 1 trans_str  | ream1 trans                  |

| ÷ | mm[4].mm.trans_stream1 | ority:3'h1 | t <mark>tt</mark> trans    | s_stream1                | . trans_                 | stream1 tra                 | ns_stream1                    | trans_str    | eam1 tr                      |

| ÷ | mm[5].mm.trans_stream1 | ority:3'h0 | tra <sup>‡</sup> trans_    | stream1                  | rans_1                   | trans_strea                 | m1 trans_                     | stream1 tra  | uns_stream1                  |

| ÷ | mm[6].mm.trans_stream1 |            | <mark>t*</mark> trans_st   | r*tran*                  | tran                     | s_stream1                   | trans_stream1                 | t' trans_s   | tream1 tra                   |

| ÷ | mm[7].mm.trans_stream1 | ority:3'h0 | rans_stre                  | trans_s                  | stream1                  | trans_stre                  | am <mark>1 t</mark> rans_st   | trans_strea  | am1 trans_str                |

| ÷ | mm[8].mm.trans_stream1 | ority:3'h1 | tra <mark>* tra*</mark> ti | ra* <mark>trans</mark> _ | _ <mark>*</mark> trans_s | t <mark>'t*</mark> trans_s  | * trans_stre                  | eam1 tra     | ans_stream1                  |

| ÷ | mm[9].mm.trans_stream1 | ority:3'h0 | :rans_stre                 | trans                    | _stream1                 | trans_st                    | ream1 tr* <mark>tra</mark> *t | rans_stream1 | trans_stre                   |

XVIII. MISCELLANEOUS

#### Checkpoint / Restart

Simulation are sometimes quite long running – hours, days or even weeks. Using a checkpoint enables a restore to begin from a checkpoint without all the previous simulation being repeated. Many users checkpoint their long running simulations every 3 hours. As simulation continues, bugs may be found. When a bug is found, then debug can occur by starting (restoring) from the previous checkpoint. In this way, a bug is only 3 hours of simulation away. Any convenient frequency for checkpointing can be used.

#### SEARCH

Debug is better visibility. Search can improve visibility by finding things quickly. Using search can help find the things that may be problematic – perhaps some verification engineer suspects the "exception\_entry" code is problematic. Using a powerful search can find the suspect code quickly. Powerful search is critical to better debug.

# UVM Config Debug

The UVM has a variety of data structures, one of which – the Configuration Database – is particularly hard to debug. There are UVM switches available for dumping the config database and interactions with it, but often the problems cannot be discovered with the built-in switches. The debug tool should provide some way to understand the type matching type specifications and the inner loop checking that can cause a mismatch. Use simulator command line arguments for help debugging (+UVM\_RESOURCE\_DB\_TRACE +UVM\_CONFIG\_DB\_TRACE) or use your debugger. [4]

## Macro Debug

Macros are notoriously hard to debug. Normally a macro is created for some collection of well-tested code with well-understood behavior. When a macro needs to be debugged, the debugger will need to support it. If not, the last resort is to expand the macro, and then use it expanded in-line. This is a tedious exercise, but necessary if the macro is a complicated collection of code. For example, debugging the UVM field-automation macros would be a case where a debugger or in-line expansion would be necessary.

### XIX. CONCLUSION

Debug techniques for a variety of situations have been discussed. Adopting some or all of them will improve debug productivity. They can be used alone, or combined for even more productivity. Knowing what tools are in the toolbox is the first step to more product debug.

Breakpoints, Conditional breakpoints, Instance specific breakpoints and break-on-change are all powerful ways to debug simulation problems with live simulation.

Fancy \$display and waveforms with classes and transactions can be used in live simulation and in post-simulation debug.

Whatever bugs you may be trying to uncover, the best way to do it is to know what tools you have available.

#### XX. REFERENCES

[1] SystemVerilog Language Reference Manual, <u>http://standards.ieee.org/getieee/1800/download/1800-2012.pdf</u>

- [2] UVM Language Reference Manual, http://www.accellera.org/images/downloads/standards/uvm/uvm\_users\_guide\_1.2.pdf

- [3] *"Thinking In Transactions"*, DVCON India 2017, Rich Edelman, Mustufa Kanchwala.

- [4] "Go Figure UVM Configure" The Good, The Bad, The Debug", DVCON Europe 2016, Rich Edelman, Dirk Hansen.