Calling All Checkers: Collaboratively Utilizing SVA In UVM Based Simulation

> Hui C. K. Zhang Broadcom/Avago Tech

## **Abstract**

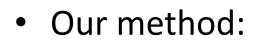

Scoreboard and SVA are two commonly used self-checking mechanisms in verification. However in common practice, they are employed independently without any elaboration except in the interface. This paper presents a new method and practical solution to utilize SVA collaboratively in UVM based simulations. By combining SVA and scoreboard in conjunction with uvm\_config\_db, control event and informational parameters can be shared and communicated bidirectional between SVA and scoreboards to quicken and ease the debug.

### Keyword

Scoreboard; SVA; UVM; uvm\_config\_db;

# Introduction

• Common practice:

SVA in formal analysis

Scoreboard in simulation

SVA in interface & module

Combine Scoreboard &

SVA In UVM based

simulation

Check forward &

Backward

# Scoreboard

#### • Pro:

- Major checker in classed based simulation

- Predicator : Reference

- Model to expect RTL behavior

- Comparator: report Pass/Fail information

- Con:

- Only report high level outline of the failure at transaction level

- Maybe many clock cycles later after the error source

- Usually get info from monitor (interface signal)

- Lack inside information of

- RTL (internal protocol & FSM)

## SVA

#### • Pro:

• Con:

- Used in formal analysis

- Used in interface in Class based simulation or binding in TB module

- Concurrent SVA not allowed in class

- Simulation performance penalty due to the checking in every clock ticks

# uvm\_config\_db: the Connecting Bridge

➢Allows objects and variables been stored and retrieved across various verification components within different hierarchical setup in testbench.

Use lookup strings and a pair of set/get functionsuvm\_config\_db function syntax:

class uvm\_config\_db#(type T=int) extends uvm\_resource\_db#(T)

static function void uvm\_config\_db#(type T)::set(uvm\_component cntxt,

string inst\_name, string field\_name, T value)

static function bit void uvm\_config\_db#(type T)::get(uvm\_component cntxt,

string inst\_name, string field\_name, ref T value)

## **Our Solution**

# **Execution Flow**

- 1. Run simulation. Record the interest point and parameters reported by scoreboard.

- 2. Create property and Pass the control parameters to SVA through uvm\_config\_db.

- 3. Run simulation with the same seed with SVA.

- 4. Debug the failure reported by SVA.

- 5. Adjust control parameters adaptively and repeat the step 3-5 if required. (optional for backward case).

- 6. Feedback from SVA can be used to control simulation (Optional).

# Application

• Forward Method:

Look forward in time

Suit for error propagation and recovery

Check for low power state transition

• Backward method:

➤ Backward in time

Back trace the sources of

errors

Identify error sources

## **Application: Forward Flow**

class sb comparator extends uvm component; uvm event sb sva event; bit sb sva chk en; function void build phase (uvm phase phase); sb sva event = new ("sb sva event"); uvm config db#(uvm event)::set( null, ""\*","sb\_sva\_event",sb\_sva\_event) endf;unction task run phase(uvm phase phase); forever begin fork cmp exp fifo.get(exp tran); cmp act fifo.get(act tran); join compare(exp tran,act tran); if (comp error) begin sb sva event.trigger(); uvm config db#(bit)::set( null, "\*", "sb sva chk en",1); end endtask ... endclass

#### m o dule top

```

import sva pkg::*;

uvm_event tb_sva_event;

bit sb sva chk en=0;

sva_cfg sva_cfg1;

dut dut 1(.*);

initial begin

sva cfg1 = new();

end of elaboration ph.wait for state(UVM PHASE DONE,UVM EQ);

void'(uvm_config_db #(uvm_event)::get(nul1,"","sb_sva_event",tb_sva_event);

tb_sva_event.wait_trigger();

void'(uvm_config_db #(bit)::get(null,"","sb_sva_chk_en",sb_sva_chk_en);

sva cfg::sb sva chk en = sb sva chk en;

....

end

a sb forward: assert property

(p sb forward(sys clk,rst n,sva cfg::sb sva chk en,state))

`uvm info("tb sva",$sformatf("SVA PASSED \n"));

else `uvm error("tb sva",$sformatf("SVA FAILED\n")

endmodule

```

# **Property Package**

• Forward Method:

package sva\_pkg;

property p\_sb\_forward(clk,rst\_n,sb\_sva\_chk\_en,state);

@ (posedge dk) disable iff(!rst\_n ||!sb\_sva\_chk\_en)

state==STATE\_ERR|=>##[1:5] (STATE==RECOVERY|| STATE==NORMAL);

endproperty : p\_sb\_forward

```

property p_sb_forward_lp(clk,rst_n,sb_sva_chk_en,state);

@ (posedge_clk) disable iff (!rst_n ||!sb_sva_chk_en)

state==STATE_PML1|=>##[1:10] (STATE==PML2);

endproperty : p_sb_forward

```

class sva\_cfg extends uvm\_object; static int sb\_sva\_chk\_en; endclass

endpackage

## • Backward Method:

\$past(state,2)==STATE\_PRE2||\$past(state,1)==STATE\_PRE1; endproperty : p\_sb\_backward

class sva\_cfg extends uvm\_object; static int\_sb\_chk\_en; static int\_sb\_time0; endclass

endpackage

# Conclusion

- A new method and practical solution to utilize SVA collaboratively in UVM based simulations, as by combining SVA with scoreboard in conjunction with uvm\_config\_db which share & pass control event and informational parameters.

- It can facilitate the debugging process and localize the root cause as well as analyze the preceding and following protocol/sequences efficiently.

- It can minimize the SVA simulation performance penalty .