# Best Practices in Verification Planning Benjamin Ehlers

Presented by

Paul Carzola – Senior Architect

Cadence Design Systems

#### Feb 2013

Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire, C-Ware, the Energy Efficient Solutions logo, Kinetis, mobileGT, PEG, PowerQUICC, Processor Expert, Qorl/Q, Qorivva, StarCore, Symphony and VortiQa are trademarks of Freescale Semiconductor, Inc., Reg, U.S. Pat. & Tm. Off. Alrfast, Beekfit, BeeStack, CoreNet, Flexis, Layerscape, Magnity, MXC, Platform in a Package, Qorl/Q Converge, QuICC Engine, Ready Play, SafeAssure, the SafeAssure logo, SMARTMOS, Tower, TurboLink, Vybrid and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2013 Freescale Semiconductor, Inc.

# **Discussion Topics:**

- Verification planning problems

- Planning challenges to address

- Notion of Executable Verification Plan

- Recommended verification solution

- Example verification planning flow

- Value Analysis

- Failure to Plan Means Planning to Fail

- Verification planning, the most crucial step

- Improves quality

- Improves efficiency

- Methodology based on actual experiences on an SoC

- Includes strategy, planning, changes and closure

- Begins with culture of Metric Driven Verification

- Follows a well organized process

- Enhanced with the executable verification plan

# **Verification Planning Problems:**

- Verification planning as an afterthought

- Lack of organized or standardized flow

- Absence of verification methodologies

- Lack of process for changing and evolving requirements

- Fear of verification planning costs

- Limitations in Technology

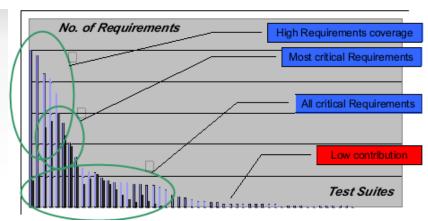

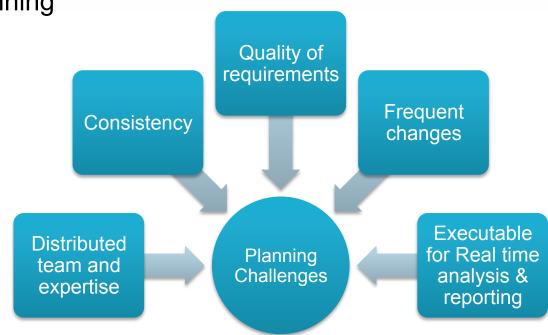

# **Planning Challenges to Address:**

- Large scale distributed planning approach:

- large team of engineers

- variety of individual styles, priorities, experience

- Enable and maintain Consistency/Coherency

- Quality of design documentation and design requirements

- Frequent design changes

- Needs to support concept of Executable Verification Plan

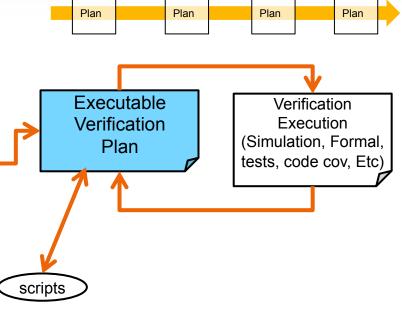

### **Codified and Executable Verification Plan**

- Single point of source across entire verification flow

- Defines the scope of verification

- Describes all key design features

- Supports link to the verification metrics

- testcases, checkers, monitors, coverage, results

- Link to specifications

Specifications

- Planning for the total verification project

- complete and coherent verification flow

- · Flexible for scripting

- What makes a plan "executable"?

- The notion to define and refine your verification strategy

- The notion of collecting all run time results to make the plan dynamic and alive

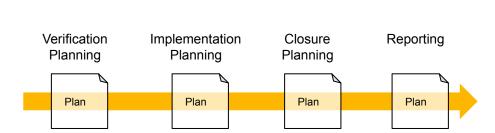

Implementation Planning

Closure

**Planning**

Reporting

Verification

**Planning**

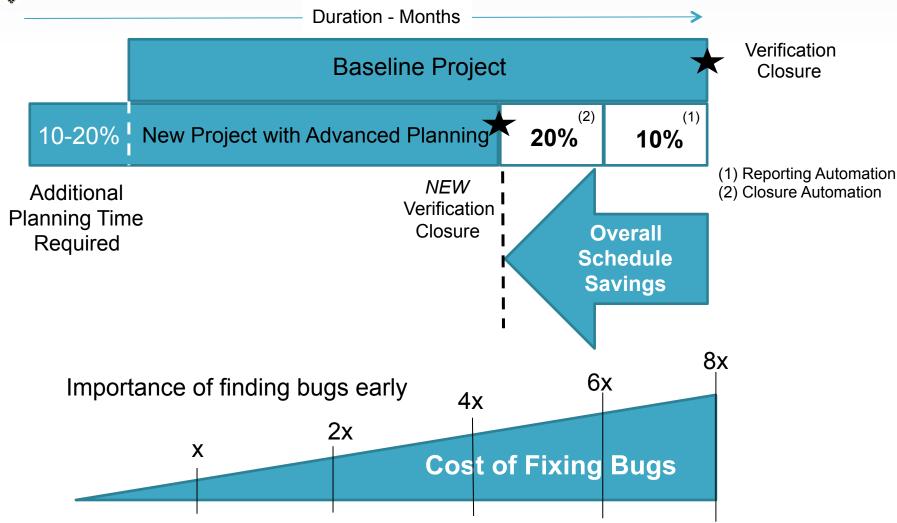

# How Executable Plan Recovers Cost of Up-Front Planning

- Testbench design begins in planning

- Planned coverage, checks, tests cases provide guidance on testbench code and tests cases that need to be written

- The final verification results and completions criteria are built into the executable plan

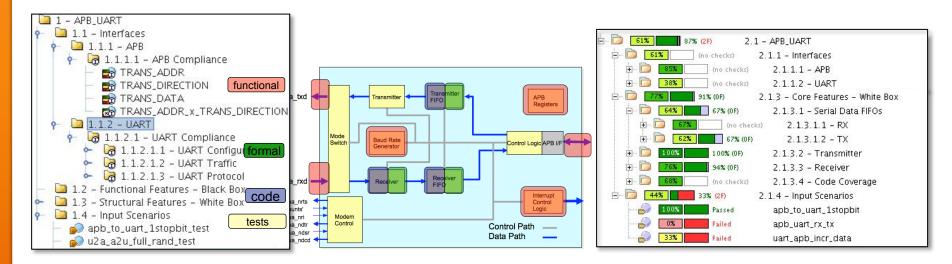

# **Executable Plan: Linking all the key elements**

2.1 - APB\_UART 2.1.1 - Interfaces

2.1.1.2 - UART

2.1.3 - Core Features - White Box 2.1.3.1 - Serial Data FIFOs

> 2.1.3.1.1 - RX 2.1.3.1.2 - TX

2.1.3.2 - Transmitter

2.1.3.3 - Receiver

2.1.3.4 - Code Coverage

2.1.4 - Input Scenarios

apb\_to\_uart\_1stopbit

apb\_uart\_rx\_tx

uart\_apb\_incr\_data

Requirements Objectives

> Heterogeneous Verification Tools (ie Formal)

Specification

Test

Scenarios

Distributed Team and Plans

The verification plan becomes the anchor to connect teams and technologies together

Error

Conditions

After

Execution

# **Best Practice Planning Methodology**

- Successfully used at Freescale on a large SoC project

- With a widely distributed verification team

All very important aspects to the Planning Methodology

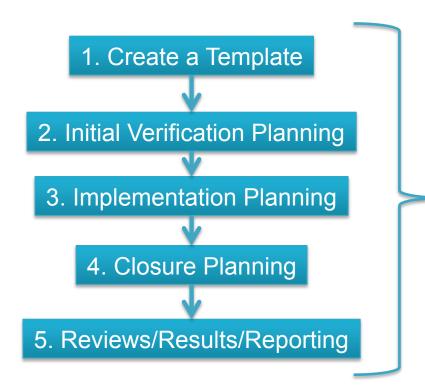

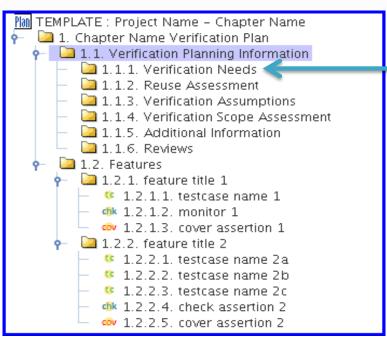

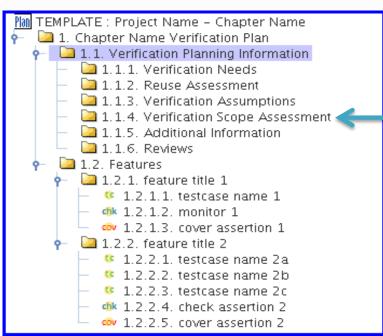

### 1. Create a Template:

- Enable and help ensure Consistency and Coherency from the beginning

- Provides a prescriptive approach to follow

- May seem trivial, unnecessary...

- VITAL STEP

- Make sure template supports merging/importing multiple plans

- distributed verification approach

- Include detailed explanation descriptions

```

TEMPLATE: Project Name - Chapter Name

🞑 1. Chapter Name Verification Plan

1.1. Verification Planning Information

1.1.1. Verification Needs

1.1.2. Reuse Assessment

1.1.3. Verification Assumptions

1.1.4. Verification Scope Assessment

1.1.5. Additional Information

1.1.6. Reviews

1.2. Features

🞑 1.2.1. feature title 1

1.2.1.1. testcase name 1

4 1.2.1.2. monitor 1

1.2.1.3. cover assertion 1

1.2.2. feature title 2

1.2.2.1. testcase name 2a

1.2.2.2. testcase name 2b

1.2.2.3. testcase name 2c

4 1.2.2.4. check assertion 2

1.2.2.5. cover assertion 2

```

#### 2. Initial Verification Planning: Verification Needs

- Design documents

- Tools

- Models behavior or functional

- Design blocks that cannot be modeled

- Protocols used

- Testbench components

- Purchase vs Make components

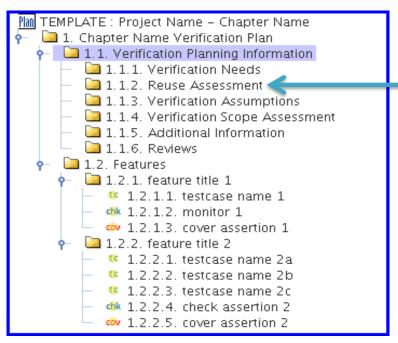

#### 2. Initial Verification Planning: Reuse Assessment

- Determine how much can be reused from previous projects

- Test benches, checks, tests,VIP, etc...

- Don't under scope

- Team reuse and dynamics

- What teams work well together vs new teams.

- Determine what needs to be developed

- Review existing documentation

- What designers are available for questions

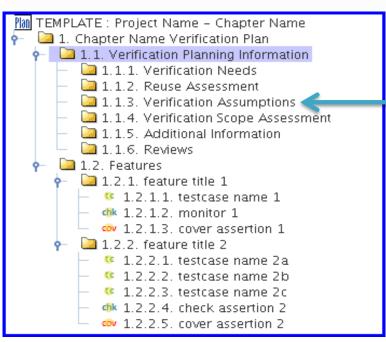

#### 2. Initial Verification Planning: Verification Assumptions

- Assumptions are all too often left unspoken leading to design features being misinterpreted

- Document and review any assumptions

- Review with designer early

- Have face-to-face meetings

- Document all findings

- E.g.

- Feature X cannot be verified in digital, needs Analog Mixed Signal

- System level signal needs to be modeled during SoC verification

- · Checklist can be useful here

- Some captured during post mortem time

- Use action item system

- Make this a committed contract so there are no surprises

#### 2. Initial Verification Planning: Verification Scope Assessment

- Consider all the available capabilities available to you: directed test, constrained random, formal, checks, coverage properties, code coverage, etc...

- Methodology doc for how to choose.

- Iterative process

- Take inputs from reuse assessment

- Understand the cost to create new test benches

- Determine the skill set of the verification engineers

# 3. Implementation Planning: Plan Creation

- The essence of successful verification planning

- Verification must driven by:

- Requirements Driven from design requirements

- Feature Driven from design specifications

- Priority Driven from the priority of Features

- Organize the verification plan according to design feature groups

- Testbench and stimulus can be extracted

```

The UART can receive and transmit data in a configurable word format and size. These configuration features are common to both the Rx and Tx traffic. All combinations of configuration shall be tested.

Both Rx and Tx sides must be verified to operate in all programmable word data lengths as indicated in the UART functional Spec. The character length select register defines the number of bits in each character. Those values are: 5, 6, 7 and 8 bits.

Cov The Rx and Tx sides of the UART can produce traffic with different levels of parity. The Parity type selections the expected parity to check on receive and the parity to generate on transmit. Those values are: even with, odd parity, 'forced to 0' parity (space), 'forced to 1' parity (mark), no parity set. We are also interested in verifying all combinations of the data length with the parity mode. We are also interested in verifying that all parity modes that have been active with all values of the data length.

Cov Both UART Rx and Tx paths support the configuration of various number of stop bits to detect on the support the configuration of various number of stop bits to detect on the support of the parity. Those values are: 1 stop bit, 5 stop bits, 2 stop bits.

```

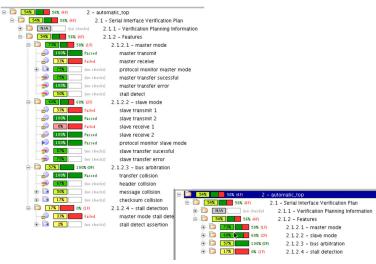

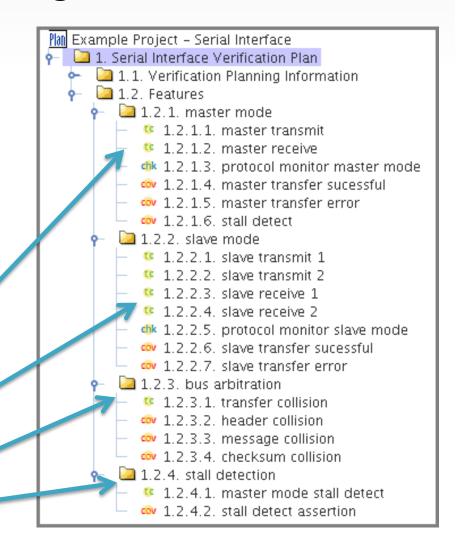

# 3. Implementation Planning: Correlated Results

```

Example Project - Serial Interface

1. Serial Interface Verification Plan

1.1. Verification Planning Information

1.2. Features

1.2.1. master mode

1.2.1.1. master transmit

1.2.1.2. master receive

4 1.2.1.3. protocol monitor master mode

1.2.1.4. master transfer sucessful

1.2.1.5. master transfer error

1.2.1.6. stall detect

1.2.2. slave mode.

1.2.2.1. slave transmit 1.

1.2.2.2. slave transmit 2

1.2.2.3. slave receive 1

1.2.2.4. slave receive 2.

4 1.2.2.5. protocol monitor slave mode

1.2.2.6. slave transfer successful.

1.2.2.7. slave transfer error.

1.2.3. bus arbitration

1.2.3.1. transfer collision

1.2.3.2. header collision.

1.2.3.3. message collision

1.2.3.4. checksum collision

1.2.4. stall detection

1.2.4.1. master mode stall detect

1.2.4.2. stall detect assertion.

```

- Link to tests, checks, cover groups, code coverage, etc...

- Brings the planning to closure into full circle

```

▽ O∰ ovm test top

▽ O∰ ve

apb0

🛂 apb_uart0

🗸 🔾 🛂 uart 0

🗸 🔾 🛂 monitor

♪ ⇔ arx traffic cg

□■ PARITY ERROR GEN

⟨□□□ FRAME BREAK

¬ ← □ uart_trans_frame_cg

➡

stop bits1

⟨□□□ NUM STOP BITS

←

■

DATA LENGTH

Output

Description

💳 PARITY MODE

← PARITY_ERROR

```

#### 4. Closure Planning

stall detect assertion

- Determine the signoff and completion criteria

- Don't wait until the end

- Verification Completion Criteria must be based on metrics

- Coverage metrics:

2 - automatic\_top

2.1.2 - Features

Executable verification plan includes direct coverage correlation

2.1 - Serial Interface Verification Plan

2.1.2.1 - master mode 2.1.2.2 - slave mode 2.1.2.3 - bus arbitration 2.1.2.4 - stall detection

2.1.1 - Verification Planning Information

56% (4F)

# 5. Plan for Reviews/Results/Reporting

- Plan for key milestone reviews and get commitment up front

- If not, they don't get done

- Need a consistent review flow and formats

- Executable verification plan

- includes direct results correlation

- Report merge and roll-up

|       | А            | В                        | С                | D               | E                                                           | F           |     |

|-------|--------------|--------------------------|------------------|-----------------|-------------------------------------------------------------|-------------|-----|

| 1     | Results      |                          |                  |                 |                                                             |             |     |

| 2     | Total        | 85                       |                  |                 |                                                             |             |     |

| 3     | passed       | 43                       |                  |                 |                                                             |             |     |

| 4     | failed       | 22                       |                  |                 |                                                             |             |     |

| 5     | incomplete   | 20                       |                  |                 |                                                             |             |     |

| 6     |              |                          |                  |                 |                                                             |             |     |

| 7     | Status 💌     | Test Name                | Plan Name        | test group      | Error Description                                           | known fails | •   |

| 8     | failed       | master_transmit          | Serial Interface | master_mode     | comparison error! Expected data = 'h24 , Actual Data = 'h27 | TKT00428    |     |

| 9     | failed       | slave_transmit_1         | Serial Interface | slave_mode      | comparison error! Expected data = 'h48 , Actual Data = 'h47 | TKT00428    |     |

| 10    | failed       | master_mode_stall_detect | Serial Interface | stall_detection | FATAL ERROR! State machine in unknown state                 |             |     |

| 11    | incomplete   | slave_transmit_2         | Serial Interface | slave_mode      | (None)                                                      |             |     |

| 12    | incomplete   | transfer_collision       | Serial Interface | bus_arbitration | (None)                                                      |             |     |

| 13    | passed       | master_receive           | Serial Interface | master_mode     | (None)                                                      |             |     |

| 14    | passed       | slave_receive_1          | Serial Interface | slave_mode      | (None)                                                      |             |     |

| 15    | passed       | slave_receive_2          | Serial Interface | slave_mode      | (None)                                                      |             |     |

|       |              |                          |                  |                 | Halt_mon: Unexpected transition of signal                   |             |     |

| 16    | failed       | halt_mode_recovery       | Core             | halt_mode       | core_transfer_complete                                      |             |     |

|       |              |                          |                  |                 | Halt_mon: Unexpected transition of signal                   |             |     |

| 17    | failed       | halt_mode_entry          | Core             | halt_mode       | core_transfer_complete                                      |             |     |

| 18    | passed       | bridge_transfer_1        | Core             | bridge_gasket   | (None)                                                      |             |     |

| 19    | passed       | bridge_transfer_2        | Core             | bridge_gasket   | (None)                                                      |             |     |

|       | passed       | bus error detect         | Core             | bus seq         | (None)                                                      |             |     |

| 14 -4 | → →   regres | sion_results / 🐫         |                  |                 |                                                             |             | - b |

# Formalized Planning: Value

# Summary

- Verification Planning is not simply a task that is done once and forgotten

- It is a living, breathing and executable methodology saving time and resources

- There is a cost but with a tremendous set of benefits

- Analysis and reporting is automated

- Saved 10%-40% in Freescale projects