# Be a Sequence Pro to Avoid Bad Con Sequences

Presenter: Mark Litterick

Contributors: Jeff Vance, Jeff Montesano

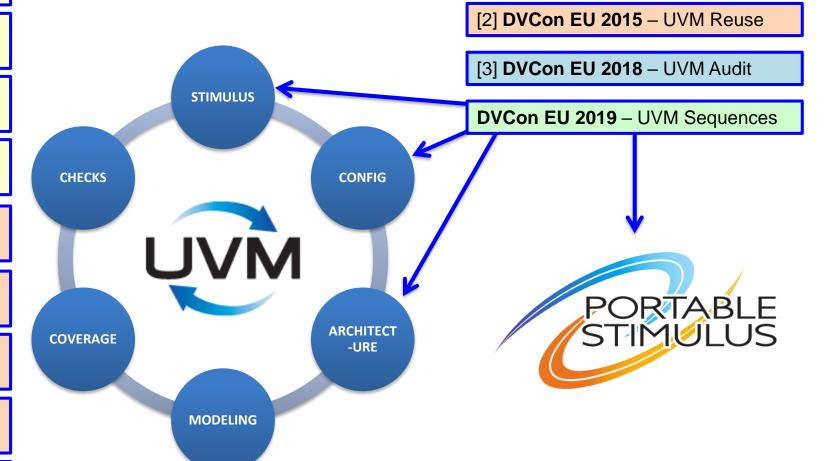

### **UVM Overview**

**Verification Environment**

Universal Verification Methodology (UVM)

SystemVerilog IEEE1800

Questa<sup>TM</sup>

Xcelium™

VCS<sup>TM</sup>

- Application-specific code

- Uses UVM & SystemVerilog

- Open source (Apache)

- Class library & methodology

- Facilitates interoperability

- Uses SystemVerilog

- Supported by all simulators

- Multi-language simulators

- VHDL, Verilog, SV, SC

### **UVM** provides:

- base class library

- methodologyfor using it

# but methodology allows flexibility

- it is necessary

- best practices

### **Tutorial Content**

Behind the Scenes of the UVM Factory

Advanced UVM Register Modeling & Performance

Demystifying the UVM Configuration Database

Effective **Stimulus** & Sequence Hierarchies

Vertical & Horizontal Reuse of UVM Environments

Configuration Object & config\_db Usage

Parameterized Classes, Interfaces & Registers

Adaptive Protocol Checks

- Config Aware **Assertions**

Self-Tuning Functional Coverage

[1] **DVCon EU 2014** – Advanced UVM

### **Problem Statement**

### **UVM** sequences are vital for verification success

#### **Need Control**

- Reach scenarios

- Find and isolate bugs

- Close coverage

### **Manage Complexity**

- Debug constraint failures

- Reduce mistakes

- Transfer knowledge

#### **Need Reuse**

- Within a sequence library

- With derivative projects

- For generic VIP

### **UVM** sequences are often not applied appropriately

#### **Insufficient API**

- Can't control from tests

- Can't isolate features

#### **Too Complex**

- Intractable constraint failures

- Invalid stimulus

#### **Not Reusable**

- Copy/pasted routines

- Tied to a specific DUT

Poor visibility of project status

No risk-management of features

### **Tutorial Outline**

- Background to tutorial

- Introduction to sequences what are they & why do we care

- Sequence execution masters, reactive slaves, streaming data

- Sequence guidelines improve control, complexity, & reuse

- **Verification productivity** *strategies to manage features*

- Portable Stimulus Considerations how PSS impacts sequences

- Conclusion & references

What are UVM sequences and why do we care?

### **INTRODUCTION TO SEQUENCES**

# What is a Sequence?

### UVM sequence class encapsulates constrained-random stimulus

```

class access seq extends base seq;

rand master enum source;

rand cmd enum cmd;

rand bit[15:0] addr;

bit[15:0] data;

constraint legal c {

cmd != NOP;

addr <= MAX ADDR C;</pre>

task body();

if (p sequencer.cfg.mode == ACTIVE) *

```

Sequences can be **reused**, **extended**, **randomized**, and **combined** sequentially and hierarchically in *interesting* ways to produce *realistic* stimulus... [UVM ref. man.]

Random control knobs for users

Constraints on random options

**Procedural body**

Access resources via sequencer

### Comparing Sequences and Tasks

```

class access_seq extends base_seq;

rand master_enum source;

rand cmd_enum cmd;

rand bit[15:0] addr;

bit[15:0] data;

constraint legal_c {...}

task body();

...

```

```

task access_task (

master_enum source,

cmd_enum cmd,

bit[15:0] addr,

ref bit[15:0] data);

// task body

...

```

### Both **sequences** and **tasks**:

- encapsulate a scenario

- provide control options

- have procedural body

### **Executing Sequences and Tasks**

```

class read test extends uvm test;

task run phase (uvm phase phase);

access seq a seq;

`uvm do with(a seq,{

source == PORT A;

cmd == READ;

addr == 'hA0;

})

if (a_seq.data == 'h55)

```

```

class read test extends uvm test;

task run phase (uvm phase phase);

bit[15:0] rdata;

access task (

.source (PORT A),

.cmd (WRITE),

.addr ('hA0),

.data (rdata)

if (rdata == 'h55)

```

In the most **basic** cases, tasks and sequences can be equivalent...

# Why Bother Using Sequences?

#### **Tasks**

- Arguments are mandatory (or fixed by default)

- Users must randomize args

- No built-in arg validity checks

- Awkward to return data (use ref arguments)

- No built-in access to resources

- Adding args breaks existing code

#### **Sequences**

- Arguments are optional (random by default)

- Legal randomization is built-in

- Constraints validate user options

- Caller can access any data (with sequence handle)

- Access to resources via sequencer

- Adding options has minimal impact

# **Orchestrating Stimulus**

# Sequence API Strategy

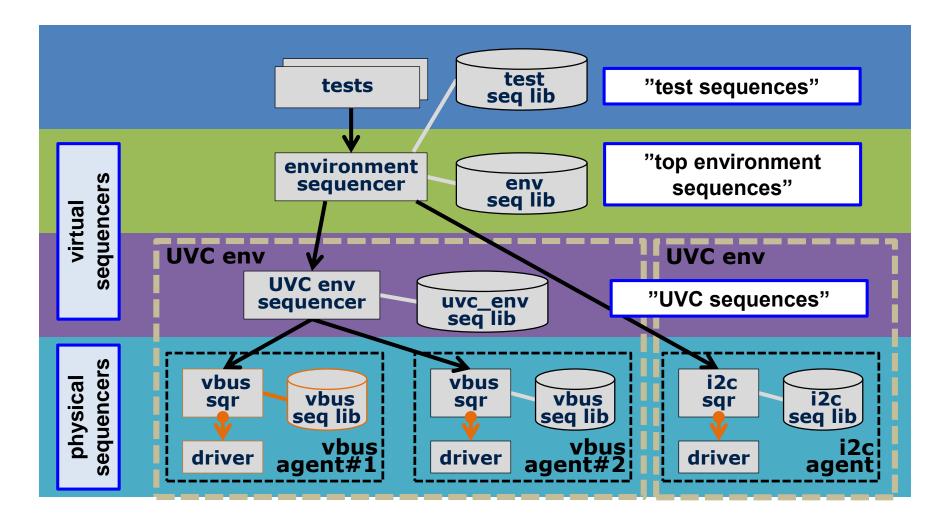

# Sequence Layer Roles

| LAYER |        | CONSTRAINTS             | PRIMARY PURPOSE                |

|-------|--------|-------------------------|--------------------------------|

| TEST  |        | Test scenario           | Highest-level sequence         |

| ТОР   | User   | DUT use cases/scenarios | API for test writer            |

|       | Lower  | System requirements     | Scenario building blocks       |

| UVC   | User   | Protocol use cases      | Encapsulates sequencer(s)      |

|       | Middle | Protocol operations     | Encapsulates basic operations  |

|       | Low    | Low-level requirements  | Data formatting                |

|       | Item   | Enforce legality        | Support all possible scenarios |

Reduce complexity at each layer

Control with intuitive APIs

Sequences decoupled and reusable

Each layer resolves a subset of random options

Benefits both directed and random tests

Existence of some layers is application dependent

How different types of sequences are executed

# **SEQUENCE EXECUTION**

### Sequence Execution Overview

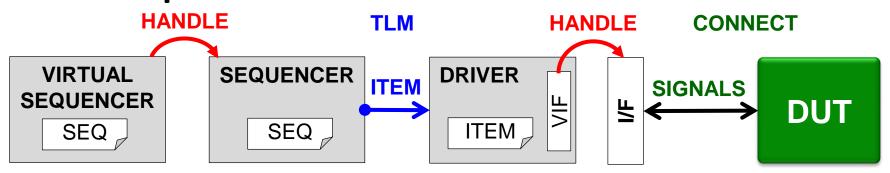

### Sequences execute on sequencers to control stimulus

- virtual sequences coordinate and execute one or more sequences

- physical sequences generate items which are passed to drivers

- drivers interact with DUT via signal interface

### Sequence execution affected by:

- verification component role proactive or reactive

- sequencer type virtual (no item) or physical (item)

- item content single transaction or stream description

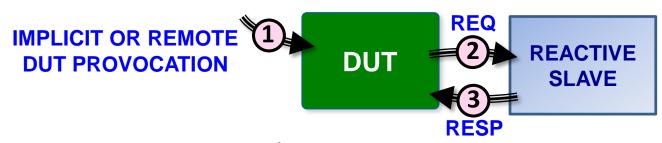

### **Proactive Masters & Reactive Slaves**

Proactive Masters:

- Test controls when sequences are executed on the UVC and timing of requests to DUT

- Stimulus blocks test flow waiting for DUT response

- Reactive Slaves:

- Timing of DUT requests is unpredictable (e.g. due to embedded FW execution)

- UVC must react to request and respond autonomously without blocking test flow

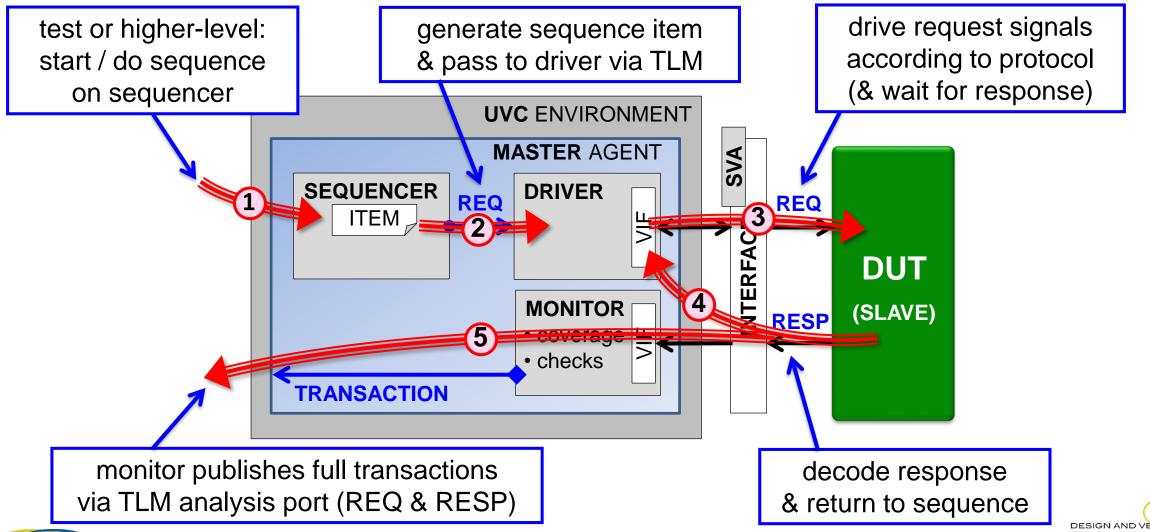

# Proactive Master Operation

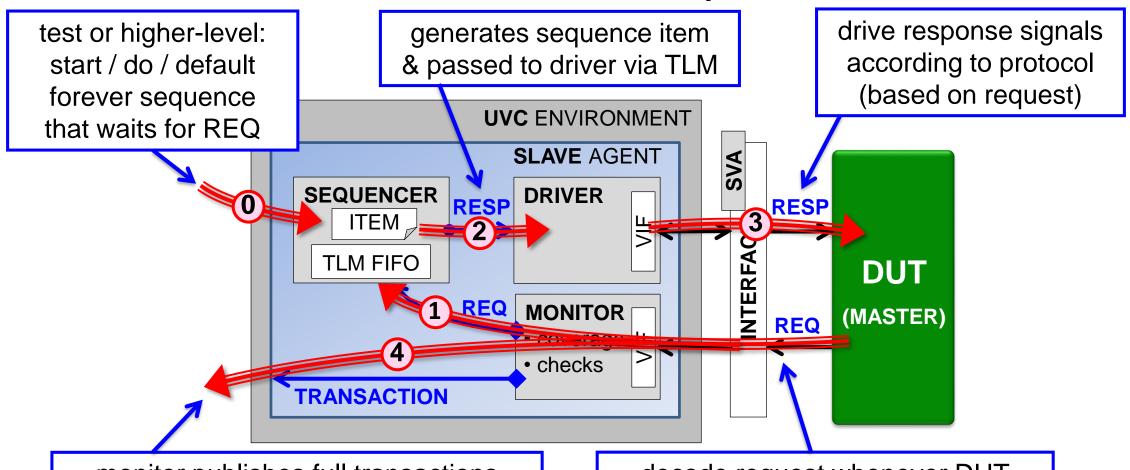

# Reactive Slave Operation

monitor publishes full transactions via TLM analysis port (REQ & RESP)

decode request whenever DUT initiates it & publish to sequencer

# Sequence Types

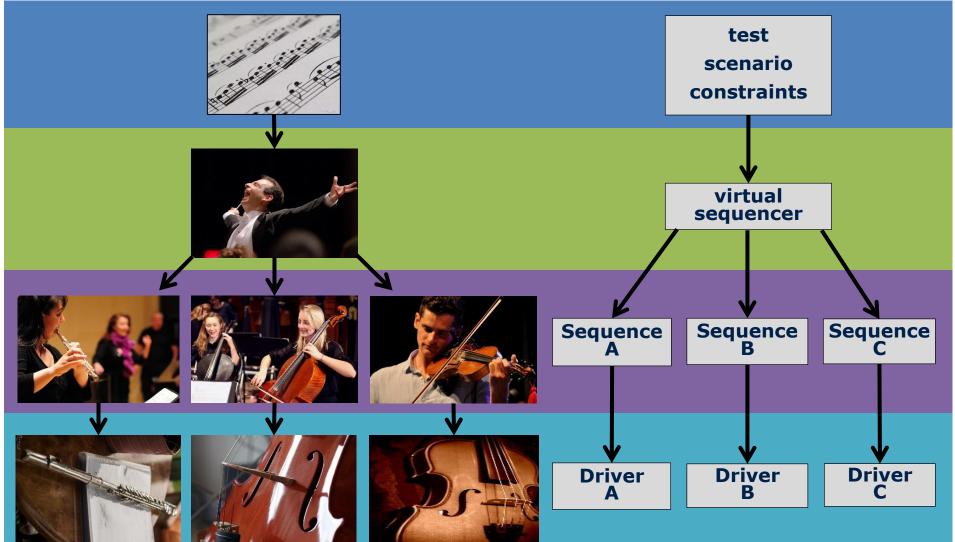

• Virtual Sequences: Control *other* sequences

Normal Sequences: Generate a single transaction

• Streaming Sequences: Generate autonomous stimulus

# Virtual Sequences

### • Virtual sequences:

- do not directly generate an item

- coordinate & execute other sequences

- define scenarios, interaction & encapsulation

- high-level scenarios

- parallel transactions

- sequential transactions

- multiple agents/UVCs

- constraint wrapper

- resource encapsulation

### Key characteristics

- full control over all child sequences

- may be blocked by time-consuming sequences

- multiple virtual sequences may run at same time (nested or parallel) on same virtual sequencer

Must target different resources (not possible for physical sequencers)

# Virtual Sequence

```

class my_virtual_seq extends uvm_sequence;

AGENT

// rand fields ...;

// constraints ...;

DUT

fork multiple sequences in parallel

task body();

bus poll fifo seq poll fifo seq;

i2c send data seq send data seq;

fork

`uvm do with(poll fifo seq, {

execute on this virtual sequencer

timeout == 1ms;

(targets different physical sequencer)

`uvm do on with(send data seq, p sequencer.i2c sequencer,{

slave == 1;

data == local::data;

execute on referenced

physical sequencer

join

```

**ENV**

# Normal Sequences

### Normal sequences use a sequence item to:

- Generate stimulus via a driver

- Describe required transaction-level stimulus

- Define a single finite transaction

- bus transactions

- data packet

- power on/reset

### Key characteristics:

- Driver is not autonomous

- Fully controllable from virtual sequences

- Sequence handshake is blocking

- Sequence items handled consecutively

Return after **complete** transaction (& response)

Proactive Master Sequence

```

UVC ENV

class my_master_request_seq extends

MASTER AGENT

uvm sequence # (my master seq item);

rand cmd enum

cmd;

rand bit[31:0] addr;

rand bit[31:0] data[];

my master seq item m item;

generate request item

task body();

based on sequence knobs

`uvm do with(m item, {

m item.m cmd == local::cmd;

m item.m addr == local::addr;

foreach (local::data[i]) m item.m data[i] == local::data[i];

})

```

**DUT**

### **Proactive Master Driver**

```

MASTER AGENT

class my master driver extends uvm driver# (my master seq item);

my master seq item m item;

task run phase(...);

forever begin

seq item port.get next item(m item);

drive item(m item);

seq item port.item done();

standard driver-sequencer interaction

end

endtask

task drive_item(my master seq item item);

drive request signals to DUT

endtask

(based on sequence item fields)

endclass

```

**DUT**

**UVC** ENV

Reactive Slave Sequence

```

class my_slave_response_seq extends

SLAVE AGENT

uvm sequence # (my slave seq item);

my slave seq item m_item;

DUT

call forever loop inside sequence

my transaction m request;

(sequence runs throughout phase:

task body();

...do not raise and drop objections!)

forever begin

p sequencer.request fifo.get(m request);

wait for a transaction request

case (m request.m direction)

(fifo.get is blocking)

READ:

`uvm do with(m item,{

m item.m resp kind == READ RESPONSE;

m item.m delay <= get max delay();</pre>

m item.m data == get data(m request.m addr);

generate response item

based on observed request

```

**UVC** ENV

### Reactive Slave Driver

```

SLAVE AGENT

class my_slave_driver extends uvm_driver # (my slave seq item);

my slave seq item m item;

DUT

task run phase(...);

forever begin

seq item port.get next item(m item);

standard driver-sequencer interaction

drive item(m item);

seq item port.item done();

drive response signals to DUT

end

(based on sequence item fields)

endtask

task drive_item(my slave seq item item);

identical code structure

to proactive master

endtask

```

endclass

**UVC** ENV

[4] Mastering Reactive Slaves in UVM – Verilab, SNUG 2016

# Streaming Sequences

- Streaming is a stimulus pattern where:

- Item defines repetitive autonomous stimulus

- Driver generates derived patterns on its own

- clock generators

- background traffic

- analog waveforms (real number models)

- Key characteristics for successful streaming include:

- Sequences (& config) control the autonomous behavior

- Sequence handshake must be non-blocking

Sequences can run forever

Operation can be interrupted by a new operation

Safely stopped and started again

# Streaming Sequence

```

UVC ENV

class my_ramp_seq extends uvm_sequence # (my_analog_seq_item);

ANALOG AGENT

rand real start;

rand real step;

DUT

random real and time control knobs[*]

rand time rate;

my analog seq item m item;

real and time constraints

// constraint start inside {[0.0:0.75]};

// constraint rate inside {[1ps:100ns]};

generate normal sequence item

task body();

constrained by control knobs

`uvm do with(m item, {

m item.m start == local::start;

m item.m step == local::step;

totally normal physical

m item.m rate == local::rate;

sequence structure

```

[\*] Or use random integers with scaling factor for real and time values

# Streaming Driver

```

ANALOG AGENT

class my_analog_driver extends uvm_driver # (my_analog_seq_item)

my analog seq item m item;

DUT

call item done before drive item

task run_phase(...);

to pass control back to sequencer

forever begin

blocking peek waits for new item

seq_item_port.get_next_item(m item);

seq item port.item done();

fork

task drive item (my analog seq item item);

seq item port.peek(m item);

real value = item.start;

drive item(m item);

forever begin // ramp generation

join any

vif.data = value;

disable fork;

#(item.rate);

end

value += item.step;

endtask

... // saturation & looping

end

till drive_item task when new item

drive request pattern forever

(unless new item received)

endtask

```

**UVC** ENV

How to maximize the benefits of using sequences

### **SEQUENCE GUIDELINES**

# Sequence Constraint Guidelines

- Produce legal stimulus by default

- Use sequence layers to isolate constraints

- Minimize the number of control knobs

- Use dedicated constraint blocks to support extensibility<sup>[5]</sup>

- Use soft contraints carefully and sparingly<sup>[5]</sup>

- Use descriptor objects to encapsulate complex contraint sets<sup>[5]</sup>

- Use policy classes to redefine constraints and bypass layers<sup>[6]</sup>

- [5] Use the Sequence, Luke Verilab, SNUG 2018

- [6] SystemVerilog Constraint Layering via Reusable Randomization Policy Classes John Dickol, DVCon 2015

# Produce legal stimulus by default

```

class bus burst seq extends base seq;

Provide 0, 1 or more

rand int addr; // start address

inline constraints

rand int length; // burst length

// other fields (direction, data, etc.)

Legal stimulus

guaranteed

constraint legal c {

addr%4 == 0;

length inside {16,64,256,1024};

Constraint solver

addr + length <= p sequencer.cfg.get max addr();</pre>

detects illegal values

illegal combination?

address misaligned?

// user code examples

`uvm do(burst seq)

any burst

`uvm do with(burst seq, {addr == 'h4321;}) /// any length

`uvm do with(burst seq, {length == 256;}) / // any address

`uvm do with(burst seq, {addr == 'hFFF0; length == 1024;})

```

### Use sequence layers to isolate constraints

```

class bus_burst_seq extends base_seq;

rand int addr; // start address

rand burst_t burst; // burst type

... // other fields (direction,

constraint legal_c {

burst inside {WRAP,INCR};

(burst == INCR) -> addr%4 == 0; // INCR m

...

}

```

#### Two-Step Randomization:

- 1. randomize local variables

- 2. randomize lower sequences

- easy to debug

#### Without layer isolation:

- unexpected distribution

- illegal combinations

- hard to debug

### only does WRAP bursts!

```

`uvm_do_with(burst_seq, {addr== 'h4321; burst inside {WRAP,INCR};})

```

```

rand burst_t burst;

constraint burst_c {burst inside {WRAP, INCR};}

`uvm_do_with(burst_seq, {addr=='h4321; burst == local::burst;})

```

### Minimize the number of control knobs

```

class master write seq extends base seq;

rand int addr; // address_

exposed control knob

protected rand int slave; // derived field

hidden control knob

constraint slave c {

slave == p sequencer.cfg.get slave id(addr);

fixed lower-level knob

task body();

slave bus seq bus seq;

`uvm do with(bus seq,/{

background config

bus seq.dir == WRITE;/

bus seq.prot == p sequencer.cfg.get prot();

bus seq.addr == local::addr;

bus seq.slave == local::slave;

```

Sequences are easy to use

Sequences are hard to abuse

Typically lower-level sequences have more control knobs

# Sequence Reuse Guidelines

- Make test sequences independent of testbench architecture

- Use configuration objects and accessor methods to adapt to setup

- Use utility methods to support self-tuning sequences

# Make tests independent of architecture

```

class test feature seq extends base test seq; // test seq

`uvm do with(config seq, {mode == FAST; crc en == 0;})

`uvm do with(write seq, {addr == 'hFFF0; data == 'h5555;})

class dut config seq extends hase seq: // mid-level seq

only mid-level seq references regmodel

regmodel.block.CTRL REG.SPEED.set(int'(mode));

regmodel.block.CTRL REG.CRCEN.set(crc en);

regmodel.block.CTRL REG.update(status);

class bus write seq extends hase seq. // mid-level seq

only mid-level seq references structure

`uvm do on with (cmd send seq,

p sequencer.master sequencer[0], {

cmd send seq.addr == local::addr;

cmd send seq.data == local::data;}

```

Test sequences decoupled from testbench architecture

Tests are generic and reusable on derivative projects

# Use config & access methods to adapt seqs

```

class bus config extends uvm object;

Keep project-specific configuration

rand int fifo depth;

constraints outside of sequences

rand time clk period;

constraint fifo c {fifo depth inside {[1:`MAX DEPTH]};

constraint clk c {clk period inside {[10ns:100ns]};

function int get fifo depth(); // current fifo depth

function time get transfer time(int len); // len * clk period

class fifo_seq

evel sea

Use config access methods in sequences

Sequence adapts to

repeat (p sequencer.cfg.get fifo depth())

current configuration

... // do something

Sequence is generic

`uvm do(start seq)

and reusable

#(p sequencer.cfg.get_transfer_time(length));

`uvm do with(status seq, {exp flag == 1; exp error == 0;})

```

### Use utility methods to support self-tuning

Define utility methods in package scope, base seq, or config (depends on who needs to use it – e.g. driver, monitor, or just seq)

```

function automatic int calc base address(int addr);

return (addr / DATA_WORDS_PER_ADDR_C);

function automatic int calc data_offset(int addr);

return ((addr / DATA_WORD_SIZE_C) % DATA_WORDS_PER_ADDR_C);

return ((addr / DATA_WORD_SIZE_C) % DATA_WORDS_PER_ADDR_C);

```

```

class write_word_seq extends base_seq;

rand bit[31:0] addr;

task body();

'uvm_do_with(write_single_seq, {

write_single_seq.addr == calc_base_address(addr);

write_single_seq.word_sel == calc_data_offset(addr);

})

Use utility methods in sequences

Avoid code duplication between sequences

Sequences adapt to changes in calculations

write_single_seq.word_sel == calc_data_offset(addr);

Use utility methods in sequences

```

### Sequence Library Tips

- Use typedef header at top of sequence library file

- Provide random and fixed versions of configuration sequences

- Implement start and end messages in base sequence

- Group related sequences into sequence library files<sup>[5]</sup>

- Construct sequences using inheritance or composition<sup>[5]</sup>

- Use enumerated types for improved clarity<sup>[5]</sup>

# Use typedef header at top of seq lib file

```

typedef class init seq; //

initialization

typedef header

typedef class power on seq; //

power ramp

typedef class reset seq; // hard reset

class init seq extends base seq;

typically multiple classes per file

power on seq pwr seq;

(normal UVM has one class per file)

reset seq    rst seq;

typically many lines of code per file

endclass

(sequence libraries are large files)

class power on seq extends base seq;

documents content

endclass

class reset seq extends base seq;

allows sequences

used in any order

endclass

```

# Provide random and fixed config seqs

```

class config random seq extends base seq; // mid-level seq

rand speed mode t mode;

hard legal constraints

rand bit

crc en;

rand int

trim;

strong seq API enables user

constraint mode c {mode inside {FAST, SLOW};}

to target & isolate features

constraint trim c {trim inside {[1:15]};}

good seq base for scenario

regmodel.block.CTRL REG.SPEED.set(int'(mode));

development & PSS tests

regmodel.block.CTRL REG.CRCEN.set(crc en);

regmodel.block.CTRL REG.update(status);

class config fixed seq extends config random seq;

constraint fixed c {

`uvm do(random seq)

soft mode == SLOW;

`uvm do(fixed seq)

soft crc en == 1;

fuvm do with(fixed seq, {mode == FAST;})

soft trim == 1;

soft tuning constraints

```

# Implement start and end messages in base seq

Generic non-verbose messages inherited by all sequences

Use **pre/post\_start()** called by seq.start() and `uvm\_do\*(seq)

Strategies to apply sequence API to reach project goals

### **VERIFICATION PRODUCTIVITY**

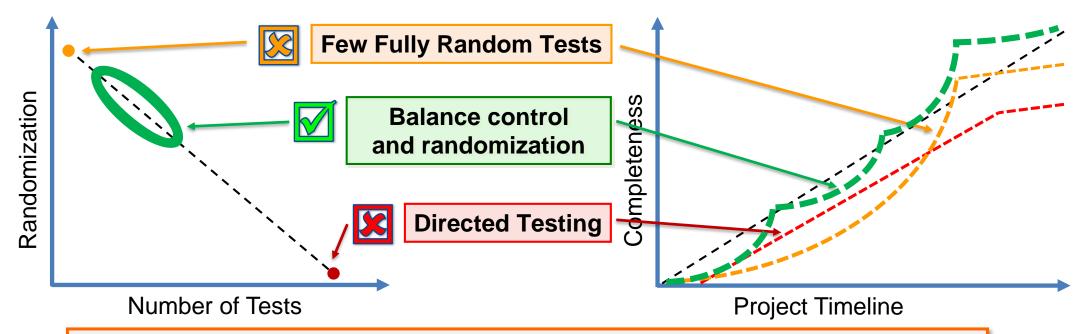

# How do we leverage our Sequence API?

#### **Project Goals**

- Meet milestone deadlines

- Maximize chance of finding bugs

- Report status to stakeholders

#### **Project Challenges**

- Massive evolving state space to verify

- Need to make & track progress despite bugs

- Need to adapt to changing requirements & priorities

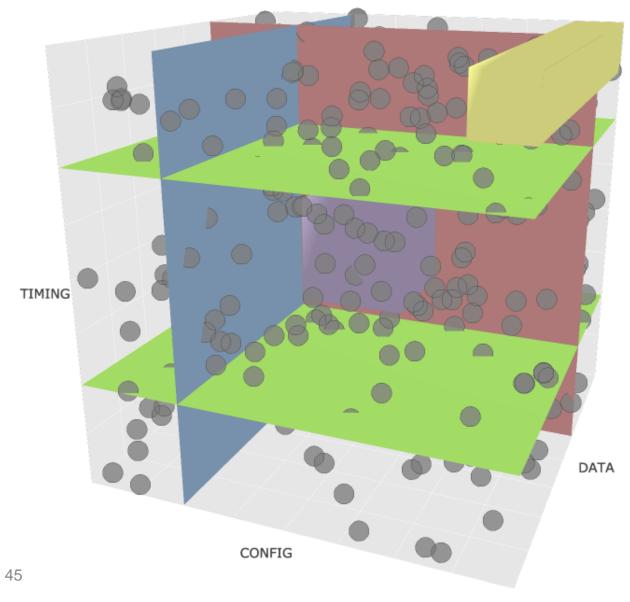

# Feature Group Isolation

| Test Type | Configuration | Data  | Timing       |  |

|-----------|---------------|-------|--------------|--|

| Smoke     | FIXED         | FIXED | FIXED        |  |

| Bug-Hunt  | RAND          | RAND  | RAND         |  |

| Feature   | RAND          | RAND  | FIXED (Low)  |  |

| Feature   | RAND          | RAND  | FIXED (High) |  |

| Feature   | FIXED         | RAND  | RAND         |  |

| Feature   | RAND          | FIXED | RAND         |  |

| Corner    | MAX           | RAND  | MAX          |  |

| Use-Case  | TYPICAL       | RAND  | TYPICAL      |  |

Virtual Sequence Control Knob Options

**Coarse-grained Isolation**

# Mapping features to control knobs

#### Identify design features that partition *major* DUT functionality

#### **Configurations**

- number of channels

- mode of operation

- memory size

#### **Data Patterns**

- directed/random

- corner cases

- use-case

#### **Timing**

- directed / random

- corner / use-cases

- flow patterns

- CH\_ALL, CH\_1, CH\_2

- FAST\_MODE, ...

- M256, M512, M1024

- FIXED, RAND

- ADC\_MAX, ADC\_MIN

- DEFAULT, CASE1, ...

- FIXED, RAND

- DELAY\_MAX, DELAY\_MIN

- SEQUENTIAL, PARALLEL

**Stress features in isolation**

**Combine features in groups**

We can't isolate **every** feature. Choose strategically!

### Test Suite Example

| Test Name       | Configuration |          | Data  | Timing    |            |

|-----------------|---------------|----------|-------|-----------|------------|

|                 | DUT_MODE      | CH_CFG   | Input | TR_DELAY  | DUT_FLOW   |

| seq_flow_test   | RAND          | RAND     | RAND  | FIXED     | SEQUENTIAL |

| par_flow_test   | RAND          | RAND     | RAND  | FIXED     | PARALLEL   |

| fast_mode_test  | FAST_MODE     | SINGLE   | RAND  | RAND      | RAND       |

| basic_data_test | RAND          | RAND     | FIXED | RAND      | RAND       |

| max_thput_test  | FAST_MODE     | ALL_CHAN | RAND  | MIN_DELAY | PARALLEL   |

| use_case_test   | NORM_MODE     | TYPICAL  | RAND  | TYPICAL   | PARALLEL   |

Only possible with properly designed sequence API

Where does portable stimulus fit in?

### **PORTABLE STIMULUS**

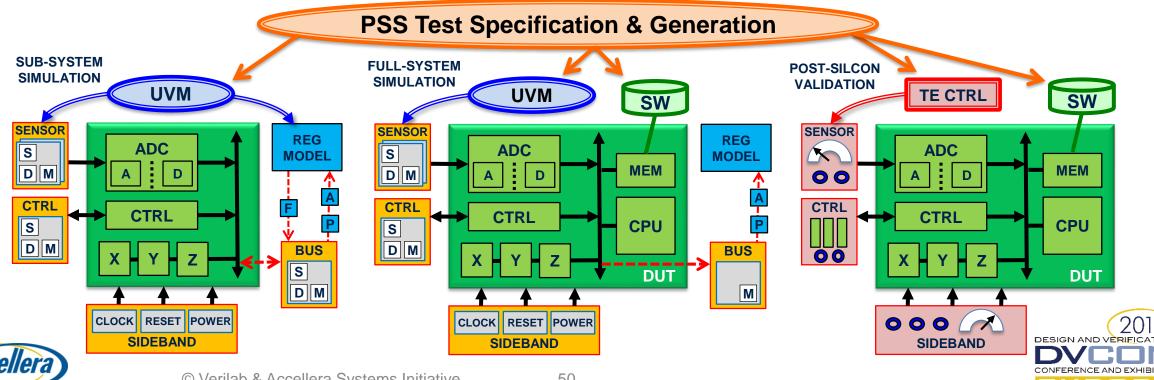

### What is Portable Stimulus?

Portable Test and Stimulus Standard (PSS) [7]

"[PSS] defines a **specification** for creating a single representation of **stimulus** and **test** scenarios ... enabling the generation of different implementations of a scenario that run on a variety of execution platforms..."

#### Key features:

- higher level of abstraction for describing test intent

- test intent is decoupled from implementation details

- declarative domain-specific system modeling language

- allows test portability between implementations and platforms

- executes implementation-specific methods and sequences

- Does PSS replace all our UVM sequences and stimulus?

- no, but it can replace the test layer and some virtual sequences...

### Test Reuse

#### PSS addresses reuse of test intent

- vertical reuse from (block to) sub-system to full-system (within UVM)

- reuse of tests on different target implementations (e.g. UVM or SW)

- reuse of tests on different target platforms (e.g. simulation or hardware)

SYSTEMS INITIATIVE

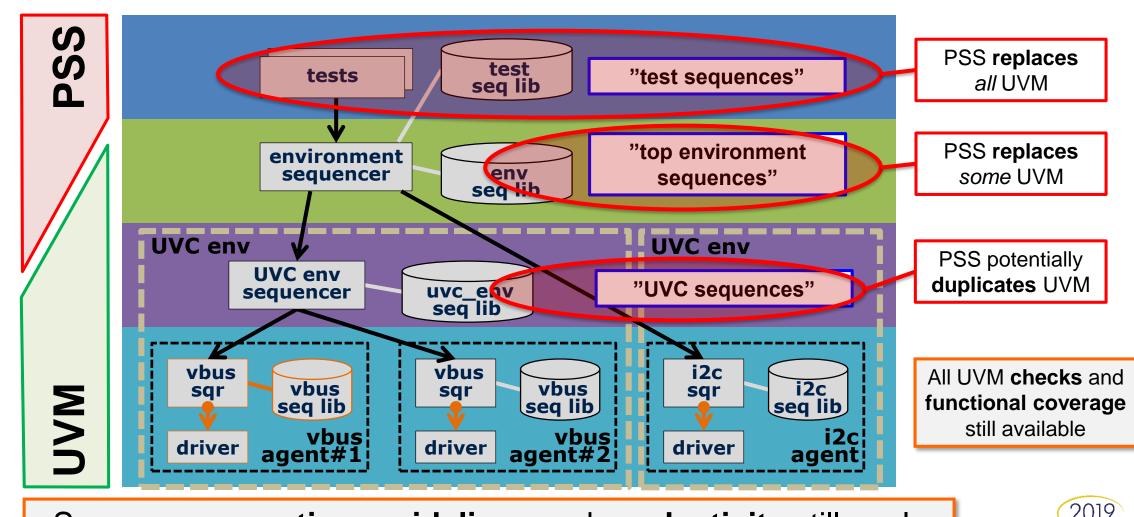

### What Changes

- High-level test scenarios & use-cases delegated to PSS

- (almost\*) all test sequences & test components replaced by PSS

- some sub-system and full-system scenario virtual sequences replaced by PSS

- We do not implement these tests in UVM

- we generate UVM tests from the PSS tools

- we conceive test scenarios using PSS modeling paradigm

- PSS tests are responsible for corresponding high-level checks

- PSS also has built-in (stimulus) functional coverage capability

(\*) Retain some pure UVM tests to sign-off & regress UVM environment

### PSS Tests & UVM Sequences

Sequence execution, guidelines and productivity still apply

### **CONCLUSION**

### Conclusion

#### **Common Problems We All Face**

Poor visibility of project status

No risk-management of features

#### **Apply Sequence API Guidelines**

**Achieved Control**

**Managed Complexity**

**Enabled Reuse**

#### **Control Advanced Scenarios**

**Control Reactive Slaves**

**Autonomous Streaming Sequences**

### Conclusion (cont.)

#### **Project Challenges**

Poor visibility of project status

No risk-management of features

#### **Apply Sequence API Strategically**

Prioritize features efficiently

Track and report status easily

Anticipate and manage project risks

#### **UVM Sequences Remain Vital**

PSS benefits from high quality sequences

### References

- 1 Advanced UVM Tutorial Verilab, DVCon Europe 2014

- 2 UVM Reuse Tutorial Verilab, DVCon Europe 2015

- 3 UVM Audit Tutorial Verilab, DVCon Europe 2018

- 4 Mastering Reactive Slaves in UVM Verilab, SNUG 2016

- 5 Use the Sequence, Luke Verilab, SNUG 2018

- 6 SystemVerilog Constraint Layering via Reusable Randomization Policy Classes, John Dickol, DVCon 2015

- 7 Portable Test and Stimulus Standard, Version 1.0, Accellera

Verilab papers and presentations available from:

http://www.verilab.com/resources/papers-and-presentations/

# Q & A

mark.litterick@verilab.com

#### The following images are licensed under <a href="#">CC BY 2.0</a>

- Verdi\_Requiem 008 by Penn State

- Sheet music by Trey Jones

- Flutist by operaficionado

- Cello Orchestra by Malvern St James

- Folk\_am\_Neckar\_4915 by Ralf Schulze

- Flute by <u>Bmeje</u>

- Cello by Lori Griffin