## Automated Performance Verification to Maximize your ARMv8 pulling power

Nick Heaton, Distinguished Engineer, Cadence Simon Rance, Sr Product Manager, ARM

cādence°

### **Agenda**

- Introduction to ARM v8 CPU Subsystem

- System Coherency

- DDR Bandwidth and Latency Demands

- Example Performance Use-case

- Building a testbench early performance exploration

- Testbench Automation

- Cadence Interconnect Workbench

- Debugging Failing Use-cases

- Visualizing System Back-pressure and DDR Events

- Summary

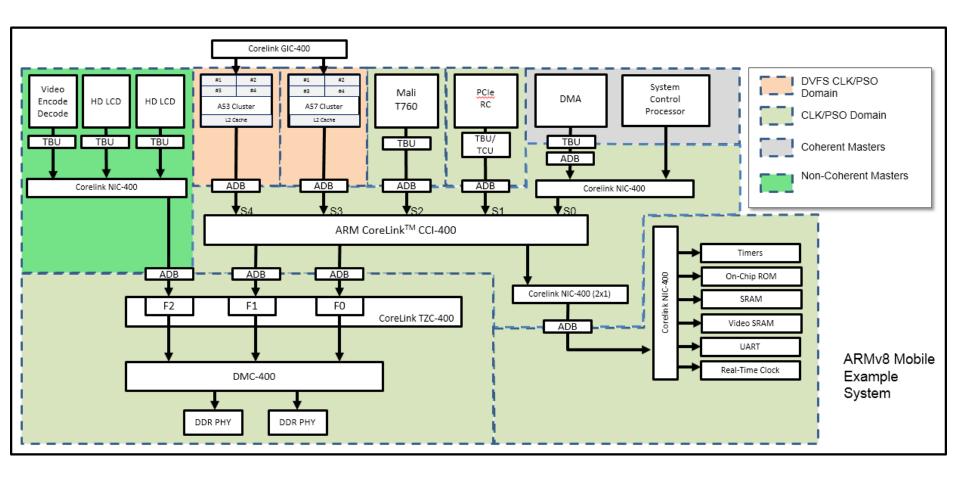

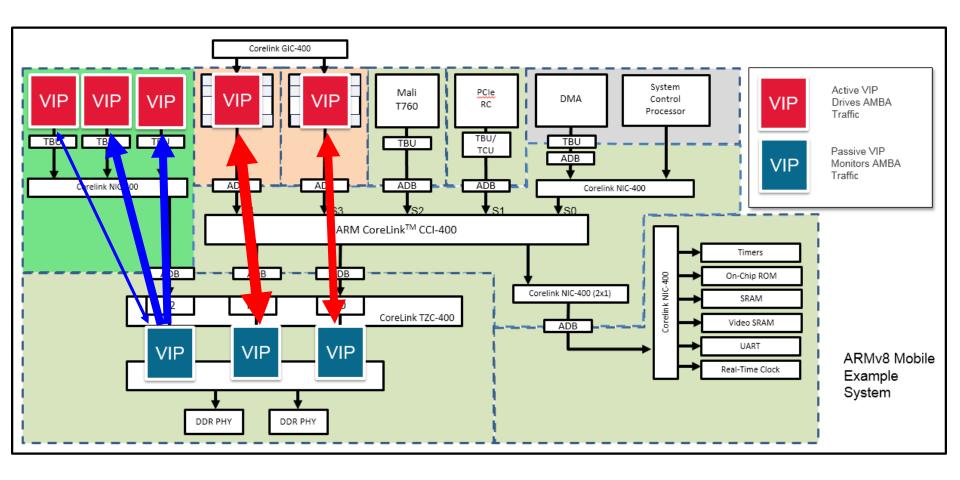

## **ARM v8 Compute Subsystem**

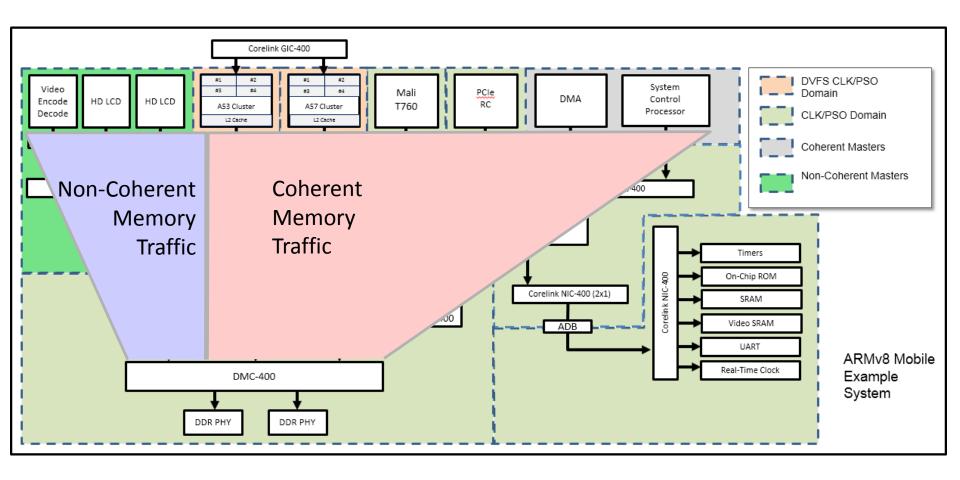

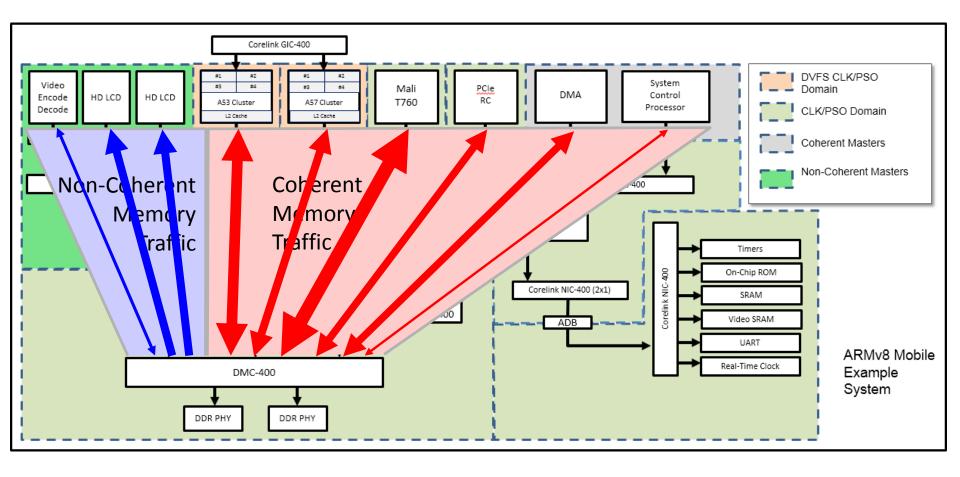

## **System Coherency**

# DDR Bandwidth and latency Demands

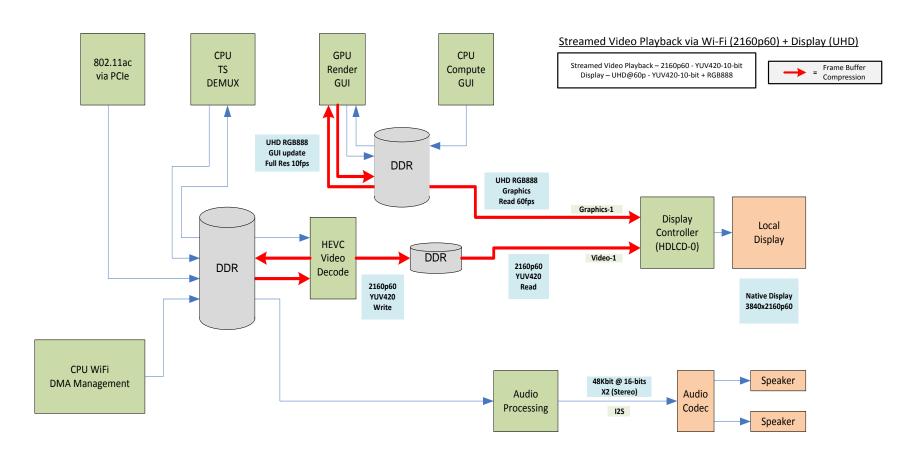

## **Example Performance Use-Case: Streamed Video Playback**

#### Testbench for early analysis

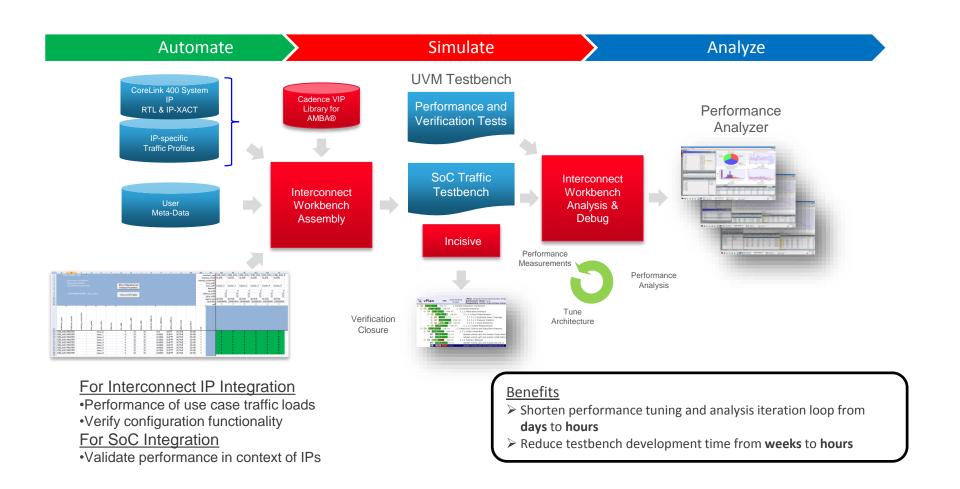

#### **Testbench Automation**

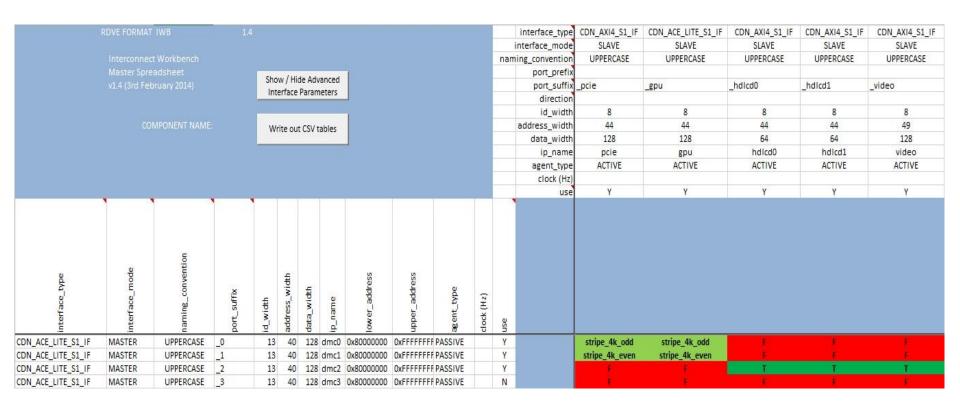

#### Cadence Interconnect Workbench

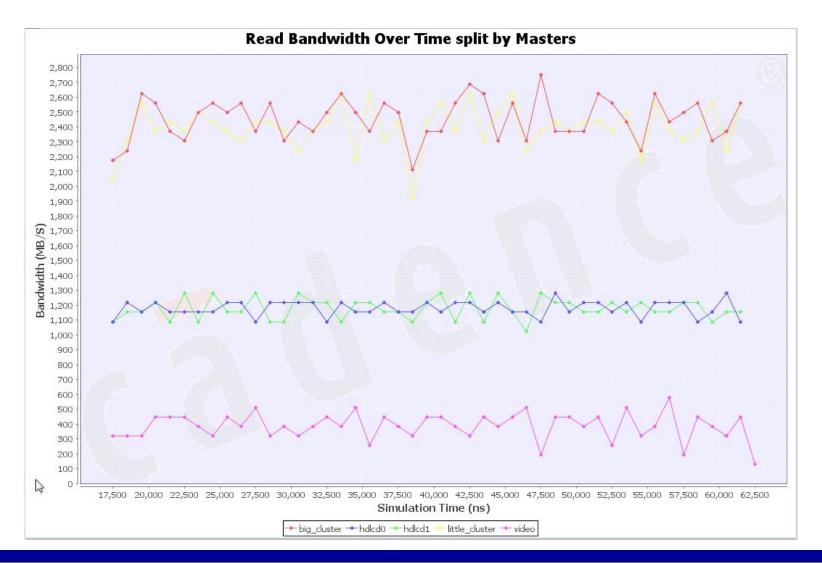

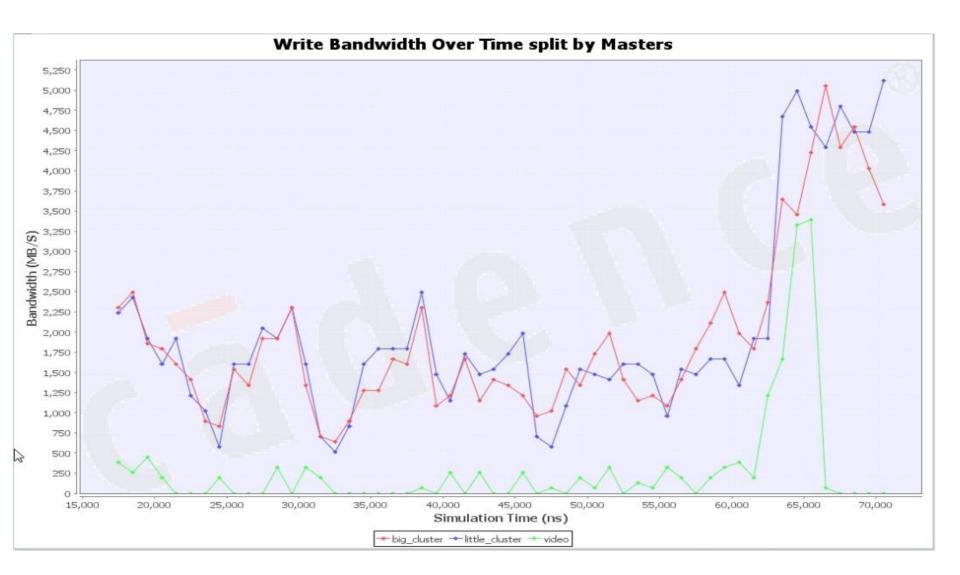

#### **Modelled Use-case results**

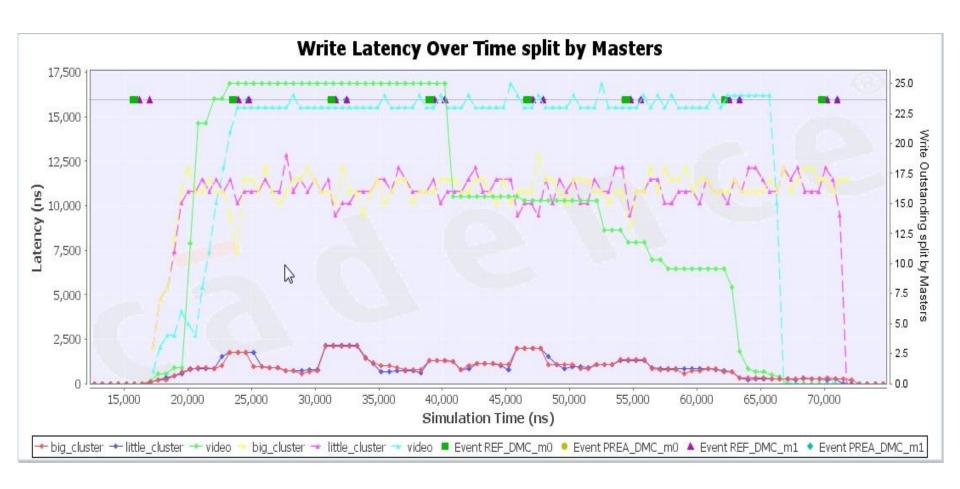

#### **Debugging Failing Use-cases**

## Visualizing System back-Pressure and DDR Events

### **Summary**

- CPU Subsystems are becoming more complex

- Sophisticated System IP provides powerful capabilities and configurability to ensure system performance can be achieved

- Analysis tools and automation are essential productivity aids for early exploration of system performance on the RTL.