# Assertion-based Verification for Analog and Mixed Signal Designs

Srinivas Aluri Texas Instruments Dallas TX, USA s-aluri@ti.com

**Abstract:** Assertion-based verification approaches have been making great strides into mixed signal verification environments. As the design complexity increases so does the means to verify it. Verification engineers have been using assertion-based approach in the analog domain as well. Most of the effort in this domain has been to code assertions on analog models which are abstract representation of a real circuit. This paper shows a methodology of coding assertions directly on electrical ports of a schematic sub circuit and hence can be bound to a sub circuit, thereby greatly increasing modularization and facilitating re-use.

**Introduction**: We are very familiar with the concept of coding checkers without touching the design by binding the code to it using verification units in the digital domain. This methodology is gaining traction in the analog and mixed signal domains. By using vunit, verification engineers can bind assertions to abstract models of analog or interactions between digital and models of analog. There are scenarios where an analog block is not modelled and is run in schematic form and verification checks needs to be performed in a complete analog domain. We should be able to apply the same techniques to effectively verify the design without slowing down the simulation speed. The work shown in this paper specifically targets such scenarios and shows how assertion techniques can be used for verifying analog parameters.

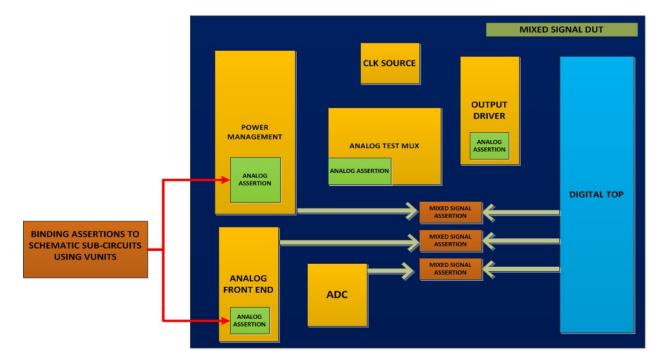

**Binding Assertions:** Fig.1 shows the block diagram of mixed signal DUT. Assertions can be bound as below for the shown mixed signal design.

Fig 1: Block diagram showing Assertions bound to sub-circuits in Mixed signal DUT

- a. Bind assertions to digital modules and instances

- b. Bind assertions to behavioral modules of analog blocks

- c. Bind assertions to top level so that you can write mixed signal assertions by accessing signals from both analog and digital domain

- d. Bind assertions directly to analog module (not model).

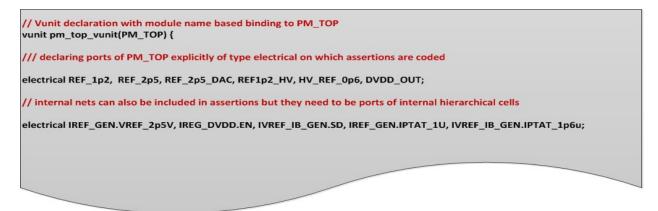

The code below shows module name based assertion binding on analog module mentioned in (d) above. Vunit and relevant declarations of electrical ports on which checking needs to be performed are shown.

#### Example Code- I:

The snippets of code below shows some important steps followed while using this methodology

- a. Ports of the sub-circuit on which assertions are to be coded using vunit needs to be explicitly declared as electrical as shown in fig.2.

- b. Assertions can be written on hierarchial nets as well, but you need to use the name of the port which the net is connected to write an assertion, and that port needs to be declared as electrical.

Fig 2: Code showing Vunit declaration and explicit port declaration on which assertions are planned.

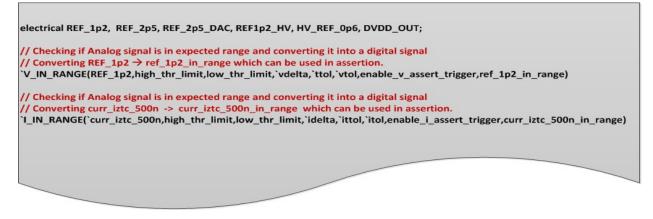

c. Before writing assertions on the analog domain signal, we need to convert them to digital, for speed and tool limitations. Fig.3 shows the required conversion on voltage and current signals.

Fig 3: Code showing Vunit declaration and explicit port declaration on which assertions are planned.

REF\_1p2 which is an electrical signal is monitored and converted to an event driven signal by using a custom macro shown in fig.4. By using appropriate threshold and tolerances in voltage and time analog variations are converted to digital signal events, which is ref\_1p2\_in\_range in this case. In the case of current, we cannot directly use the port name as in the case of voltage, but instead need to use \$cgav system task. Below is the example

`define curr\_iztc\_500n `get\_abs(\$cgav("<Hierarchial\_DUT\_path>.IZTC\_500n","flow"))

Below is the detailed code of the macros used in the above code.

`define V\_IN\_RANGE(Node,hthr,lthr,vdelta,ttol,vtol,enable,digout) \

always @(absdelta(V(Node),vdelta,ttol,vtol,enable)) begin \

if((V(Node) > hthr) || (V(Node) < lthr)) digout = 0; \

else digout = 1; \

end</pre>

`define I\_IN\_RANGE(exp,hthr,lthr,edelta,ttol,etol,enable,digout) \

always @(absdelta(exp,edelta,ttol,etol,enable)) begin \

if((exp > hthr) || (exp < lthr)) digout = 0; \

else digout = 1; \</pre>

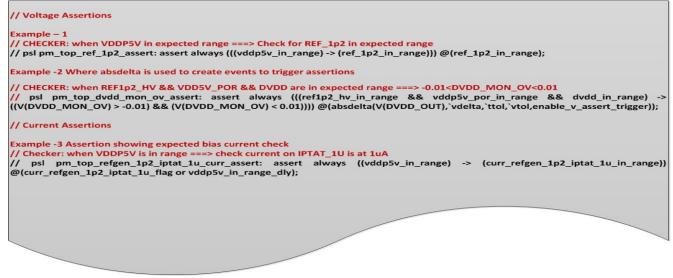

After converting the analog signals to digital domain, we can use those signals and code psl assertions completely in the digital domain. Fig.5 shows an example of voltage and current checking assertions. The voltage assertion in example-1 is checking for ref\_1p2 voltage in range, if vddp5v is in expected range. This assertion is triggered each time there is a change in ref\_p12. In example-2 the assertion is checking for the dvdd\_mon signal in the expected range, if ref1p2\_hv, vdd5v\_por and dvdd are in range. This assertion is triggered whenever an event is created by the absdelta function. In example-3 iptat\_1u current is checked to see if it is in the expected range when vddp5v is in range. This assertion is triggered when there is a change in iptat current or if there is a change in vddp5v.

Fig 5: Example code showing assertions on analog parameters.

*Example code* – II: Input and Output Analog testmux is a very standard feature. Oftentimes these testmuxes have large number of inputs to select from and we can effectively verify the functionality using the assertion technique discussed above.

- a. For example lets say if a regulated voltage needs to be observed on testmux we can write an assertion shown in fig.6 to connect the source which in this case is the output of an LDO to output of the output analog testmux, given that the mux is programmed with a specific selection.

- **b.** Similarly we can write an assertion to check input testmux functionality for a case where lets say we want to drive an analog value into the design through input testmux rather coming from another block in the design.

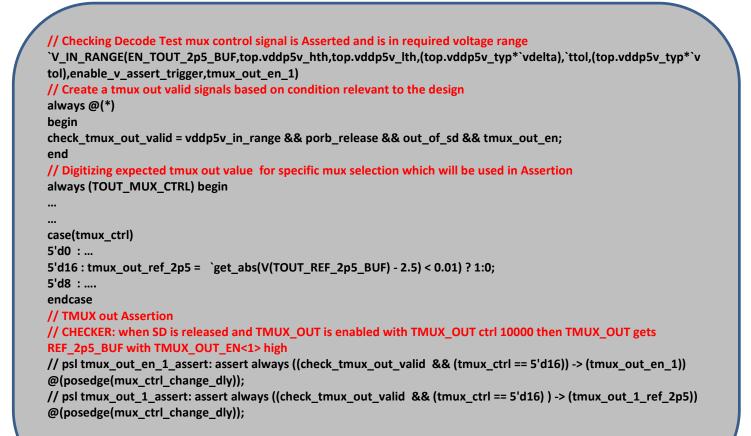

#### Fig 6: Example code showing Analog Output Testmux Assertion.

In the above example shown in fig.6, for every combination of testmux selection two assertions which are getting checked are shown.

- a. When the tmux out is valid, and if the mux selection is programmed to a specific value then check if the relevant enable signal is activated.

- b. When the tmux out is valid, and if the mux selection is programmed to a specific value then check if the mux output is equal to expected value.

Similar approach can be taken to check for the input testmux functionality.

#### PSL v/s SVA Assertions :

- **a.** The above mentioned verification methodology can be used with SVA assertions, but it is not as straight forward as using PSL assertions.

- **b.** SystemVerilog standard does not allow the presence of continuos domain object. Therefore creating analog expressions is not possible. This capability is possible and comes native to PSL.

- **c.** However SystemVerilog allows the usage of real valued variables and these can be used in the context of SystemVerilog assertions. This is possible with analog value fetch system functions like "cds\_get\_analog\_value".

- **d.** In PSL to obtain the potential of analog singal you can directly bind a vunit to a subckt and use access functions like "V(signal)". We can also use this function directly in the assertion. On contrary this is not possible in SystemVerilog and hence each we want to fetch an analog value we need to use analog fetch system functions and provide the entire design hierarchy path to the required signal.

- e. In case fetching current parameter of a signal of interest I(signal) access function does not work for both PSL and SVA. Only way to get this is to use analog fetch system function \$CGAV with "flow" as shown in fig.7.

### ANALOG VALUE FETCH FOR PSL AND SVA

#### PSL

Voltage --- Bind Vunit to subckt and use voltage access functions V(). This can be used in PSL Assertions Current --- `define curr\_iztc\_500n\_0 `get\_abs(\$cgav("<Hierarchial\_DUT\_path>.IZTC\_500n[0]","flow"))

#### SVA

Analog domain not possible in SVA assertions, use analog fetch functions to get analog values into real variables and use them in assertions.

Voltage --- `define v\_refgen\_1p2 `get\_abs(\$cgav("<Hierarchial\_DUT\_path>.IZTC\_500n[0]","potential")) Current --- `define curr\_iztc\_500n\_0 `get\_abs(\$cgav("<Hierarchial\_DUT\_path>.IZTC\_500n[0]","flow"))

#### Fig.7 Example code showing analog value fetch and usage in PSL and SVA assertions

**Methodology and structure for SVA assertions:** Since SVA assertions has some limitations related to assertions on analog domain variables, the Vunit based structure explained for PSL is not applicable. If you have to go the SVA route, we need to use SV modules to write SVA assertions and use analog fetch functions to get analog parameters like voltage and current as shown in Fig.7 and assign them to real variables and use them in SVA assertions inside SV module. Fig.8 below shows the topology.

| SVA Assertions topology                                                   |                                                                                                                                                                                                                                               |

|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Top.vams:                                                                 | //SVA assertions module                                                                                                                                                                                                                       |

| Module top ()                                                             | module sva_module();                                                                                                                                                                                                                          |

| <pre>//instantiate SVA module sva_module sva_module_i (); endmodule</pre> | real analog_v, analog_i<br>analog_v = \$cgav("signal_path", "potential");<br>analog_i = \$cgav("signal_path", "flow")<br>// SVA assertion using above real variables<br>assert property (@(trig) (cond a)  -> (analog_v > vth));<br>endmodule |

Fig.8 Topology for using SVA assertions.

#### Integration of PSL Assertions into DV environment:

In the incisive or command line flow, these assertions can be pulled in with irun option of "-assert -propfile\_vlog" and file name with externsion of ".psl". In virtuoso flow, you can enter this option in the ADE state in the additional argument section. Fig.9 shows snapshot of how to pull in psl assertion file into the virtuoso environment.

| AMS Options     Main Netlister Messages | PLI SDF Timing Miscell                      | laneous |

|-----------------------------------------|---------------------------------------------|---------|

| many unecomes (-y)                      |                                             | laneous |

| file extensions for -y (-libext)        |                                             |         |

| TIMESCALE OPTIONS                       |                                             |         |

| âlobal sim time                         | 1                                           |         |

| Inits for global sim time               | ns                                          |         |

| Global sim precision                    | 1                                           |         |

| Inits for global sim precision          | ns                                          |         |

| DISCIPLINE OPTIONS                      |                                             |         |

| Default discipline                      | logic                                       |         |

| lse detailed discipline resolution      | <b>¥</b>                                    |         |

| LIBRARY COMPILATION OPTIONS             |                                             |         |

| Pre-compiled                            | libraries (-reflib) Settings                |         |

| Run-time library co                     | mpilation (-makelib) Settings               |         |

| OTHER OPTIONS                           |                                             |         |

| nable line debug to use with Simvisio   | n 🖵                                         |         |

| Additional arguments                    | <pre> +top top -assert -propfile_vloc</pre> |         |

|                                         |                                             |         |

Fig 9: AMS option form in ADE showing arguments to pull in assertion files.

Assertions can be arranged into various vunit files, as per design hierarchy, and since these assertions are bound to the sub-circuit/module, they can be portable along with the design. To pull in multiple assertion files, enter the below commands into a common file and pull in this file with irun or through ADE.

| // To pull in multiple assertion files with one common file |  |

|-------------------------------------------------------------|--|

| -assert -propfile_vlog cell1.psl                            |  |

| -assert -propfile_vlog cell2.psl                            |  |

| -assert -propfile_vlog cell2.psl                            |  |

|                                                             |  |

**Integration of SVA Assertions into ADE environment:** In the incisive or command line flow, these assertions can be pulled in with irun –f top.vams and –top top. In virtuoso flow, you can enter this option in the ADE state in the additional argument section. Fig.10 shows snapshot of how to pull in SVA assertion files into the virtuoso environment. In case you have any PSL assertions in the SVA module you activate them by using a "-assert" option to the irun or enter it in the additional arguments section of the AMS option form.

| 🗙 💽 AMS Options                         |                                | $\odot \odot \odot$ | $\otimes$ |                              |

|-----------------------------------------|--------------------------------|---------------------|-----------|------------------------------|

| Main Netlister Messages                 | PLI SDF Timing Miscellaneous   |                     |           |                              |

| Files on irun command line              | DS_Latest/ams/set/top.vams     |                     |           |                              |

| Include paths (-incdir)                 | 3/tiva \${CDS_VLOGA_INCLUDE}   |                     | C.        |                              |

| VERILOG                                 |                                |                     |           |                              |

| Library files (-v)                      | jlib/msl270/PAL/udp/udps.v     |                     |           | Pulling top.vams             |

| Library directories (-y)                |                                |                     |           | which contains sva<br>module |

| File extensions for -y (-libext)        | × <b>v</b> .                   |                     |           | moudie                       |

| TIMESCALE OPTIONS                       |                                |                     |           |                              |

| Global sim time                         | 1                              |                     |           |                              |

| Units for global sim time               | ns                             |                     |           |                              |

| Global sim precision                    | 1                              |                     |           |                              |

| Units for global sim precision          | ns                             |                     |           |                              |

| DISCIPLINE OPTIONS                      |                                |                     |           |                              |

| Default discipline                      | logic                          |                     |           |                              |

| Use detailed discipline resolution      | ⊻                              |                     |           |                              |

| LIBRARY COMPILATION OPTIONS             |                                |                     |           |                              |

| Pre-compiled lib                        | raries (-reflib) Settings      |                     |           | Declaring parallel to        |

| Run-time library com                    | vilation (-makelib) Settings   |                     |           | level hierarchy              |

| OTHER OPTIONS                           |                                |                     |           |                              |

| Enable line debug to use with SimVision |                                |                     |           |                              |

| Additional arguments                    | le -allowredefinition -top top |                     |           |                              |

Fig 10: AMS option form in ADE showing arguments to pull in SVA assertion files.

#### Simulation Results:

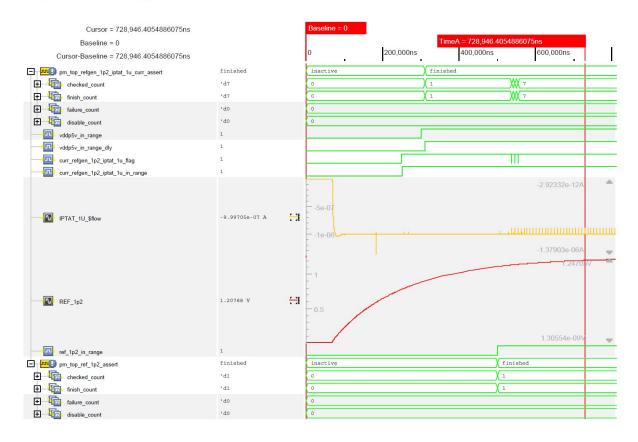

Fig10. Shows simulation results of current and voltage assertions along with assertion metrics which is useful in observing how many times each assertion is checked for any possible violation counts.

**Current Assertion :** For the current assertion each time there is a certain specified change in the value of the IPTAT current, the assertion check triggers to check if the current is within the specified range. Current assertion check uses a layered approach, one to check for actual change which is what the curr\_xxx\_flag signal is doing, and the other which filters out the flag signal if the out of range duration is very small and acceptable, which is indicated by curr\_xxxx\_in\_range.

**Voltage Assertion** : For the voltage assertion, the assertion check is triggered whenever ref\_1p2 signal undergoes a variation which is more than the specified tolerance which causes the state of ref\_1p2\_in\_range to change, which in turn triggers the assertion and checks for the specification that ref\_1p2 should be in expected range once vddp5v is in expected range and any variation later is an error condition.

Also these assertions can be viewed in the assertion browser, which shows the list of all the assertions used, and their stats related pass/fail. Fig11. Shows the snapshot of assertion browser.

| Assertion Browser 2 - Sim<br>Edit View Explore Windows            |                                                                                    |                                                     |                          | cādence  |

|-------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------|--------------------------|----------|

| Por Contractions                                                  | Tech                                                                               |                                                     | 🕌 🗳 - Send To: 🗽 💥 🔍 📰 🔳 |          |

|                                                                   |                                                                                    | - 49 49                                             |                          | = 🔤 🖭    |

| x <sub>2</sub> limeA▼ = 1,138,486.Ut▼ ns▼                         | 👯 🔹 🤙 💁 Search Times: Value 🗸 👘                                                    | I ()., ().                                          | Assertions In-           |          |

| 🔯 - 🔯 - Scope: 🛙 sim_top                                          | _level.I0.ICORE.IBIAS                                                              |                                                     | Assertions In            | Deen 🖒 A |

| Assertion Name                                                    | Type Cov Module/Unit Instance                                                      | Current Disabled Finished<br>State Count Count      | Failed<br>Count          |          |

| bias_vbg_assert                                                   | assert TPS50601A_I sim_top_level.I0.IC                                             | ORE finished 0 1                                    |                          | (        |

| Current Assertion State Summary ()<br>Failed (10%) Finished: 1 (1 | -Illered) - Assertions Displayed 1                                                 | 0%) Inactive: 0 (0%)<br>Off: 0 (0%) Flushed: 0 (0%) |                          |          |

|                                                                   | ve 🖡 active 🛒 finished 📕 failed 🕷 disabi<br>rt 👅 assume 👅 cover 🕷 restrict 🛒 vcomp |                                                     | Instance Filter:         | 1        |

|                                                                   |                                                                                    |                                                     |                          |          |

Fig.11: Assertion browser showing assertion statistics.

## **Current and Voltage Assertion Checks**

Page 1 of 1

Fig. 11: Simulation results showing current and voltage assertion checks.

**Summary**: Using the above mentioned strategy, we can successfully implement assertion based verification of analog parameters. This is useful even if the dut is completey an analog design or mixed signal design.Binding assertions to the cell, makes assertions portable and can be effectively re-used along with saving design time in the verification cycle. This implementation is advantageous, over traditional analog checkers where you have to write procedural code using verilogA/Verilog-AMS or using ocean to do post process checking.