## Architecting "Checker IP" for AMBA protocols

Ajeetha Kumari, Verification Consultant, VerifWorks Pvt. Ltd. Srinivasan Venkataramanan, Verification Technologist, VerifWorks Pvt. Ltd

- CIP Introduction

- What to Verify in Assertion

- AHB CIP Example

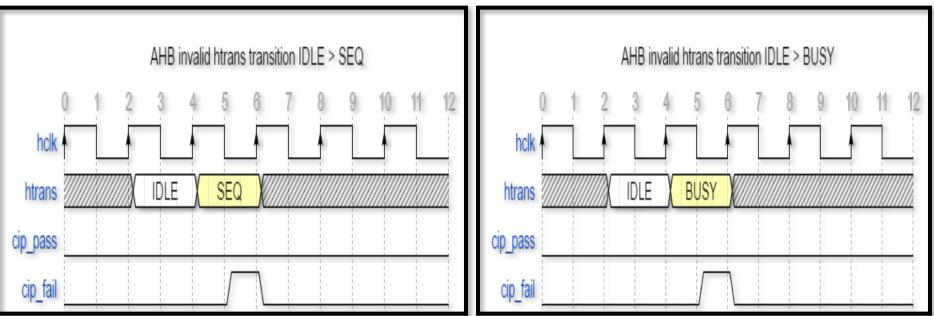

- AXI3 Architecture

- CIP Guidelines

- Using Go2UVM Framework

- Using SVUnit

- Summary

- References

### **INTRODUCTION CIP**

- CIP Checker IP

- Set of assertions for a given protocol

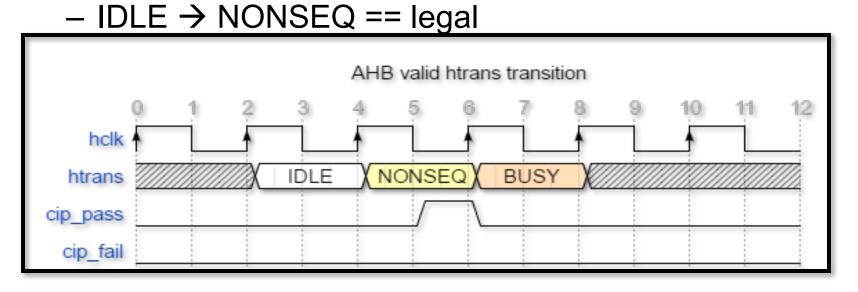

- AHB requirement *htrans* signal from an AHB master.

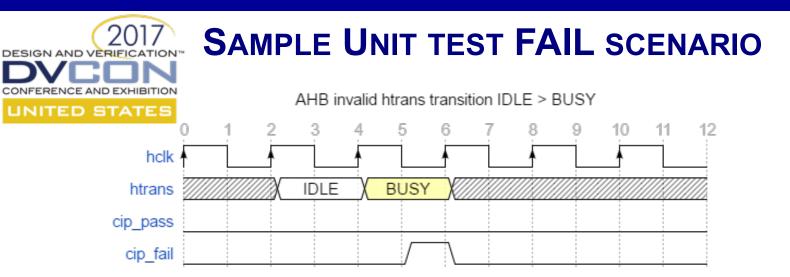

- The signals *cip\_pass* and *cip\_fail* indicates state of assertions capturing this requirement.

- •To enumerate the fail scenarios, other possible transitions of *htrans* need to be explored.

- In these figures the signal *cip\_fail* goes HIGH indicating a protocol violation.

- Assertion aspects

- Intent :- reflects the system engineer or designer's understanding or vision of what is desired, as defined in written, assumed, unsaid, or implied requirements, many of which may be loosely (or tightly) specified in timing diagrams and in engineers' heads.

- Accuracy :-deals with the proper expression of the requirements with emphasis on coding rules, style, and coverage of intended cases.

- Efficiency :- deals with coding that puts too much unnecessary overhead on the simulator because of unneeded threads.

- Purpose :- addresses the uses or application of the verification environment.

### **Property as checker**

### **Property as constraint**

1322 m\_p\_vw\_awaddr\_boundary: assume property (p\_vw\_awaddr\_boundary);

1323

m\_p\_vw\_awaddr\_wrap\_align: assume property (p\_vw\_awaddr\_wrap\_align) ;

- 1326 m\_p\_vw\_awburst: assume property (p\_vw\_awburst);

1327

- 1328 m\_p\_vw\_awcache: assume property (p\_vw\_awcache) ;

1329

- 1330 m\_p\_vw\_awlen\_wrap: assume property (p\_vw\_awlen\_wrap) ;

1331

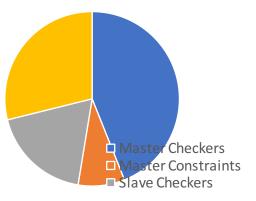

#### No of properties

1324 1325

- •Use of *checker…endchecker* construct

- •Use module as a container

- •Use bind construct

- •Use of *interface* as a container

- •Use text macro in action blocks

- •Use appropriate delays in value change functions

- RTL designers inlined checks

- Verification engineers external using *bind*

- A set of small assertions is usually better than single large assertions

- Instantiations

- Concurrent

- Immediate

- Procedural concurrent

- How to insert a group of assertions inline in RTL?

# Using checker...endchecker

- SV 2009 added new container for assertions

*checker*

- Offers flexibility in terms of instantiation

- All 3 forms immediate, concurrent & procedural concurrent

- Useful for smaller checkers (OVL like)

- Support "free/rand variables"

Great for pure formal verification tools

- For CIP not recommended because of language restrictions

- No parameters

- SystemVerilog *module* is well known construct

- Easy to use/code

- Modules can instantiate other modules

- Direct

- Indirect via bind

- Assertions can be coded inside modules

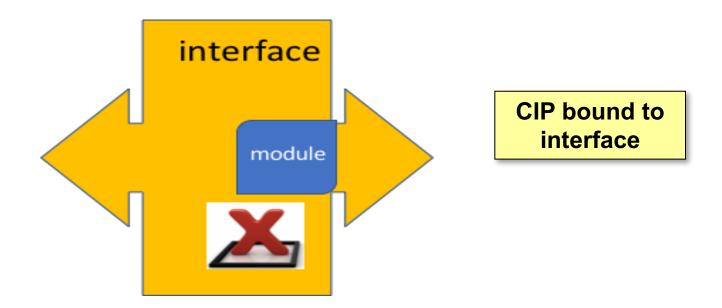

## Can NOT bind a *module* to an *interface*Interface is widely used construct

Interface is a popular construct in SV

Widely used for communication between dut and tb

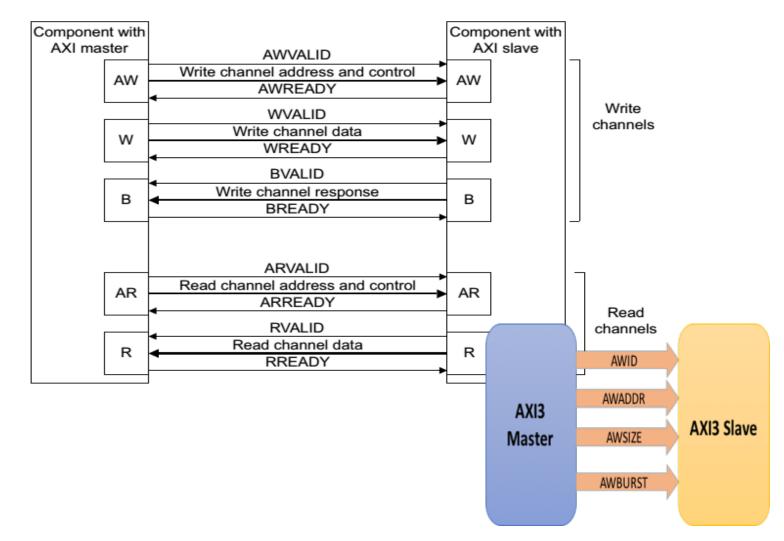

Text macros can be used to insert a block of code which is useful in simulation to make them FV friendly and vice versa

VW\_CIP\_SIM is used

| 1599<br>1600<br>1601<br>1602 | a_p_vw_awburst: assert property (p_vw_awburst)                                                                      |

|------------------------------|---------------------------------------------------------------------------------------------------------------------|

| 1602                         | `ifdef VW_CIP_SIM                                                                                                   |

| 1603                         | else                                                                                                                |

| 1604                         | `uvm_error (vw_id,"p_vw_awburst: When AWVALID is high, a value of 2'b11 on AWBURST is not permitted. Spec: table 4- |

| 3                            | 3 on page 4-5")                                                                                                     |

| 1605                         | `endif //VW_CIP_SIM                                                                                                 |

| 1606                         |                                                                                                                     |

| 1607                         |                                                                                                                     |

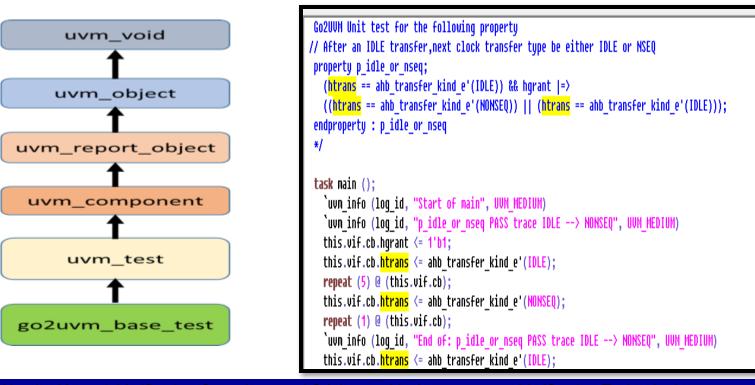

## USING GO2UVM FRAMEWORK

- Goal: develop unit tests in UVM framework

- Problem: UVM is too big for this task at hand

- Solution: open-source Go2UVM package.

/owifl//owles Dut I to

## **USING SVUNIT REPORT MOCKER**

- <u>Self-checking of unit tests through SVUnit's UVM</u> <u>Report Mock:</u>

- Need to declare PASS/FAIL automatically based on the user's intent.

- This challenge is more than typical DUT PASS/FAIL declaration (that could be based on presence of UVM\_ERROR in log file).

- Unit tests inject "error scenarios" by definition

- Manual classification of expected UVM\_ERRORs is not feasible

At clock tick 6, we would expect an assertion to fire. If we run the trace as-is, it reports an UVM ERROR like shown below:

**UVM\_ERROR**../vw\_cip\_src/vw\_ahb\_lite\_cip.sv(134) @ 175.00 ns: reporter [SVA] Invalid htrans transition - from IDLE only NSEQ is allowed. **Assertion 'a\_p\_idle\_or\_nseq' FAILED** at time: 175ns (18 clk), scope:vw\_ahb\_lite\_cip\_go2uvm.vw\_ahb\_lite\_cip\_0, start-time: 165ns (17 clk)

# CONFERENCE AND EXHIBITION Using repor mock API

```

repeat (1) @ (this.vif.cb);

`uvm_info (log_id, "End of: p_idle_or_nseq PASS trace IDLE --> NONSEQ", UVM_MEDIUM)

this.vif.cb.htrans <= ahb_transfer_kind_e'(IDLE);</pre>

repeat (5) @ (this.vif.cb);

this.vif.cb.htrans <= ahb_transfer_kind_e'(SEQ);</pre>

repeat (2) @ (this.vif.cb);

uvm_report_mock::expect_error("SUA");

`uvm_info (log_id, "End of: p_idle_or_nseq FAIL trace IDLE --> SEQ", UVM_MEDIUM)

this.vif.cb.htrans <= ahb_transfer_kind_e'(IDLE);</pre>

repeat (5) @ (this.vif.cb);

// uvm report mock::expect error();

this.vif.cb.htrans <= ahb_transfer_kind_e'(BUSY);</pre>

repeat (2) @ (this.vif.cb);

// TBD find a better way to handle this

go2uvm_test_fail_count += (!uvm_report_mock::verify_complete());

`uvm_info (log_id, "End of: p_idle_or_nseq FAIL trace IDLE --> BUSY", UVM_MEDIUM)

endtask : main

endclass : vw_ahb_lite_cip_test

```

- Simple checkers can be developed quickly and used across design entities,

- Comprehensive CIP (Checker IP) takes

- a good architecture

- set of coding guidelines to keep them reusable.

- In this paper, we have shared our experience of:

- Converting a plain set of properties to a reusable CIP.

- How we used a self-checking unit test framework to verify each assertion in a CIP.

1. SystemVerilog LRM -

- http://standards.ieee.org/getieee/1800/download/1800-2012.pdf

- 2. ARM AXI specification <u>https://www.arm.com/products/system-</u> ip/amba-specifications

- 3. ARM releases assertion models https://www.arm.com/about/newsroom/12266.php

- 4. Experiencing Checkers for a Cache Controller Design http://systemverilog.us/DvCon2010/DvCon10\_Checkers\_paper.pdf

- 5. Accellera Open Verification Library (OVL) <u>http://accellera.org/activities/working-groups/ovl</u>

- 6. SystemVerilog Assertions handbook, <u>www.systemverilog.us</u>, <u>www.verifnews.org/publications/book</u>

- 7. "What are \$past compared to on first clock event?" <u>http://bit.ly/2hkb7nV</u>

- 8. Go2UVM open-source test layer, <u>www.go2uvm.org</u>.

- 9. SVUnit <u>http://www.agilesoc.com/open-source-projects/svunit/</u>

## Thanks

Ajeetha Kumari, Verification Consultant and Srinivasan Venkataramanan, Verification Technologist,