# Advanced UVM in the real world - Tutorial -

Mark Litterick

Jason Sprott

Jonathan Bromley

Vanessa Cooper

#### **INTRODUCTION**

#### What is UVM?

Application-specific code Verification Environment Uses UVM building blocks Open source (Apache) Universal Verification Methodology Class library (UVM) Consistent methodology Facilitates interoperability Supported by all simulators SystemVerilog IEEE1800 Multi-language simulators **VCS**<sup>TM</sup> **IUS<sup>TM</sup>** Questa<sup>TM</sup> VHDL, Verilog, SystemVerilog, SystemC

## **Key Elements**

## SystemVerilog Language

- syntax

- RTL

- OOP

- class

- interface

- etc...

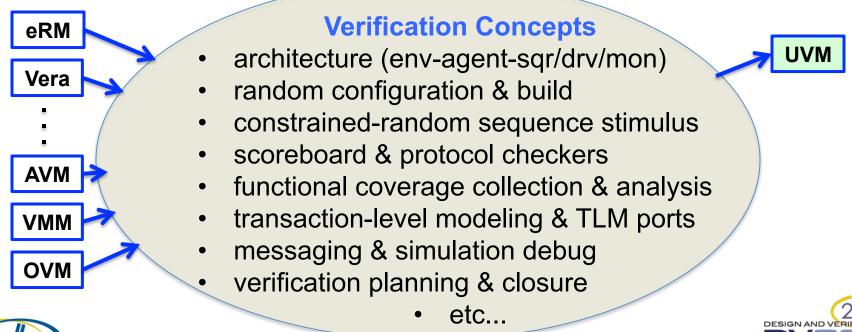

## **Verification Concepts**

- constrained-random

- coverage-driven

- transaction-level

- sequences

- scoreboards

- etc...

#### **UVM Methodology**

- base-classes

- use-cases

- configuration-db

- factory operation

- phases

- etc...

## SystemVerilog

- Language syntax & semantics are pre-requisite

- detailed understanding is not unique to UVM...

- ...but, verification superset much bigger than design!

#### **Design**

RTL

blocks

modules

vectors

assignments

arrays

etc.

#### Verification

signals

interfaces

clocking-block

scheduling

functions

tasks

etc.

OOP

class

random

constraints

coverage

queues

etc.

#### **Verification Concepts**

- Generic language-independent concepts apply

- detailed understanding is not unique to UVM...

- ...but, implementation details do vary!

## Methodology

#### Base-class library

- generic building blocks

- solutions to software patterns

- save time & effort

#### Way of doing things

- consistent approach

- facilitates interoperability

- engineering resource flexibility

range of **complexity**, implementation **difficulty**, and **learning** curve

- reg-model

- factory

- config-db

- callbacks

- parameterizing

- sequences

- seq-items

- transactions

- phases

- transaction-recording

- event-pool

- field-macros

- TLM-ports

- virtual-interfaces

- messaging

- components

- objects

DESIGN AND VERIE

#### **Tutorial Topics**

- Selected based on:

- experiences on many projects at different clients

- relatively complex implementation or confusing for user

- benefit from deeper understanding of background code

- require more description than available documentation

- Demystifying the UVM Configuration Database

- Behind the Scenes of the UVM Factory

- Effective Stimulus & Sequence Hierarchies

- Advanced UVM Register Modeling & Performance

## Demystifying the UVM Configuration Database

Vanessa Cooper, Verilab, Inc.

Paul Marriott, Verilab Canada

#### Introduction

- What is the uvm\_config\_db?

- When is the uvm\_config\_db used?

- How is data stored and retrieved?

- How do I debug when something goes wrong?

- Conclusion

## WHAT IS THE CONFIGURATION DATABASE

The **database** is essentially a lookup table which uses a string as a key and allows you to add and retrieve entries.

#### uvm\_resource\_db

- data sharing mechanism where hierarchy is not important

- each entry is called a resource

- when accessing the database, you must specify the resource type as a parameter

class uvm\_resource\_db#(type T=uvm\_object)

| Methods       | Description                                                                                |

|---------------|--------------------------------------------------------------------------------------------|

| get_by_type   | Gets the resource by the type specified by the parameter so the only argument is the scope |

| get_by_name   | Gets a resource by using both the scope and name                                           |

| set           | Creates a new resource in the database                                                     |

| read_by_name  | Locates the resource using the scope and name                                              |

| read_by_type  | Locates the resource using only the scope                                                  |

| write_by_name | Creates the resource by scope and name                                                     |

| write_by_type | Creates the resource by scope only                                                         |

TABLE 1: uvm\_resource\_db methods

**Example:** A scoreboard has a bit **disable\_sb** that turns off checking if the value is 1. How do you change the value of that bit using the **uvm\_resource\_db**?

All functions are static and must use scope resolution operator ::

**Example:** Using the uvm\_resource\_db with register tests

## WHEN IS THE CONFIGURATION DATABASE USED

The **database** is essentially a lookup table which uses a string as a key and allows you to add and retrieve entries.

#### uvm\_config\_db

- used when hierarchy is important

- can specify, with great detail, the level of access to a resource

- almost always used instead of the resource database

class uvm\_config\_db#(type T=int) extends uvm\_resource\_db#(T)

#### DATA STORAGE AND RETRIEVAL

cntxt: starting point he uvm\_config\_db ect from the *uvm\_config\_db* inst name: instance name which limits accessibility static function void set (uvm component cntxt, string inst name, string field name, T value)

field\_name: label used for lookup

value: value to be stored

cntxt: starting point

The Virtual Interface

inst\_name: instance name

which limits accessibility

field\_name: label used for lookup

value: value to be stored

\* should rarely be used

```

uvm_config_db#(TYPE)::set(uvm_root::get(),"*.path","label",value);

```

```

"retry_count" "rty_cnt"

"my_env_cfg" "env_cfg"

```

```

uvm_config_db#(TYPE)::get(this,"","label",value);

```

```

"retry_count" "rty_cnt"

```

#### **DEBUGGING**

What's the first step in debugging?

```

if(!uvm_config_db#(TYPE)::get(this,"","label",value))

`uvm_fatal("NOVIF", "Virtual interface GET failed.")

```

```

sim_cmd +UVM_TESTNAME=my_test +UVM_RESOURCE_DB_TRACE

```

```

sim_cmd +UVM_TESTNAME=my_test +UVM_CONFIG_DB_TRACE

```

```

UVM_INFO reporter [CFGDB/SET] Configuration "*_agent.*_in_intf"

(type virtual interface dut_if) set by = (virtual interface

dut_if)

```

```

UVM_INFO report [CFGDB/GET] Configuration

'uvm_test_top.env.agent.driver.in_intf" (type virtual interface

dut_if) read by uvm_test_top.env.agent.driver = (virtual

interface dut_if) ?

```

#### **CONCLUSION**

- The database is a powerful facility used in testbench constuction

- The resource database can be thought of as a pool of variables used without concern for hierarchy

- The configuration database is structured hierarchically and is more suited to data that is related to the structure of the testbench itself.

#### **REFERENCES**

## Additional Reading & References

- http://www.accellera.org

- Vanessa Cooper, Getting Started with UVM: A Beginner's Guide, 1<sup>st</sup> ed, Verilab Publishing, 2013

## Questions

## Behind the Scenes of the UVM Factory

Mark Litterick, Verilab GmbH.

#### Introduction

- Factory pattern in OOP

- standard software paradigm

- Implementation in OVM/UVM

- base-class implementation and operation

- Usage of factory and build configuration

- understanding detailed usage model

- Debugging factory problems & gotchas

- things the watch out for and common mistakes

- Conclusion

- additional reading and references

#### **FACTORY PATTERN**

#### Software Patterns

In **software engineering**, a **design pattern** is a general **reusable solution** to a commonly occurring problem within a given context.

- SystemVerilog is an Object-Oriented Programming language

- OVM/UVM make extensive use of standard OOP patterns

- Factory creation of objects without specifying exact type

- Object Pool sharing set of initialized objects

- Singleton ensure only one instance with global access

- Proxy provides surrogate or placeholder for another object

- Publisher/Subscriber object distribution to 0 or more targets

- Strategy/Policy implement behavioural parameter sets

- etc...

## The Factory Pattern

The factory method pattern is an object-oriented creational design pattern to implement the concept of factories and deals with the problem of creating objects without specifying the exact class of object that will be created.

- OVM/UVM implement a version of the factory method pattern

- Factory method pattern overview:

- define a seperate method for creating objects

- subclasses override method to specify derived type

- client receives handle to derived class

- Factory pattern enables:

- users override class types and operation without modifying environment code

- just add derived class & override line

- original code operates on derived class without being aware of substitution

substitute any component or object in the verification environment without modifying a single line of code

## Factory Usage in OVM/UVM

- Factory is an essential part of OVM/UVM

- required for test registration and operation

- recommended for all components

(env, agent, sequencer, driver, monitor, scoreboard, etc.)

- recommended for all objects(config, transaction, seq\_item, etc.)

- not appropriate for static interconnect

(TLM port, TLM FIFO, cover group, interface, etc.)

- Operates in conjunction with configuration

- both affect topology and behavior of environment

- factory responsible for inst and type overrides and construction

- configuration responsible for build and functional behavior

#### **FACTORY IMPLEMENTATION**

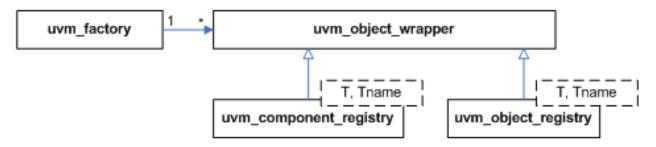

#### **OVM/UVM Factory Implementation**

#### **Factory Classes**

- The main O/UVM files are:

- o/uvm\_object\_defines.svh

- o/uvm\_registry.svh

- o/uvm\_factory.svh

a great **benefit** of **OVM/UVM** is that all **source-code** is **open-source**

- Overview:

- user object and component types are registered via typedef

- factory generates and stores proxies: \*\_registry#(T,Tname)

- proxy only knows how to construct the object it represents

- factory determines what type to create based on configuration, then asks that type's proxy to construct instance for the user

#### User API

Register components and objects with the factory

```

`uvm_component_utils(component_type)

`uvm_object_utils(object_type)

```

```

do not use deprecated sequence*_utils

```

- Construct components and objects using create not new

- components should be created during build phase of parent

```

component_type::type_id::create("name",this);

object_type::type_id::create("name",this);

```

Use type-based override mechanisms

```

set_type_override_by_type(...);

set_inst_override_by_type(...);

```

# `uvm\_component\_utils - Macro

```

define uvm component utils(T) \

class my comp extends uvm component;

`uvm component utils(my comp)

endclass

class my comp extends uvm component;

typedef uvm component registry # (my comp, "my comp") type id;

static **unction type id get_type();

return type id::get();

explains what <a href="my_comp::type_id">my_comp::type_id</a> is

declared a typedef specialization

t wrapper get object type();

of uvm_component_registry class

but what about register and ::create ???

endfunction

const static string type name = "my comp";

virtual function string get type name ();

return type name;

endfunction

endclass

```

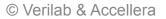

#### uvm\_component\_registry - Register

```

class uvm component registry

proxy type

#(type T, string Tname) extends uvm

lightweight substitute for real object

typedef uvm component registry # (T, Tname) this type;

local static this type me = get();  local static proxy variable calls get()

static function this type get();

if (me == null) begin

construct instance of proxy, not real class

uvm factory f = uvm factory::get();

me = new;

register proxy with factory

f.register(me);

end

registration is via static initialization

return me;

=> happens at simulation load time

endfunction

function void uvm factory::register (uvm object wrapper obj);

virtu

stati

// add to associative arrays

stati

m type names[obj.get type name()] = obj;

stati

m types[obj] = 1;

endclas

to register a component type, you only need a typedef

specialization of its proxy class, using `uvm_component_utils

```

SYSTEMS INITIATIVE

#### uvm\_component\_registry - Create

```

comp = my_comp::type_id::create("comp",this);

```

uvm\_component\_registry # (my\_comp, "my\_comp")

static **create** function

```

class uvm component registry #(T, Tname) extends uvm object wrapper;

static function T create(name, parent, contxt="");

uvm_object obj; / request factory create based on existing type overrides (if any)

uvm factory f vvm factory::get();

obj = f.create component_by_type get(), contxt, name, parent);

i f

rt fatal(...);

return handle to real override object

virtual function uvm_component create_component (name, parent);

T obi;

search queues for overrides

obj = new(name, parent)//

function uvm component uvm factory::create_component_by_type

ndf

(type, contxt, name parent);

requested type = nd override by type (requested type, path);

endcla return requested type create component (name, parent);

endfunction

call create_component for proxy of override type

```

#### **Factory Overrides**

not shown: use static \*\_type::get\_type() in all cases

- Users can override original types with derived types:

- using registry wrapper methods

```

original_type::type_id::set_type_override(override_type);

```

```

original_type::type_id::set_inst_override(override_type,...);

```

using component factory methods

```

set_type_override_by_type(original_type,override_type);

```

```

set_inst_override_by_type(...,original_type,override_type);

```

Factory constructs override descriptor and adds to a queue:

```

function void uvm_factory::set_type_override_by_type (...);

override = new(...);

m_type_overrides.push_back(override);

endfunction

```

this is the queue searched by uvm\_factory::find\_override\_by\_type

#### **Factory Operation**

# Summary of Factory Operation

- users only have to call macros to register types with factory

- resulting typedef is enough for registration to occur

- static initialization registers proxy classes with factory

- call type\_id::create instead of new

- allows factory to search for type overrides

- factory creates instance of required type and returns handle

- components call create in build phase to allow configuration

- override using type-based interface

- factory constructs descriptor of override and adds to queue

- overrides can be per-instance or for all instances of that type

- override types must derive from original types

- external files can modify environment class structure and behavior without changing code

#### **CONFIGURATION DATABASE**

# **OVM/UVM Configuration Overview**

OVM & UVM provide global and component set/get\_config\*

for int (integral), string and object types, e.g.

```

set_config_object("inst","field",value,0);

if (!this.get config object("field",value)) `uvm fatal(...)

```

UVM these are mapped to config\_db, e.g. (simplification)

```

function void set_config_object("inst","field",value);

uvm_config_db#(uvm_object)::set(this,"inst","field",value);

endfunction

```

In UVM it is recommended to use config\_db explicitly

```

uvm_config_db#(my_type)::set(cntxt,"inst","field",value);

```

Implements string-based lookup tables in a database

set methods do not configure targeted component fields directly

#### **Automatic Field Configuration**

Normally the user has to do an explicit get from db, e.g.

```

uvm_config_db#(my_type)::get(this,"","field",value)

```

build phase for component base-class automatically configures all fields registered using field macros

```

function void uvm_component::build_phase(...);

apply_config_settings(..); // search for fields & configure

endfunction

```

build phase for derived comps must call super.build

```

class my_comp extends

`uvm_component_uti] missing field-macro results in no auto-config

`uvm_field_int(my_field,UVM_DEFAULT)

...

function void buil missing super.build results in no auto-config

super.build_phase(..);

// class-specific build operations like create

```

# INTERACTION OF FACTORY & CONFIGURATION

#### **Example Environment**

```

class my comp extends uvm component;

`uvm component utils(my comp) <

register class type with factory

endclass

class my_obj extends uvm_object;

`uvm object utils(my obj)

endclass

class my env extends uvm env;

my comp comp;

my obj obj;

register field for automation

`uvm component utils begin(my env)

`uvm field object(obj,UVM DEFAULT)

`uvm component utils end

allow auto-config using apply_config_settings()

function new(..);

function void build phase(..);

(example) requires obj to be in config db

super.build phase(..);

(there is no create/new inside this env)

if (obj==null) `uvm fatal(...

comp = my comp::type id::create("comp", this);

endfunction

use create() instead of new() for children

endclass

```

DESIGN AND VERIFICA

# **Example Configure and Override**

```

class test comp extends my comp;

must be derived in order to substitute

`uvm component utils(test comp)

// modify behavior

"class test comp extends uvm component;"

endclass

does not work, must be derived from my_comp

class my test extends uvm t

my env env;

my obj obj;

`uvm component utils(my test)

function new(..);

create using factory (results only in new not build)

function void build phase

super.build_phase(..);

env = my env::type id::create("env", this);

obj = my_obj::type id::create("obj",this);

set_type_overide_by_type(

override type in factory prior to env::build

my comp::get type(),

test comp::get type());

configure obj in db prior to env::build

set config object("env", "obj", obj, 0);

endfunction

build phase is top-down

endclass

lower-level child::build comes after parent::build completed

accellera

```

SYSTEMS INITIATIVE

#### Override Order

override env and comp before my\_env::type\_id::create is always OK

remember create only results in a new() not a build

```

function void my_test: build_phase(..);

...

set_type_overide_by_type(my_comp, test_comp); // Good

set_type_overide_by_type(my_env, test_env); // Good

env = my_env::type_id::create("env", this);

set_type_overide_by_type(my_comp, test_comp); // Good

set_type_overide_by_type(my_env, test_env); // Bad

```

override comp after my\_env::type\_id::create is OK since my\_comp is not yet created (it is created later in my\_env::build\_phase)

override env after my\_env::type\_id::create is BAD since my\_env is already created (hence override is simply ignored)

endfunction

# Configure Order

set\_config using a null value is an error

(obj is not yet constructed)

endfunction

acceliera )

SYSTEMS INITIATIVE

set\_config after obj is created and before env is created is OK

(env create does not use the value anyway)

```

set_config_object("env","obj",obj,0); // Bad

obj = my_obj::type_id::create("obj",this);

set_config_object("env","obj",obj,0); // Good

env = my_env::type_id::create("env",this);

set_config_object("env","obj",obj,0); // Good

...

```

set\_config after both obj and env are created is also OK

(obj setting in config\_db is not used until env::build phase)

so set\_config\* can come before or after the create for corresponding component!

do not confuse create (which tells the factory to new original or override type) with build phase (which is top-down dynamic building of environment)

#### Interaction of Factory, Config & Build

```

test

class my test extends uvm test;

env

function new(..);

test

function void build phase(..);

comp

env = my env::type id::create("env", this);

obj = my obj::type id::create("obj", this\( ; );

obi

set type overide by type (my comp, test comp);

set_config_object("env", "obj", obj, 0);

endfunction

obi

endclass

factory

class my env extends uvm env;

test

`uvm field object(obj,UVM DEFAULT)

comp

function void build phase(..);

super.build phase(..);

if (obj==null) `uvm fatal(..)

comp = my comp::type id::create("comp", this);

obi

endfunction

endclass

```

# FACTORY & CONFIGURATION PROBLEMS

#### **Problem Detection**

- Factory and configuration problems are especially frustrating

- often the code compiles and runs, because it is legal code

- but ignores the user overrides and specialization

- Different kinds of problems may be detected:

- at compile time (if you are lucky or careless!)

- at run-time (usually during initial phases)

- never...

- ...by inspection only!

- Worse still, accuracy of report is tool dependant

- although some bugs are reported by OVM/UVM base-classes

factory and configuration problems are a special category of bugs

#### Common Factory Problems

- using new instead of ::type\_id::create

- typically deep in hierarchy somewhere, and not exposed

- deriving override class from same base as original class

- override class must derive from original class for substitution

- performing ::type\_id::create on override instead of original

- this will limit flexibility and was probably not intended

- factory override after an instance of original class created

- this order problem is hard to see and reports no errors

- confusing class inheritance with build composition

- super has nothing to do with parent/child relationship

- it is only related to super-class and sub-class inheritance

- bad string matching and typos when using name-based API

- name-based factory API is not recommended, use type-based

# **Common Configuration Problems**

- missing field macro when using automatic configuration

- apply\_config\_settings() only works with registered fields

- missing super.build\* when using automatic configuration

- apply\_config\_settings() is only in uvm\_component base

- missing config\_bd::get when config\_db::set was used

- config\_db::set does not interact with apply\_config\_settings()

- need an explicit config\_db::get to retrieve settings

- attempting set\_config\_object on a null object

- bad string matching and typos for inst and name settings

- scope and context problems with string-based config

#### **Debugging Hints**

- call factory.print() in base-test end\_of\_elaboration phase

- prints all classes registered with factory and current overrides

```

if (uvm report enabled(UVM FULL)) factory.print();

```

- call this.print() in base-test end\_of\_elaboration phase

- prints the entire test environment topology that was actually built

```

if (uvm_report_enabled(UVM_FULL)) this.print();

```

- temporarily call this.print() anywhere during build

- e.g. at the end of relevant suspicious new and build\* functions

- use +UVM\_CONFIG\_DB\_TRACE to debug configuration

- pay attention to the handle identifiers in tool windows

- e.g. component@123 or object@456

- they should be identical for all references to the same thing

#### **CONCLUSION & REFERENCES**

#### Conclusion

- OVM/UVM Factory is easy to use

- simple user API and guidelines

- complicated behind the scenes

- can be difficult to debug

- Standard OOP pattern not invented for OVM/UVM

- Used in conjunction with configuration to control testbench

- topology, class types, content and behavior

- without modifying source code of environment

- You do not need to understand detailed internal operation

- but OVM/UVM have open-source code

- so we can see how it is implemented and learn...

- ...cool stuff that keeps us interested and informed!

# Additional Reading & References

- OVM and UVM base-class code

- OVM and UVM class reference documentation

- "The OVM/UVM Factory & Factory Overrides: How They Work

- Why They Are Important"

- SNUG 2012, Cliff Cummings, <u>www.sunburst-design.com</u>

- "Improve Your SystemVerilog OOP Skills: By Learning Principles and Patterns"

- SVUG 2008, Jason Sprott, <u>www.verilab.com</u>

- https://verificationacademy.com/sessions/understandingfactory-and-configuration

- Verification Academy Video, Mentor

- http://cluelogic.com/2012/11/uvm-tutorial-for-candylovers-10-inside-candy-factory/

- UVM Tutorial, ClueLogic

*accellera*

SYSTEMS INITIATIVE

# Questions

# **UVM Stimulus and Sequences**

Jonathan Bromley, Verilab Ltd Mark Litterick, Verilab GmbH

#### Introduction

• tbd

#### **GETTING THE BASICS RIGHT**

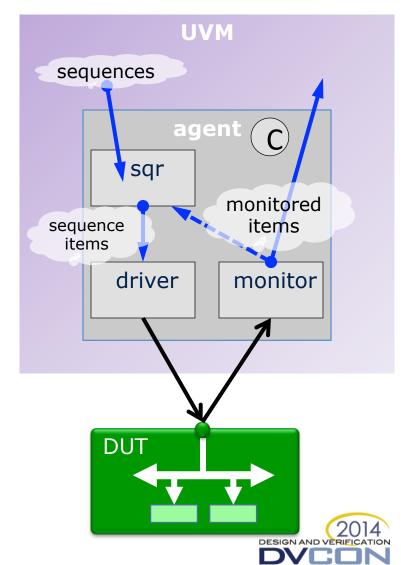

#### UVM stimulus architecture review

- Monitor+driver+sequencer

active agent

implementing a protocol

- Stimulus driven into DUT by a *driver*

- Stimulus data sent to driver from a sequencer

- Run sequences on sequencer to make interesting activity

# Stimulus transaction class (item)

Item base class should contain ONLY transaction data

Stimulus item needs additional constraints and control knobs

```

class vbus_seq_item extends vbus_item;

rand bit only_IO_space;

constraint c_restrict_IO {

only_IO_space -> (addr >= 'hFC00);

} ...

```

Bus protocol controls *only*! Class is part of uVC

sequences

sequence

items

driver

- NO distribution constraints

- NO DUT-specific strategy

monitored

monitor

# Low-level sequences

Simple, general-purpose stream of transactions with some coordination

Not DUT-specific! Supplied with the uVC

```

class vbus seq block wr extends vbus sequence;

rand bit [15:0] block size;

sequences

rand bit [15:0] base addr;

constraint c block align {

block size inside {1,2,4,8,16};

sar

monitored

addr % block size == 0;

NO distribution constraints

items

NO DUT-specific strategy

driver

monitor

rand vbus seq item item;

task body();

for (int beat=0; beat<block size; beat++) begin

`uvm do with ( item,

{addr==base addr+beat; dir==WR;} )

end

Behaviour is meaningful even without any external constraint

endtask

```

#### The story so far...

- provides a flexible base for customization

- does not restrict the uVC's applicability

- already interesting for reactive slave sequences

- predominantly random

- more guidance later in this section

- may be useful for simple bring-up tests

#### **LAUNCHING SEQUENCES**

# Launching a sequence: `uvm\_do

- On same sequencer, from another sequence's body

- good for simple sequence hierarchy

```

class vbus_seq_block_wr ...

rand bit [15:0] block_size;

rand bit [15:0] base_addr;

```

constraint using values picked from previous sequence's randomization

#### Launching a sequence: `uvm do on

**UVM**  On a different sequencer virtual sequencer sequence good for virtual sequences p sequencer sgr i sgr v uvm\_do\_on 92c\_seq vbus sea class collision seq extends dut sequence; M M `uvm object utils(collision seq) `uvm declare p sequencer (dut sequencer datatype of virtual sequencer vbus write seq vbus seq; i2c write seq i2c seq; properties of the virtual sequencer task body(); fork `uvm do on with (vbus seq, p sequencer.sqr  $v_{1}$ {...}) `uvm\_do\_on\_with(i2c seq, p sequencer.sqr i, \*\{\ldots\}) join

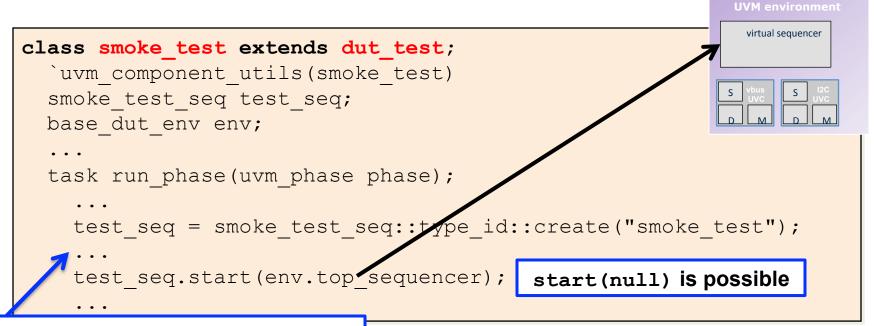

### Launching a sequence: start

- Can be called from any code

- Always used to start top-level test sequence

configure/randomize the test seq

## Review of UVM1.2 changes

- Default sequence of sequencer is deprecated

- <describe other consequent changes>

## Exploiting the sequencer

- m\_sequencer

- reference to the sequencer we're running on

- datatype is uvm\_sequence, too generic for most uses

- p\_sequencer

- exists only if you use `uvm\_declare\_p\_sequencer

- has the correct data type for the sequence's expected sequencer class

- allows access to members of that class

- persistent data across the life of many sequences

- storage of configuration information, sub-sequencer references, ...

## Virtual sequences and sequencers

- Without a sequence item

- Roles and responsibilities

- Methodology details come later in this section

## Sequences without sequencers?

- We recommend you do not do this

- A hierarchy of sequencers allows clear isolation of concerns

- each layer of the TB takes responsibility for its own activity

- make use of facilities provided by lower levels

- Each sequencer can be given references to all the lower-level sequencers it needs to use

## Example hierarchical sequences

- TBD: example showing different styles of constraint and different sequence design concerns at each level

- lowest (UVC) level: completely generic, no strategy, only legality and control knobs to configure legality and basic values

- UVC sequence library level: a big repertoire of sequences to perform typical operations, with control knobs relevant to those operations

- DUT level: coordinate sequences across multiple UVCs to establish setup activity, typical operation scenarios, error conditions

## Responsibilities of sequences at various levels

- TBD: see previous slide, closer look at concerns on each level

- role of control knobs in seq vs. scenario

- different styles of constraint at different levels

## Readback from a sequence

- If a sequence does something that returns a result...

- read data from a bus

- transaction has a response value

- ...later parts of the sequence may need the result

- For a sequence item: get result directly from the item when the sequence has finished

- For a sequence: provide storage in the sequence, populate from lower-level sequence or item

- needs consistent planning through the sequence hierarchy

## Readback from a sequence

- TBD: several slides illustrating preferred techniques

- brief mention of methods based on use of the monitor

- some mention of item\_done() responses, generally discouraged - better to use ref to request item

## Using a uvm\_reg model in sequences (briefly!)

- built-in reg sequences

- reading and writing registers

## How sequences should interact with the config DB and user config objects

- Sequences should avoid pulling data directly from the config-DB

- heavy performance overhead

- As always, populate a config object from the config DB at build time

- A reference to a centralized config object means that value updates in the central object are automatically visible

- Sequence should look into its sequencer to find config object

- using p\_sequencer

## Guidelines for using objections in sequences

- roughly, don't

- but there are some exceptions

- TBD: prescriptive guidance and suggestions, probably "only in top level test sequence" (???)

## A couple of fancy examples:

#### TBD:

- interrupt sequence (illustrate use of grab)

- random choice of sequence in a scenario (using uvm\_sequence\_library????)

#### **CONCLUSION & REFERENCES**

### Conclusion

• TBD

## Additional Reading & References

- UVM base-class code

- UVM class reference documentation

• ...

## Questions

# Advanced UVM Register Modeling & Performance

Mark Litterick, Verilab GmbH.

#### Introduction

- UVM register model overview

- structure, integration, concepts & operation

- field modeling, access policies & interaction

- behavior modification using hooks & callbacks

- Modeling examples

- worked examples with multiple solutions illustrated

- field access policies, field interaction, model interaction

- Register model performance

- impact of factory on large register model environments

#### **REGISTER MODEL OVERVIEW**

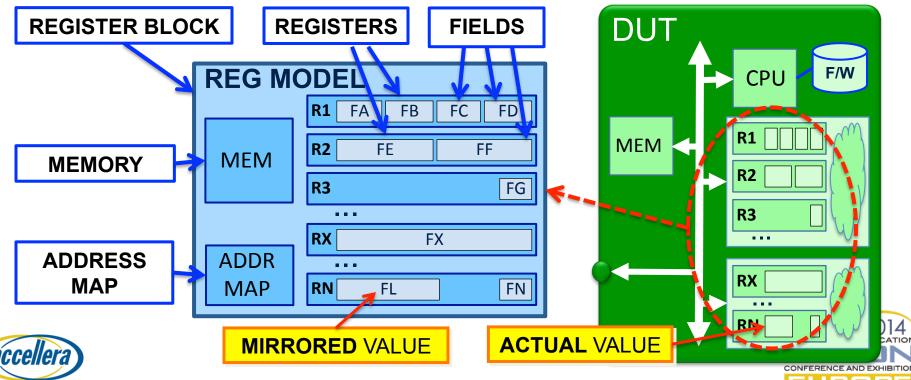

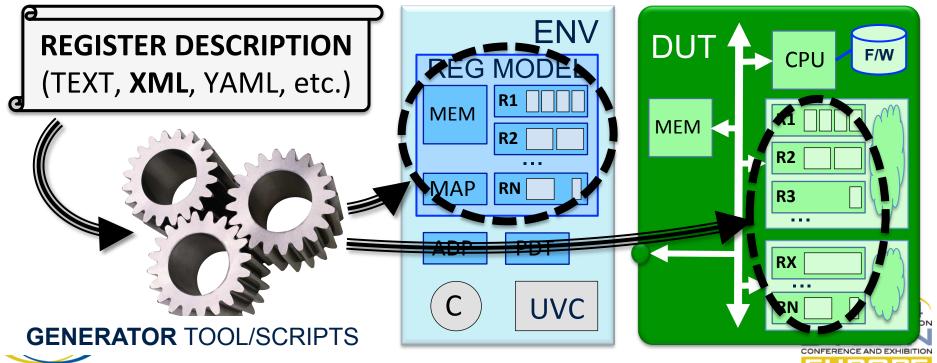

## Register Model Structure

- Register model (or register abstraction layer)

- models memory-mapped behavior of registers in DUT

- topology, organization, packing, mapping, operation, ...

- facilitates stimulus generation, checks & coverage

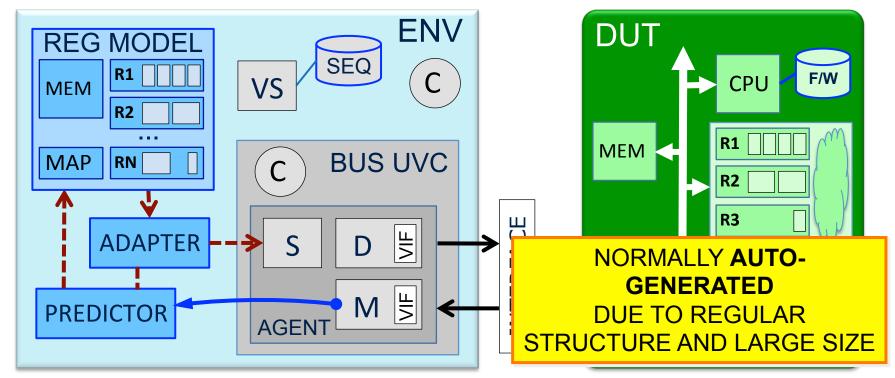

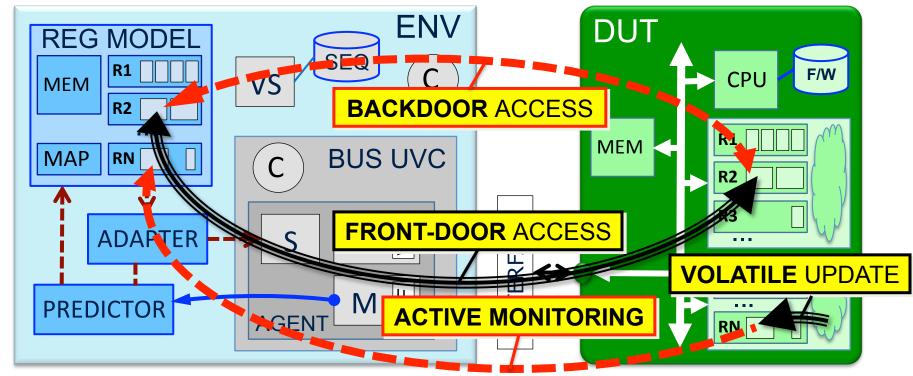

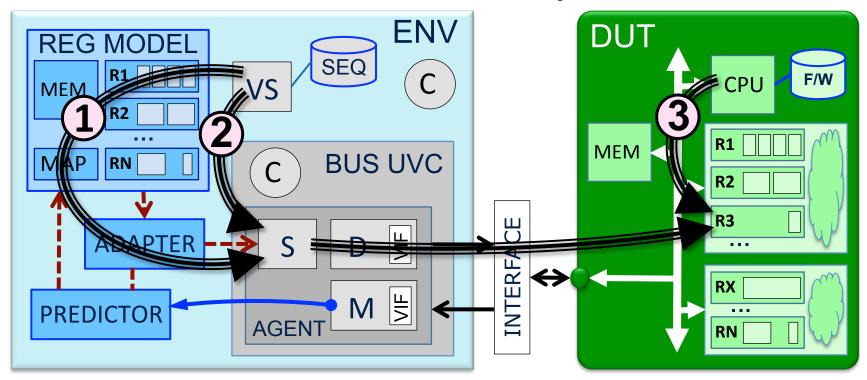

## Register Model Integration

- Set of DUT-specific files that extend uvm\_reg\* base

- Instantiated in env alongside bus interface UVCs

- adapter converts generic read/write to bus transactions

- predictor updates model based on observed transactions

*accellera*

## Register Model Concepts

- Normal front-door access via bus transaction & I/F

- sneaky backdoor access via hdl\_path no bus transaction

- Volatile fields modified by non-bus RTL functionality

- model updated using active monitoring via hdl\_path

accellera

### **Active & Passive Operation**

- Model must tolerate active & passive operations:

- 1. active model read/write generates items via adapter

- 2. passive behavior when a sequence does not use model

- 3. passive behavior when embedded CPU updates register

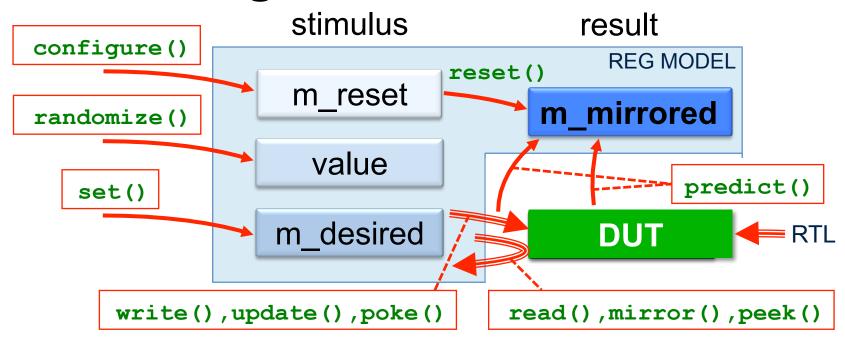

### Register Access API

- Use-case can be register or field-centric

- constrained random stimulus typically register-centric e.g. reg.randomize(); reg.update();

- directed or higher-level scenarios typically field-centric

e.g. object.randomize(); field.write(object.var.value);

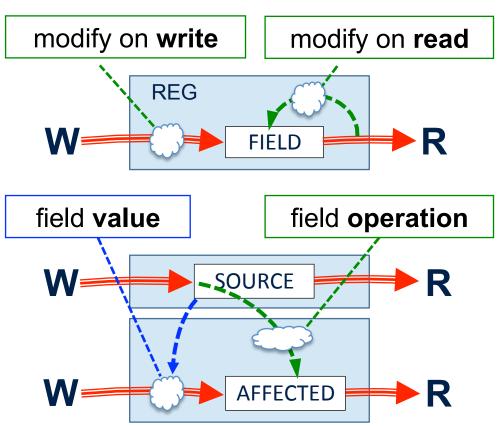

## Register Field Modeling

- Field access policy

- self-contained operations on this register field

Field interaction

*áccellera*

SYSTEMS INITIATIVE

between different register fields

- Register access rights in associated memory map

- Model functional behavior of DUT for volatile fields 20

#### Field Access Policies

Comprehensive pre-defined field access policies

|               | NO<br>WRITE | WRITE<br>VALUE | WRITE<br>CLEAR         | WRITE<br>SET           | WRITE<br>TOGGLE                                           | WRITE<br>ONCE                         |  |

|---------------|-------------|----------------|------------------------|------------------------|-----------------------------------------------------------|---------------------------------------|--|

| NO<br>READ    | -           | wo             | woc                    | wos                    | -                                                         | WO1                                   |  |

| READ<br>VALUE | RO          | RW             | WC<br>W1C<br>W0C       | WS<br>W1S<br>W0S       | W1T<br>W0T                                                | W1                                    |  |

| READ<br>CLEAR | RC          | WRC            | -                      | WSRC<br>W1SRC<br>W0SRC | Just <b>defining</b> access policy is <i>not enough</i> ! |                                       |  |

| READ<br>SET   | RS          | WRS            | WCRS<br>W1CRS<br>W0CRS | -                      |                                                           | Must also implement special behavior! |  |

User-defined field access policies can be added

#### **Hooks & Callbacks**

- Field base class has empty virtual method hooks

- implement in derived field to specialize behavior

```

class my_reg_field extends uvm_reg_field;

virtual task post_write(item rw);

// specific implementation

endtask

```

pre\_write post\_write pre\_read post\_read

pre write

post\_write

pre read

post read

encode

decode

post\_predict

- Callback base class has empty virtual methods

- implement in derived callback & register it with field

```

class my_field_cb extends uvm_reg_cbs;

function new(string name, ...);

virtual task post_wr

// specific implem endtask

my field cb my cb = new("my cb", ...);

my field cb my cb = new("my cb", ...);

```

uvm reg field cb::add(regX.fieldY, my cb);

*áccellera*

#### **Hook & Callback Execution**

- Field method hooks are always executed

- Callback methods are only executed if registered

```

task uvm_reg_field::do_write(item rw);

...

rw.local_map.do_write(rw);

...

post_write(rw);

for (uvm_reg_cbs cb=cbs.first();

cb!=null;

cb=cbs.next())

cb.post_write(rw);

endtask

- CALLBACK METHOD

FOR ALL REGISTERED CBS

```

callback methods executed in cbs queue order

#### **MODELING EXAMPLES**

## Write-to-Reset Example

- Example user-defined field access policy

- pre-defined access policies for Write-to-Clear/Set (WC,WS)

- user-defined policy required for Write-to-Reset (WRES)

```

uvm_reg_field::define_access("WRES")

```

- Demonstrate three possible solutions:

- post\_write hook implementation in derived field

- post\_write implementation in callback

- post\_predict implementation in callback

## WRES Using *post\_write* Hook

```

class wres field t extends uvm reg field;

DERIVED FIELD

virtual task post write(uvm reg item rw);

if (!predict(rw.get_reset())) `u

IMPLEMENT post write TO

NOT PASSIVE

SET MIRROR TO RESET VALUE

class wres reg t extends uvm reg;

USE DERIVED FIELD

rand wres field t wres field; <

FIELD CREATED IN REG::BUILD

function void build();

// wres field create()/configure(.."WRES"..)

class my reg block extends uvm reg block;

rand wres reg t wres reg;

REGISTER CREATED IN BLOCK::BUILD

function void build();

// wres reg create()/configure()/build()/add map()

```

reg/block build() is not component build\_phase()

## WRES Using *post\_write* Callback

```

class wres field cb extends uvm reg cbs;

DERIVED CALLBACK

virtual task post write(uvm reg item rw);

if (!predict(rw.get reset()))

IMPLEMENT post write TO

NOT PASSIVE

SET MIRROR TO RESET VALUE

class wres reg_t extends uvm_reg;

rand uvm_reg_field wres field; <

USE BASE FIELD

function void build();

// wres field create()/configure(.."WRES"..)

class my reg block extends uvm reg blo

CONSTRUCT CALLBACK

rand wres reg t wres reg;

REGISTER CALLBACK

WITH REQUIRED FIELD

function void build();

// wres reg create()/configure()/build()/add map()

wres_field_cb wres_cb = new("wres_cb");

uvm reg field cb::add(wres reg.wres field, wres cb);

accell

```

## WRES Using post\_predict Callback

```

IMPLEMENT post_predict TO

class wres field cb extends

SET MIRROR VALUE TO RESET STATE

virtual function void post predict (..., fld, value, ...);

if(kind==UVM PREDICT WRITE) value = fld.get reset();

PASSIVE OPERATION

virtual

function void post predict(

input

uvm reg field

fld,

class wres reg t exter

input

uvm reg data t

previous,

rand uvm reg field w

inout

uvm reg data t

value,

uvm predict e

input

kind,

function void build(

input

uvm path e

path,

// wres field create

input

uvm reg map

map

class my reg bloc

if we use this callback

post predict is only

rand wres reg t

with a register we get

available for fields

not registers

silent non-operation!

function void bu

// wres_reg create()/configure()/build()/add map()

wres field cb wres cb = new("wres cb");

```

uvm reg field cb::add(wres reg.wres field, wres cb);

17

accell

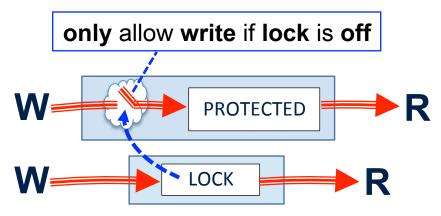

## Lock/Protect Example

- Example register field interaction

- protected field behavior based on state of lock field, or

- lock field operation modifies behavior of protected field

- Demonstrate two possible solutions:

- post\_predict implementation in callback

- dynamic field access policy controlled by callback

- (not **bad** pre\_write implementation from UVM User Guid

## Lock Using post\_predict Callback

```

class prot field cb extends uvm reg cbs;

HANDLE TO

local uvm reg field lock field; <

LOCK FIELD

function new (string name, uvm reg field lock);

super.new (name);

this.lock field = lock;

endfunction

virtual function void post_predict(..previous, value);

if (kind == UVM PREDICT WRITE)

REVERT TO PREVIOUS

if (lock field.get())

VALUE IF LOCK ACTIVE

value = previous; <</pre>

endfunction

CONNECT LOCK FIELD

class my reg block extends uvm reg block;

prot field cb prot cb = new("prot cb", lock field);

uvm req field cb::add(prot field, prot cb);

```

REGISTER CALLBACK

WITH PROTECTED FIELD

# Lock Using Dynamic Access Policy

```

class lock field cb extends uvm reg cbs;

HANDLE TO

local uvm_reg_field prot field; <

PROTECTED FIELD

function new (string name, uvm reg field prot);

super.new (name);

this.prot field = prot;

endfunction

SET ACCESS POLICY FOR

virtual function void post predict

PROTECTED FIELD BASED ON

if (kind == UVM PREDICT WRITE)

LOCK OPERATION

if (value)

void'(prot field.set access("RO"))

else

prot field.get access()

void'(prot field.set access("RW'

RETURNS CURRENT POLICY

en

REGISTER CALLBACK

WITH LOCK FIELD

CONNECT PROTECTED FIELD

```

RIFICATION

CHENCE AND EXHIBITION

accell

SYSTEMS INITIATIVE

class my reg block extends uvm reg block;

uvm reg field cb::add(lock field, lock cb);

lock field cb lock cb new("lock cb", prot field);

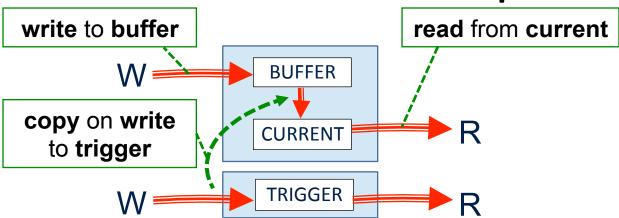

### Buffered Write Example

- Example register field interaction

- trigger field operation effects buffered field behavior

- Demonstrate two possible solutions:

- overlapped register implementation with callback

- derived buffer field controlled by multiple callbacks

# Buffered Write Using 2 Registers

```

HANDLES TO BOTH

class trig field cb extends uvm reg o

CURRENT & BUFFER FIELDS

local uvm reg field current, buffer;

function new (string name, uvm reg field current,

uvm reg field buffer);

COPY FROM BUFFER TO CURRENT

virtual function void post predi

ON WRITE TO TRIGGER

if (kind == UVM PREDICT WRITE) begin

uvm req data t val = buffer.get mirrored value();

if (!current.predict(val))

RO & WO REGISTER AT SAME ADDRESS

all writes go to WO buffer

class my reg block extends uvn

all reads come from RO current

default_map.add reg(cur reg, 'h10, "RO");

default map.add reg(buf reg,

'h10, "WO");

cannot share address again

REGISTER CALLBACK WITH TRIGGER FIELD

complicated to generate

cur field, buf reg.buf field);

confusing map for user

```

22

uvm reg rreru co..auu trig field, trig cb);

accene

### Buffered Write Using Derived Field

```

class buf reg field extends uvm reg field;

uvm reg data t buffer; <-</pre>

ADD BUFFER TO DERIVED FIELD

virtual function void reset (string king);

super.reset(kind);

RESET BUFFER TO FIELD RESET VALUE

buffer = get reset(kind);

post predict callback

class buf field cb extends uvm reg cbs;

required for passive

local buf reg field buf field;

virtual function void post predict(...); // if write

buf_field.buffer = value SET BUFFER TO VALUE ON WRITE TO FIELD,

value = previous;

SET MIRROR TO PREVIOUS (UNCHANGED)

class trig_field cb extends uvm reg cbs;

local buf reg field buf field;

COPY BUFFER TO MIRROR

ON WRITE TO TRIGGER

virtual function void post predict...

buf field.predict(buf field.buffer);

REGISTER CALLBACKS WITH

buf field cb buf cb = new("buf cb"

BUFFERED & TRIGGER FIELDS

uvm reg field cb::add(buf field, bull cb),

trig field cb trig_cb = new("trig cb",buf field);

uvm reg field cb::add(trig field, trig cb);

```

23

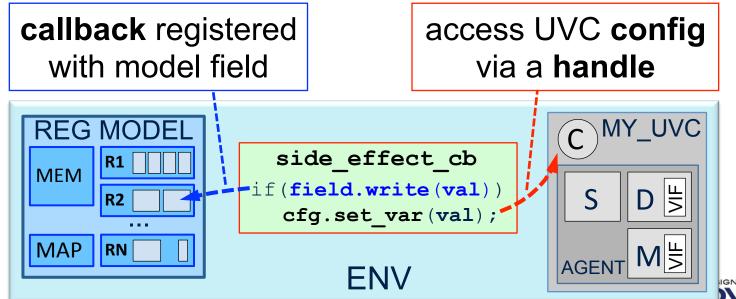

### Register Side-Effects Example

- Randomize or modify registers & reconfigure DUT

- what about UVC configuration?

- update from register sequences

**snoop** on DUT bus transactions

• implement *post\_predict* callback | passive & backdoor

## Config Update Using Callback

```

class reg cfg cb extends uvm reg cbs;

my config cfg; <-

HANDLE TO CONFIG OBJECT

function new (string name, my config cfg);

super.new (name);

this.cfg = cfg;

endfunction

SET CONFIG ON WRITE

TO REGISTER FIELD

virtual function void post predict

(TRANSLATE IF REQUIRED)

if (kind == UVM PREDICT WRITE)

cfg.set var(my enum t'(value));

endfunction

ENVIRONMENT HAS

class my env extends uvm env;

UVC & REG MODEL

uvc = my uvc::type id::create(...);

CONNECT CONFIG

reg model = my reg block::type id::create(

REGISTER CALLBACK

reg cfg cb cfg cb = new("cfg cb", uvc.cfg);

uvm reg field cb::add(reg model.reg.field, cfg_cb);

```

#### REGISTER MODEL PERFORMANCE

#### Performance

- Big register models have performance impact

- full SoC can have >10k fields

MANY REGISTER CLASSES (MORE THAN REST OF ENV)

- Register model & RTL typically auto-generated

- made-to-measure for each device deri

DIFFERENT USE-CASE

THAN FACTORY

### Life Without The Factory

- Example SoC with 14k+ fields in 7k registers

- many register classes (most fields are base type)

- not using factory overrides generated on demand

| MODE                     | FACTORY | COMPILE | LOAD | BUILD | DISK  |

|--------------------------|---------|---------|------|-------|-------|

|                          | TYPES   | TIME    | TIME | TIME  | USAGE |

| NO REGISTER MODEL        | 598     | 23      | 9    | 1     | 280M  |

| +REGISTERS USING FACTORY | 8563    | 141     | 95   | 13    | 702M  |

| +REGISTERS NO FACTORY    | 784     | 71      | 17   | 1     | 398M  |

COMPILE TIME x2 +1 min infrequently LOAD + BUILD TIME x5 +1.5 min for every sim

- Register model still works without the factory

- do not use uvm\_object\_utils macro for fields & registers

- construct registers using new instead of type\_id::create

*accellera*

# `uvm\_object\_utils

```

define uvm object utils(T) \

<u>m uvm object registry internal(T,T)</u>

tion

class my reg extends uvm reg;

`uvm object utils(my req)

endclass

define m uvm object registry internal (T

class my reg extends uvm reg;

typedef uvm_object_registry # (my reg, "my reg") type_id;

static function type_id get_type();

return type id::get();

explains what <a href="my_reg">my_reg::type_id</a> is

declare a typedef specialization

t wrapper get_object_type();

of uvm_object_registry class

but what about factory registration

endfunction

and type_id::create ???

function uvm object create (strin

const static string type name = "my reg";

viplual function string get_type_name ();

return type name;

declare some methods

for factory API

```

accenera )

### uvm\_object\_registry

```

class uvm object registry

proxy type

#(type T, string Tname) extends uv

lightweight substitute for real object

typedef uvm object registry # (T, Tname) this type;

local static this type me = get();

local static proxy variable calls get()

static function this type get();

if (me == null) begin

construct instance of proxy, not real class

uvm factory f = uvm factory: qet();

me = new;

register proxy with factory

f.register(me);

end

registration is via static initialization

return me;

=> happens at simulation load time

endfunction

function void uvm_factory::register (uvm_object_wrapper obj);

virtu

stati

// add to associative arrays

stati

m type names[obj.get type name()] = obj;

stati

endcla.

thousands of registers means thousands of proxy classes

are constructed and added to factory when files loaded

```

do not need these classes for register generator use-case!

EURORE

### type\_id::create

```

class uvm_object_registry #(T, Tname) extends uvm_object_wrapper;

...

static function T create(name, parent, contxt="");

uvm_object obj; request factory create based on existing type overrides (if any)

uvm_factory f uvm_factory::get();

obj = f.create_object_by_type(get(), contxt, name, parent);

if return handle to object

virtual function uvm_object create_object (name, parent);

T obj;

obj = new(name, parent)

constructs actual object uvm_factory::create_object_by_type

reconstructs actual object uvm_factory::create_object_by_type

```

during the pre-run phase for the environment (build time)

end

no need to search for overrides for register generator use-case!

#### Conclusions

- There's more than one way to skin a reg...

- but some are better than others!

- consider: passive operation, backdoor access, use-cases,...

- Full-chip SoC register model performance impact

- for generated models we can avoid using the factory

- All solutions evaluated in UVM-1.1d & OVM-2.1.2

- updated uvm\_reg\_pkg that includes UVM-1.1d bug fixes (available from www.verilab.com)

# Questions