## TUTORIAL: Achieving Portable Stimulus with Graph-Based Verification

25 September 2014

# **Tutorial Objectives**

- Provide overview of technical requirements that is driving us towards a portable stimulus standard

- Describe Graph Based Verification

- What is a graph?

- How tests modeled with graphs

- How graphs enable portable tests

- Verification reuse from IP to subsystem to full-chip

# Today's Agenda and Presenters

| • | Introductions                            | Josef Derner     | 5 mins  |

|---|------------------------------------------|------------------|---------|

| • | Do we Need it?                           | Holger Horbach   | 20 mins |

| • | Portable Stimulus for SW                 | Frederic Krampac | 25 mins |

| • | Portable and Efficient Graph-Based Tests | Staffan Berg     | 25 mins |

| • | Conclusion                               | Staffan Berg     | 5 mins  |

# Introducing Today's Presenters

- IBM

- Holger Horbach, Verification Engineer

- Breker

- Frederic Krampac, Sr Applications Engineer

- Mentor Graphics

- Staffan Berg, European Applications Engineer FV

## Portable Tests with Graph-Based Scenario Models *Hopes, Dreams and Aspirations*

#### Frederic Krampac

**Breker Verification Systems**

# Agenda

- Motivation

- Defining Verification Intent

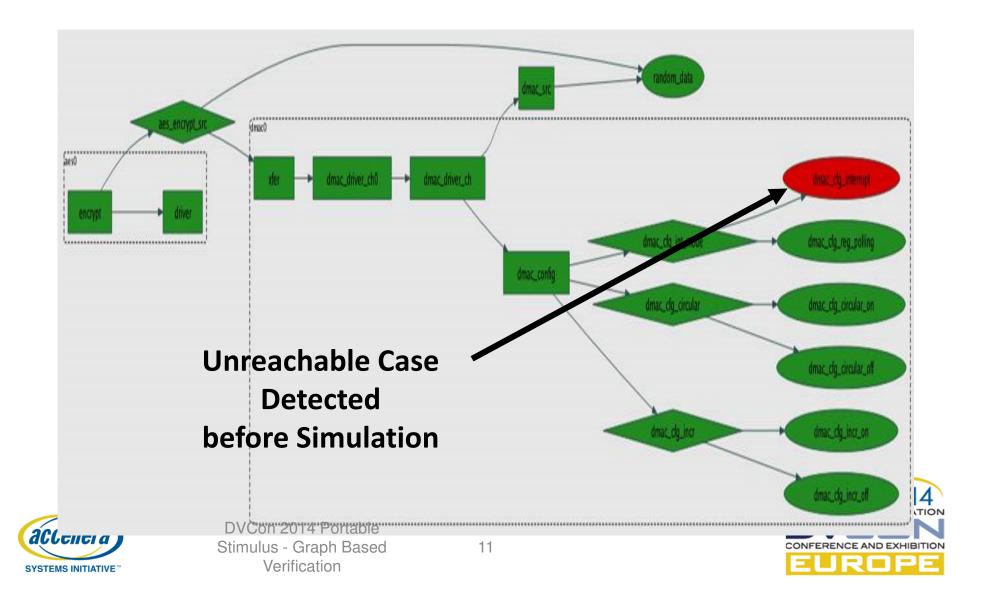

- Reachability Analysis

- Verification Intent Coverage

- Composability

- UVM transactions vs. Software Driven Tests

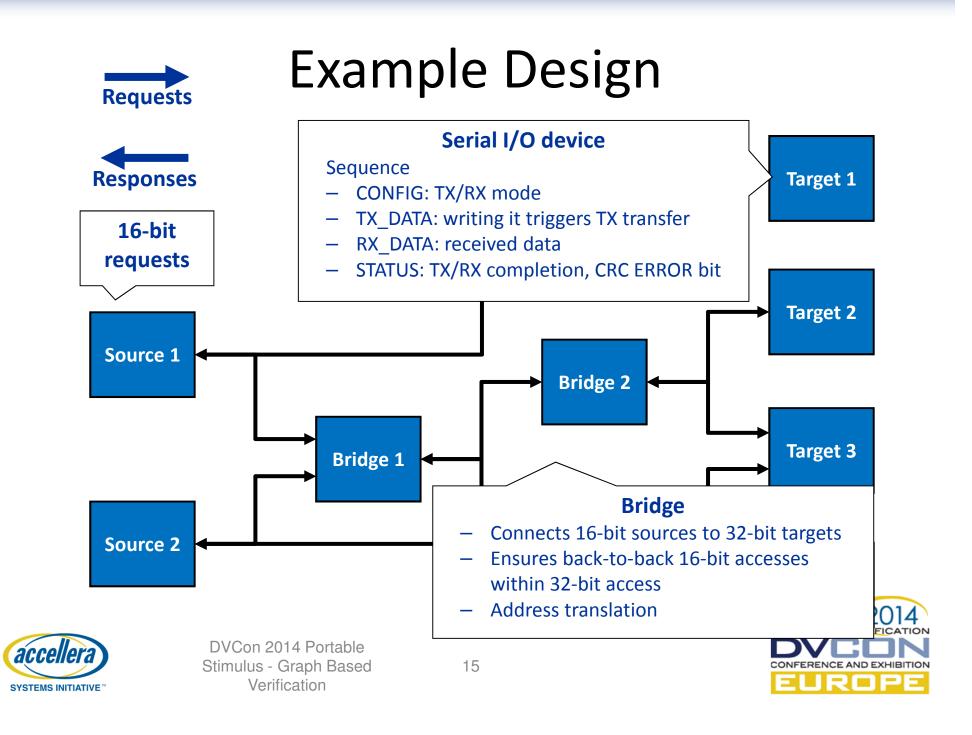

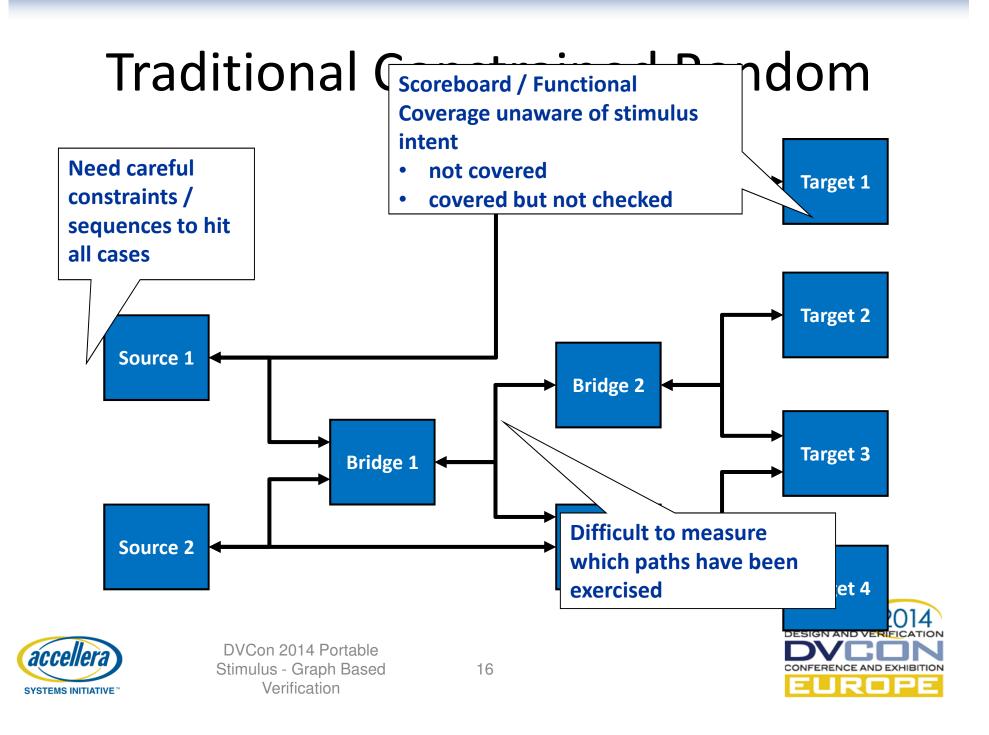

## Motivation

- Separate verification intent from testbench implementation

- Verification Intent covers both stimulus and checks

- Define verification intent once, use it at each stage of verification

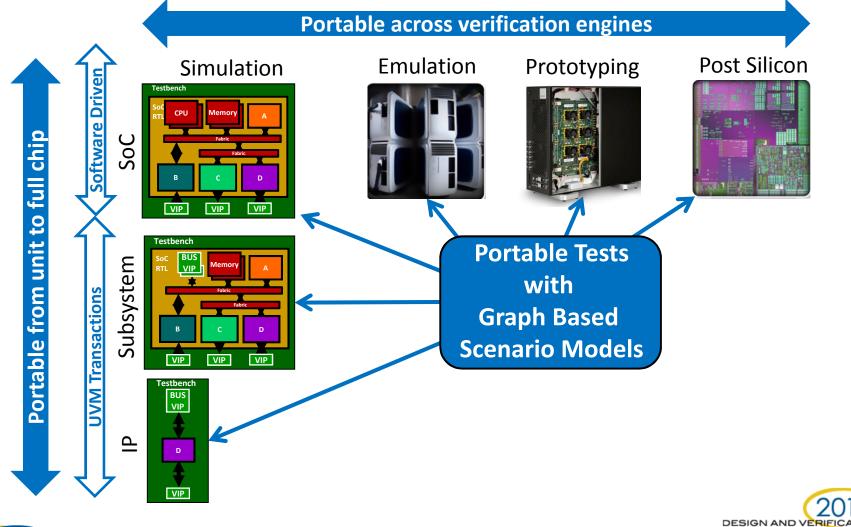

## Motivation: Portable Tests

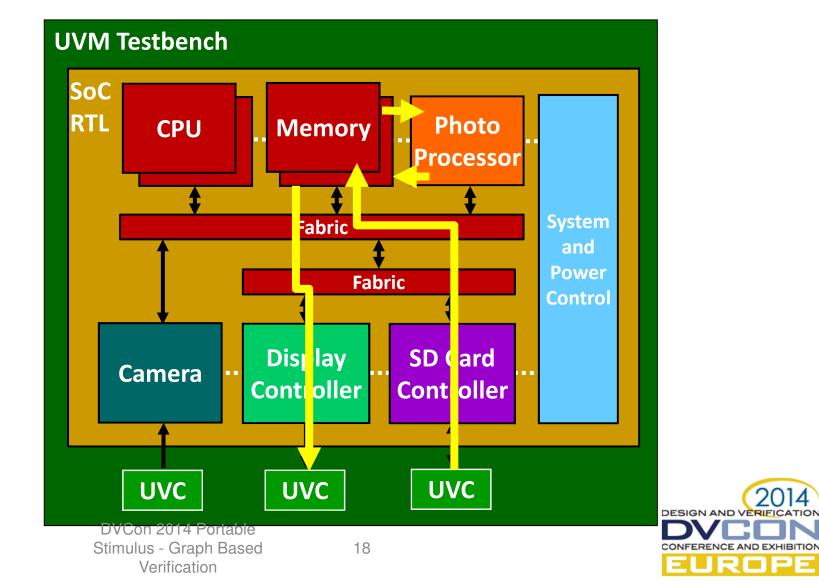

DVCon 2014 Portable Stimulus - Graph Based Verification

# **Defining Verification Intent**

- Feature capability from spec

- Check what precisely must be checked in TB

- Stimulus how to to sensitize check

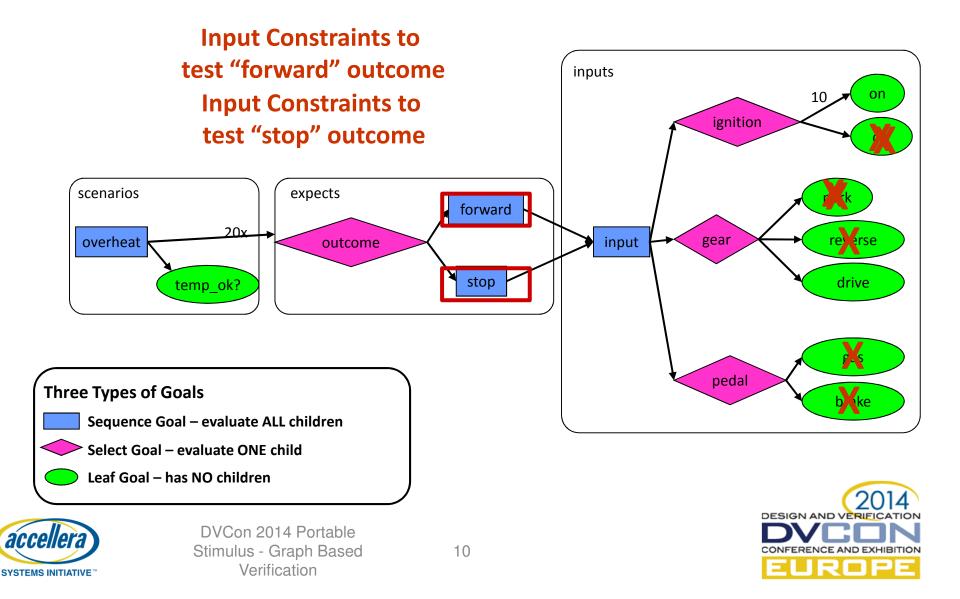

# Defining Intent: Verifying a Car

### **Reachability Analysis**

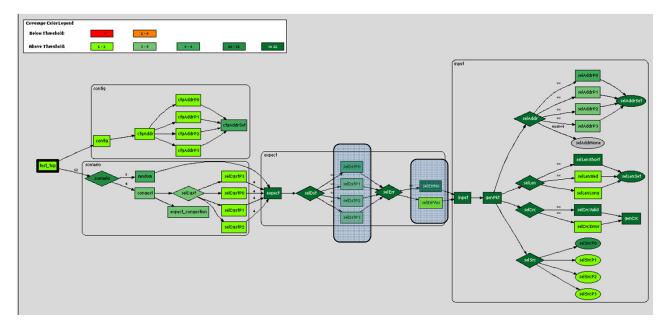

## **Verification Intent Coverage**

**Target A: Hit all input ports**

**Target B: Hit both error conditions**

Target C: Cross A x B (8 total paths)

DVCon 2014 Portable Stimulus - Graph Based Verification

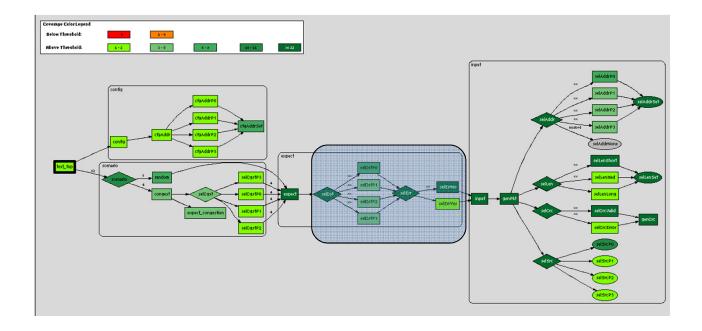

### Automatic Coverage Closure

#### **Automatically Close Coverage Targets**

Example: "cross 2 choices and walk all 8 paths"

DVCon 2014 Portable Stimulus - Graph Based Verification

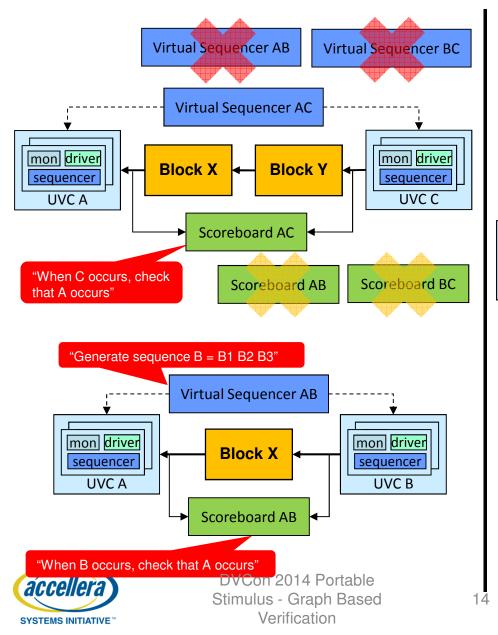

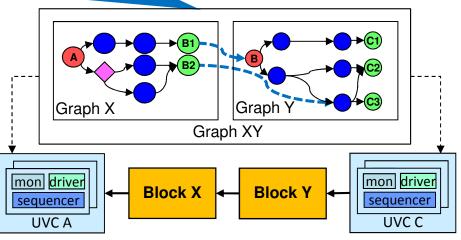

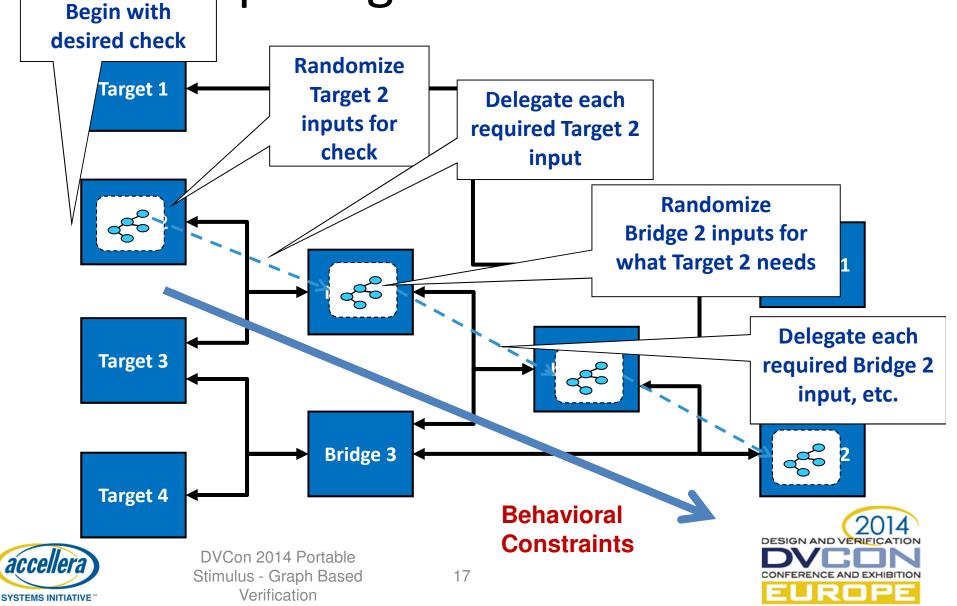

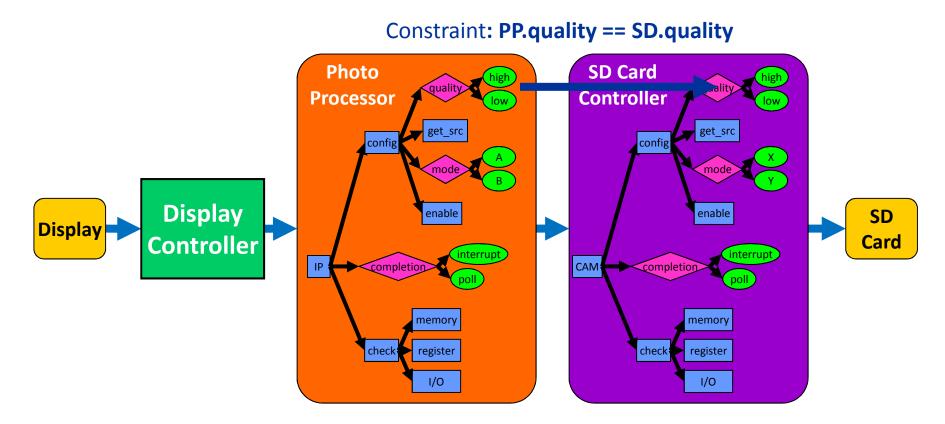

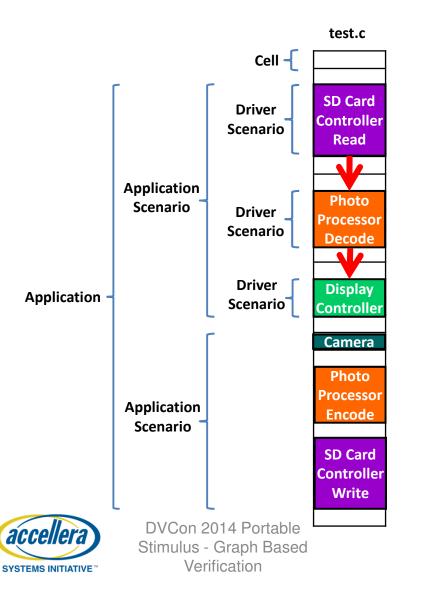

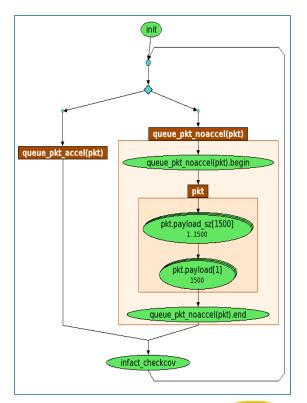

#### Composability

"To make A happen, generate sequence B1 B2; to make B1 happen, generate C1 C2 C3; to make B2 happen, generate C3"

## **Composing Scenario Models**

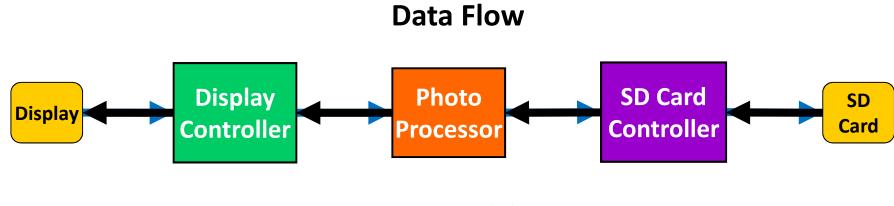

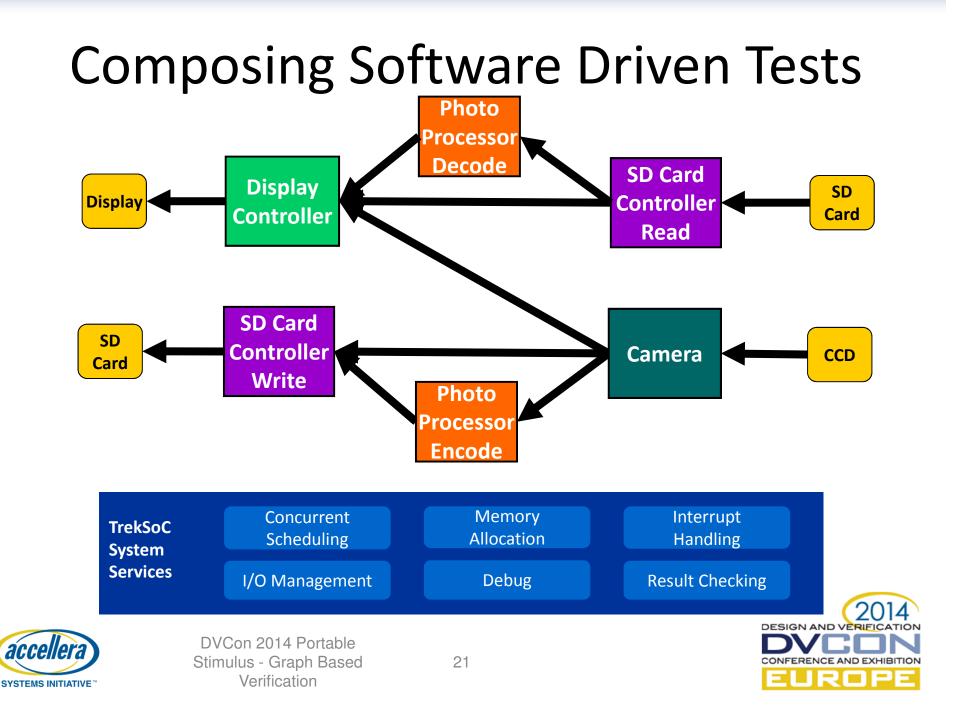

## **Composing Software Driven Tests**

# **Composing Software Driven Tests**

#### Prerequisites

DVCon 2014 Portable Stimulus - Graph Based Verification

## **Composing Software Driven Tests**

DVCon 2014 Portable Stimulus - Graph Based Verification

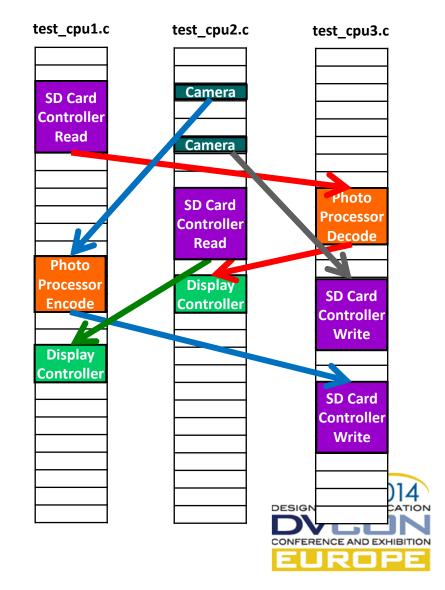

#### **Multi-Processor Scheduling**

22

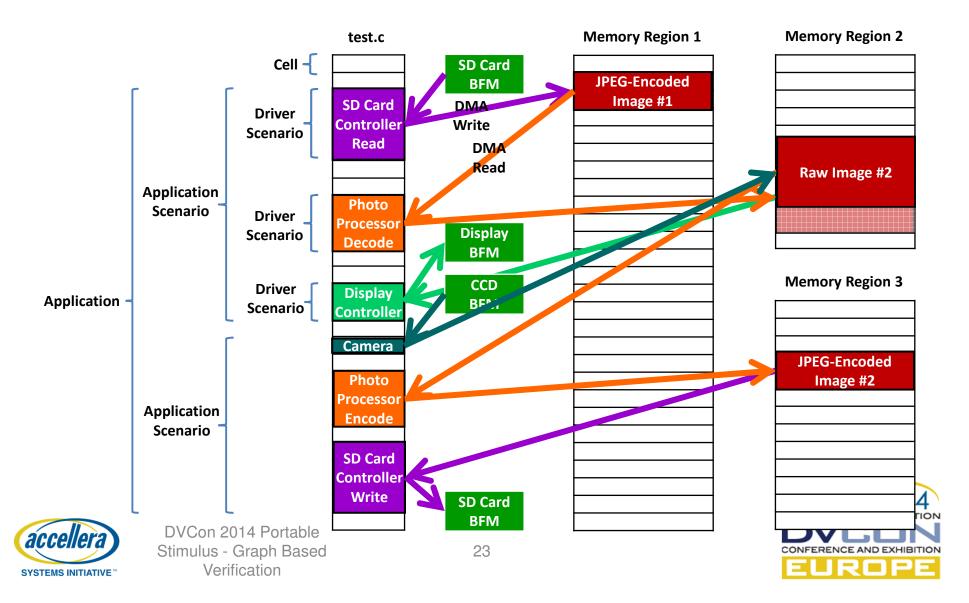

## **Memory Scheduling**

#### **UVM Transaction vs Software Driven Tests**

SYSTEMS INITIATIVE

Verification

# Summary

- Portable stimulus must be extended to checks and coverage -> portable tests

- Graph-based scenario models provide portable tests

- Efficient coverage closure of stimulus and checks

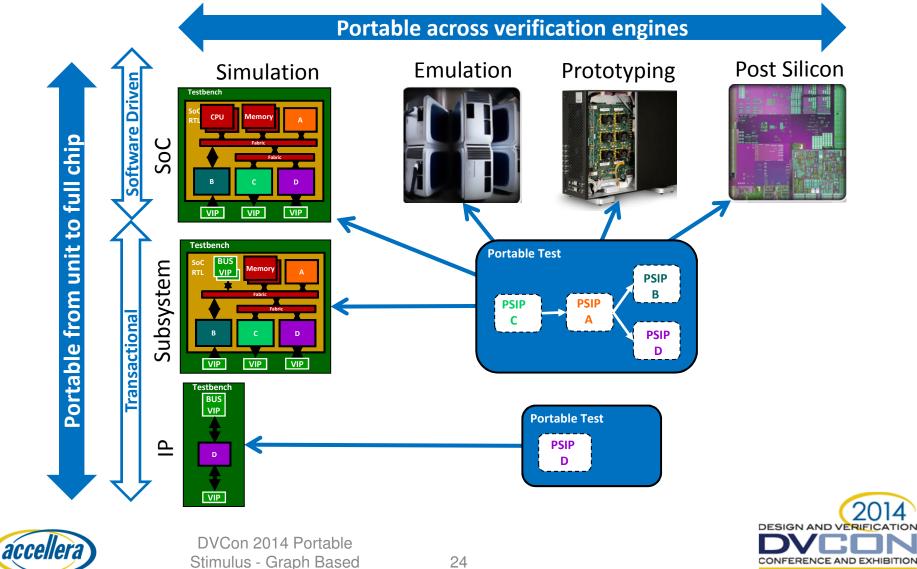

- Portability

- From unit to cluster/subsystem to full-chip

- From simulation to hardware platforms to silicon

- Both transactional and SoC software-driven tests

#### Portable and Efficient Graph-Based Tests

Staffan Berg

## Agenda

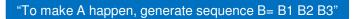

• Modeling Tests with Graphs

• Portable Stimulus with Graphs

• Graph-Based Stimulus Applications

## Agenda

Modeling Tests with Graphs

• Portable Stimulus with Graphs

• Graph-Based Stimulus Applications

### **Stimulus Specification Fundamentals**

- What is legal

- Universe of what could happen

- Captures both data and scenario

- Enables creation of 'unexpected' cases

- What to target

- Cases of specific interest

- What to verify today, during this test

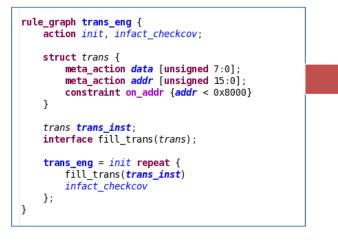

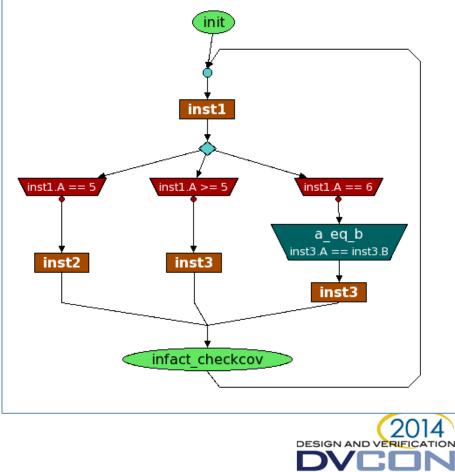

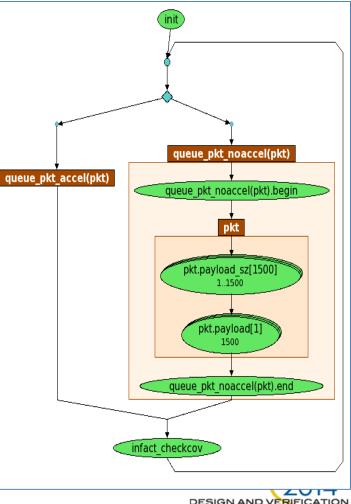

# **Graph-Based Stimulus Description**

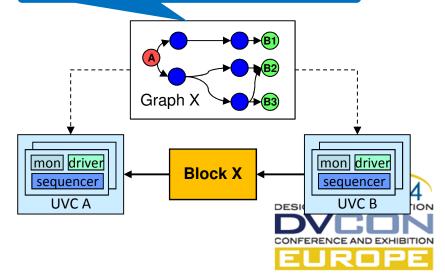

- Stimulus scenario described using <u>Rules</u>

- Captures data and control flow aspects of test scenario

- Describes legal stimulus scenario space

- Efficient description mechanism

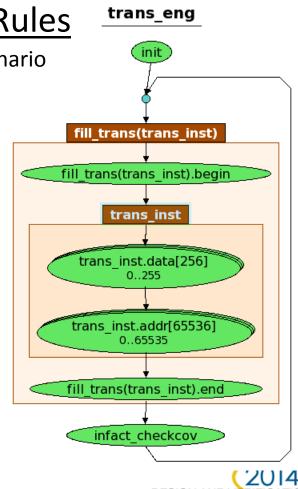

- Rules are compiled into Graphs

- Visual representation of the stimulus model

- Easy to review

DVCon 2014 Portable Stimulus - Graph Based Verification

# **Graph-Based Stimulus Description**

Captures data and data relationships

- Scalar types

- Signed and unsigned integer types

- Enumerated types

- Composite data structures

- 'struct', supports type extension

- Aggregate data types

- Single and multi-dimensional fixed-size arrays

- Variables can be input or output

- Output variables (default) send values to the environment

- Input variables bring values in from the environment

- Constraints

- Algebraic expressions, inside, if/else, foreach, etc

| <pre>struct my_struct1 {  meta_action  meta_action</pre>       | <pre>A[unsigned 3:0];</pre> |  |

|----------------------------------------------------------------|-----------------------------|--|

| }                                                              |                             |  |

| <pre>struct my_struct2 extends my_struct1 {  meta_action</pre> |                             |  |

| constraint c {                                                 |                             |  |

| C < A;                                                         |                             |  |

| }                                                              |                             |  |

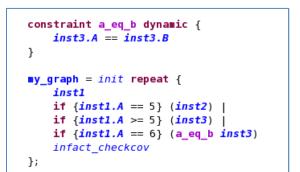

# **Graph-Based Stimulus Description**

Captures test scenario control flow

- Captures process of stimulus generation

- Sequences of operations

- Choices

- Loops

- Branch-specific constraints

- Conditional execution

- Partitions scenario structurally

CONFERENCE AND EXHIE

DVCon 2014 Portable Stimulus - Graph Based Verification

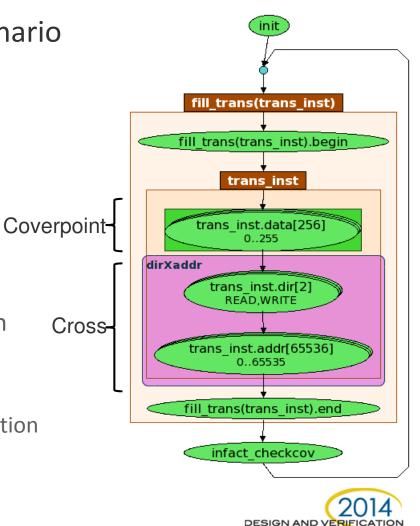

### **Test Selection and Prioritization**

#### **Coverage Strategy**

- Coverage strategy expresses test scenario goals

- Key stimulus values

- Key stimulus combinations

- Key stimulus sequences

#### Flexible

- Prioritize certain goals

- Combine random/systematic generation

#### Reactive

Adapts to changes in the DUT or the verification environment state

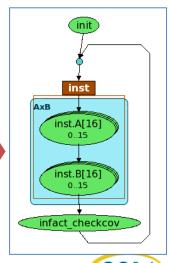

#### Test Selection and Prioritization Target value specification

- Variable domains can be divided using 'bins'

- Split a value range into N bins

- Split a value range into bins of size N

| my_struct1 | inst;                   |  |  |

|------------|-------------------------|--|--|

|            |                         |  |  |

| bin_scheme | <pre>small_vals {</pre> |  |  |

| inst.A     | [03]:1 [415]/4;         |  |  |

| inst.B     | [01]:1 [215]/8;         |  |  |

| }          |                         |  |  |

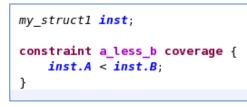

- Coverage constraints select target space with expressions

- Only active when targeting the coverage goal

- Prioritizes specific combinations

- Full legal space reachable otherwise

- Example: A x B

- Full legal space is 256 (16 \* 16)

- Constraint A < B selects 120 combinations</li>

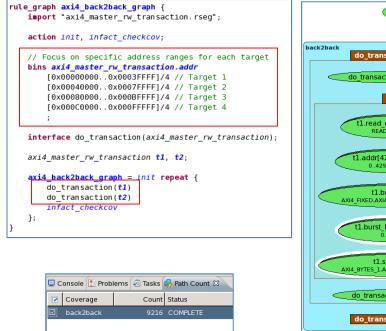

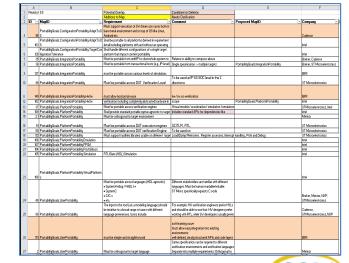

#### AXI4 Adjacency Example Efficient description at transaction level

- *Struct* captures transaction

- Key transaction fields

- Constraints

```

rule_segment {

struct axi4_master_rw_transaction {

meta_action read_or_write<axi4_rw_e>[enum READ, WRITE];

meta_action addr[unsigned 31:0];

meta action burst<axi4 burst e>[enum AXI4 FIXED, AXI4 INCR, AXI4 WRAP];

meta_action burst_length[unsigned 7:0];

meta action size<axi4 size e>[enum AXI4 BYTES 1, AXI4 BYTES 2, AXI4 BYTES 3, AXI4 BYTES 4];

// Align address for wraps

constraint addr_align_c {

if (burst == AXI4 WRAP) {

(addr % (1 << size) == 0);

}

}

// Limit burst length for wrapping bursts

constraint burst_len_c {

burst_length <= 15;</pre>

if (burst == AXI4 WRAP) {

burst length inside [1,3,7,15];

3

}

}

```

Reusable in multiple graphs

#### AXI4 Adjacency Example Efficient scenario specification and selection

- Specify target address ranges

- Four target devices

- Target four ranges in each device

- Generate transaction sequences

- R/W, address, burst sequences

- T2->T1 adjacencies are random

- Burst length, size random

- Pre-simulation size analysis

- 9216 sequences selected

- Efficient and flexible generation

#### Agenda

• Modeling Tests with Graphs

• Portable Stimulus with Graphs

• Graph-Based Stimulus Applications

## Graph Reuse and Portability

- Graphs are language and environment-independent

- Self-contained

- Describe data and sequence scenario

- Graphs mapped to specific environments

- Communicate data to/from environment

- Synchronize execution

- Can reuse graphs across environments

- Create with UVM, reuse with embedded sw

- Create with C model, reuse in UVM

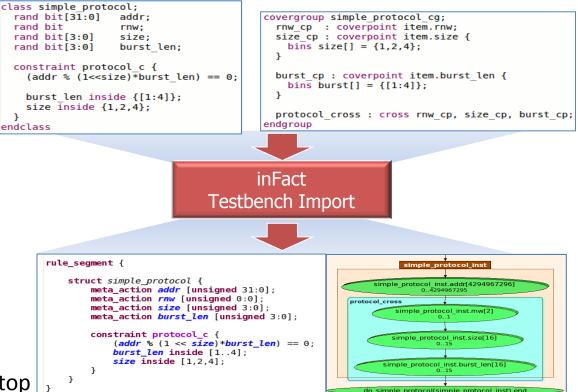

### **Graphs Enable Reuse**

Testbench Import leverages existing SystemVerilog

- Imports

- SV classes

- Fields, constraints

- Covergroups

- Creates

- Rules

- Coverage strategy

- Testbench integration

- Leverages existing SV

- Raises abstraction level

- Import transaction classes

- Build complex scenarios on top

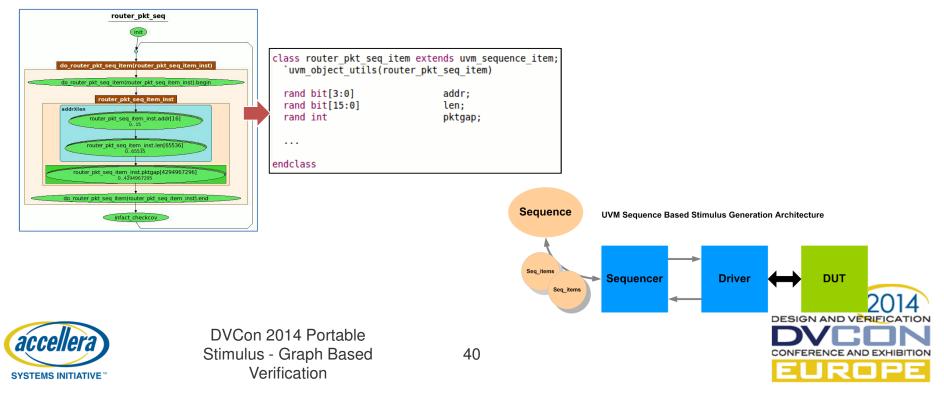

Transaction-level UVM

- Graph runs in a UVM sequence

- Graph nodes set sequence-item fields

- Each graph iteration produces a transaction

- Graph-based sequence is "just another UVM sequence"

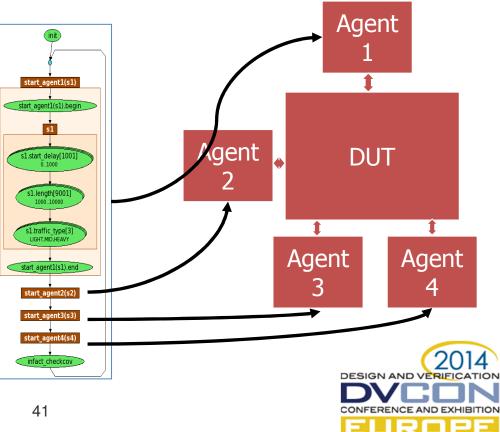

Virtual Sequence UVM

- Graph runs in a UVM virtual sequence

- Graph execution

- Selects sequence parameters

- Starts sequences

- Sub-sequences can be

- Graph-based UVM

- Random or directed

DVCon 2014 Portable Stimulus - Graph Based Verification

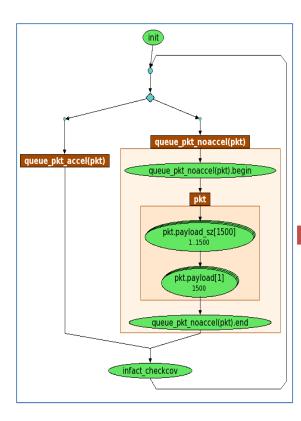

Embedded software

- Graphs call existing 'C' methods

- Select parameter values

- Sequence method calls

- Graphs can run

- Independently

- Cooperatively

- Single/multi-core

- Single/multi-thread

#### Supports

- Simulation

- Emulation

- Silicon

DVCon 2014 Portable Stimulus - Graph Based Verification

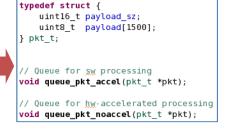

Embedded Software – Coordinated Scenarios

- Hw/Sw scenarios coordinated via a mailbox

- Mailbox infrastructure provided

#### Agenda

• Modeling Tests with Graphs

• Portable Stimulus with Graphs

• Graph-Based Stimulus Applications

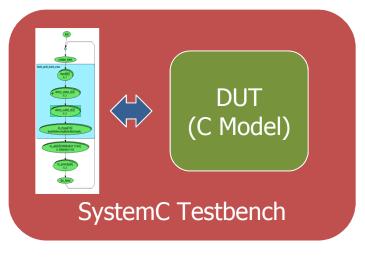

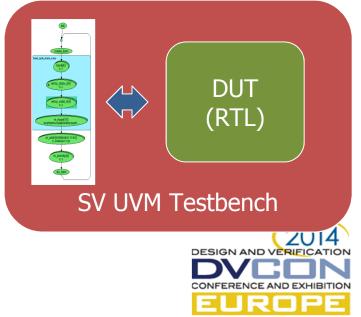

## C Model Verification

Portable stimulus across block-Level environments

- Verify C model for high-level synthesis

- SystemC simulation environment

- Re-run same tests on RTL result of synthesis

- SystemVerilog simulation environment

- UVM testbench

- Graph Benefits

- Same graph used in both environments

- Highly-productive test creation SystemC

- Systematic verification

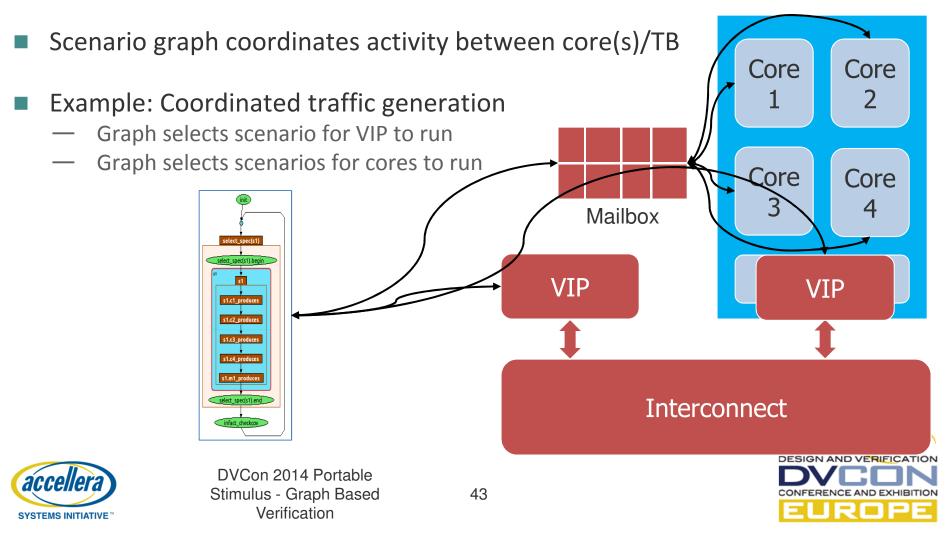

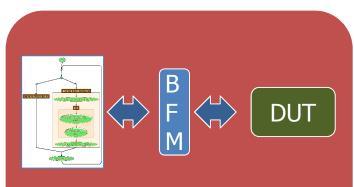

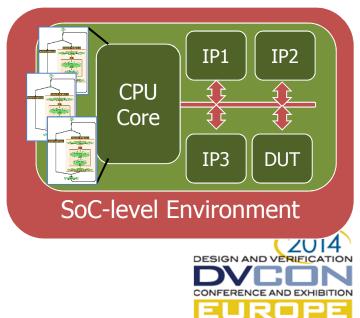

#### Test Reuse IP to SoC

Portable stimulus enables vertical reuse

- Run IP-level test in UVM environment

- Scenario driven via BFM

- Test targets single IP block

- Re-run test in SoC environment

- Scenario driven via processor core

- Run tests for multiple IP blocks in parallel

- Graph Benefits

- Same test scenario run in both environments

- More-comprehensive testing at SoC level

#### Block-level Environment

## **Graph-Based Portable Stimulus**

- High-Productivity Input Specification

- Familiar data constructs and constraints

- Formally captures control flow

- Efficient and flexible execution

- 10-100x more efficient than random

- Scalable to a simulation farm

- Portable

- Existing HVLs

- Embedded software

- Highly Automatable

- Import/export

- Analysis

#### Portable Stimulus Standardization

- Portable Stimulus Proposed Working Group

- Launched in May 2014

- PSPWG Charter

- Investigate need and requirements for a Portable Stimulus standard

- Report to the Accellera board

- Recommendation on formation of a working group

- Scope of the proposed working group

- PSPWG Status

- Weekly meetings

- Collecting and organizing requirements

- Users and vendors actively participating

- Report to Accellera board in November

## Questions

#### Finalize slide set with questions slide

# **Thank You!**

#### www.mentor.com

www.brekersystems.com