# Achieving Faster Reset Verification Closure with Intelligent Reset Domain Crossings Detection Milanpreet Kaur, Sulabh Kumar Khare Mentor, A Siemens Business

# **Introduction**

> Complex reset architecture of multiple reset sources splits SoC chip into several reset domains

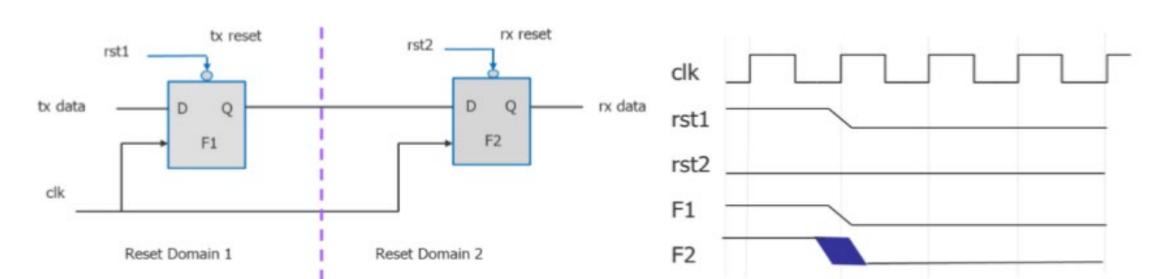

#### > Data signal metastability captured on a Reset Domain Crossing (RDC) path can cause chip to fail

## **Complexity Of Reset Domain Verification Analysis**

- Rise in functional modes leads to rise in combinational resets resulting in complex reset architecture

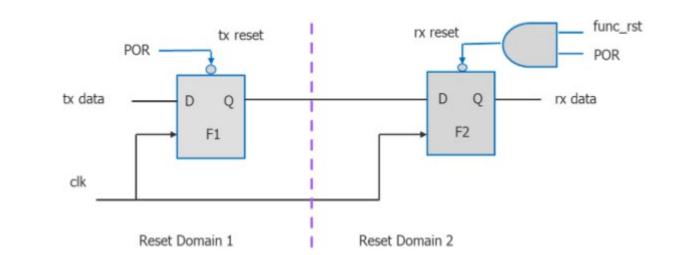

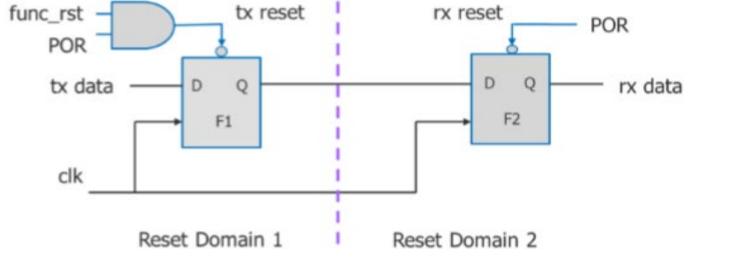

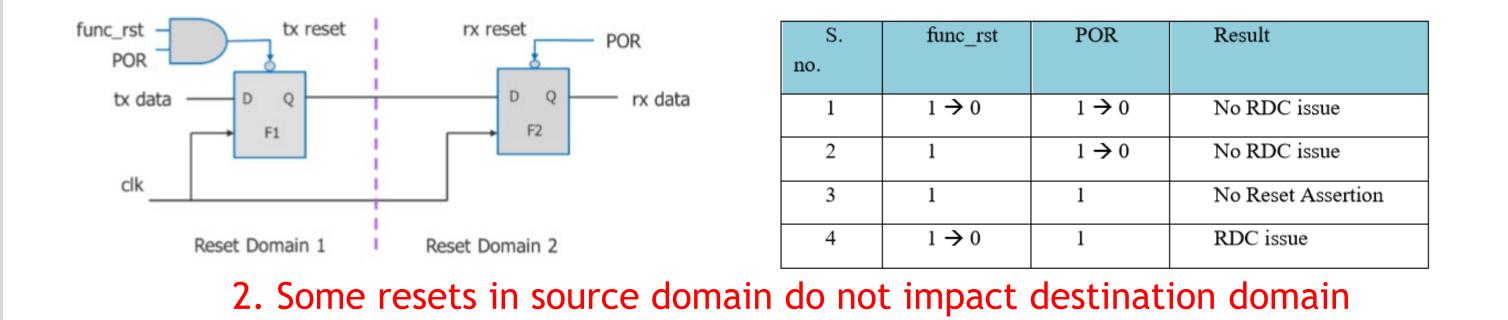

- > Two categories of crossings having multiple dependent reset assertions, reported as bugs by traditional methodologies:

| S.  | POR               | func_rst          | Result             |

|-----|-------------------|-------------------|--------------------|

| no. |                   |                   |                    |

| 1   | $1 \rightarrow 0$ | $1 \rightarrow 0$ | No RDC issue       |

| 2   | $1 \rightarrow 0$ | 1                 | No RDC issue       |

| 3   | 1                 | $1 \rightarrow 0$ | No Reset Assertion |

| 4   | 1                 | 1                 | No Reset Assertion |

>Dependency of reset domain of a sequential on concurrent assertion/de-assertion of several reset sources complicates RDC analysis

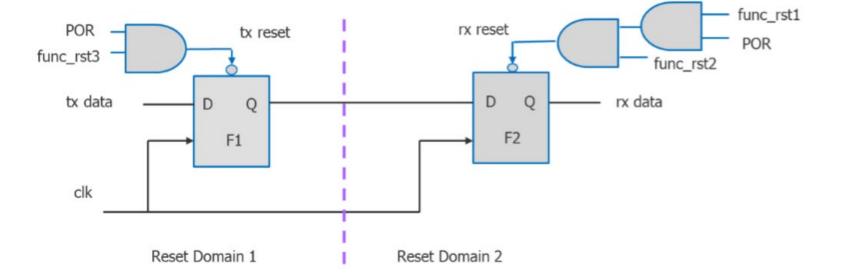

RDC verification of SoC, in addition to critical bugs, may also catch false crossings having overlapping reset domains

func\_rst - \_\_\_\_\_tx reset ! rx reset \_\_\_\_\_ pop

#### 1. All resets in source domain impact destination domain

## **Reset Detection Optimization Methodology**

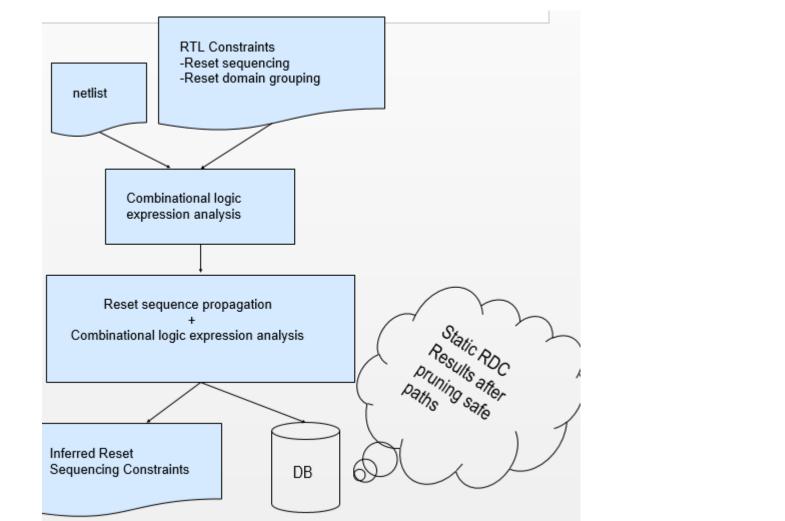

$\succ$  The proposed method utilizes a combination of structural reset analysis, expression analysis, and functional analysis to prune noisy and inefficient RDC paths in the design during static verification.

# **Analysis of Reset detection Optimization Methodology**

Quality of results and minimal noise

- Proposed methodology always resulted in reduction in noise by at least one fourth

- > Ease of debug

- Filtered crossings and ordered crossings available for user separately to debug and verify

- Debug aids available for reset structure analysis and tracing inferred reset sequencing in the form of report file

> Accuracy

• Multi-level complex reset structures handled accurately

- Stage 1: Comprehensive expression analysis of the resets at source and destination to identify and prune safe candidates

- Stage 2: Propagation of user defined reset sequencing across combinational resets in addition to reset expression analysis to identify and prune safe candidates out of second category crossings

- Reduction in verification time

- False crossings pruned in the initial stage of analysis giving cleaner, genuine RDC paths for designer to verify.

# **CASE STUDY**

- > The proposed methodology was benchmarked on a highly complex real SoC with more than 1.8 million registers, and 5 RAMs

- > Out of Identified 287 reset domains including asynchronous and synchronous resets, 90k RDC crossings detected during RDC analysis.

- > Comparison of RDC results on the SoC with and without proposed methodology, with reset grouping and reset ordering applicable:

| Reset Domain Crossings                                                 | Number of crossings |

|------------------------------------------------------------------------|---------------------|

| RDCs having source and destination registers in different asynchronous | 34562               |

| reset domains <i>without</i> proposed methodology                      |                     |

| RDCs having source and destination registers in different asynchronous | 22811               |

| reset domains <i>with</i> proposed methodology                         |                     |

| Ordered RDC paths (based on sequencing information) without proposed   | 23126               |

| methodology                                                            |                     |

| Ordered RDC paths (based on sequencing information) with proposed      | 27650               |

| methodology                                                            |                     |

# **CONCLUSIONS**

- Proposed automatic technique improves quality of results for static RDC analysis, and reduces closure time required for real RDC issues

- Improved tool performance

- > Methodology ensures no critical path is missed and false crossings are pruned

- Advanced techniques utilize reset ordering information as well to simplify the reset architecture and enhances the tool capabilities

## **REFERENCES**

[1] Yossi Mirsky, "Comprehensive and Automated Static Tool Based Strategies for the Detection and Resolution of Reset Domain Crossings", DVCON

> Around ~34% crossings pruned as false paths, ~20% increase in ordered crossings.

[2] Chris Kwok, Priya Viswanathan, Ping Yeung, "Addressing the Challenges of Reset Verification in SoC Designs", DVCon US, 2015

[3] Akanksha Gupta, Ashish Hari, Anwesha Choudhary, "Systematic Methodology to Solve Reset Challenges in Automotive SoCs", DVCON Europe 2019

#### Add acknowledgments, organization involved, logo's contact information here

## © Accellera Systems Initiative