# ACE'ing the Verification of SOCs with Cache Coherent Heterogeneous Multiprocessors Targeted for Optimized Power Consumption

Authors Mehul Kumar | Broadcom Corp. Shawn Honess | Synopsys Inc Amir Nilipour | Synopsys Inc. Tushar Mattu | Synopsys Inc.

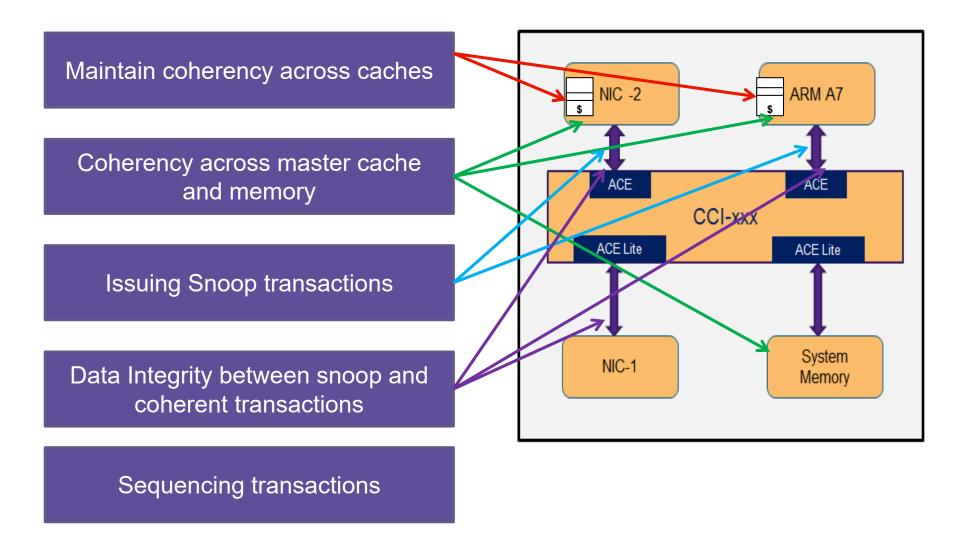

### **System Coherency Verification**

© Synopsys 2012 2

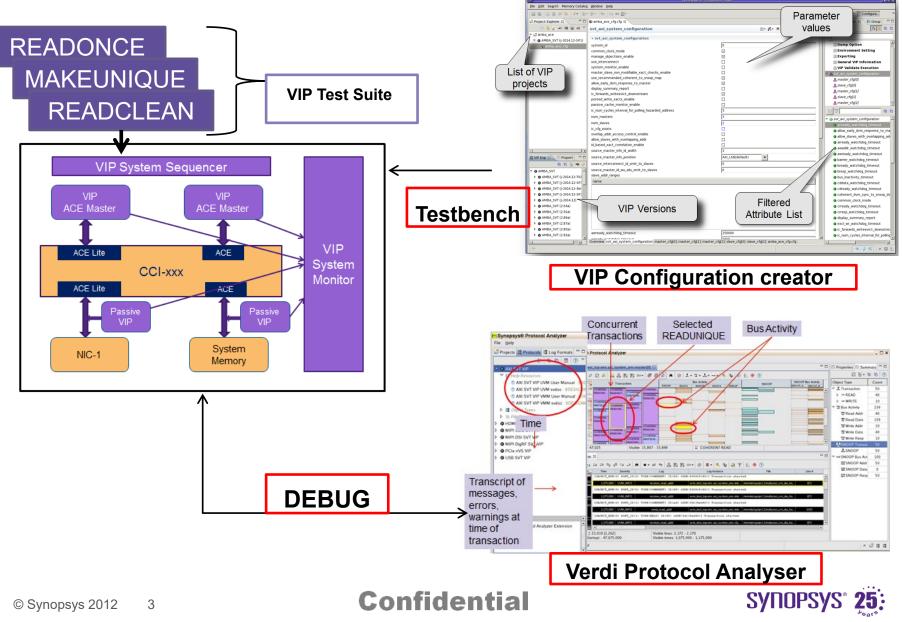

### **Verification Environment**

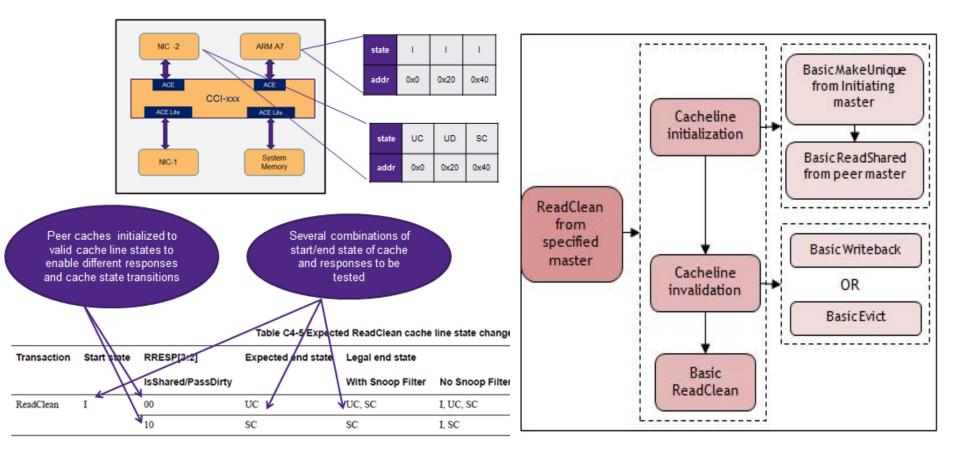

### **Coherent Stimulus**

#### **Stimulus Permutations**

#### Sample Sequence Flow

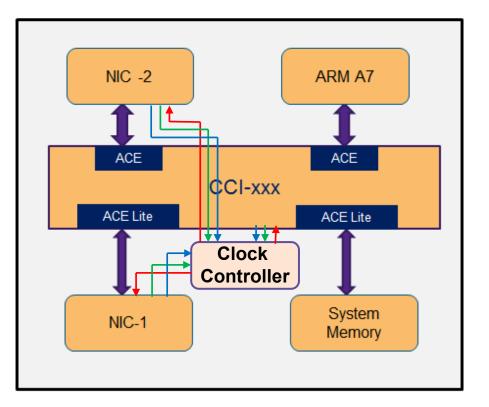

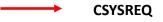

# Low Power (LP) Interface : C-Channel

Low Power Interface used to reduce power consumption of a system

LP signaling and handshake between peripherals & clock controller

Dynamically disable/enable clocks to peripherals and system components

Peripheral can request its clock to be enabled or disabled

CSYSACK

## **VIP for Low Power(LP) Interface**

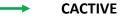

## Low Power Entry & Exit Scoreboarding

UVM ERROR @ 118555.1ns: [scoreboard] csysack cd\_clk\_sysm not changing as expected

Clock not turning off after required N clock cycle expiry: UVM ERROR @ 119473.2ns: [scoreboard] cactive\_cd\_clk\_sysm csysreq\_cd\_clk\_sysm not changing as expected after Timer timeout Confidential SYNOPSYS<sup>®</sup> 25: 7

## Conclusion

- Complex dynamic clock gating scheme was validated at backplane level.

- The design issues are caught early in the RTL design cycle using the methodology proposed.

- VIP Verification features enabled team to spent more time in writing design specific tests, checks and coverage.

- The verification performed with combination of Synopsys

VIP system checking and end-end Scoreboard lowered risk

© Synopsys 2012 8