# Accelerating CDC Verification Closure on Gate-Level Designs

Anwesha Choudhury, Mentor Graphics Ashish Hari, Mentor Graphics

# **Agenda**

- Why CDC Verification on Gate-Level Designs

- Traditional Methodology and Challenges

- Proposed Gate-CDC Verification Methodology

- Experiments & Results

# **Clock Domain Crossing(CDC)**

- What is CDC

- Signal originating in one clock domain sampled in another asynchronous clock domain

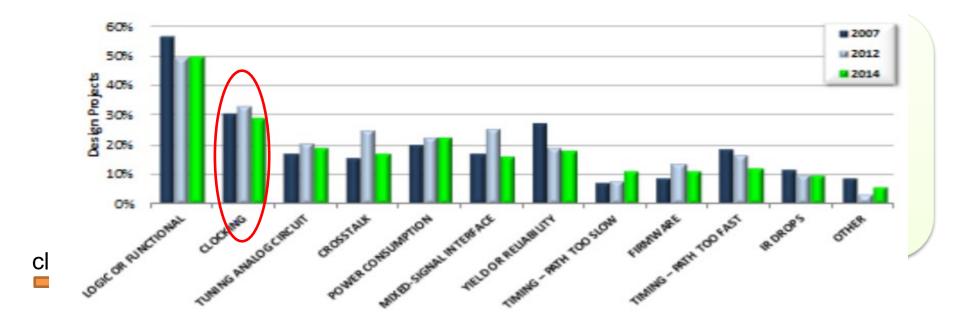

- CDC issues are #2 reason for silicon respins

### **Need for Gate-Level CDC Verification**

Traditionally CDC verification done on RTL

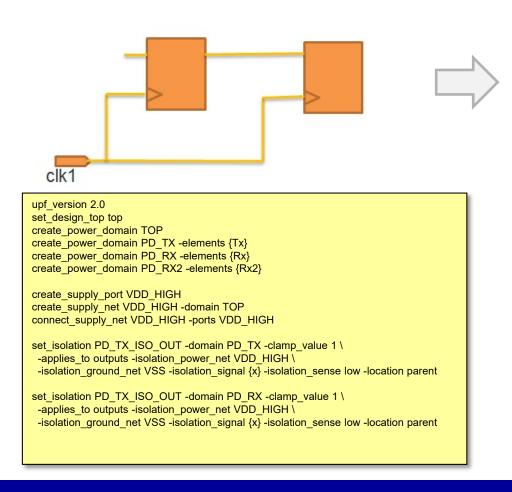

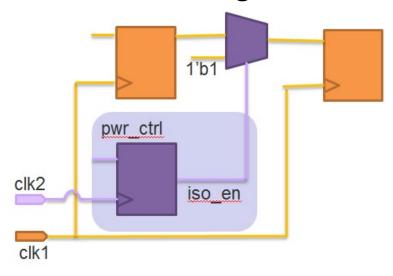

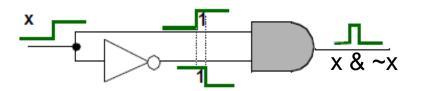

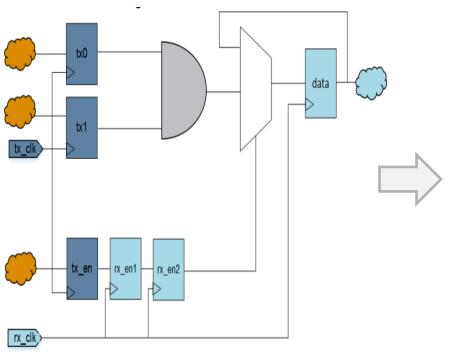

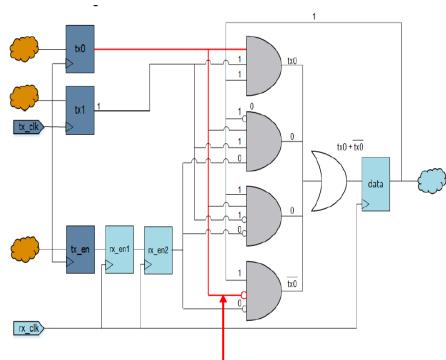

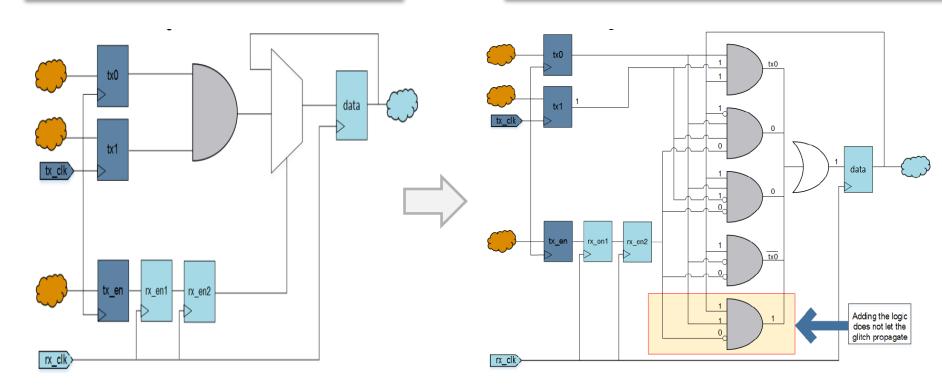

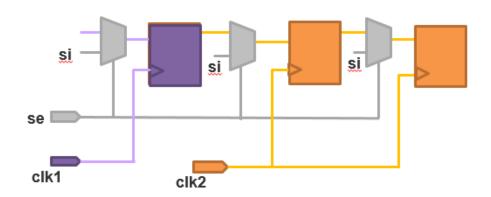

### **Gate-CDC Example**

CDC path introduced due to insertion of logic

Combination logic that can reduce to :

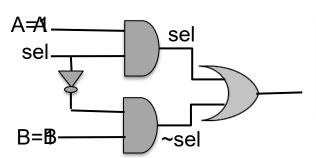

RTL Logic : Mux based synchronizer

Mux implementation after synthesis

Glitch-prone:

sel | ~sel when

A = 1 and B =1

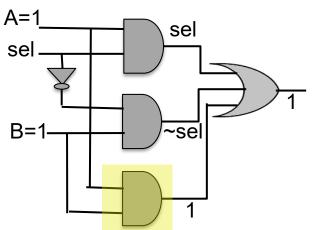

Glitch blocked:

Output = 1 when

A = 1 and B = 1

RTL Logic: Mux based synchronizer

Combo-logic implementation after synthesis

For given constants, logic reduces to (tx0|~tx0) which causes glitch

RTL Logic: Mux based synchronizer

Combo-logic implementation after synthesis

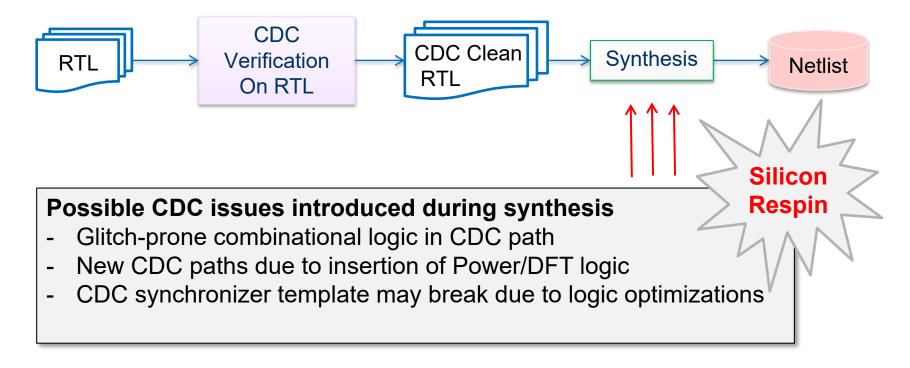

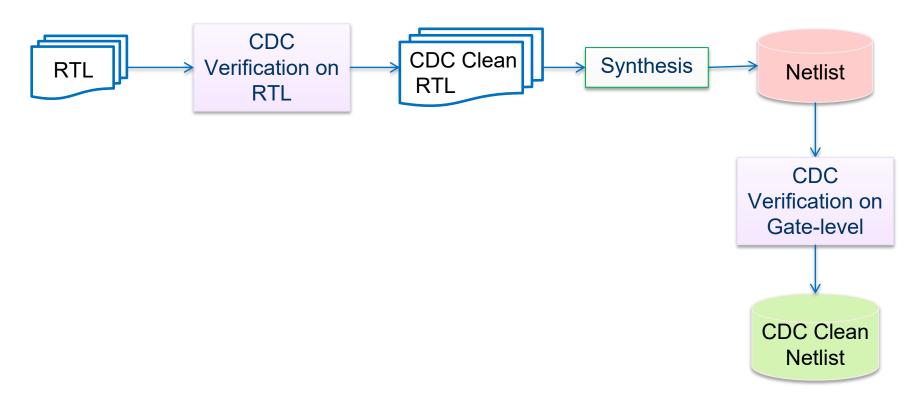

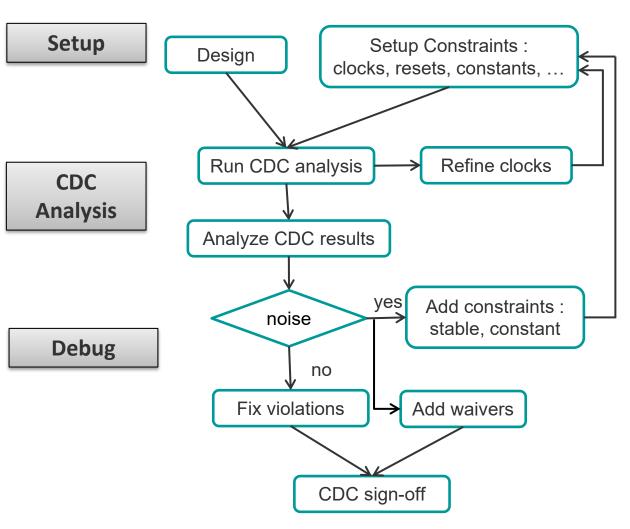

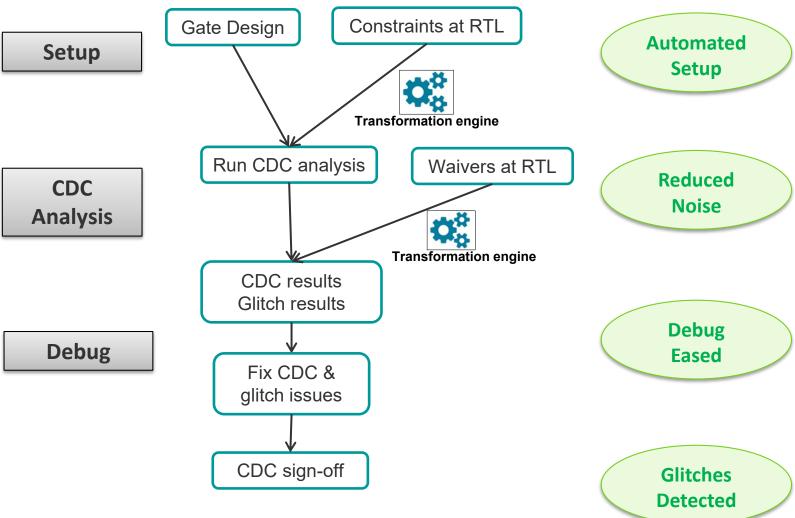

### **CDC Verification Flow**

CDC verification is necessary on gate-level netlist

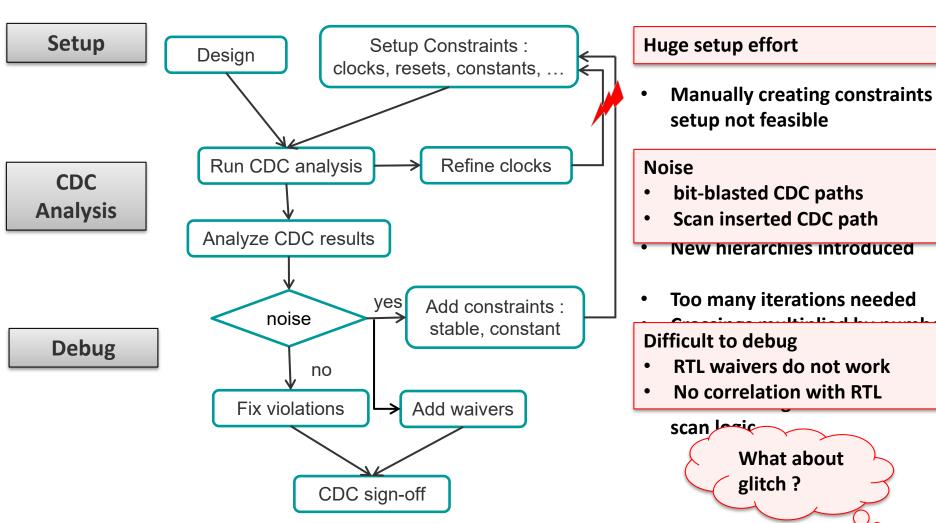

### **Traditional Methodology**

# **Traditional Methodology**

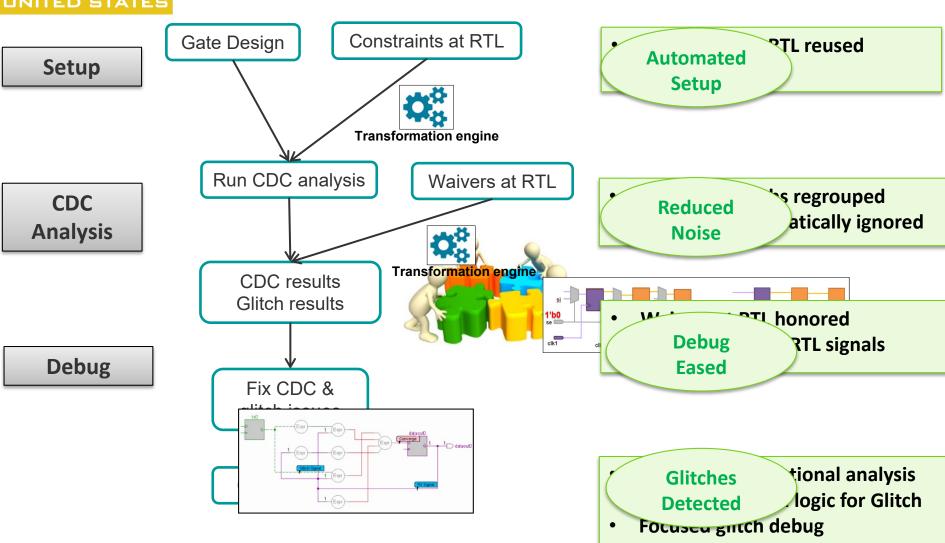

### **Proposed Methodology**

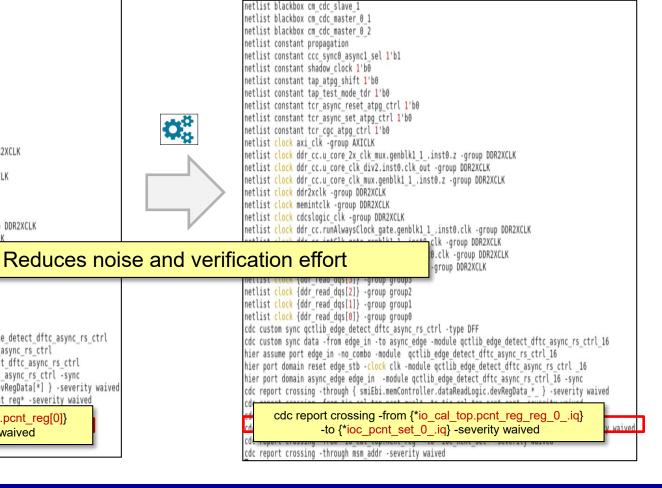

### **RTL Constraints Reuse**

#### **RTL Constraints**

```

netlist blackbox cm cdc master

netlist blackbox c

netlist constant propagation

netlist constant ccc sync0 async1 sel 1'b1

netlist constant shadow clock 1'b0

netlist constant tap_atpg_shift 1'b0

netlist constant tap test mode tdr 1'b0

netlist constant tcr async reset atpg ctrl 1'b0

netlist constant tcr_async_set_atpg_ctrl 1'b0

netlist constant tcr cgc atpg ctrl 1'b0

netlist constant msm addr range 1'b1

netlist clock axi clk -group AXICLK

netlist clock ddr cc.u core 2x clk mux.genblk1[1].inst0.z -group DDR2XCLK

netlist clock ddr cc.u core clk div2.inst0.clk out -group DDR2XCLK

netlist clock ddr cc.u core clk mux.genblk1[1].inst0.z -group DDR2XCLK

netlist clock ddr2xclk -group DDR2XCLK

netlist clock memintclk -group DDR2XCLK

netlist clock cdcslogic clk -group DDR2XCLK

netlist clock ddr cc.runAlwaysClock gate.genblk1[1].inst0.clk -group DDR2XCLK

netlist clock ddr cc.intClk gate.genblk1[1].inst0.clk -group DDR2XCLK

netlist clock ddr_cc.ddr2xClk_gate.genblk1[1].inst0.clk -group DDR2XCLK

netlist clock ddr cc.u clk src.genblk1[1].inst0.z -group DDR2XCLK

netlist clock {ddr_read_dqs[3]} -group group3

netlist clock {ddr read dqs[2]} -group group2

netlist clock {ddr read dgs[1]} -group group1

cdc custom sync qctlib edge detect async rs ctrl

cdc custom sv

cdc custom sync data -from edge in -to async edge -module qctlib edge detect dftc async rs ctr

hier assume port edge in -no combo -module qctlib edge detect dftc async rs ctrl

hier port domain reset edge stb -clock clk -module qctlib_edge_detect_dftc_async_rs_ctrl

hier port domain async edge edge in -module qctlib edge detect dftc async rs ctrl -sync

cdc report crossing -through { smiEbi.memController.dataReadLogic.devRegData[*] } -severity waived

cdc report crossing -from *io cal top.pcnt qual* -to *io cal top.pcnt reg* -severity waived

cdc report crossing -from *io_cal_top.ncnt_qual* -to *io_cal_top.ncnt_reg* -severity waived

cdc report crossing -from {*io_cal_top.pcnt_reg[0]} -to {*ioc_pcnt_set[0]} -severity waived

cdc report crossing -from *io cal top.ncnt reg* -to *ioc ncnt set* -severity waived

cdc report crossing -through msm addr -severity waived

```

#### **Traditional Methodology:**

- Constraints not applied due to name and topology changes post synthesis

- No black-boxing

- Redundant processing inside the module

- Custom synchronizer not detected

- False missing synchronizer Noise

### **RTL Constraints Reuse**

#### **RTL Constraints**

```

etlist blackbox cm

netlist blackbox cm cdc master

etlist blackbox cr

netlist constant propagation

netlist constant ccc sync0 async1 sel 1'b1

netlist constant shadow clock 1'b0

netlist constant tap_atpg_shift 1'b0

netlist constant tap test mode tdr 1'b0

netlist constant tcr async reset atpg ctrl 1'b0

netlist constant tcr async set atpg ctrl 1'b0

netlist constant tcr_cgc_atpg_ctrl 1'b0

netlist constant msm_addr_range 1'b1

netlist clock axi_clk -group AXICLK

netlist clock ddr cc.u core 2x clk mux.genblk1[1].inst0.z -group DDR2XCLK

netlist clock ddr cc.u core clk div2.inst0.clk out -group DDR2XCLK

netlist clock ddr cc.u core clk mux.genblk1[1].inst0.z -group DDR2XCLK

netlist clock ddr2xclk -group DDR2XCLK

netlist clock memintclk -group DDR2XCLK

netlist clock cdcslogic_clk -group DDR2XCLK

netlist clock ddr cc.runAlwaysClock gate.genblk1[1].inst0.clk -group DDR2XCLK

netlist clock ddr cc.intClk gate.genblk1[1].inst0.clk -group DDR2XCLK

netlist clock ddr_cc.ddr2xClk gate.genblk1[1].inst0.clk -group DDR2XCLK

netlist clock ddr cc.u clk src.genblk1[1].inst0.z -group DDR2XCLK

netlist clock {ddr read dqs[3]} -group group3

netlist clock {ddr read dqs[2]} -group group2

netlist clock {ddr_read_dqs[1]} -group group1

cdc custom sync actlib edge detect async rs ctrl

cdc custom sync data -from edge in -to async edge -module qctlib edge detect dftc async rs ctr

hier assume port edge in -no combo -module gctlib edge detect dftc async rs ctrl

hier port domain reset edge stb -clock clk -module gctlib edge detect dftc async rs ctrl

hier port domain async edge edge in -module gctlib edge detect dftc async rs ctrl -sync

cdc report crossing -through { smiEbi.memController.dataReadLogic.devRegData[*] } -severity waived

cdc report crossing -from *io cal top.pcnt qual* -to *io cal top.pcnt reg* -severity waived

cdc report crossing -from *io_cal_top.ncnt_qual* -to *io_cal_top.ncnt_reg* -severity waived

cdc report crossing -from {*io cal top.pcnt reg[0]} -to {*ioc pcnt set[0]} -severity waived

cdc report crossing -from *io cal top.ncnt reg* -to *ioc ncnt set* -severity waived

cdc report crossing -through msm addr -severity waived

```

#### **Auto-generated gate constraints**

```

netilist blackbox cm cdq master 0 2

netlist blackbox cm cdd master 0 1

netlist constant ccc_sync0_async1_sel 1'b1

netlist constant shadow clock 1'b0

netlist constant tap atpg shift 1'b0

netlist constant tap test mode tdr 1'b0

netlist constant tor async reset atpg ctrl 1'b0

netlist constant tcr async set atpg ctrl 1'b0

netlist constant tor cgc atpg ctrl 1'b0

netlist clock axi_clk -group AXICLK

netlist clock ddr cc.u core 2x clk mux.genblk1 1 .inst0.z -group DDR2XCLK

netlist clock ddr cc.u core clk div2.inst0.clk out -group DDR2XCLK

netlist clock ddr_cc.u_core_clk_mux.genblk1_1 .inst0.z -group DDR2XCLK

netlist clock ddr2xclk -group DDR2XCLK

netlist clock memintclk -group DDR2XCLK

netlist clock cdcslogic clk -group DDR2XCLK

netlist clock ddr_cc.runAlwaysClock_gate.genblk1_1_.inst0.clk -group DDR2XCLK

netlist clock ddr cc.intClk gate.genblk1 1 .inst0.clk -group DDR2XCLK

netlist clock ddr_cc.ddr2xClk_gate.genblk1_1_.inst0.clk -group DDR2XCLK

netlist clock ddr_cc.u_clk src.genblk1_1 .inst0.z -group DDR2XCLK

netlist clock {ddr read dqs[3]} -group group3

netlist clock {ddr read dgs[2]} -group group2

netlist clock {ddr read dqs[1]} -group group1

cdc custom sync qctlib edge detect async rs ctrl 16

```

hier assume port edge in -no combo -module qctlib edge detect dftc async rs ctrl 16

cdc report crossing -from \*io cal top.ncnt reg\* -to \*ioc ncnt set\* -severity waived

cdc report crossing -through msm addr -severity waived

hier port domain reset edge stb -clock clk -module gctlib edge detect dftc async rs ctrl 16

hier port domain async edge edge in -module gctlib edge detect dftc async rs ctrl 16 -sync

cdc report crossing -from \*io\_cal\_top.pcnt\_qual\* -to \*io\_cal\_top.pcnt\_reg\* -severity waived

cdc report crossing -from \*io\_cal\_top.ncnt\_qual\* -to \*io\_cal\_top.ncnt\_reg\* -severity waived

cdc report crossing -through { smiEbi.memController.dataReadLogic.devRegData \* } -severity waived

cdc report crossing -from {\*io cal top.pcnt reg reg θ .iq} -to {\*ioc pcnt set reg θ .iq} -severity waived

### **RTL Waivers Reuse**

#### **RTL Constraints**

```

netlist blackbox cm cdc slave

netlist blackbox cm cdc master

netlist constant propagation

netlist constant ccc sync0 async1 sel 1'b1

netlist constant shadow clock 1'b0

netlist constant tap_atpg_shift 1'b0

netlist constant tap test mode tdr 1'b0

netlist constant tcr async reset atpg ctrl 1'b0

netlist constant tcr_async_set_atpg_ctrl 1'b0

netlist constant tcr cgc atpg ctrl 1'b0

netlist constant msm addr range 1'b1

netlist clock axi_clk -group AXICLK

netlist clock ddr cc.u core 2x clk mux.genblk1[1].inst0.z -group DDR2XCLK

netlist clock ddr cc.u core clk div2.inst0.clk out -group DDR2XCLK

netlist clock ddr cc.u core clk mux.genblk1[1].inst0.z -group DDR2XCLK

netlist clock ddr2xclk -group DDR2XCLK

netlist clock memintclk -group DDR2XCLK

netlist clock cdcslogic_clk -group DDR2XCLK

netlist clock ddr cc.runAlwaysClock gate.genblk1[1].inst0.clk -group DDR2XCLK

netlist clock ddr cc.intClk gate.genblk1[1].inst@.clk -group DDR2XCLK

netlist clock ddr_cc.ddr2xClk_gate.genblk1[1].in

netlist clock ddr cc.u clk src.genblk1[1].inst0.

netlist clock {ddr_read_dqs[3]} -group group3

netlist clock {ddr read dqs[2]} -group group2

netlist clock {ddr_read_dqs[1]} -group group1

netlist clock {ddr read dqs[0]} -group group0

cdc custom sync gctlib edge detect dftc async rs ctrl -type DFF

cdc custom sync data -from edge_in -to async_edge -module qctlib_edge_detect_dftc_async_rs_ctrl

hier assume port edge in -no combo -module qctlib edge detect dftc async rs ctrl

hier port domain reset edge stb -clock clk -module gctlib edge detect dftc async rs ctrl

hier port domain async edge edge in -module qctlib edge detect dftc async rs ctrl -sync

cdc report crossing -through { smiEbi.memController.dataReadLogic.devRegData[*] } -severity waived

cdc report crossing -from *io cal top.pcnt qual* -to *io cal top.pcnt reg* -severity waived

cdc report

cdc report crossing -from {*io cal top.pcnt reg[0]}

cdc report

-to {*ioc pcnt set[0]} -severity waived

cdc report

cdc report crossing -through msm addr -severity waived

```

#### **Auto-generated gate constraints**

## **Auto Infer Test Mode Settings**

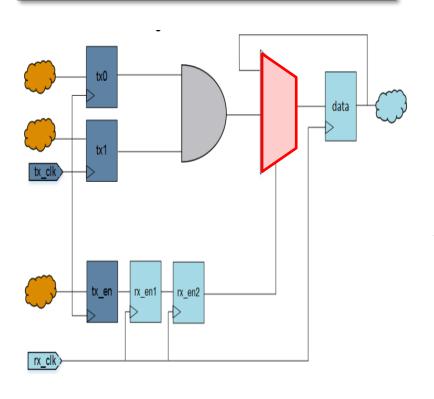

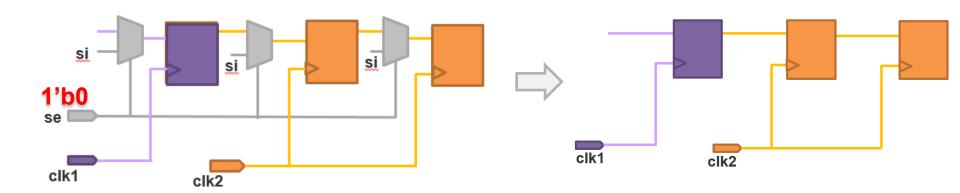

Scan mux inserted CDC path

- Traditional methodology

- Synchronizer not detected

### **Auto Infer Test Mode Settings**

Scan mux inserted CDC path

- Proposed methodology

- Structural analysis detects scan enable settings

- Two dff synchronizer detected

sync

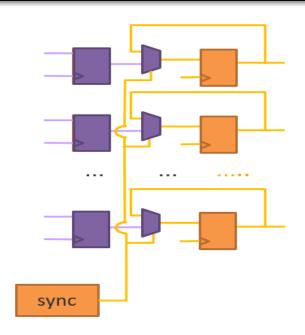

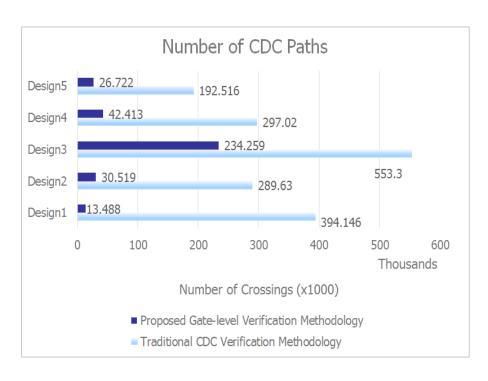

### **Regroup Bit-blasted Crossings**

RTL: 16-bit data path

d[15:0] q[15:0]

**Gate-level: 16 separate 1-bit paths**

- Traditional methodology

- 16 separate 1-bit paths reported

- r\_reg\_0.iq -> q\_reg\_0.iq, r\_reg\_1.iq -> q\_reg\_1.iq, ...

Crossing count multiplied by number of vector signal bits

sync

d[15:0]

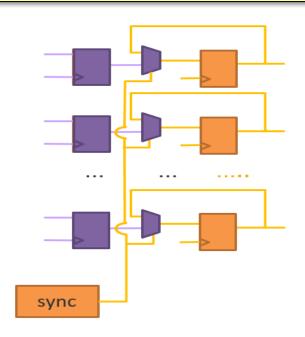

### **Regroup Bit-blasted Crossings**

RTL: 16-bit data path

q[15:0]

**Gate-level: 16 separate 1-bit paths**

- Proposed methodology

- 16 separate paths regrouped to 1 CDC path

- r\_reg\_[15:0].iq -> q\_reg\_[15:0].iq

Crossing count same as RTL for vector signals

# **Proposed Methodology**

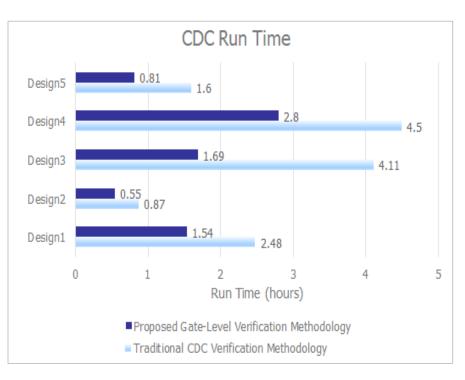

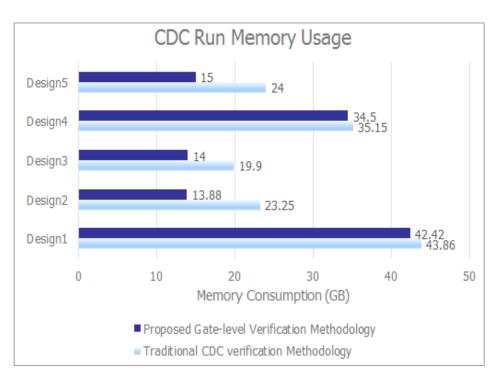

### **Experiment Results**

- Average 1.6x improvement in runtime

- Average10% improvement in memory consumption

- No iterations required for setup

### **Experiment Results**

- Upto 80% reduction in noise

- Bit-merging

- Constraints & waivers reuse

- Test logic removed

### **Summary**

- Gate-CDC verification is necessary

- Proposed methodology addresses gate-level CDC verification challenges

- Automatic RTL constraints transformation engine

- Auto detection of test logic

- Detect glitches introduced in synthesis

- Regroup bit-blasted CDC paths

- Correlates gate-CDC results with RTL

- Waiver reuse

- Benefits

- Seamless setup and reduced noise

- Accelerates verification closure

### **Summary**

- Gate-CDC verification closure in now possible

- Proposed methodology addresses gate-level CDC verification challenges

- Automatic RTL constraints transformation engine

- Auto detection of test logic

- Detect glitches introduced in synthesis

- Regroup bit-blasted CDC paths

- Correlates gate-CDC results with RTL

- Waiver reuse

- Benefits

- Seamless setup and reduced noise

- Accelerates verification closure

# **Thank You**