# A SystemC Library for Advanced TLM Verification – Towards an *Enhanced* OVM/UVM for SystemC

Marcio F. S. Oliveira, Christoph Kuznik, Wolfgang Mueller

University of Paderborn / C-LAB Germany

<u>marcio@c-lab.de</u> kuznik@c-lab.de wolfgang@acm.org

Wolfgang Ecker, Volkan Esen

Infineon Technologies Munich, Germany

Wolfgang.Ecker@infineon.com Volkan.Esen@infineon.com

### **Agenda**

- Introduction

- Verification Methodology Libraries: Quick History Review

- OVM and UVM for SystemC

- System Verification Methodology Library

- Library Overview

- Available Features

- Library Examples

- Final Remarks

#### Introduction

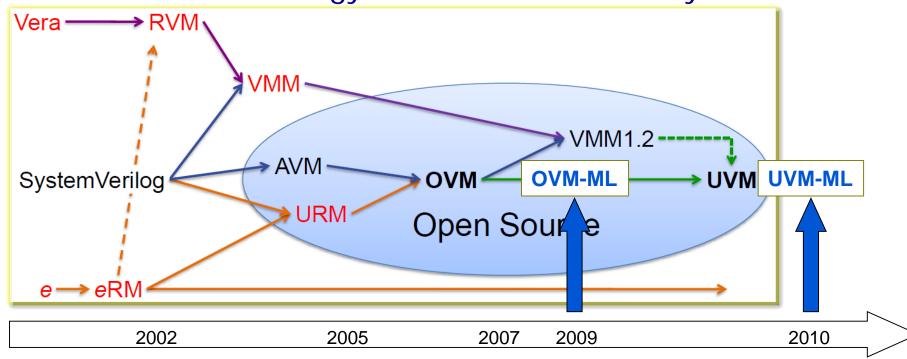

Verification Methodology Libraries: Quick History Review

#### Introduction

#### OVM and UVM for SystemC

- Partial implementation of OVM/UVM base package:

- Phasing

- ovm\_component

- Configuration

- Factory

- Packing

Provides interoperation with SystemVerilog Environment

No verification methodological expertise transfer from SystemVerilog to SystemC version

- SANITAS project: Improvements for verification at TLM

- Industrial automation

- Automotive

- OVM and SystemC as basic technologies

- Vendor neutral implementation

- Promotes the convergence to unified verification methodology library for SystemVerilog and SystemC

System Verification Methodology

**Library - SVM** Others SANITAS' **SVM Library Overview** Partners Contribution Randomization System Verification Methodology Library and Register **Stimulus** Transaction Structural Constraints Abstraction Components Sequence Routing Layer **Transaction OVM-SC library** Recording **Assertions** Ovm Configuration Component Cmd-Line **Processor Factory** Phasing Packing Automation Callbacks Coverage Cadence OVM-ML

Cadence OVM-ML contribution to OVM-world

OSCI SystemC

**Boost Libraries**

ISO/IEC C++

#### Base Package

- Add features:

- Callbacks

- Transaction routing

- Transaction recording

- Command-line processor

- Alignment of OVM and SystemC Simulation Phases

- Emulation of Connection Phase

- Limitation: no full hierarchical path name for binding

#### Component package

- Provides structural components for systematic testbench development

- Includes Testbench, Environment, Agent, Sequencer, Driver, Monitor, Scoreboard, Subscriber

- Adds transaction API to components

- Use of TLM to TLM and TLM to RTL interfaces

#### Component package

```

class ActorAgent : public svm_agent {

tlm::tlm analysis port<tlm::tlm generic payload > aport;

ActorDriver *pDriver;

ActorMonitor *pMonitor;

ActorSequencer *pSequencer;

SVM COMPONENT UTILS(ActorAgent)

void ActorAgent::build()

svm agent::build();

get config_int("debug", debug);

pSequencer = DCAST<ActorSequencer*>(

svm factory::create component(

"ActorSequencer", "", "pSequencer") );

```

#### Component package

```

void ActorDriver::run()

while(true)

IfxCommandItem *item = new IfxCommandItem();

seq_item_port->get(*item);

//Converts the sequence item to generic payload

// Drives the TLM DUT's ports

iSktOfSif->b transport(trans,myT);

//Syncronize

myT += sc time(1000, SC NS);

wait(myT);

```

- Decouple stimuli from the component hierarchy

- Provides advanced stimuli management

- Ordered stream of high level behavior defined as a set of transactions, with routing of responses to request

- Built-in Sequences: random, simple, all\_sequences

```

class IfxCommandItem : public svm sequence item, public rand obj

randv<IfxCommandValT> command;

randv<unsigned int> degree;

randv<unsigned int> percent;

IfxCommandItem(const std::string& name)

: svm_sequence_item(name)

constraint(0 <= degree() && degree() <= 255);</pre>

constraint(0 <= percent() && percent() <= 99);</pre>

SVM_OBJECT_UTILS(IfxCommandItem);

};

```

```

void ActorTest::run()

{

SequenceOfCommands *pSequenceOfCommands;

pSequenceOfCommands = DCAST<SequenceOfCommands*>(

svm_factory::create_object(

"SequenceOfCommands","","pSequenceOfCommands",false) );

pSequenceOfCommands->start(

pActorAgent->pSequencer, 0, 100, true );

svm_manager::get_instance()->stop_request();

}

```

```

void SequenceOfCommands::body()

static Generator<Context> inline constraints;

static rand vec<IfxCommandValT> commands;

inline constraints(commands().size() <= 20);</pre>

inline constraints(commands().size() >= 10);

SequenceOneCommand *pSequenceOneCommand;

for (int i = 0; i < commands.size(); ++i)</pre>

pSequenceOneCommand = DCAST<SequenceOneCommand*>(

svm::svm_factory::create_object("SequenceOneCommand", "",

"pSequenceOneCommand", false) );

start item(pSequenceOneCommand);

pSequenceOneCommand->fixedCmd = commands[i];

finish item(pSequenceOneCommand);

```

| Feature                     | OVM  | UVM | OVM-SC | SVM   |

|-----------------------------|------|-----|--------|-------|

| Call-backs                  | Yes  | Yes | No     | Yes   |

| Comparison                  |      |     | No     |       |

| Methodology<br>Components   | Yes  | Yes | No     | Yes   |

| Phasing                     |      |     | Yes    | Yes   |

| Polices                     | Yes  | Yes | No     | No    |

| Recording                   | Yes  | Yes | SCV    | I     |

| Register Abstraction Layer  | Yes* | Yes | No     | Yes** |

| Reporting                   | Yes  | Yes | SC     | SC    |

| Transaction Routing         |      |     | No     |       |

| Sequencing / Stimulus       | Yes  | Yes | No     | Yes   |

| Assertion                   | SV   |     | No     | Ι     |

| Coverage                    |      |     | SCV    | I     |

| Randomization / Cosntraints | SV   | SV  | SCV    | I     |

Oliveira, Marcio F. S., C-LAB, University of Paderborn

15 of 22

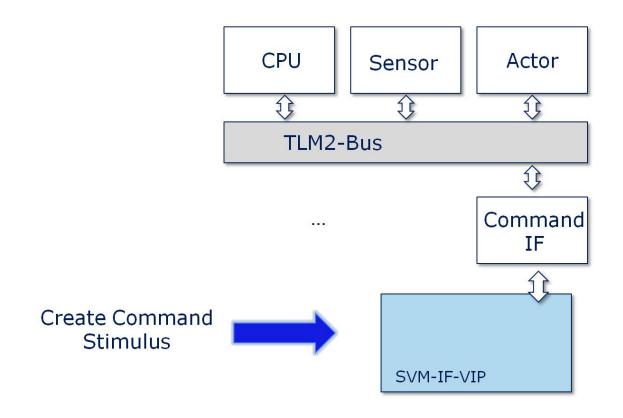

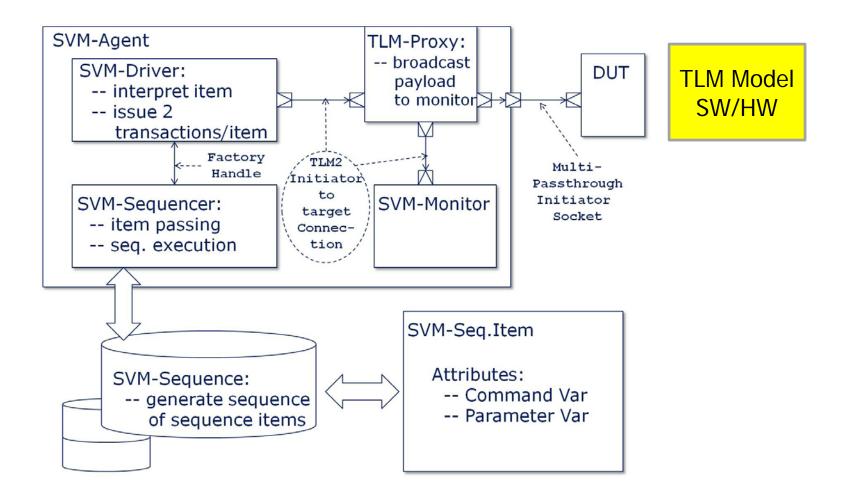

### **Library Example**

### **Library Example**

- TLM-Proxy broadcasts transactions to DUT and Monitor

- Regular TLM2 interfaces connects DUT and VC

- Delta-free connection

- Better performance by applying Quantum Keeping

- Plain SystemC provides several advantages

- Avoid delta-cycles between DUT and testbench

- Enables the verification of timing-abstraction such as TLM+ and quantum keeping

#### Final remarks

- A (fully) implemented Verification Methodoly Library for SystemC based on OVM

- Provides advanced features for TLM verification

- Improved the verification methodology for SystemC by adding new features as Components, Sequences, etc

- Integrated Coverage, Assertion and Randomization

#### **Outlook**

- Alignment with other outcomes of SANITAS project

- Integration of Register Abstraction Layer

- Improvements in the API

- Conformance to UVM

- New features

- SystemC revision P1666-2011

- Exploit the new features

### Acknowledgement

SPONSORED BY THE

Federal Ministry of Education and Research

This work was partly funded by the DFG Collaborative Research Centre 614 and by the German Ministry of Education and Research (BMBF) through the BMBF project SANITAS (01M3088).

Thank you for your attention!

Are there any questions?

### **Library Example**