# A concept for expanding a UVM testbench

to the analog-centric toplevel

Felix Assmann<sup>1</sup>, Axel Strobel<sup>1</sup>, Hans Zander<sup>2</sup>

<sup>1</sup>Bosch Sensortec GmbH, Dresden, Germany <sup>2</sup>Cadence Design Systems Inc., Feldkirchen, Germany

#### INTRODUCTION

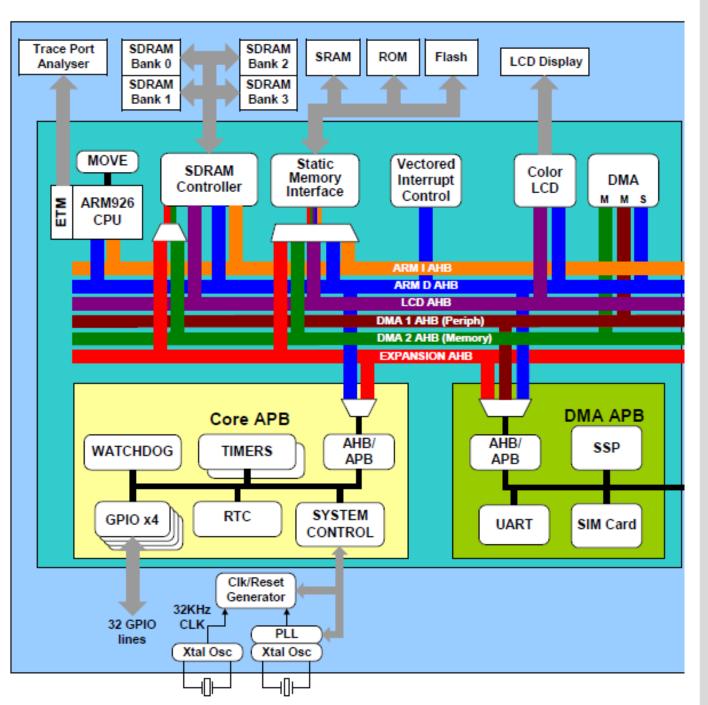

- Challenges in todays mixed signal designs:

- Analog and digital together (highest complexity)

- DUV communicates via pins and protocols (SPI/I<sup>2</sup>C)

- Different verification scenarios like Wafer Level Test, Module Test or Normal operation

#### **Requirements for an analog-centric verification environment**

- Analog- and digitalteam need always working testbench

- Coverage and checks for verification team only

- Interactive features like register read/write or pin read/write

- NVM/RAM/EPROM/... need to be configured

- Analog-, digital- and verificationteam need to work closely

- But everybody has a different understanding about verification

- How to bring everything together?

- Configurable testbench to cover different verification scenarios

- We need a special testbench architecture and an AMS driven simulation flow

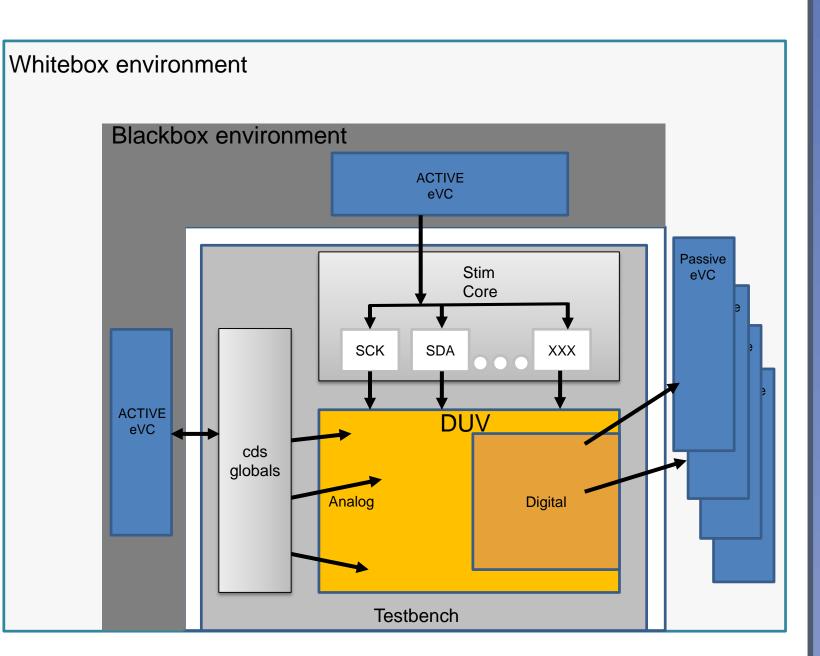

### **Blackbox/Whitebox approach**

#### Blackbox:

- Testcase development

- Always working, contains interface UVC's only

- No checks

- Contains interactive command interface for debugging

- Contains configuration sequences

- Generates RAM and NVM

- For gate level

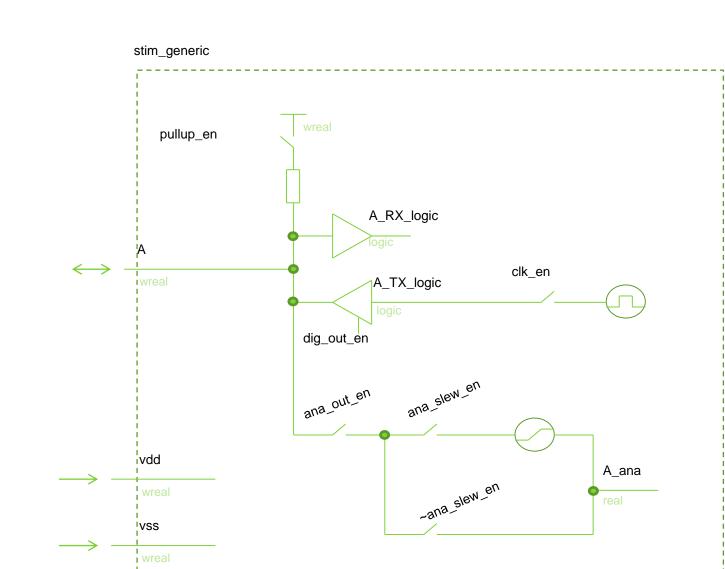

### **AMS driven simulation flow**

- Generic pin modules

(digital/analog stimulus, pullup, supply ramp, ...)

- VAMS file to configure analog models (cds\_globals), controlled by UVC

- Model analog sub blocks only (model as close as possible to transistor level)

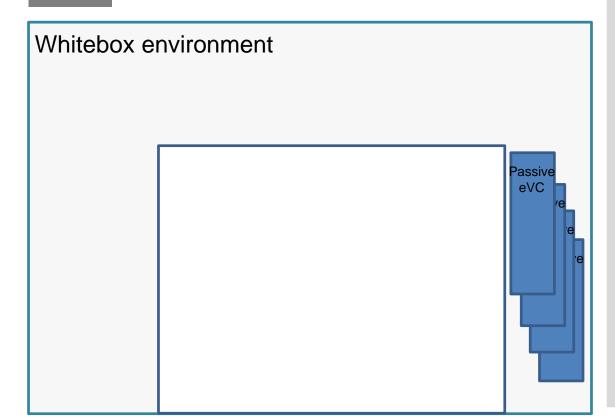

#### Whitebox:

- For regression

- Contains all UVC's

- Imports Blackbox for modular reuse

- All tests from Blackbox can be run in Whitebox

- All Blackbox features are usable

- Supply sensitive connect modules

- Use of config views for netlisting to cover different scenarios

## **CONCLUSIONS**

- One toplevel testbench

- Efficient testcase creation

- Efficient analog component adjustment

- Simulation time speedup (10s vs. 5min with different configurations)

- Analog-, digital- and verificationteam work closely together

#### **REFERENCES**

Ira Miller, Ana Ferreira-Noullet, Behavioral Modeling in Industrial IC Design Experiences and Observations, BMAS, 2004

Jones, K., Analog and mixed signal verification, FMCAD, 2008

Mixed-Signal System-on-a-Chip (SoC) Verification Based on SystemVerilog Model, 45th Southeastern Symposium on System Theory Baylor University, 2013

Chao Liang, Mixed-Signal Verification Methods for Multi-Power Mixed-Signal Systemon-Chip (SoC) Design, ASICON, 2013

#### Next steps:

- Verification of analog models

- Enhance interactive mode

- Testbench qualification

© Accellera Systems Initiative