### INTRODUCTION

#### Abbreviations SC: SystemC SV: SystemVerilog **TLM:** Transaction Level Modelling **UVMC:** Universal Verification Methodology Connect

Today's world deals with a lot of designs involving mixed languages like SV and SC. This paper describes an easy method of integrating these two languages, using TLM connections made via **UVMC**. Using a UVMC example, this paper will demonstrate how to build, connect and execute a verification simulation with SV and SC.

With the increasing use of mixed language in today's semiconductor and design industry, the question arises of how to effectively verify such complex designs. The strength of each language can be used to provide random verification for your model. And you can leverage the **speed and capacity of SC** for verifying untimed or loosely timed system-level environments. In this paper, we will discuss two examples, one is a simple example dealing with TLM-1.0 and a complex example with TLM-2.0. TLM uses transaction-based methods which can be used for communication between modules.

This paper discusses two examples. One is a simple example of data transfer by port connection and the other is data transfer of different transaction types and sizes on both the SV and SC side.

# Why not "Connect" using UVM Connect: Mixed Language communication got easier with UVMC

## Vishal Baskar

Siemens Industry Software, 46871 Bayside Parkway, Fremont, CA 94538 Vishal.Baskar@siemens.com

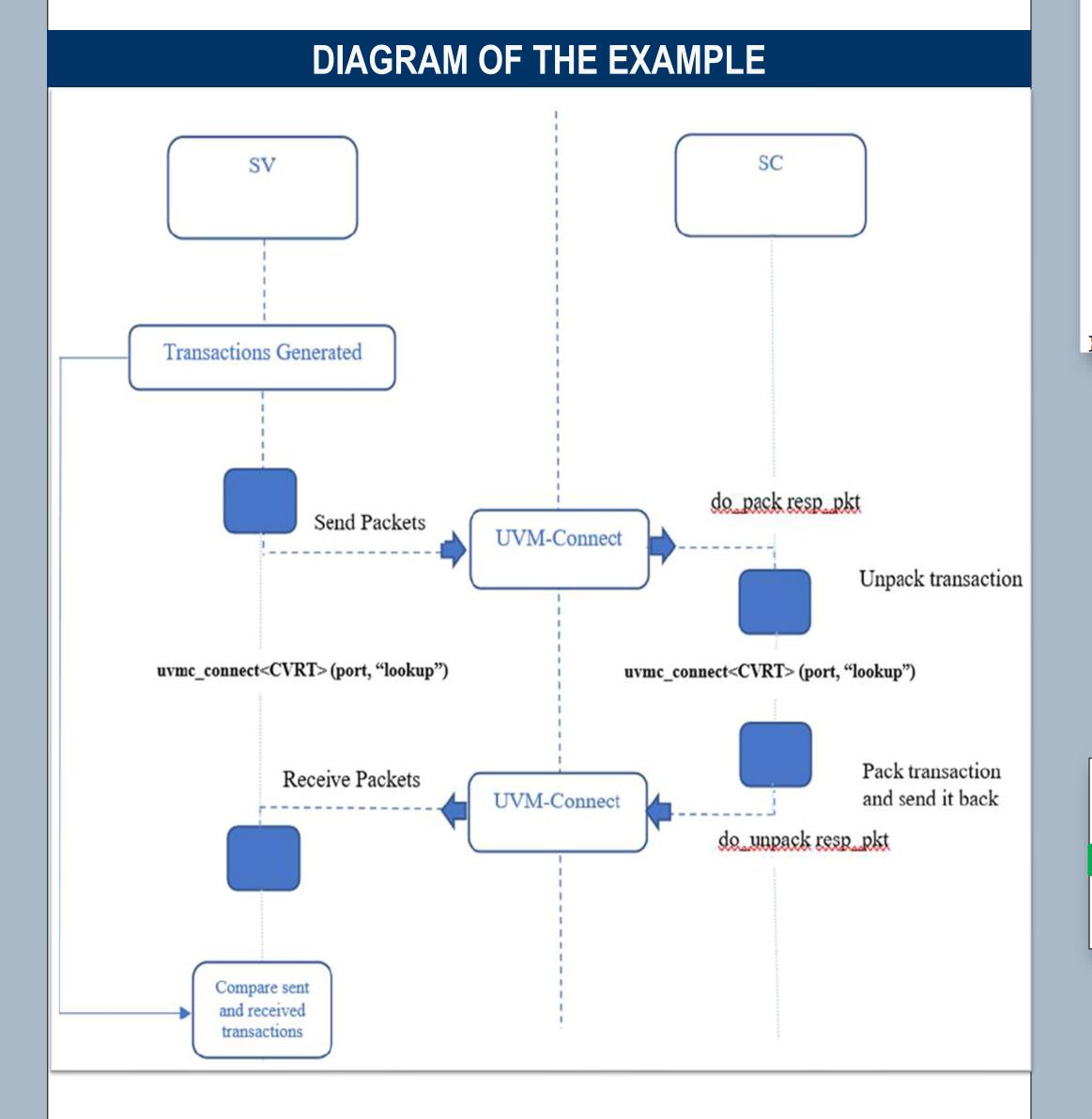

| EXAMPLE OF SIMPLE PORT CONNECTION                                                                                                                                                                          |                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| In this example, packets of data are being transferred from the                                                                                                                                            |                     |

| SV side to the SC side via <b>TLM 1.0 blocking transport port</b><br>using the UVM connections, and unpacking is done on the SC                                                                            |                     |

| side, and the bits are then sent back to the SV side, ensuring no                                                                                                                                          |                     |

| loss of data. To communicate, the datatype for the connections                                                                                                                                             |                     |

| should look the same regardless of the types. During elaboration,                                                                                                                                          | 1                   |

| in the SV side, UVMC will connect the ports whose registered                                                                                                                                               | 9                   |

| "lookup" strings match. In the example below,<br>"transport_port_sv_out" is the lookup string and the same look                                                                                            |                     |

| up string will be used from the SC side.                                                                                                                                                                   |                     |

| <pre>virtual function void connect_phase(uvm_phase phase);     super.connect_phase(phase);     uvmc_tlm1 #(req_packet, rsp_packet)::connect(out, 'transport_port_sv_out") endfunction</pre>                | class p<br>`uvm_    |

| SV Side:                                                                                                                                                                                                   | type<br>rand        |

| <pre>class req_packet extends uvm_sequence_item; class rsp_packet extends uvm_sequence_item;</pre>                                                                                                         | rand                |

| rand bit rnw; rand bit [32-1:0] addr;                                                                                                                                                                      | rand<br>funct       |

| rand bit [32-1:0] addr;<br>rand logic [32-1:0] wdata;<br>bit [32-1:0] rdata;                                                                                                                               | sup<br>endfu        |

| endclass : rsp_packet                                                                                                                                                                                      | virtu<br>`uv<br>`uv |

| endclass : req_packet                                                                                                                                                                                      | ` u\<br>` u\        |

| <u>SC Side:</u>                                                                                                                                                                                            | endfu               |

| class req_packet                                                                                                                                                                                           |                     |

| <pre> l class rsp_packet</pre>                                                                                                                                                                             | 1                   |

| sc_bv < 32 > addr;       sc_bv < 32 > addr;         sc_lv < 32 > wdata;       sc_bv < 32 > rdata;         sc_bv < 32 > rdata;       rsp_packet() { }                                                       |                     |

| <pre>req_packet() { } virtual ~rsp_packet() { }</pre>                                                                                                                                                      |                     |

| <pre>virtual void do_pack(uvmc_packer&amp; p) const {     p &lt;&lt; rnw ;     p &lt;&lt; addr ;     p &lt;&lt; addr ; </pre> virtual void do_pack(uvmc_packer& p) const {     p << addr ;     p << addr ; |                     |

| p << uddi y y y y y y y y y y y y y y y y y y                                                                                                                                                              |                     |

| <pre>} virtual void do_unpack(uvmc_packer&amp; p) {     p &gt;&gt; addr ;     p &gt;&gt; addr ;     p &gt;&gt; addr ;     p &gt;&gt; addr ; </pre>                                                         | 2                   |

| <pre>p &gt;&gt; rnw ; p &gt;&gt; addr ; p &gt;&gt; wdata ; </pre>                                                                                                                                          |                     |

| p >> rdata ;<br>}                                                                                                                                                                                          |                     |

| };<br>A concurrent of the second                                                                                       |                     |

| A consumer class with a transport port in the SC side, is created<br>to receive the packet on the "put" port ( <b>sv_out</b> ) and send it back                                                            |                     |

| to the analysis port ( <b>sv_in</b> ) on the SV side.                                                                                                                                                      |                     |

| <pre>sc_export<tlm::tlm_transport_if <="" req_packet,="" rsp_packet=""> &gt; sv_out; rsp_packet tx_rsp;</tlm::tlm_transport_if></pre>                                                                      |                     |

| <pre>consumer_with_transport_port(sc_module_name nm) : sc_module(nm), sv_out("sv_out"), tx_rsp()</pre>                                                                                                     | i                   |

| {<br>sv_out(*this);                                                                                                                                                                                        | f                   |

| <pre>} int sc_main(int argc, char* argv[]) {     consument with transport point cons("cons");</pre>                                                                                                        |                     |

| <pre>consumer_with_transport_port cons("cons"); <u>uvmc_connect<reg_r< u="">sp_packet_converter, req_rsp_packet_converter &gt; (cons.sv_out,</reg_r<></u></pre>                                            |                     |

| <pre>transport port sv out");     sc_start();</pre>                                                                                                                                                        |                     |

| return 0;<br>}                                                                                                                                                                                             |                     |

| A <b>comparator</b> function checks the transaction queues " <b>out_q</b> " and " <b>in_q</b> " and then checks for the size of the bits in the transactions, on the SV side.                              |                     |

| <pre>virtual function void do_check();     int unsigned min_size;</pre>                                                                                                                                    |                     |

| <pre>`uvm_info(get_type_name(), \$psprintf("out_q size: %1d, in_q size<br/>%1d"_out_q size(),in_q.size()), UVM_LOW)<br/>if (out_q.size() == in_q.size()) begin<br/>compare_status = 1;</pre>               | ::                  |

| end else begin<br>compare_status = 0;<br>end                                                                                                                                                               |                     |

|                                                                                                                                                                                                            |                     |

### COMPLEX EXAMPLE USING CONVERTERS

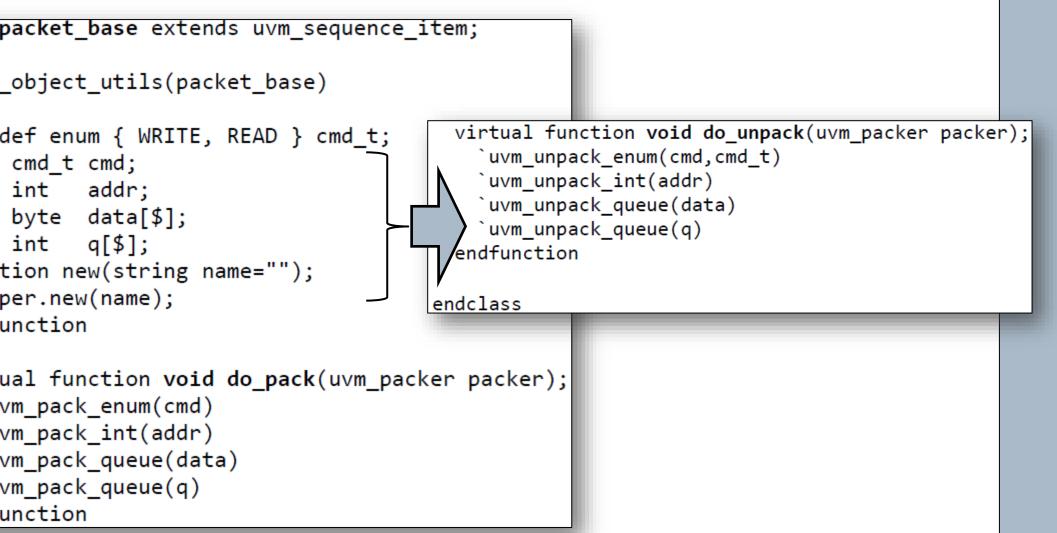

When the data types other than the generic payload are required, one can define a conversion algorithm for all connections of a transaction type or design a custom-made conversion algorithm for each connection using TLM-2.0 libraries. Although both the component agrees with the same content of the transaction, this time their transaction definitions are of different types. A converter can adapt different transaction definitions and at the same time serialize the data. In the SV side, a conversion algorithm is declared within transaction class itself which is derived from **uvm\_sequence\_item.**

In the **connect phase**, we register the producer's output port for the UVMC connection using the search string "stimulus". The SC side registers its consumer's port with the same search string. UVMC will match these two strings and complete the crosslanguage connection, i.e. SV producer's <out> port will be bound to the SC consumer's <in> export

#### SV Side:

```

module sv_main;

function void connect_phase(uvm_phase phase);

uvmc_tlm #(packet)::connect(prod.out, 'stimulus');

endfunction

```

A generic producer is parameterized on the transaction type. The packets that are sent from the SV side are checked with the ones that are received from the SC side and are checked for inverted data and addresses ensuring no loss in packets during the process.

#### **Producer**:

```

class producer #(type T=int) extends uvm_component;

uvm_tlm_b_transport_port #(T) out;

int num_pkts;

`uvm_component_param_utils(producer #(T))

```

Ideally, we would have this mirror the transaction types on the SV-side. Or we can choose a nominal way to write our **custom** converter. We will define a converter for this packet, then connect an instance of the consumer with an SV-side producer using a **blocking transport interface** conveying that transaction.

struct packet\_converter : public uvmc\_converter<packet> static void do\_pack(const packet &t, uvmc\_packer &packer) int cmd\_tmp; if (t.write)  $cmd_tmp = 0;$ else  $cmd_tmp = 1;$ packer << cmd\_tmp</pre> << t.addr\_lo << t.addr\_hi << (int)(t.len) << t.payload << t.sc\_q; static void do\_unpack(packet &t, uvmc\_packer &packer) { int cmd\_tmp; vector<unsigned char> data\_tmp; packer >> cmd\_tmp >> t.addr\_lo >> t.addr\_hi >> data\_tmp; class sc\_env: public sc\_module public: consumer<packet> cons; sc\_env(sc\_module\_name nm) : cons("cons") {uvmc\_connect<packet\_converter>(cons.in,'stimulus') int sc\_main(int argc, char\* argv[]) sc\_env env("env"); sc\_start(); return 0; Consumer: template <class T> class consumer : public sc\_module, public tlm\_blocking\_transport\_if<T> { public: sc\_export<tlm\_blocking\_transport\_if<T> > in; consumer(sc\_module\_name nm) : in("in") in(\*this); CHALLENGES AND THE FUTURE Earlier, the objects on the SC side should have equivalent data types and fields with that of the SV side. This was resolved by using a **converter or an adapter** that translates between the transaction types irrespective of the data types and sizes. Earlier versions of the UVMC library "do\_pack" and "do\_unpack" functions implemented as methods of transactions had their **shortcomings** in payload length limiting it to not more than **4K Bytes**. But with the latest UVMC library 2.3.1, they have not only removed fixed limitations on the data payload sizes but have also added the support for "fast packer converters" which greatly improves the performance. UVMC bridges both language boundaries by providing TLM-1.0 and TLM-2.0 connectivity between components. The UVMC libraries and SV UVM components can be used to **independently design and communicate** without referencing each other and can further be integrated into both and mixed-language environments without native modifications, making them **reusable**. With the increasingly complex designs that are emerging in today's world, it is safe to say that UVMC has the **flexibility** to connect different UVM components involving SV and SC models with ease.

#### SC Side - Custom Converter: