# What Does The Sequence Say? Powering Productivity with Polymorphism

Rich Edelman Siemens Digital Industries Software Siemens EDA Fremont, CA 94538

*Abstract*-In a SystemVerilog UVM testbench a UVM sequence is much like a program or a function call or a test. Writing interesting sequences can help with productivity and coverage closure. On one hand a sequence is simply a list of instructions, but on the other hand how those instructions are built or how they are used with other instructions can improve the test. This paper will demonstrate easy ways to incorporate new transactions and sequences into a SystemVerilog UVM Testbench.

#### I. INTRODUCTION

This paper assumes some familiarity with SystemVerilog [1] and the UVM [2]. The examples here will be simple, but some of the concepts will be easier with a deeper background. Certainly, new users to the UVM can understand these concepts and can apply them to their first testbench. This is not a primer for new object-oriented programmers.

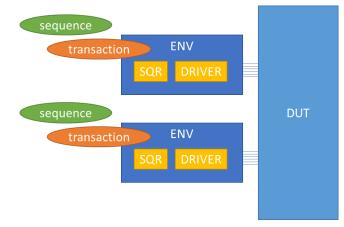

Our UVM testbenches in this paper will resemble the architecture below. A collection of UVM components (sequencer and driver) will be constructed in an environment (or agent). A sequence will be constructed by a test or a virtual sequence. It will be "started" (run) on the sequencer. It will generate transactions which will "go into the sequencer" and then get picked up by the driver. The driver will cause those transactions to be interpreted and the appropriate bus signals to be driven. This is basic UVM. Nothing fancy. The basic testbench is very simple. Our productivity boost will come from not changing any existing code, but by simply adding a few lines of new code and "overriding" the factory constructions.

Figure 1 - Basic UVM Testbench with Two Interfaces

II. UNDERSTANDING INHERITANCE AND POLYMORPHISM

# The Base Class

Polymorphism is about inheritance in an object-oriented programming world. Polymorphism is simple. But the details get hard sometimes. A polymorphic object is much like the base class, but "better". For example, if we had a base class describing a BALL object, we could derive a BASKETBALL and a RACQUETBALL from the BALL object. We could further derive a kids BASKETBALL and a professional BASKETBALL from a BASKETBALL

```

class ball;

virtual function string get_name();

return "Ball";

```

```

endfunction

virtual function void print();

$display("%s", get_name());

endfunction

endclass

```

The class 'ball' is our base class. It defines two functions, get\_name() and print(). They are virtual functions. Virtual functions are important later when the polymorphic object handles are used. This is important. When a handle is used to call a function, the function called could be from the DECLARED class of the object (ball) or the actual handle type (in the case of polymorphic assignments) – the function in the ACTUAL, DERIVED class. If the function is declared as a virtual function, then the derived version is used in the case of a polymorphic assignment. That's what we want. Generally, just always declare functions and tasks as virtual. It will usually be what is wanted.

```

class basketball extends ball;

virtual function string get_name();

return {"Basketball", "<=", super.get_name()};

endfunction

endclass

```

The class 'basketball' is an extended class, or a refinement, or specialization of a ball. It is by some measure a "better ball". Notice it redefines get\_name() and calls super.get\_name(). Calling super.get\_name() is the way we can call the base class function get\_name(). Notice also that basketball does not define a new print() function. It will inherit the implementation from ball.

```

class kids_basketball extends basketball;

virtual function string get_name();

return {"Kids Basketball", "<=", super.get_name()};

endfunction

endclass

class pro_basketball extends basketball;

virtual function string get_name();

return {"Pro Basketball", "<=", super.get_name()};

endfunction

endclass

class racquetball extends ball;

virtual function string get_name();

return {"Racquetball", "<=", super.get_name()};

endfunction

endclass

```

In a manner like basketball, we define kids\_basketball and pro\_basketball as extended classes from basketball, and a racquetball class extended from ball.

# The Extended Class (derived class)

For the extended class, say 'pro\_basketball', calling the print function will call the implementation in the base class, which calls get\_name(). This is where the 'virtual' definitions help us. Which get\_name() should get called? Ball? Basketball? Pro\_basketball? The answer is pro\_basketball. The pro\_basketball.get\_name() will call super.get\_name() for the basketball, which will call super.get\_name() for the bask.

#### Definitions of class handles

Simple declarations of class handles. Nothing special yet.

```

ball BALL;

basketball BASKETBALL;

kids_basketball KIDS_BASKETBALL;

pro_basketball PRO_BASKETBALL;

racquetball RACQUETBALL;

ball ANY_BALL[5];

```

#### Class Object creation and handle assignment

The objects get constructed with new(). Nothing special yet.

```

initial begin

BALL = new();

BASKETBALL = new();

KIDS_BASKETBALL = new();

PRO_BASKETBALL = new();

RACQUETBALL = new();

```

# Calling print()

Using the object handles to call a function (print). Nothing special yet.

BALL.print(); BASKETBALL.print(); KIDS\_BASKETBALL.print(); PRO\_BASKETBALL.print(); RACQUETBALL.print();

# Assigning handles polymorphically

The array of handles (ALL\_BALLS) is an array of "balls". The ball, basketball, kids\_basketball, pro\_basketball and racquetballs are all "balls". They are "assignment compatible" with ball. They can be assigned to a ball.

ANY\_BALL[0] = BALL; ANY\_BALL[1] = BASKETBALL; ANY\_BALL[2] = KIDS\_BASKETBALL; ANY\_BALL[3] = PRO\_BASKETBALL; ANY\_BALL[4] = RACQUETBALL;

Special. ANY\_BALL is declared as an array of 'balls' types. Yet, we're assigning those array elements object handles that are BASKETBALL, KIDS\_BASKETBALL, PRO\_BASKETBALL and RAQUETBALL. This is allowed, since those listed object handles are all "better balls".

## Calling print() polymorphically

For each of the "balls", call the print() function

```

foreach (ANY_BALL[i])

ANY BALL[i].print();

```

Very special. This is the power of polymorphism at work. Print() gets calls in each of the objects – ANY\_BALL[4].print() calls the RACQUETBALL print() routine.

Directly assigning an extended class handle to a base class handle

```

BALL = RACQUETBALL;

BALL.print();

```

The print() routine that gets called in this case is the RACQUETBALL.print() routine. The print function is a virtual function, so the particular print function that will be called will be the print() function defined in the object type of the object handle – not the object type of the declared variable (BALL is a declared ball object).

The ball example is a simple example. The remainder of this paper will use the virtual functions, inheritance and polymorphism to describe how to easily extend a UVM testbench to improve productivity.

# III. THE BASIC UVM TRANSACTION

The design of a UVM testbench often starts with a transaction class. The transaction class below defines a few random variables (rw, addr, data), and some non-random variables (low\_addr, high\_addr, id). It also defines two random constraints to control the value of addr and the contents of the data array. It has a constructor and defines convert2string and do\_record. Convert2string is a simple way to return a string value of a transaction. Do\_record describes the transaction data that will be recorded.

#### Transaction Base Class

```

typedef enum bit {READ=1, WRITE=0} rw_t;

class transaction extends uvm_sequence_item;

```

```

`uvm object utils(transaction)

// Read and Write to Memory

rand rw t rw;

rand reg [31:0] addr;

rand reg [7:0] data [];

reg [31:0] low_addr;

reg [31:0] high addr;

reg [7:0] id;

constraint legal range {

addr >= low_addr;

addr <= high addr;

}

constraint max length {

data.size() < 16;

data.size() > 0;

}

function new(string name = "transaction");

super.new(name);

low_addr = 0; // Defaults

high addr = 256;

endfunction

function string convert2string();

return $sformatf("%s %0d %p (%s) id=%0d",

(rw==READ) ?"READ":"WRITE",

addr, data, get_type_name(), id);

endfunction

function void do record(uvm recorder recorder);

super.do record(recorder);

`uvm record field("name", get name())

`uvm_record_field("rw", rw)

`uvm record_field("addr", addr)

`uvm record field("data", data)

`uvm record field("id", id)

endfunction

endclass

```

# Extended Transaction Types

Three extended transaction types are defined below. They extend the basic transaction – making it in some ways better. These specialized transactions will be used to augment our generated transactions from the sequence. But the sequence doesn't know anything about these new types. And it doesn't need to.

```

class odd_address_transaction extends transaction;

`uvm_object_utils(odd_address_transaction)

constraint odd_address {

addr[0] == 1;

}

...

endclass

```

The odd transaction adds a constraint so that every address is odd.

```

class big_transaction extends transaction;

`uvm_object_utils(big_transaction)

constraint max_length {

data.size() < 255;

data.size() > 63;

}

...

endclass

```

The big\_transaction changes (overrides) the base class constraint 'max length'.

```

class double_transaction extends transaction;

`uvm_object_utils(double_transaction)

rand reg [31:0] addr2;

constraint legal_range_addr2 {

addr2 >= low_addr;

addr2 <= high_addr;

}

constraint addr2_value {

addr2 != addr;

}

function string convert2string();

return $sformatf("%s (addr2=%0d)",

super.convert2string(), addr2);

endfunction

...

```

endclass

The double\_transaction adds a new class member variable (addr2) and two constraints for its value. Additionally, it implements a new convert2string().

## IV. THE BASIC SEQUENCE

#### Basic Sequence

The basic sequence is simple. It creates, randomizes and issues 'maximum\_transactions' and ends. It only knows about the 'transaction' type. It is a basic sequence.

```

class basic sequence extends uvm sequence#(transaction);

`uvm object utils(basic sequence)

transaction tr;

string name;

int maximum transactions;

. . .

task body();

for (int i = 0; i < maximum transactions; i++) begin</pre>

name = $sformatf("transaction%0d", i);

tr = transaction::type id::create(name);

start item(tr);

if (!tr.randomize()) begin

`uvm_info(get_type_name(), "Randomize FAILED",

UVM MEDIUM)

end

finish_item(tr);

end

endtask

endclass

```

#### Extended Sequence - The Checker

The checker\_sequence below is an extended sequence. It extends the basic sequence, adds a data field and changes the behavior. This sequence only knows about the transaction type 'transaction'.

```

class checker_sequence extends basic_sequence;

`uvm_object_utils(checker_sequence)

reg [7:0] wdata [];

...

task body();

for (int i = 0; i < maximum_transactions; i++) begin

name = $sformatf("transaction%0d", i);

tr = transaction::type_id::create(name);

```

```

// Write

start item(tr);

if (!tr.randomize()) begin

`uvm info(get type name(), "Randomize FAILED", UVM MEDIUM)

end

tr.rw = WRITE; // Force WRITE.

finish item(tr);

wdata = tr.data;

// Read

tr.rw = READ; // Force READ.

start item(tr);

finish item(tr);

// Check

if (wdata != tr.data)

uvm_info(get_type_name(),

$sformatf("Mismatch Wrote %p, Read %p", wdata, tr.data), UVM_MEDIUM)

end

endtask

endclass

```

The checker\_sequence is a self-checking sequence. It issues a randomized WRITE, and then it READS from the same location, checking the data read against the data written.

# V. THE UVM FACTORY

In the sequences above – and the remaining classes in this testbench, the UVM Factory is used to create objects. The UVM Factory is a polymorphic system. The call below calls the factory interface to return a class of type 'transaction'.

tr = transaction::type id::create(name);

Normally, when the call above returns, a 'transaction' object handle would be returned. But the UVM Factory has a way to override the type of object returned. The call below tells the factory to return a different type – a derived type, instead of a 'transaction'. It is quite a mouthful. But this syntax means "anytime the factory is asked for a transaction object instance, instead, please construct an odd address transaction object instance.

transaction::type id::set type override(odd address transaction::get type(),1);

There are multiple different ways to override the types in the factory. The above syntax is the recommended way to over a type. A specific instance can also be overridden using

transaction::type\_id::set\_inst\_override(object\_type,"inst\_path", parent);

Productivity can be increased by overriding transaction and then the basic transaction can generate many different transaction streams. In addition to overriding the transaction, the basic\_sequence could also be overridden with the checker\_sequence. Overriding the sequence allows a different "program" to generate and check transactions.

The syntax below tells the factory that anytime a basic\_sequence is requested to instead return an object of type checker\_sequence.

basic sequence::type id::set type override(checker sequence::get type(),1);

With both overrides in place, the old testbench with a basic\_sequence and a transaction are now a new test with a checker\_sequence and an odd\_address\_transaction

# VI. FIRST PRODUCTIVITY

This is the first step in productivity. By defining new transactions and new sequences, an existing testbench can be easily reused. But there are some limitations. The UVM Factory allows a type or instance to be overridden. That replaces one type for the other type. But what if we wanted to randomly pick a transaction type? For example, instead of getting just a 'transaction' or the overridden 'odd\_address\_transaction', what if we wanted to randomly choose between three different transactions at the same time? We need a way to choose from a set of object types – not just have one that replaces the other.

#### The Transaction Picker

We can create an object that will pick from a list and give us back one of the objects. This is a kind of factory. The factory is still being used, but the picker allows for many types to replace one type, not just one for one.

The transaction picker below is really nothing more than a global array of object types. From that array, when 'get()' is called, one of the object types will be constructed and returned. This transaction picker can return any polymorphically related object.

```

class transaction picker;

static uvm object wrapper types[$];

static int

number[$];

static function void add(uvm object wrapper w);

types.push front(w);

endfunction

static function transaction get();

transaction tr;

string name;

uvm object o;

int d;

d = $urandom_range(types.size()-1, 0);

o = types[d].create object("transaction picker");

name = $sformatf("%s%0d", types[d].get type name(), number[d]++);

o.set name(name);

$cast(tr, o);

return tr;

endfunction

endclass

```

## Putting objects into the picker

The transaction picker is a static object with static variables. Calling 'add' using a mouthful of syntax is easy.

```

transaction_picker::add( transaction::get_type());

transaction_picker::add(odd_address_transaction::get_type());

transaction_picker::add( big_transaction::get_type());

transaction_picker::add( double_transaction::get_type());

```

The picker is really just a global array that randomly returns a value from the array when get() is called. Exactly what is desired. When a transaction is needed, the picker will pick one from the array.

#### Getting objects from the picker

Any object which desires to get an object handle to a derived class of transaction simply has to call the 'get()' function in the picker. Instead of calling new() or TYPE::type\_id::create() a sequence would call the get() call.

Replace the factory interface

tr = transaction::type\_id::create(name);

with the picker interface

tr = transaction\_picker::get();

Anyone needing a homework assignment can make the picker parameterized so that it works for any type of class.

## VII. SECOND PRODUCTIVITY

With the picker in place in the checker\_sequence, the basic\_sequence test has been extended to be a self-checking sequence with a few different types of transactions. Without changing any code, productivity is improved with random transaction types and a self-checking sequence.

The astute reader might be wondering "Why not use the UVM Sequence Library?" – at least for sequence picking. The answer is simplicity, transparency and debuggability. The UVM Sequence Library is 815 lines long. The transaction picker is 21 lines long and is readable.

# VIII. INTERRUPT SEQUENCES

The job of an interrupt sequence is to wait for an interrupt to occur, then "service" that interrupt. A sequence can start a transaction which will cause the driver to begin a thread waiting for the interrupt. When the interrupt occurs, the thread will wake up and trigger an event in the transaction handle, which the original interrupt sequence is waiting on. Once that trigger has happened the interrupt sequence can do whatever is necessary to service the interrupt.

#### Interrupt transaction

```

class interrupt_transactionA extends transaction;

`uvm_object_utils(interrupt_transactionA)

int icount;

event w;

...

function string convert2string();

return $sformatf("%s (icount=%0d)", super.convert2string(), icount);

endfunction

endclass

```

Simply supply an event to wait on and trigger. Any additional data could also be here (like icount).

## Interrupt sequences

Create an interrupt transaction handle and send it to the driver. When the start/finish returns, wait for the even to trigger. When it triggers, service the interrupt. After servicing the interrupt, setup another interrupt service thread.

#### Handling interrupt transactions in the driver

```

int interrupt serviceA count;

interrupt transactionA itrA;

task interrupt_serviceA_routine(transaction t);

wait (bus.interruptA);

itrA.icount = interrupt serviceA count++;

-> itrA.w;

endtask

task run_phase(uvm_phase phase);

forever begin

seq item port.get next item(t);

if ($cast(itrA, t)) begin

fork

interrupt serviceA routine(itrA);

join none;

end

else begin // Normal processing

process sequence item(t);

uvm info(get type name()

$sformatf("sending '%s'", t.convert2string()),

```

```

UVM_MEDIUM)

end

seq_item_port.item_done();

end

endtask

```

In the driver use \$cast to create a handler for that interrupt\_transactionA type. The handler will run in a fork/join\_none thread, waiting for the interrupt bus signal. When the bus signal happens, the transaction handle event will be triggered and the driver handler thread will end. It sounds complicated but it's not. The sequence starts a transaction and then waits for any interrupt. The driver simply waits for the interrupt in a thread, and marks the transaction object when the interrupt occurs. (In the same transaction object that originated the interrupt watching).

# IX. OTHER SEQUENCES

# Fire and forget sequences

These fire and forget sequences are just "regular" sequences. The sequences does start\_item(t) and finish\_item(t) and moves to the next generation of transaction. The basic\_sequence is a fire and forget sequence.

## Virtual Sequences. Sequences that communicate with each other. Handle sharing, event triggers

Virtual sequences can be used to start other sequences. A virtual sequence is nothing more than a puppet master getting other sequences to do work for it. It has special knowledge and special access. In the example code below, the virtual sequence has a handle to a collection of environments. It reaches in and starts sequences. And then it coordinates their activities. In this example, each sequence is made to wait for the others before advancing. Each sequence is released to WRITE at the same time. And then each sequence is released to READ at the same time.

| \$    | Signal Name                        | Values C1 |        |           | 3         | 9000   | 40000         | 41000           |            | 4      |

|-------|------------------------------------|-----------|--------|-----------|-----------|--------|---------------|-----------------|------------|--------|

| @syna | ced_sequence@1.state               | WRITING   | WAIT_* | WRITING   | READING   | WRITI* | WAIT_FOR_RE   | AD_PERMISSION   |            | READI* |

| @synd | ced_sequence@2. <mark>state</mark> | WRITING   | WAIT_* | W*WAIT_*  | R*WAIT_*  |        | WRITING       |                 | (WAIT_F*   |        |

| @synd | ced_sequence@3. <mark>state</mark> | WRITING   | READI* | WRI*WAI*  | REA* WAI* |        | WRITING       | WAIT FOR READ F | PERMISSION |        |

| @synd | ced_sequence@4.state               | WRITING   | WAIT_* | * [WAIT_* | R*WAIT_*  |        | WRITIN        | IG              |            |        |

| @synd | ced_sequence@5. <mark>state</mark> | WRITING   | WAIT_* | WRITING * | READING * | WRIT*  | WAIT_FOR_RE   | AD_PERMISSION   |            | READI* |

| @synd | ced_sequence@6.state               | WRITING   | WAIT_* | WRITING   | READI* W* | W*     | WAIT_FOR_READ | _PERMISSION     |            | R*     |

|       |                                    |           | WRI    | TING REA  | DING WRI  | TING   |               |                 | REA        | DING   |

The UVM test below builds a "virtual sequence" named coordinated\_sequence. It fills in the environments (e1, e2, e3, e4, e5 and e6) that it inherited from 'test'. Then the test starts the virtual sequence on a null sequencer. (coordinated\_sequences.start(null)).

```

class coordinated test extends test;

uvm_component_utils(coordinated test)

coordinated sequence coordinated seq;

function void connect phase(uvm phase phase);

coordinated seq.el = el;

coordinated seq.e2 = e2;

coordinated seq.e3 = e3;

coordinated seq.e4 = e4;

coordinated_seq.e5 = e5;

coordinated seq.e6 = e6;

endfunction

task run phase (uvm phase phase);

phase.raise objection(this);

coordinated seq.start(null);

phase.drop objection(this);

endtask

endclass

```

The coordinated\_sequence is simple. It constructs the lower level sequences (synced\_sequences) and starts them on the appropriate sequencers. At the same time, it starts a synchronizer thread that signals to the sequences, and interacts with them.

```

class coordinated sequence extends basic sequence;

`uvm object utils(coordinated sequence)

env e1, e2, e3, e4, e5, e6;

synced sequence seq1, seq2, seq3, seq4, seq5, seq6;

task synchronizer();

forever begin

-> seq1.proceed to write;

-> seq2.proceed to write;

-> seq3.proceed_to_write;

-> seq4.proceed to write;

-> seq5.proceed to write;

-> seq6.proceed to write;

. . .

-> seq1.proceed to read;

-> seq2.proceed_to_read;

-> seq3.proceed to read;

-> seq4.proceed_to_read;

-> seq5.proceed_to_read;

-> seq6.proceed to read;

end

endtask

task body();

seq1 = synced_sequence::type_id::create("sequence1");

seq2 = synced sequence::type id::create("sequence2");

seq3 = synced sequence::type id::create("sequence3");

seq4 = synced_sequence::type_id::create("sequence4");

seq5 = synced sequence::type id::create("sequence5");

seq6 = synced_sequence::type_id::create("sequence6");

fork

synchronizer();

join none

fork

seq1.start(e1.sqr);

seq2.start(e2.sqr);

seq3.start(e3.sqr);

seq4.start(e4.sqr);

seq5.start(e5.sqr);

seq6.start(e6.sqr);

join

endtask

```

```

endclass

```

The synced\_sequence is a lower level – worker – sequence. It's really the same as the checker sequence. It writes data to an address and then reads that same addresses, comparing the written data to the read data. The synced\_sequence adds a couple of events that it waits on. These events allow the virtual sequence to synchronize each of the synced\_sequences. There is also some logic to signal back to the virtual sequence that was too busy for this snippet. Please contact the author for the complete source code.

```

class synced_sequence extends basic_sequence;

`uvm_object_utils(synced_sequence)

event proceed_to_read;

event proceed_to_write;

reg [7:0] wdata [];

task body();

for (int i = 0; i < maximum_transactions; i++) begin

name = $sformatf("transaction%0d", i);

tr = transaction_picker::get();

@(proceed to write);

```

```

// Write

state = WRITING;

start item(tr);

if (!tr.randomize()) begin

`uvm info(get type name(), "Randomize FAILED",

UVM MEDIUM)

end

tr.rw = WRITE; // Force WRITE.

finish_item(tr);

wdata = tr.data;

@(proceed to read);

// Read

tr.rw = READ; // Force READ.

start item(tr);

finish_item(tr);

// Check

if (wdata != tr.data)

`uvm info(get type name(),

$sformatf("Mismatch Wrote %p, Read %p",

wdata, tr.data), UVM MEDIUM)

end

endtask

endclass

```

## X. CONCLUSION

Polymorphism is a useful concept for increasing productivity but can strike fear into the hearts of verification engineers. It shouldn't. A polymorphic object is a "better object", in the same way that a kids\_basketball is a "better ball" and a pro\_basketball is a "better kids\_basketball". By using polymorphism, less code can be written and the code that is written is smaller and easier to understand and debug.

Polymorphic coding can become unhelpful when it is overused. For example, a given testbench could have every object type overridden. In this case, examining the source code can be deceiving, since the code has been completely replaced. In the UVM, polymorphism in the transactions and sequences improves productivity without too much confusion. It is a good way to have "more or better ammunition" to send into the design-under-test. Creating a simple extension and using an override produces new tests. Replacing UVM components can also improve productivity but should be used judiciously. When the structure is changed it can make the testbench harder to understand and debug.

## Happy Coding!

The complete source code is available from the author. It is Apache licensed (the same as UVM).

#### XI. REFERENCES

SystemVerilog LRM, "1800-2017 - IEEE Standard for SystemVerilog--Unified Hardware Design, Specification, and Verification Language", <u>https://ieeexplore.ieee.org/document/8299595</u>

<sup>[2]</sup> UVM 1.1d - https://www.accellera.org/downloads/standards/uvm

# XII. APPENDIX I

#### Polymorphic Testbench

vip pkg.sv || || || vip\_pkg.sv vip\_pkg.sv // === package vip\_pkg; import uvm\_pkg::\*; `include "uvm\_macros.svh" `include "transactions.svh"

`include "drivers.svh"

`include "sequences.svh"

`include "env.svh"

`include "tests.svh" endpackage // ======= 11 transactions.svh transactions.svh 11 transactions.svh // ====== typedef enum bit {READ=1, WRITE=0} rw t; class transaction extends uvm\_sequence\_item; `uvm\_object\_utils(transaction) // Read and Write to Memory rand rw\_t rw; rand reg [31:0] addr; rand reg [7:0] data []; reg [31:0] low\_addr; reg [31:0] high\_addr; reg [7:0] id; constraint legal\_range { addr >= low\_addr; addr <= high\_addr;</pre> } constraint max length {

data.size() < 16;</pre> data.size() > 0; function new(string name = "transaction"); low\_addr = 0; // Defaults high\_addr = 256; endfunction super.new(name); function string convert2string(); return \$sformatf("%s %0d %p (%s) id=%0d", (rw==READ)?"READ":"WRITE", addr, data, get\_type\_name(), id); endfunction function void do\_record(uvm\_recorder recorder); super.do\_record(recorder); `uvm\_record\_field("name", get\_name()) `uvm\_record\_field("rw", rw) `uvm\_record\_field("addr", addr) `uvm\_record\_field("data", data) `uvm\_record\_field("id", id) endfunction endclass

```

class odd_address_transaction extends transaction;

`uvm_object_utils(odd_address_transaction)

constraint odd_address {

addr[0] == 1;

}

function new(string name = "odd_address_transaction");

super.new(name);

endfunction

endclass

class big_transaction extends transaction;

`uvm object utils(big transaction)

constraint max_length {

data.size() < 255;

data.size() > 63;

}

function new(string name = "big transaction");

super.new(name);

endfunction

endclass

class double_transaction extends transaction;

`uvm_object_utils(double_transaction)

rand reg [31:0] addr2;

constraint legal_range_addr2 {

addr2 >= low_addr;

addr2 <= high addr;</pre>

3

constraint addr2_value {

addr2 != addr;

}

function string convert2string();

return $sformatf("%s (addr2=%0d)",

super.convert2string(), addr2);

endfunction

function new(string name = "double transaction");

super.new(name);

endfunction

endclass

class transaction_picker;

static uvm_object_wrapper types[$];

static int number[$];

static function void add(uvm object wrapper w);

types.push_front(w);

endfunction

static function transaction get();

transaction tr;

string name;

uvm_object o;

int d;

d = $urandom_range(types.size()-1, 0);

o = types[d].create_object("transaction_picker");

name = $sformatf("%s%0d", types[d].get_type_name(),

number[d]++);

o.set_name(name);

$cast(tr, o);

return tr;

endfunction

endclass

```

```

11

sequences.svh

sequences.svh

sequences.svh

// ====

_____

class basic sequence extends uvm_sequence#(transaction);

uvm_object_utils(basic_sequence)

transaction tr;

string name;

int maximum transactions;

function new(string name = "basic sequence");

super.new(name);

if (maximum_transactions == 0)

maximum_transactions = 100;

endfunction -

task body();

for (int i = 0; i < maximum_transactions; i++) begin

name = $sformatf("transaction%0d", i);

//tr = transaction::type_id::create(name);</pre>

tr = transaction_picker::get();

start_item(tr);

if (!tr.randomize()) begin

`uvm_info(get_type_name(), "Randomize FAILED",

UVM_MEDIUM)

end

finish item(tr);

end

endtask

endclass

class checker_sequence extends basic_sequence;

`uvm_object_utils(checker_sequence)

reg [7:0] wdata [];

function new(string name = "checker_sequence");

super.new(name);

endfunction

task body();

for (int i = 0; i < maximum_transactions; i++) begin

name = $sformatf("transaction%0d", i);

//tr = transaction::type_id::create(name);</pre>

tr = transaction_picker::get();

// Write

start item(tr);

if (!tr.randomize()) begin

`uvm_info(get_type_name(), "Randomize FAILED",

UVM_MEDIUM)

end

tr.rw = WRITE; // Force WRITE.

finish_item(tr);

wdata = tr.data;

// Read

tr.rw = READ; // Force READ.

start_item(tr);

finish_item(tr);

// Check

if (wdata != tr.data)

(wuta := ':'.uta'a)

'uvm_info(get_type_name(),

$sformatf("Mismatch Wrote %p, Read %p",

wdata, tr.data), UVM_MEDIUM)

end

endtask

endclass

```

```

11

drivers.svh

drivers.svh

11

drivers.svh

// =====

class driver extends uvm driver#(transaction);

`uvm_component_utils(driver)

transaction t;

int d:

int id;

virtual abus bus;

function new(string name = "driver",

uvm_component parent = null);

super.new(name, parent);

endfunction

task bad(transaction t); // Bad behavior

int r;

r = $urandom range(100, 0);

if (r < 5) begin

t.data[0] = -1;

end

endtask

task process_sequence_item(transaction t);

isk process_sequence______

reg [31:0]a;

'uvm_info(get_type_name(),

$sformatf("Got___'%s'", t.convert2string()),

$sformatf("Got___'%s'", t.convert2string()),

$sformatf("Got___'%s'", t.convert2string()),

$sformatf("Sot___'%s'", t.convert2string()),

$sformatf(

d = $urandom_range(100, 50);

#d;

bad(t);

bus.rw = t.rw;

a = t.addr;

if (t.rw == 1) begin : READ

foreach (t.data[i]) begin

bus.addr = a;

bus.valid = 1;

bus.id = id++;

@(posedge bus.clk);

while (bus.ready != 1)

@(posedge bus.clk);

t.data[i] = bus.rdata;

t.id = bus.id;

a = a + 1;

bus.valid = 0;

@(negedge bus.clk);

end

end

else if (t.rw == 0) begin : WRITE

foreach (t.data[i]) begin

bus.addr = a;

bus.wdata = t.data[i];

bus.valid = 1;

bus.id = id++;

t.id = bus.id;

@(posedge bus.clk);

while (bus.ready != 1)

@(posedge bus.clk);

a = a + 1;

bus.valid = 0;

@(negedge bus.clk);

end

end

endtask

task run_phase(uvm_phase phase);

forever begin

seq_item_port.get_next_item(t);

process_sequence_item(t);

uvm_info(get_type_name(),

$sformatf("sending '%s'", t.convert2string()),

UVM_MEDIUM)

seq_item_port.item_done();

end

endtask

```

endclass

```

11

env.svh

env.svh

env.svh

// =====

class env extends uvm env;

`uvm_component_utils(env)

driver d;

uvm_sequencer#(transaction) sqr;

virtual abus bus;

function new(string name = "env",

uvm_component parent = null);

super.new(name, parent);

endfunction

function void build_phase(uvm_phase phase);

d = driver::type_id::create("driver", this);

sqr = new("sqr", this);

endfunction

function void connect_phase(uvm_phase phase);

d.seq_item_port.connect(sqr.seq_item_export);

d.bus = bus;

endfunction

endclass

// =====

tests.svh

11

tests.svh

tests.svh

// ===

class test extends uvm_test;

`uvm_component_utils(test)

env e;

basic_sequence seq;

function new(string name = "test",

uvm_component parent = null);

super.new(name, parent);

endfunction

function void build_phase(uvm_phase phase);

e = env::type_id::create("e", this);

transaction_picker::add( transaction::get_type());

transaction_picker::add(odd_address_transaction::get_type());

transaction_picker::add( big_transaction::get_type());

transaction_picker::add( double_transaction::get_type());

//transaction::type_id::set_type_override(

// od_address_transaction::get_type(),1);

//transaction::type_id::set_type_override(

// big_transaction::get_type(),1);

```

basic\_sequence::type\_id::set\_type\_override(

endmodule

endfunction task run\_phase(uvm\_phase phase); phase.raise\_objection(this); seq = basic\_sequence::type\_id::create("sequence"); seq.start(e.sqr); coq.ccut(cl.quf, phase.drop\_objection(this); `uvm\_info(get\_type\_name(), "...finished", UVM\_MEDIUM) endtask endclass 17 top.sv top.sv 11 top.sv \_\_\_\_\_ import uvm\_pkg::\*; `include "uvm\_macros.svh" import vip\_pkg::\*; module top(); reg clk; reg reset; abus bus(clk, reset); dut DUT (bus); initial begin run\_test("test"); end always begin #10; clk = 0; #10; clk = 1; end initial begin uvm\_config\_db#(virtual abus)::set(

null, "\*", "bus", bus); reset = 0;repeat (10) @(posedge clk); reset = 1; repeat (10) @(posedge clk); reset = 0;repeat (10000) @(posedge clk); \$finish(2); end

checker sequence::get type(),1);