# Vlang

#### **A System Level Verification Perspective**

PuneetGoel <puneet@coverify.com>

#### In this section ...

#### **Runtime Efficiency**

Multi UVM Root

Coverification

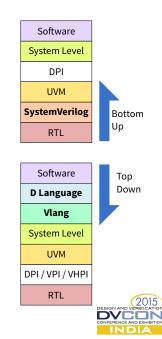

**Top Down Verification**

Modeling

**Open Source**

© Accellera Systems Initiative

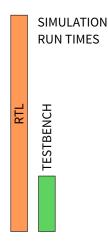

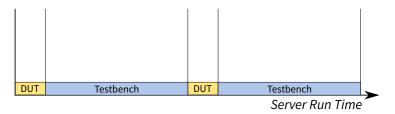

- State-of-the-art HVLs like SystemVerilog were drafted with RTL simulation in mind

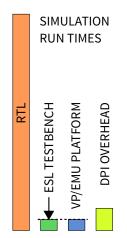

- SV performance becomes a bottleneck when testbenching Emulation/ESL Platforms

- SV DPI overhead adds to testbench performance woes

- Faster by at least an order of magnitude

- ► ABI Compatible with C/C++

- State-of-the-art HVLs like SystemVerilog were drafted with RTL simulation in mind

- SV performance becomes a bottleneck when testbenching Emulation/ESL Platforms

- SV DPI overhead adds to testbench performance woes

- Faster by at least an order of magnitude

- ► ABI Compatible with C/C++

|     |           | SIMULATION<br>RUN TIMES |                 |  |  |  |

|-----|-----------|-------------------------|-----------------|--|--|--|

| RTL | TESTBENCH |                         | VP/EMU PLATFORM |  |  |  |

- State-of-the-art HVLs like SystemVerilog were drafted with RTL simulation in mind

- SV performance becomes a bottleneck when testbenching Emulation/ESL Platforms

- SV DPI overhead adds to testbench performance woes

- Faster by at least an order of magnitude

- ► ABI Compatible with C/C++

|   |     |           | SIMULATION<br>RUN TIMES |              |  |  |  |

|---|-----|-----------|-------------------------|--------------|--|--|--|

| Ĩ | RIL | TESTBENCH | VP/EMU PLATFORM         | DPI OVERHEAD |  |  |  |

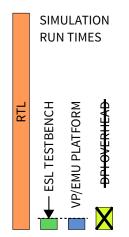

- State-of-the-art HVLs like SystemVerilog were drafted with RTL simulation in mind

- SV performance becomes a bottleneck when testbenching Emulation/ESL Platforms

- SV DPI overhead adds to testbench performance woes

- ESL Testbenches need to be ...

- Faster by at least an order of magnitude

- ► ABI Compatible with C/C++

- State-of-the-art HVLs like SystemVerilog were drafted with RTL simulation in mind

- SV performance becomes a bottleneck when testbenching Emulation/ESL Platforms

- SV DPI overhead adds to testbench performance woes

- Faster by at least an order of magnitude

- ► ABI Compatible with C/C++

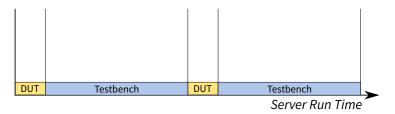

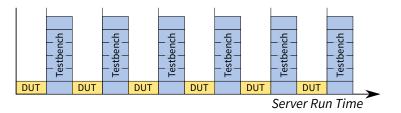

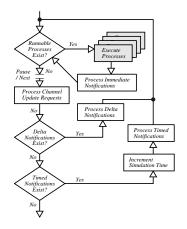

- ► Both SystemVerilog and SystemC (as of now) run on a single OS thread

- SV/SystemC use Cooperative Threading for Fork/Spawn

- Testbench can be made efficient by invoking concurrent threads

- ► And even more efficient by running the testbench in parallel

- ► Both SystemVerilog and SystemC (as of now) run on a single OS thread

- SV/SystemC use Cooperative Threading for Fork/Spawn

- Testbench can be made efficient by invoking concurrent threads

- ► And even more efficient by running the testbench in parallel

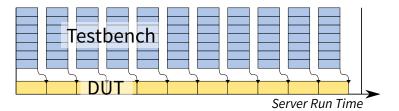

- ► Both SystemVerilog and SystemC (as of now) run on a single OS thread

- ► SV/SystemC use Cooperative Threading for Fork/Spawn

- Testbench can be made efficient by invoking concurrent threads

- ► And even more efficient by running the testbench in parallel

- ► Both SystemVerilog and SystemC (as of now) run on a single OS thread

- ► SV/SystemC use Cooperative Threading for Fork/Spawn

- Testbench can be made efficient by invoking concurrent threads

- And even more efficient by running the testbench in parallel

- It will have minimum 60 and a maximum 72 cores

- Each core will run 4 threads in parallel

- ► With up to 288 threads running in parallel, concurrency in application programs becomes an essential aspect of coding

- ► KNL will also have a minimum 16GB on-chip DRAM

- ► To maximize potential, Go Parallel

- Running multiple simulations on a Multicore Server is the quickest way to hit Memory Wall

- Multicore is here to Stay! Are you Ready!!

- ▶ It will have minimum 60 and a maximum 72 cores

- Each core will run 4 threads in parallel

- With up to 288 threads running in parallel, concurrency in application programs becomes an essential aspect of coding

- ► KNL will also have a minimum 16GB on-chip DRAM

- ► To maximize potential, Go Parallel

- Running multiple simulations on a Multicore Server is the quickest way to hit Memory Wall

- Multicore is here to Stay! Are you Ready!!

- ▶ It will have minimum 60 and a maximum 72 cores

- Each core will run 4 threads in parallel

- With up to 288 threads running in parallel, concurrency in application programs becomes an essential aspect of coding

- ► KNL will also have a minimum 16GB on-chip DRAM

- ► To maximize potential, Go Parallel

- Running multiple simulations on a Multicore Server is the quickest way to hit Memory Wall

- Multicore is here to Stay! Are you Ready!!

- ▶ It will have minimum 60 and a maximum 72 cores

- Each core will run 4 threads in parallel

- ► With up to 288 threads running in parallel, concurrency in application programs becomes an essential aspect of coding

- KNL will also have a minimum 16GB on-chip DRAM

- ► To maximize potential, Go Parallel

- Running multiple simulations on a Multicore Server is the quickest way to hit Memory Wall

- Multicore is here to Stay! Are you Ready!!

- ▶ It will have minimum 60 and a maximum 72 cores

- Each core will run 4 threads in parallel

- ► With up to 288 threads running in parallel, concurrency in application programs becomes an essential aspect of coding

- ► KNL will also have a minimum 16GB on-chip DRAM

- ► To maximize potential, Go Parallel

- Running multiple simulations on a Multicore Server is the quickest way to hit Memory Wall

- Multicore is here to Stay! Are you Ready!!

- ▶ It will have minimum 60 and a maximum 72 cores

- Each core will run 4 threads in parallel

- ► With up to 288 threads running in parallel, concurrency in application programs becomes an essential aspect of coding

- ► KNL will also have a minimum 16GB on-chip DRAM

- ► To maximize potential, Go Parallel

- Running multiple simulations on a Multicore Server is the quickest way to hit Memory Wall

- Multicore is here to Stay! Are you Ready!!

- ▶ It will have minimum 60 and a maximum 72 cores

- Each core will run 4 threads in parallel

- ► With up to 288 threads running in parallel, concurrency in application programs becomes an essential aspect of coding

- ► KNL will also have a minimum 16GB on-chip DRAM

- ► To maximize potential, Go Parallel

- Running multiple simulations on a Multicore Server is the quickest way to hit Memory Wall

- Multicore is here to Stay! Are you Ready!!

## Vlang is Multi-Core Enabled

- Vlang Simulator comes fitted with a Multicore Task Scheduler

- Customizing Multicore Parallelism in Vlang is easy

## Vlang is Multi-Core Enabled

- Vlang Simulator comes fitted with a Multicore Task Scheduler

- Customizing Multicore

Parallelism in Vlang is easy

```

class TestBench: RootEntity {

uvm_root_entity!(apb_root) tb;

this(string name) {

super(name);

}

}

int main() {

TestBench test =

new TestBench("test");

test.multiCore(4, 0);

test.elaborate();

test.simulate();

return 0;

}

```

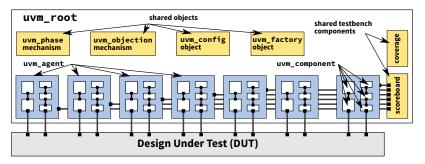

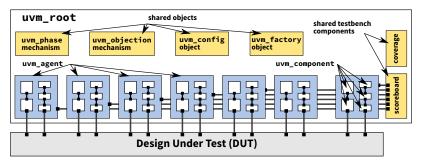

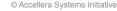

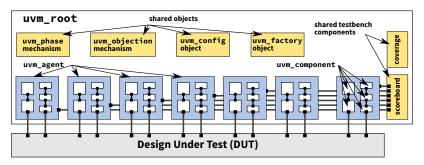

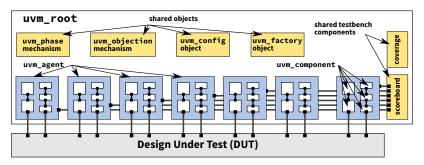

- Most System Level Designs have multiple (TLM) Interfaces

- ► Each (TLM) Interface requires a VIP (or a uvm\_agent)

- Most VPIs have no interaction with other VIPs

- ► This provides the right opportunity for parallelism

- ► Vlang UVM implementation runs uvm\_agent threads parallelly

DESIGN AND

- ► Most System Level Designs have multiple (TLM) Interfaces

- Each (TLM) Interface requires a VIP (or a uvm\_agent)

- Most VPIs have no interaction with other VIPs

- This provides the right opportunity for parallelism

- Vlang UVM implementation runs uvm\_agent threads parallelly

DESIGN AND

- ► Most System Level Designs have multiple (TLM) Interfaces

- ► Each (TLM) Interface requires a VIP (or a uvm\_agent)

- Most VPIs have no interaction with other VIPs

- ► This provides the right opportunity for parallelism

- ► Vlang UVM implementation runs uvm\_agent threads parallelly

DESIGN AND

- ► Most System Level Designs have multiple (TLM) Interfaces

- ► Each (TLM) Interface requires a VIP (or a uvm\_agent)

- Most VPIs have no interaction with other VIPs

- This provides the right opportunity for parallelism

- ► Vlang UVM implementation runs uvm\_agent threads parallelly

DESIGN AND

- ► Most System Level Designs have multiple (TLM) Interfaces

- ► Each (TLM) Interface requires a VIP (or a uvm\_agent)

- Most VPIs have no interaction with other VIPs

- ► This provides the right opportunity for parallelism

- Vlang UVM implementation runs uvm\_agent threads parallelly

DESIGN AND

### In this section ...

**Runtime Efficiency**

#### Multi UVM Root

Coverification

**Top Down Verification**

Modeling

**Open Source**

© Accellera Systems Initiative

- To conserve power many modules are switched off when inactive

- When the module is activated, it gets reset and driver is loaded

- UVM implementation provides singleton phases, not good enough for System Level Verification

- Hot plugin is another use case where singleton phasing becomes a bottleneck

- Vlang allows multiple UVM Root instances to overcome this limitation

```

class TestBench: RootEntity {

uvm_root_entity!(sys1) tb1;

uvm_root_entity!(sys2) tb2;

uvm_root_entity!(sys3) tb3;

uvm_root_entity!(sys4) tb4;

this(string name) {

super(name);

}

int main() {

TestBench test =

new TestBench("test");

test.multiCore(4, 0);

test.elaborate();

test.simulate();

return 0;

```

- To conserve power many modules are switched off when inactive

- When the module is activated, it gets reset and driver is loaded

- UVM implementation provides singleton phases, not good enough for System Level Verification

- Hot plugin is another use case where singleton phasing becomes a bottleneck

- Vlang allows multiple UVM Root instances to overcome this limitation

```

class TestBench: RootEntity {

uvm_root_entity!(sys1) tb1;

uvm_root_entity!(sys2) tb2;

uvm_root_entity!(sys3) tb3;

uvm_root_entity!(sys4) tb4;

this(string name) {

super(name);

}

int main() {

TestBench test =

new TestBench("test");

test.multiCore(4, 0);

test.elaborate();

test.simulate();

return 0;

```

- To conserve power many modules are switched off when inactive

- When the module is activated, it gets reset and driver is loaded

- UVM implementation provides singleton phases, not good enough for System Level Verification

- Hot plugin is another use case where singleton phasing becomes a bottleneck

- Vlang allows multiple UVM Root instances to overcome this limitation

```

class TestBench: RootEntity {

uvm_root_entity!(sys1) tb1;

uvm_root_entity!(sys2) tb2;

uvm_root_entity!(sys3) tb3;

uvm_root_entity!(sys4) tb4;

this(string name) {

super(name);

}

int main() {

TestBench test =

new TestBench("test");

test.multiCore(4, 0);

test.elaborate();

test.simulate();

return 0;

```

- To conserve power many modules are switched off when inactive

- When the module is activated, it gets reset and driver is loaded

- UVM implementation provides singleton phases, not good enough for System Level Verification

- Hot plugin is another use case where singleton phasing becomes a bottleneck

- Vlang allows multiple UVM Root instances to overcome this limitation

```

class TestBench: RootEntity {

uvm_root_entity!(sys1) tb1;

uvm_root_entity!(sys2) tb2;

uvm_root_entity!(sys3) tb3;

uvm_root_entity!(sys4) tb4;

this(string name) {

super(name);

}

int main() {

TestBench test =

new TestBench("test");

test.multiCore(4, 0);

test.elaborate();

test.simulate();

return 0;

```

- To conserve power many modules are switched off when inactive

- When the module is activated, it gets reset and driver is loaded

- UVM implementation provides singleton phases, not good enough for System Level Verification

- Hot plugin is another use case where singleton phasing becomes a bottleneck

- Vlang allows multiple UVM Root instances to overcome this limitation

```

class TestBench: RootEntity {

uvm_root_entity!(sys1) tb1;

uvm_root_entity!(sys2) tb2;

uvm_root_entity!(sys3) tb3;

uvm_root_entity!(sys4) tb4;

this(string name) {

super(name);

}

int main() {

TestBench test =

new TestBench("test");

test.multiCore(4, 0);

test.elaborate();

test.simulate();

return 0;

```

#### In this section ...

**Runtime Efficiency**

Multi UVM Root

#### Coverification

**Top Down Verification**

Modeling

**Open Source**

© Accellera Systems Initiative

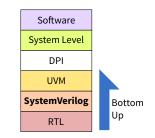

#### **Hardware Software Coverification**

- First Level user of an SoC is a Software Programmer

- HVLs are built on top of RTL Software interaction is Week

- Vlang is built on top of D Programming Language, A Systems Programming Laguage

© Accellera Systems Initiative

## **Hardware Software Coverification**

- First Level user of an SoC is a Software Programmer

- HVLs are built on top of RTL Software interaction is Week

- Vlang is built on top of D Programming Language, A Systems Programming Laguage

## **Hardware Software Coverification**

- First Level user of an SoC is a Software Programmer

- HVLs are built on top of RTL Software interaction is Week

- Vlang is built on top of D Programming Language, A Systems Programming Laguage

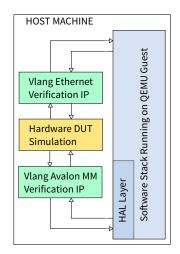

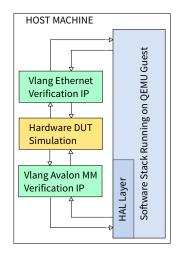

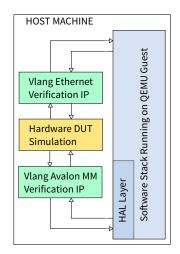

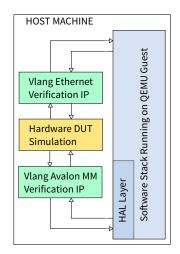

## A Quick Coverification Use Case

- QEMU is fast becoming the platform of choice for embedded software development and test

- A convenient way to exchange data with QEMU is via shared file descriptors

- Vlang VIP can directly tap a file descriptor and feed the transaction to simulation

- Data coming out of DUT is reverse fed into QEMU

#### A Quick Coverification Use Case

- QEMU is fast becoming the platform of choice for embedded software development and test

- A convenient way to exchange data with QEMU is via shared file descriptors

- Vlang VIP can directly tap a file descriptor and feed the transaction to simulation

- Data coming out of DUT is reverse fed into QEMU

#### A Quick Coverification Use Case

- QEMU is fast becoming the platform of choice for embedded software development and test

- A convenient way to exchange data with QEMU is via shared file descriptors

- Vlang VIP can directly tap a file descriptor and feed the transaction to simulation

- Data coming out of DUT is reverse fed into QEMU

#### A Quick Coverification Use Case

- QEMU is fast becoming the platform of choice for embedded software development and test

- A convenient way to exchange data with QEMU is via shared file descriptors

- Vlang VIP can directly tap a file descriptor and feed the transaction to simulation

- Data coming out of DUT is reverse fed into QEMU

#### In this section ...

**Runtime Efficiency**

Multi UVM Root

Coverification

#### **Top Down Verification**

Modeling

**Open Source**

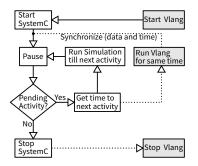

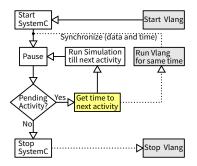

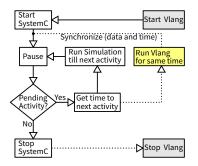

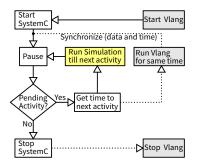

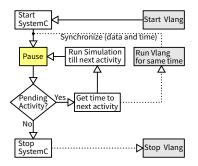

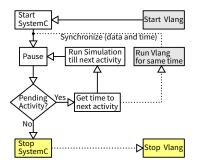

- Vlang simulator can be fully synchronized with SystemC and SystemVerilog

- With Systemc, Vlang can lock at delta cycle level

```

int main(int argc, char* argv[]) {

initEsdl():

// initialize vlana

int scresult =

sc_core::sc_elab_and_sim(argc, argv);

finalizeEsdl(): // stop vlana

return 0;

int sc_main( int argc, char* argv[]) {

sc set time resolution(1, SC PS);

top = new SYSTEM("top"):

sc start( SC ZERO TIME );

while(sc_pending_activity()) {

sc_core::sc_time time_ =

sc_time_to_pending_activity();

// start vlang simulation for given t

esdlStartSimFor(time_.value());

sc start(time );

// wait for vlana to complete time sto

esdlWait();

return 0:

```

- Vlang simulator can be fully synchronized with SystemC and SystemVerilog

- With Systemc, Vlang can lock at delta cycle level

```

int main(int argc, char* argv[]) {

initEsdl();

// initialize vlang

int scresult =

sc_core::sc_elab_and_sim(argc, argv);

finalizeEsdl(): // stop vlana

return 0;

int sc_main( int argc, char* argv[]) {

sc set time resolution(1, SC PS);

top = new SYSTEM("top"):

sc start( SC ZERO TIME );

while(sc_pending_activity()) {

sc_core::sc_time time_ =

sc_time_to_pending_activity();

// start vlang simulation for given t

esdlStartSimFor(time_.value());

sc start(time );

// wait for vlana to complete time sto

esdlWait();

return 0:

```

DESIGN AND VE

- Vlang simulator can be fully synchronized with SystemC and SystemVerilog

- With Systemc, Vlang can lock at delta cycle level

```

int main(int argc, char* argv[]) {

initEsdl():

// initialize vlana

int scresult =

sc_core::sc_elab_and_sim(argc, argv);

finalizeEsdl(): // stop vlana

return 0;

int sc_main( int argc, char* argv[]) {

sc_set_time_resolution(1, SC_PS);

top = new SYSTEM("top"):

sc_start( SC_ZERO_TIME );

while(sc_pending_activity()) {

sc_core::sc_time time_ =

sc_time_to_pending_activity();

// start vlang simulation for given t

esdlStartSimFor(time_.value());

sc start(time );

// wait for vlana to complete time sto

esdlWait();

return 0:

```

- Vlang simulator can be fully synchronized with SystemC and SystemVerilog

- With Systemc, Vlang can lock at delta cycle level

```

int main(int argc, char* argv[]) {

initEsdl():

// initialize vlana

int scresult =

sc_core::sc_elab_and_sim(argc, argv);

finalizeEsdl(): // stop vlana

return 0;

int sc_main( int argc, char* argv[]) {

sc_set_time_resolution(1, SC_PS);

top = new SYSTEM("top"):

sc start( SC ZERO TIME );

while(sc_pending_activity()) {

sc_core::sc_time time_ =

sc_time_to_pending_activity();

// start vlang simulation for given t

esdlStartSimFor(time_.value());

sc start(time );

// wait for vlana to complete time sto

esdlWait();

return 0:

```

- Vlang simulator can be fully synchronized with SystemC and SystemVerilog

- With Systemc, Vlang can lock at delta cycle level

```

int main(int argc, char* argv[]) {

initEsdl():

// initialize vlana

int scresult =

sc_core::sc_elab_and_sim(argc, argv);

finalizeEsdl(): // stop vlana

return 0;

int sc_main( int argc, char* argv[]) {

sc set time resolution(1, SC PS);

top = new SYSTEM("top"):

sc start( SC ZERO TIME );

while(sc_pending_activity()) {

sc_core::sc_time time_ =

sc_time_to_pending_activity();

// start vlang simulation for given t

esdlStartSimFor(time .value());

sc start(time );

// wait for vlana to complete time sto

esdlWait();

return 0:

```

- Vlang simulator can be fully synchronized with SystemC and SystemVerilog

- With Systemc, Vlang can lock at delta cycle level

```

int main(int argc, char* argv[]) {

initEsdl():

// initialize vlana

int scresult =

sc_core::sc_elab_and_sim(argc, argv);

finalizeEsdl(): // stop vlana

return 0;

int sc_main( int argc, char* argv[]) {

sc set time resolution(1, SC PS);

top = new SYSTEM("top"):

sc start( SC ZERO TIME );

while(sc_pending_activity()) {

sc_core::sc_time time_ =

sc_time_to_pending_activity();

// start vlang simulation for given t

esdlStartSimFor(time_.value());

sc start(time );

// wait for vlang to complete time sto

esdlWait();

return 0:

```

- Vlang simulator can be fully synchronized with SystemC and SystemVerilog

- With Systemc, Vlang can lock at delta cycle level

```

int main(int argc, char* argv[]) {

initEsdl():

// initialize vlana

int scresult =

sc_core::sc_elab_and_sim(argc, argv);

finalizeEsdl(): // stop vlana

return 0;

int sc_main( int argc, char* argv[]) {

sc set time resolution(1, SC PS);

top = new SYSTEM("top"):

sc start( SC ZERO TIME );

while(sc_pending_activity()) {

sc_core::sc_time time_ =

sc_time_to_pending_activity();

// start vlang simulation for given t

esdlStartSimFor(time_.value());

sc start(time );

// wait for vlana to complete time sto

esdlWait();

return 0:

DESIGN AND VE

```

- Vlang simulator can be fully synchronized with SystemC and SystemVerilog

- With Systemc, Vlang can lock at delta cycle level

```

int main(int argc, char* argv[]) {

initEsdl():

// initialize vlana

int scresult =

sc_core::sc_elab_and_sim(argc, argv);

finalizeEsdl(); // stop vlang

return 0;

int sc_main( int argc, char* argv[]) {

sc set time resolution(1, SC PS);

top = new SYSTEM("top"):

sc start( SC ZERO TIME );

while(sc_pending_activity()) {

sc_core::sc_time time_ =

sc_time_to_pending_activity();

// start vlang simulation for given t

esdlStartSimFor(time_.value());

sc start(time );

// wait for vlana to complete time sto

esdlWait();

return 0:

```

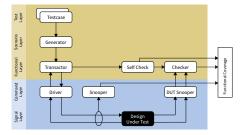

- The idea is to implement the BFM along with the design and pass the transaction to the BFM from Vlang

- Vlang implements special TLM channels for interfacing with external simulators

- Each Vlang UVM agent communicates independently with SV/SystemC blocking only when the transaction

FIFO channel is full/empty

- SystemVerilog BFM pulls transactions from the channel using DPI-C interface

- The idea is to implement the BFM along with the design and pass the transaction to the BFM from Vlang

- Vlang implements special TLM channels for interfacing with external simulators

- Each Vlang UVM agent communicates independently with SV/SystemC blocking only when the transaction

FIFO channel is full/empty

- SystemVerilog BFM pulls transactions from the channel using DPI-C interface

```

class my_root: uvm_root {

mixin uvm component utils;

env my env;

uvm_tlm_fifo_egress!bus_req fifo;

uvm_get_port!bus_req data_in;

override void initial() {

fifo = new

uvm_tlm_fifo_egress!bus_req("fifo",null

run_test();

override void connect_phase(uvm_phase phase

my_env.drv.data_out.connect(fifo.put_expo

data_in.connect(fifo.get_export);

}

uvm root entity!my root root;

extern(C) void dpi_pull_reg(int* addr,int* da

bus_req req;

root.data_in.get(req);

// get the addr and data from transaction

void main() {

root = uvm_fork!(my_root, "test")(0);

root.get_uvm_root.wait_for_end_of_elaboration

root.join();

```

- The idea is to implement the BFM along with the design and pass the transaction to the BFM from Vlang

- Vlang implements special TLM channels for interfacing with external simulators

- Each Vlang UVM agent communicates independently with SV/SystemC blocking only when the transaction

FIFO channel is full/empty

- SystemVerilog BFM pulls transactions from the channel using DPI-C interface

```

class my_root: uvm_root {

mixin uvm_component_utils;

env my env;

uvm_tlm_fifo_egress!bus_req fifo;

uvm_get_port!bus_req data_in;

override void initial() {

fifo = new

uvm_tlm_fifo_egress!bus_req("fifo",null

run_test();

}

override void connect_phase(uvm_phase phase

my_env.drv.data_out.connect(fifo.put_expo

data_in.connect(fifo.get_export);

}

uvm root entity!my root root;

extern(C) void dpi_pull_reg(int* addr,int* da

bus_req req;

root.data_in.get(req);

// get the addr and data from transaction

void main() {

root = uvm_fork!(my_root, "test")(0);

root.get_uvm_root.wait_for_end_of_elaboration

root.join();

```

- The idea is to implement the BFM along with the design and pass the transaction to the BFM from Vlang

- Vlang implements special TLM channels for interfacing with external simulators

- Each Vlang UVM agent communicates independently with SV/SystemC blocking only when the transaction

FIFO channel is full/empty

- SystemVerilog BFM pulls transactions from the channel using DPI-C interface

```

class my_root: uvm_root {

mixin uvm_component_utils;

env my env;

uvm_tlm_fifo_egress!bus_req fifo;

uvm_get_port!bus_req data_in;

override void initial() {

fifo = new

uvm_tlm_fifo_egress!bus_req("fifo",null

run_test();

override void connect_phase(uvm_phase phase

my_env.drv.data_out.connect(fifo.put_expo

data_in.connect(fifo.get_export);

}

uvm_root_entity!my_root root;

extern(C) void dpi_pull_reg(int* addr,int* da

bus_req req;

root.data_in.get(req);

// get the addr and data from transaction

void main() {

```

```

root = uvm_fork!(my_root, "test")(0);

root.get_uvm_root.wait_for_end_of_elaboration

root.join();

```

#### In this section ...

**Runtime Efficiency**

Multi UVM Root

Coverification

**Top Down Verification**

#### Modeling

**Open Source**

- How do you code an Array of Associative Arrays in C++?

- Here is how you do it in D

```

#include <vector>

#include <map>

#include <string>

void foo () {

std::vector

<std::map

<std::string, int> > myVect;

std::map<std::string,int> entry1;

std::map<std::string,int> entry2;

entry1["ABC"] = 1;

entry1["DEF"] = 2;

myVect.push_back(entry1);

entry2["ABC"] = 5;

entry2["RKD"] = 9;

mvVect.push back(entrv2):

```

. . .

- How do you code an Array of Associative Arrays in C++?

- Here is how you do it in D

```

void foo() {

int[string][] myVect =

[["ABC": 1, "DEF": 2],

["ABC": 5, "RKD": 9]];

}

```

. . .

- It is way too cumbersome to extend C++

- The result is RAW Macro based code, SC\_MODULE like

- CRAVE is a modern Constrained Randomization Library in C++

- No User Defined Attributes, No Reflections in C++, and Virtually no CTFE

- CRAVE uses wrapper templates to create Random Variables

- A Random Integer in Crave takes > 50 bytes!!

- Vlang has support for multi-dimensional array randomization and much more

- It is way too cumbersome to extend C++

- The result is RAW Macro based code, SC\_MODULE like

- CRAVE is a modern Constrained Randomization Library in C++

- No User Defined Attributes, No Reflections in C++, and Virtually no CTFE

- CRAVE uses wrapper templates to create Random Variables

- A Random Integer in Crave takes > 50 bytes!!

- Vlang has support for multi-dimensional array randomization and much more

- It is way too cumbersome to extend C++

- The result is RAW Macro based code, SC\_MODULE like

- CRAVE is a modern Constrained Randomization Library in C++

- No User Defined Attributes, No Reflections in C++, and Virtually no CTFE

- CRAVE uses wrapper templates to create Random Variables

- A Random Integer in Crave takes > 50 bytes!!

- Vlang has support for multi-dimensional array randomization and much more

```

struct packet2 : public packet {

rand<int> foo;

rand_vec<unsigned int> bar;

```

}

};

- It is way too cumbersome to extend C++

- The result is RAW Macro based code, SC\_MODULE like

- CRAVE is a modern Constrained Randomization Library in C++

- No User Defined Attributes, No Reflections in C++, and Virtually no CTFE

- CRAVE uses wrapper templates to create Random Variables

- A Random Integer in Crave takes > 50 bytes!!

- Vlang has support for multi-dimensional array randomization and much more

#### On Choosing the right Verification Language

© Accellera Systems Initiative

One way to achieve high confidence is for verification engineers to transform specifications into an implementation model in a language different from the design language. This language is called verification language...– Hardware Design Verification, William K. Lams

#### In this section ...

**Runtime Efficiency**

Multi UVM Root

Coverification

**Top Down Verification**

Modeling

**Open Source**

#### Fork me on Github

Being Open Source is an essential element of system Level...

Too many flows and methodologies require flexibility that only open source can provide

Home Page Repository (Vlang) Repository (Vlang UVM) Compiler License (Vlang) Lincese (Vlang UVM) Maintainer

```

http://vlang.org

https://github.com/coverify/vlang

https://github.com/coverify/vlang-uvm

DMD Version 2.068 (available at http://dlang.org)

Boost Software License, Version 1.0

Apache 2.0 License

Puneet Goel < puneet@coverify.com>

```

# **Questions?**