CONFERENCE AND EXHIBITION

EUROPE

MUNICH, GERMANY DECEMBER 6 - 7, 2022

### Verification of High-Speed Links through IBIS-AMI Models

Ganesh Rathinavel, Sr. Application Engineer – AMS/SI

### Outline

- Introduction to high-speed links

- System-Level modeling workflow

- Performance verification

- Statistical Domain

- Time-Domain

- Generation of IBIS-AMI

- Regression checks

- Channel Pre-layout and Post-layout

- Compliance Checking

- Summary

### Introduction to High-Speed Links

- High speed digital links or wired links are ubiquitous

- Wide variation of speed and applications, operating conditions

- Limited ports requiring multiplexing at high-speeds

- Growing demand of higher data rate and throughput

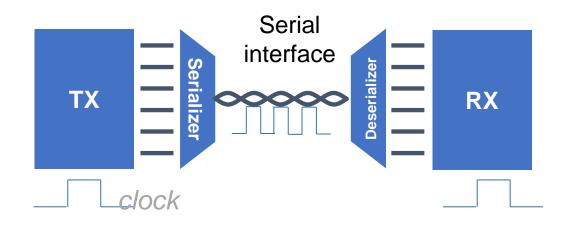

### SerDes

- Serializer Deserializer

- Send Data and Clock

- Constant increase in speed (~100Gbps)

- Special case of Mixed-Signal (DSP+RF)

- Evaluating Equalization techniques

- Example

- Ethernet

- Universal Serial BUS

- DDR (with CDR)

- PCI

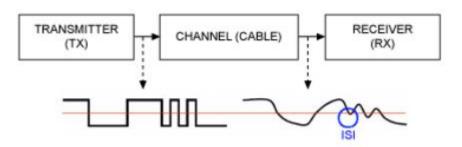

### Typical SerDes system: TX, RX and channel

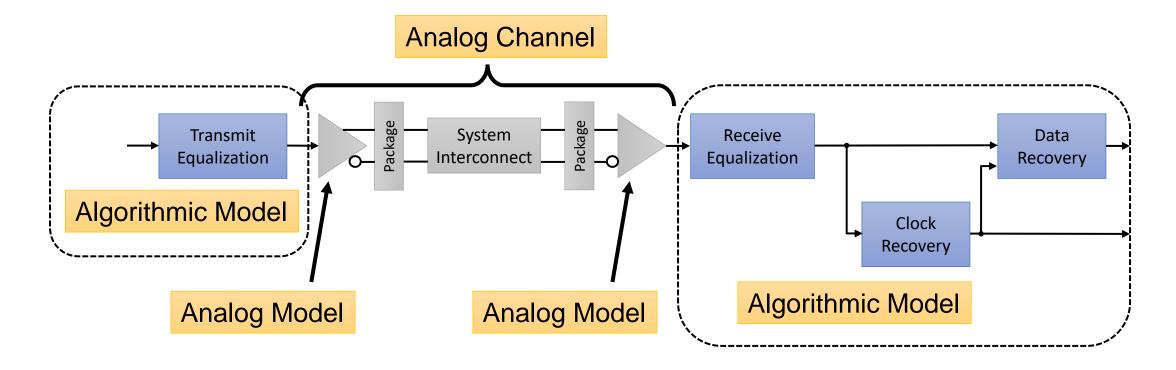

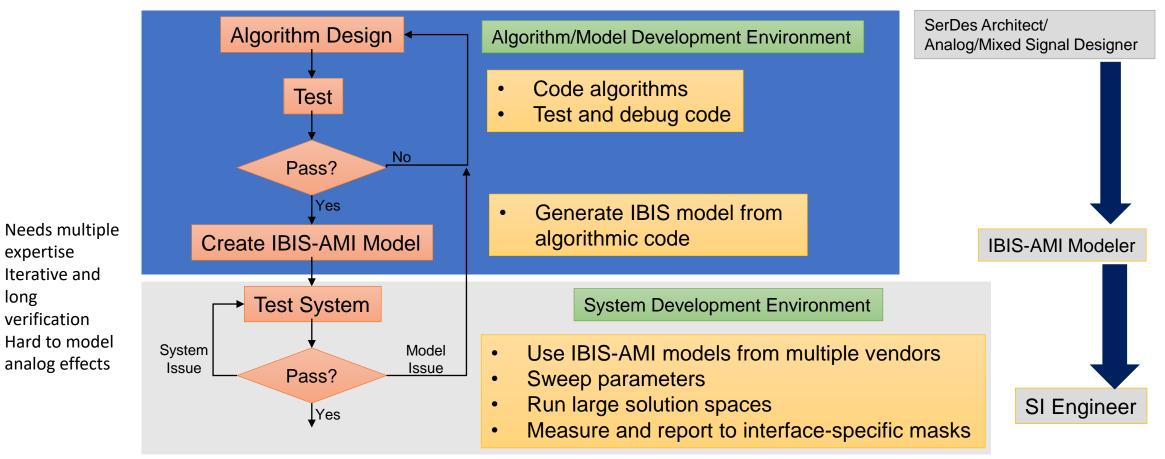

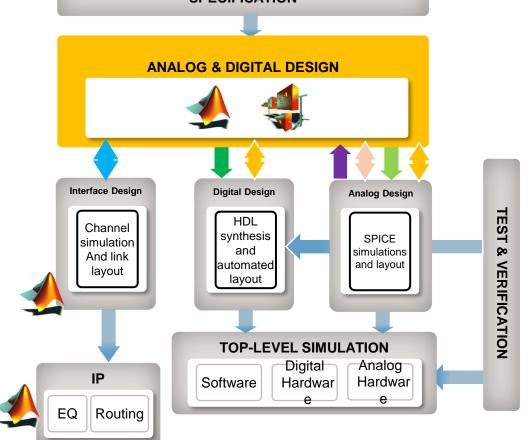

### Typical workflow

SYSTEMS INITIATIVE

long

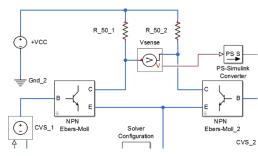

# Mixed-Signal Design with MATLAB and Simulink

### Modeling Approaches

#### **Algorithms**

#### **Behavioral Models**

#### **Physical Network**

#### **Control Logic**

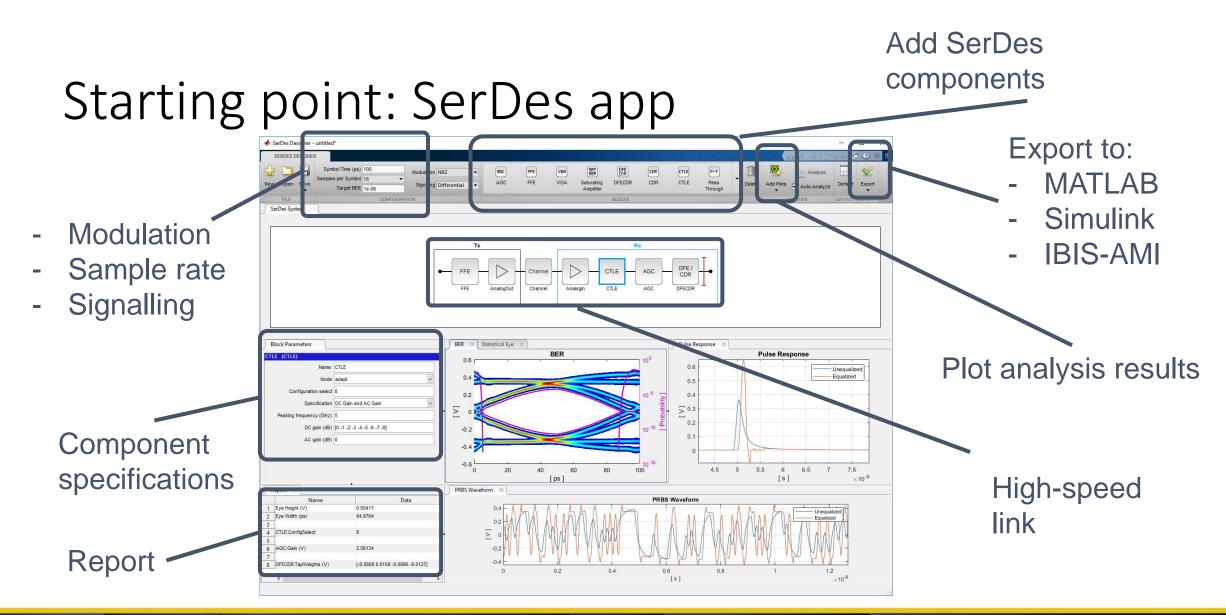

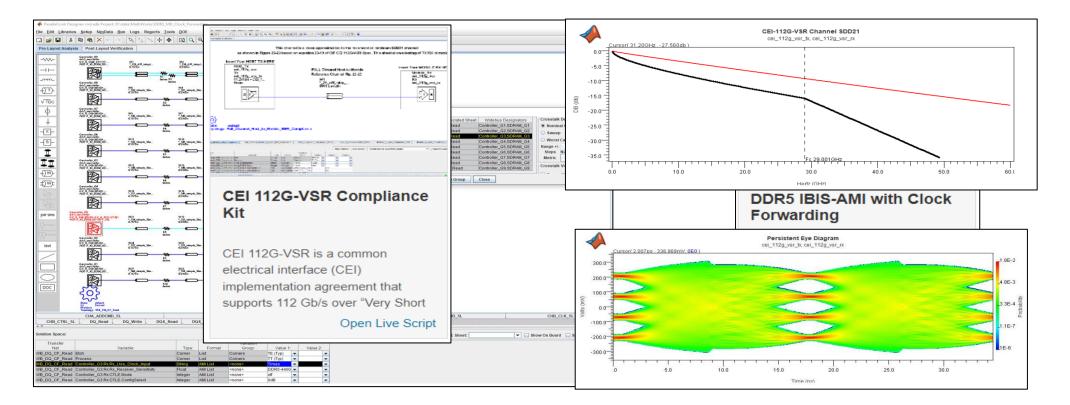

### System-level modeling workflow

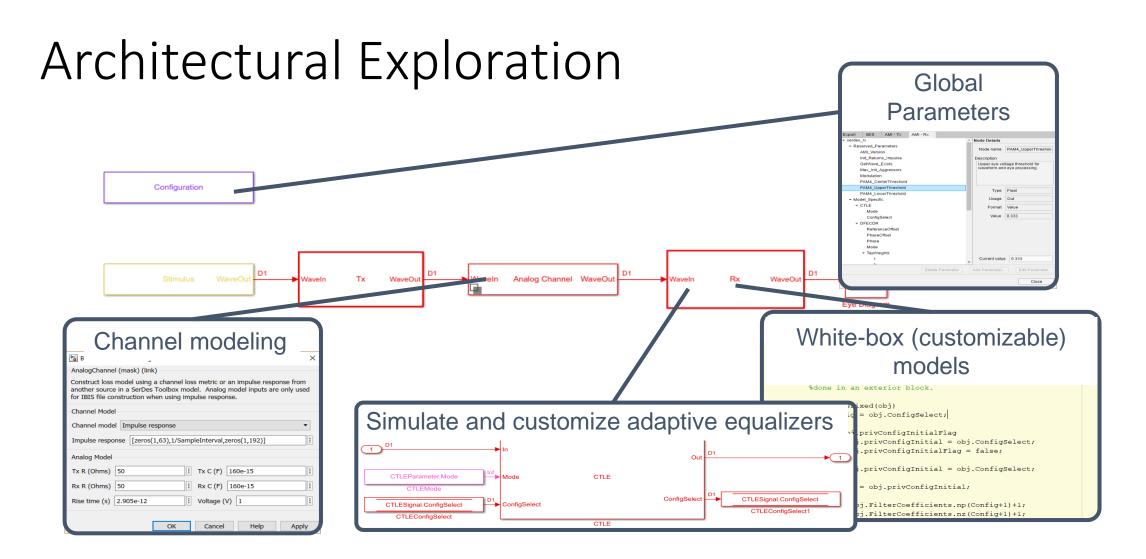

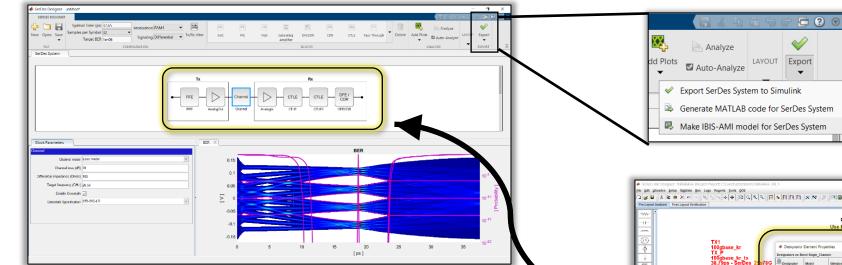

- Design and analyze transmitters and receivers with the SerDes Designer app

- Develop equalization algorithms with MATLAB System objects and Simulink blocks

- FFE, DFE, AGC, CDR, CTLE, etc...

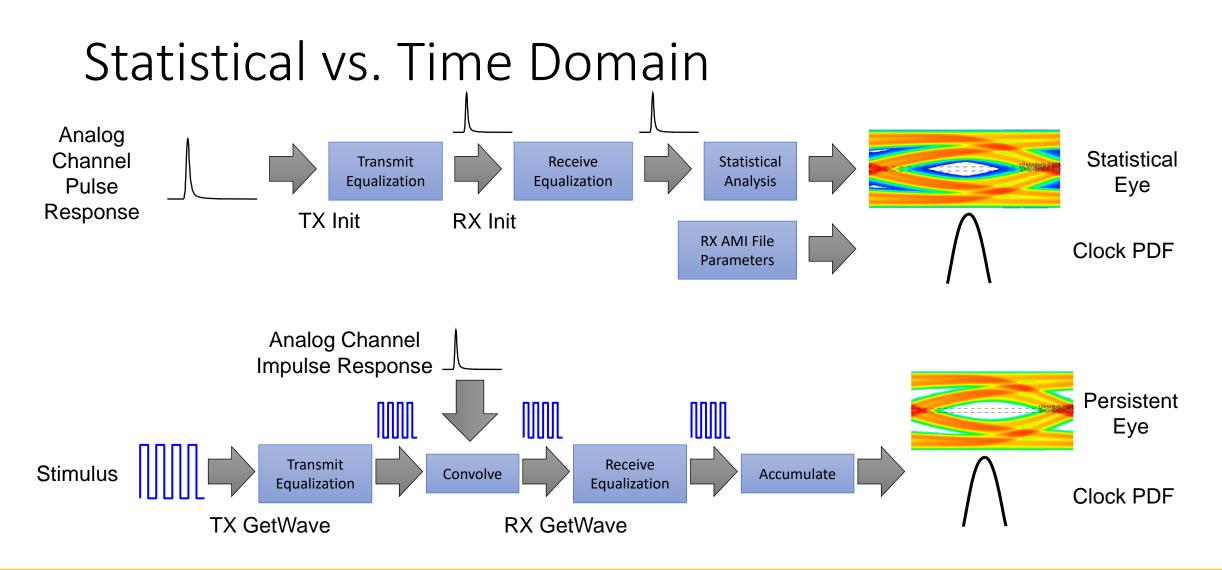

- Perform SerDes statistical analysis and timedomain simulation

- Generate **dual IBIS-AMI models** for 3rd party channel simulators

- Use reference designs for high-speed links such as Ethernet CEI-56G, DDR5, PCI-Gen4

| 📣 SerDes Designer - untitled | *                  |                       |             |                                                                                                                 |                                   |        |            |          |                        | 3. <del>_</del> 33 | đ                | X  |

|------------------------------|--------------------|-----------------------|-------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------|--------|------------|----------|------------------------|--------------------|------------------|----|

| SERDES DESIGNER              |                    |                       |             |                                                                                                                 |                                   |        |            |          |                        | 96                 | 5 ? 0            | 0  |

| New Open Save                | es per Symbol 16 👻 | naling Differential 👻 | RGC FFI     | Contraction of the second s | Saturating<br>Amplifier<br>BLOCKS | DFECDR | CDR<br>CDR | - Delete | Add Plots<br>Add Plots | Default            | Export<br>EXPORT | PI |

| SerDes System                |                    |                       |             |                                                                                                                 |                                   |        |            |          |                        |                    |                  |    |

|                              |                    | -                     | FFE AnalogO | Dut Channel                                                                                                     |                                   | -      |            |          |                        |                    |                  |    |

| Block Parameters             |                    | Plots                 |             |                                                                                                                 |                                   |        |            |          |                        |                    |                  |    |

| AnalogIn<br>R (Ohms<br>C (pF |                    |                       |             |                                                                                                                 |                                   |        |            |          |                        |                    |                  |    |

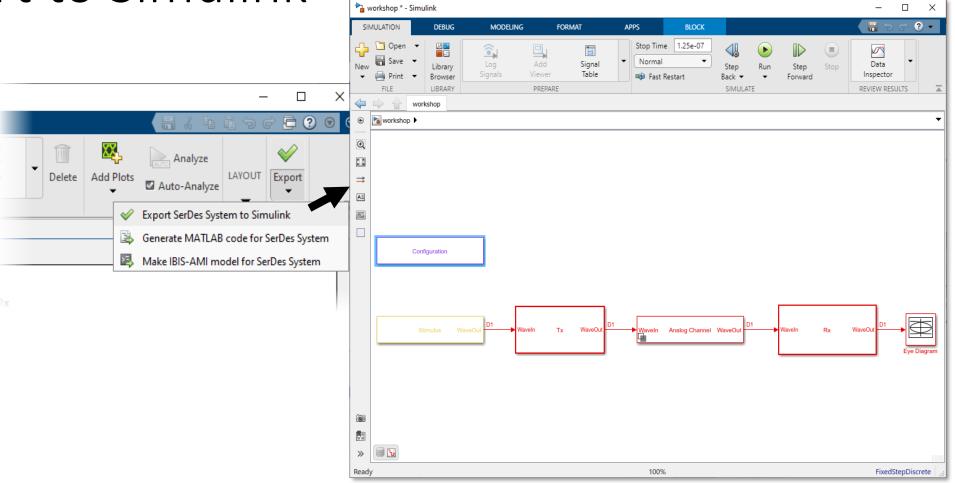

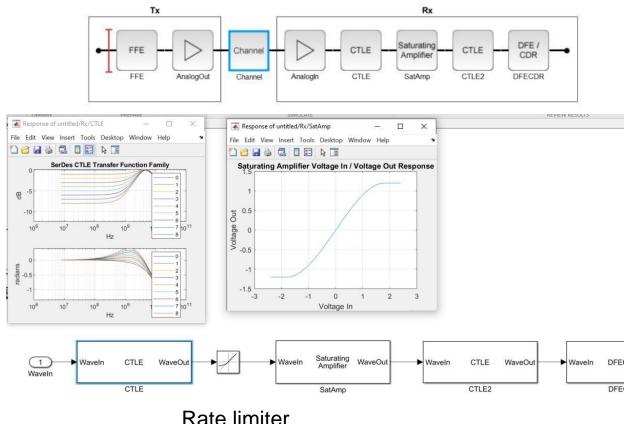

### Export to Simulink

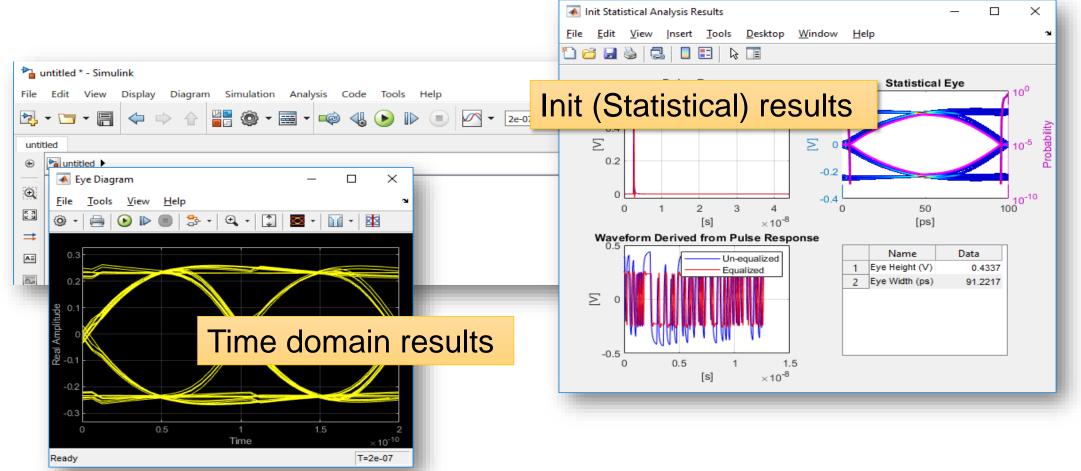

### Performance verification

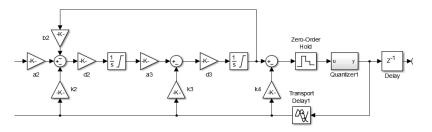

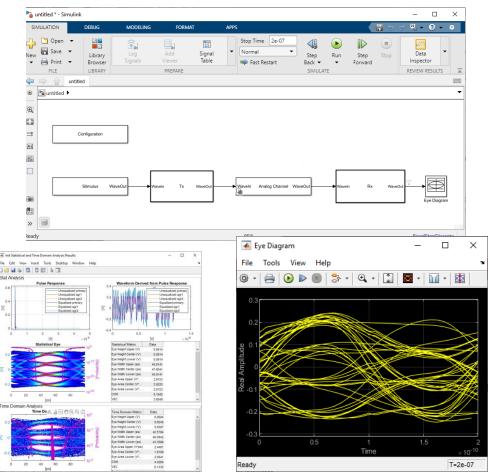

- Export to Simulink models for time-domain simulation

- Model non-linear effects such as saturation

- Customize blocks and equalization algorithms

- Enable global adaptation, and back-channel optimization

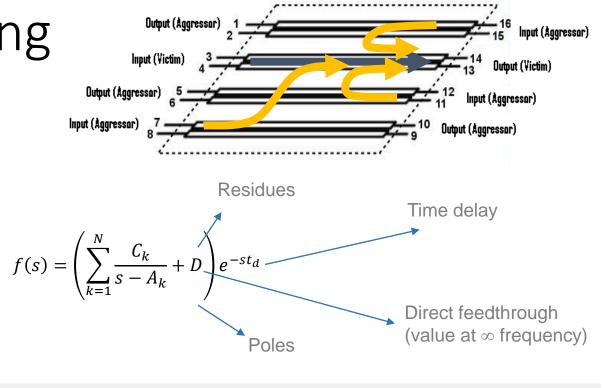

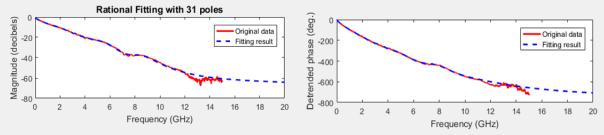

### Channel & CTLE Modeling

- Manipulate frequency data to extract the desired information

- Convert single ended **S-parameters**, select port-pair configuration

- Analyze impedance, attenuation, phase delay

- Use rational fitting for time-domain simulation

- Analyze and enforce passivity

- Causal by construction

- No overfitting of noise

SYSTEMS INITIATIVE

• Analyze impulse response, poles and zeros

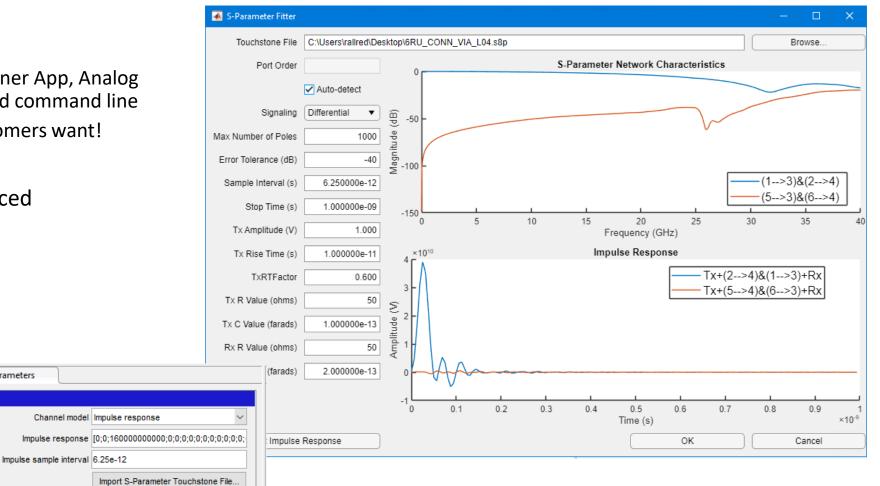

### S-Parameter Import

- S-Parameter Fitter App

- Accessible from SerDes Designer App, Analog Channel block in Simulink, and command line

Block Parameters

Channel

- Push button experience customers want!

- S-Parameter Fitter Class enhanced

- Signal-Ended support (DDR5)

- Crosstalk support

Construct loss model using a channel loss metric or an impulse response from another source in a SerDes Toolbox model. Analog model inputs are only used for

Plot Channel Responses Import S-Parameter Touchstone File...

OK Cancel

Help Apply

Tx C (F) 100e-15

Rx C (F) 200e-15

Voltage (V) 1

😼 Block Parameters: Analog Channel

IBIS file construction when using impulse response Channel Model Crosstalk

Channel model Impulse response 🔻

Impulse sample interval 6.25e-12

Analog Model

Tx R (Ohms) 50

Rx R (Ohms) 50

SYSTEMS INITIATIVE

Rise time (s) 10e-12

AnalogChannel (mask) (link)

### Improved accuracy with bottom-up modeling

- Import Data

- Preprocess Data

- Fit Data

- Visualize Data & Fit

- Integrated with

- SerDes Designer App

- CTLE Blocks

| CTLE Fitter App Import CTLE frequency response from Base workspace                                                                           | Base Workspace variables data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol Time (ps)     100     Samples per Symbol       Preprocess Options                                                                     | 128     Δt = 0.70125 ps     Max Frequency: 1/2/Δt = 040 GHz       Plot     Pulse Response     Report                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ✓ Truncate response below       0.5       GHz         ✓ Truncate response above       30       GHz         □ Remove delay       2.5       ps | Magnitude Response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Rational Fitting Parameters       Tolerance (dB)       -40       Max # of poles       6                                                      | -20 -<br>9 -30 -<br>-40 Fit 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Use common poles for whole set<br>Tends to zero<br>High Frequency Pole (GHz) 100                                                             | -50<br>-60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                              | $\begin{array}{c} -70 \\ 10^{0} \\ 10^{2} \\ 10^{4} \\ 10^{6} \\ 10^{8} \\ 10^{10} \\ 10^{10} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} \\ 10^{12} $ |

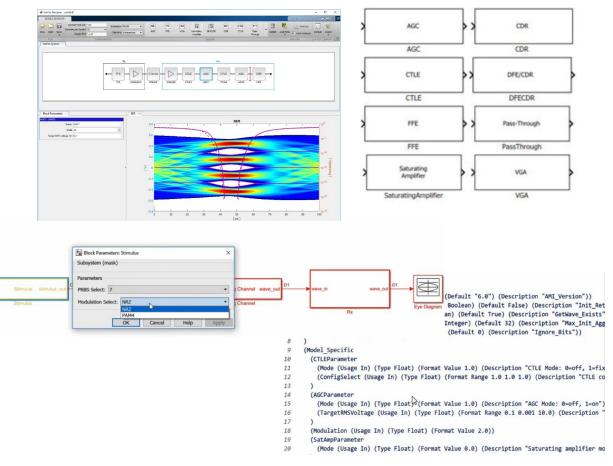

### Example of inclusion of Non-Linearity

SerDes App

Simulink Export

Rate limiter

### New Examples

- S-Parameter to Impulse Response

- Global Optimization

- Custom Block Workflow Edit CTLE

- Custom Block Workflow Use any Simulink block

Rx

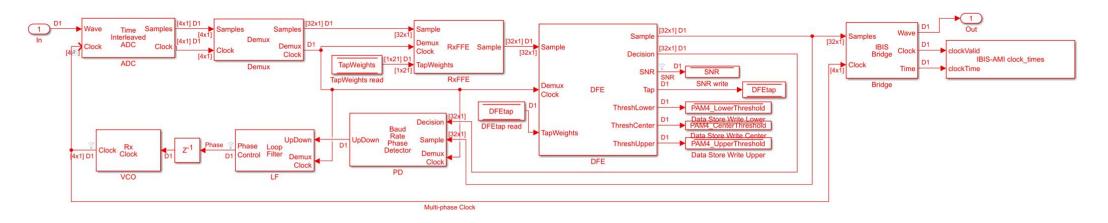

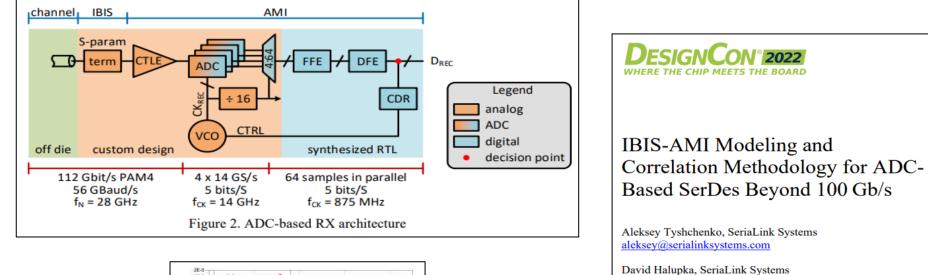

### Advanced example for high speeds

- Show how to more precisely **explore the tradeoffs** between:

- Number of interleaved ADCs

- Gain, timing, bandwidth and voltage offsets between the interleaved ADCs

- Demux width

- DSP adaptation loops

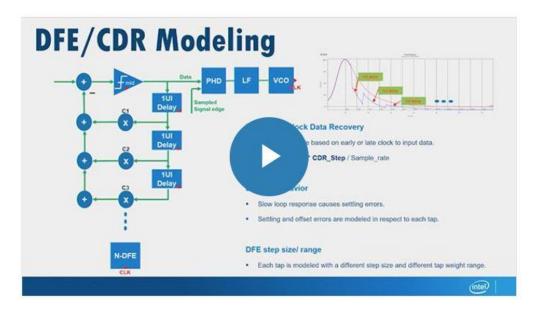

### Customer reference: Intel

• <u>56G PAM4 IBIS-AMI Model</u>

- <u>DesignCon 2020</u>

- DfA (Design for AMI) A New Integrated Workflow for Modeling 56G PAM4 SerDes Systems

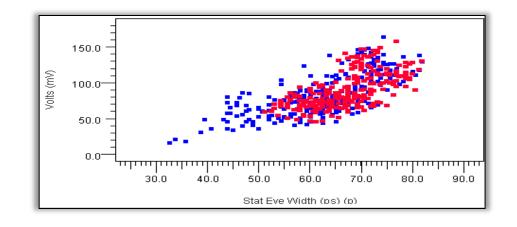

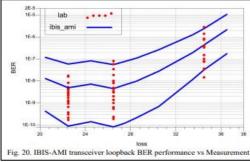

### **Correlated Simulations**

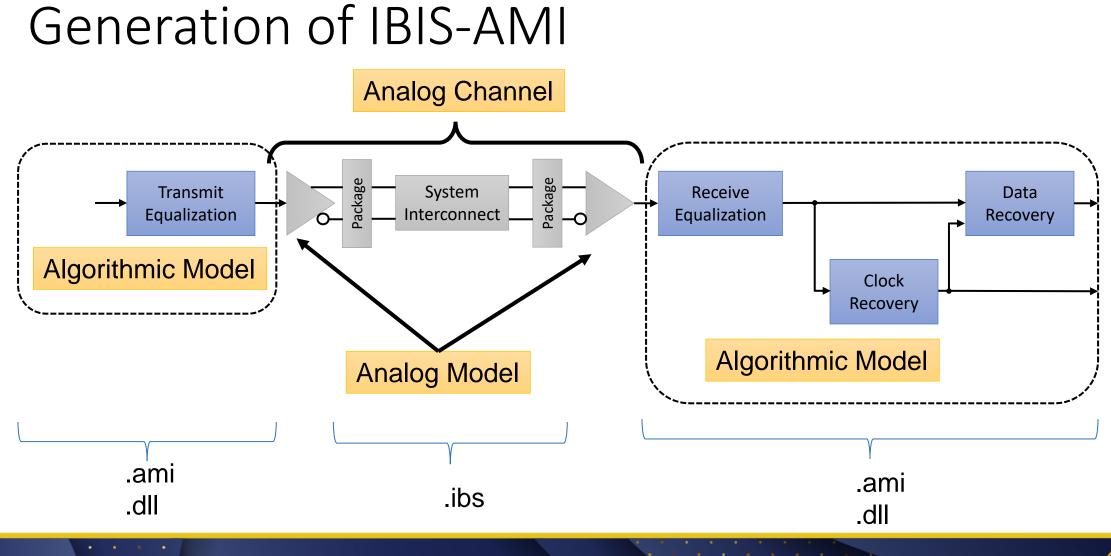

### Generation of IBIS-AMI

- Generate standard-compliant Init and GetWave IBIS-AMI models

- Generate associated analog IBIS model

- Customize the model interface by managing the IBIS- AMI-parameters

- Retimer & redriver:

- Connects Rx to Tx per IBIS-AMI spec

- I/O: Bi-directional for DDR applications

| 1 |                                |                             | E               | AMI File                                      |     |

|---|--------------------------------|-----------------------------|-----------------|-----------------------------------------------|-----|

|   |                                |                             | 0               | 📋 serdes_rx.ami                               |     |

|   |                                |                             | 9               | serdes_tx.ami Autosave Simulink Model or Libr |     |

|   | 承 SerDes IBIS-AN               | /II Manager                 |                 | untitled.slx.autosave                         | ary |

|   | Export IBIS                    | AMI - Tx AMI - Rx           |                 | Application extension                         |     |

| 1 | Model Configurati              | on                          | IBIS Settings   | serdes_rx_win64.dll                           |     |

|   | Tx and Rx                      |                             |                 | serdes_tx_win64.dll                           |     |

|   |                                | lel Name io_model           | Tx model nam    | Exports Library File                          |     |

|   | Redriver                       | _                           | Rx model nam    | 🛱 Rx.exp                                      |     |

|   | Retimer                        |                             | Tx and Rx corr  | d <sup>图</sup> Tx.exp                         |     |

|   | AMI Model Setting              | s-Tx                        | AMI Model Set 🚍 | IBS File                                      |     |

|   | Model Type                     |                             | Model Type      | serdes.ibs                                    |     |

|   | <ul> <li>Dual model</li> </ul> |                             | Dual mode       | Object File Library                           |     |

|   | GetWave on                     | v                           | GetWave         | Rx.lib                                        |     |

|   | O Init only                    |                             | O Init only     | 🖩 Tx.lib                                      |     |

|   | Bits to ignore                 | 0                           | Bits to ignore  | 0                                             |     |

|   | File Creation Option           | ons                         |                 |                                               |     |

|   | Models to export               |                             |                 |                                               |     |

|   |                                | ✓ IBIS file                 |                 |                                               |     |

|   | Both Tx and F                  | Rx IBIS file name (         | ibs) serdes.ibs |                                               |     |

|   | O Tx only                      | AMI file(s)                 |                 |                                               |     |

|   | Rx only                        | ✓ DLL file(s)               |                 |                                               |     |

|   | Target director                | S:\22\tworrell.Brf.j1322689 |                 | Browse                                        |     |

|   |                                |                             |                 | Export                                        |     |

|   |                                |                             |                 | Close                                         |     |

|   |                                |                             |                 |                                               |     |

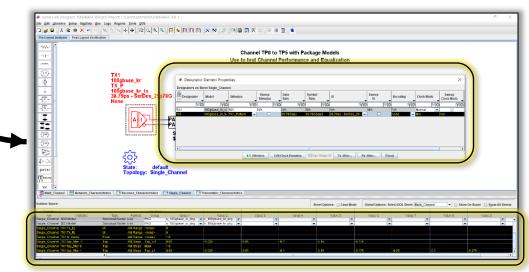

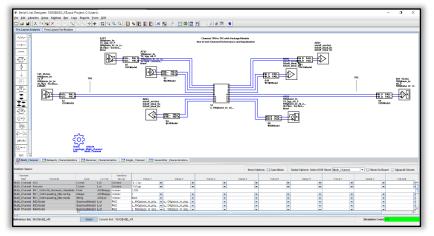

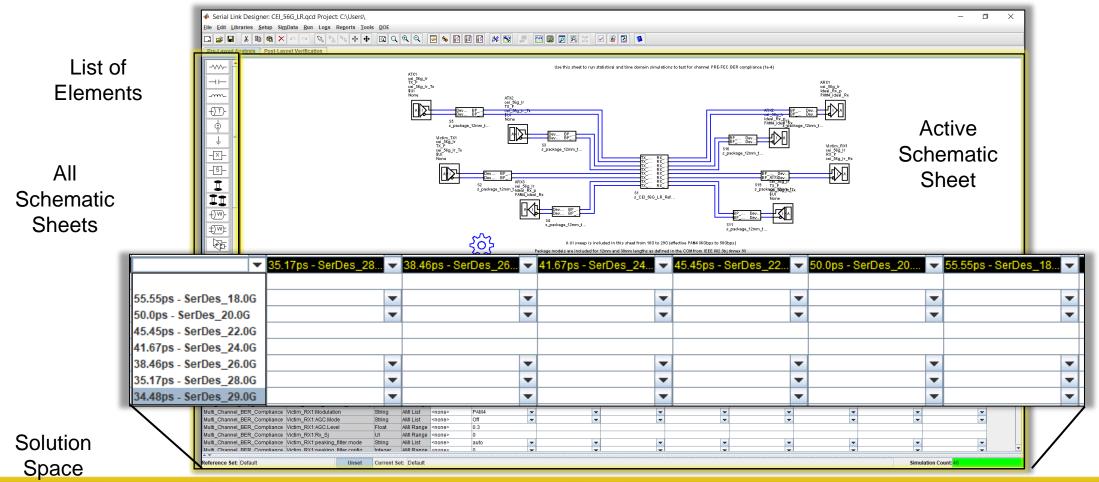

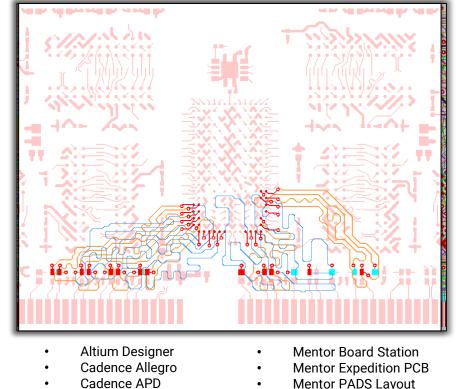

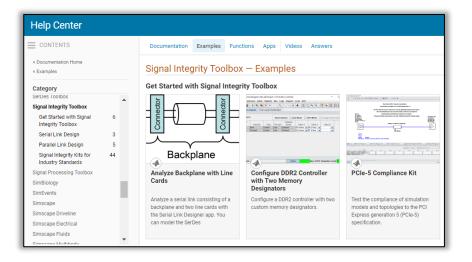

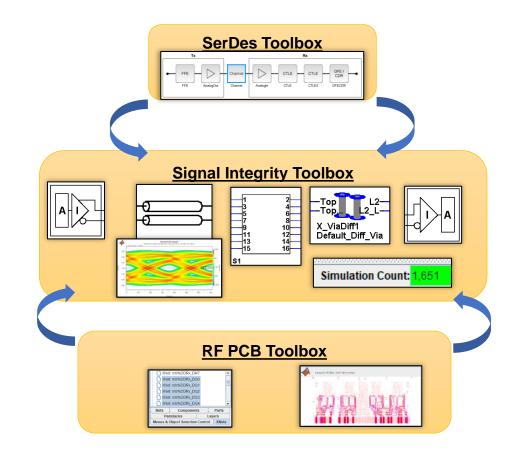

### Integration for testing

- Build your model in SerDes Toolbox and export an IBIS-AMI model directly into Signal Integrity Toolbox for Regression Analysis

- Sweep your IBIS-AMI model parameters to test them with various channels in Signal Integrity Toolbox

SYSTEMS INITIATIVE

If there are any issues, the test case can be pushed back to SerDes Toolbox / Simulink where you have full debug capabilities

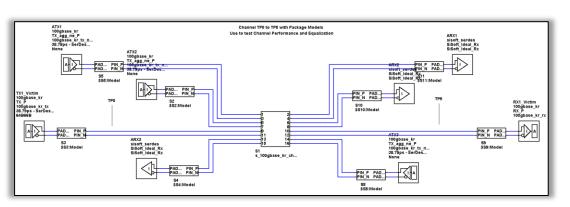

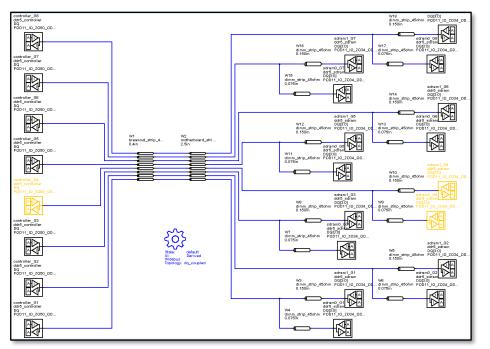

### Verifying the IBIS-AMI model with the channel

- Sweep parameters to explore the to find the best solution

- Build schematics to test the signal integrity of high-speed end-to-end serial and parallel links

- Test components and/or system designs for industry standard compliance

- Perform channel, statistical, and time-domain analyses and visualize the results

- Import PCB files for post-layout verification

- Import IBIS-AMI models for testing

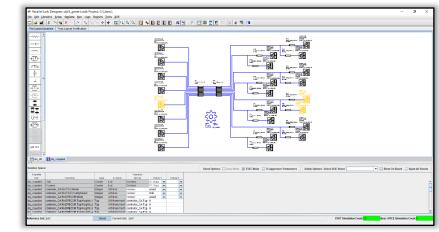

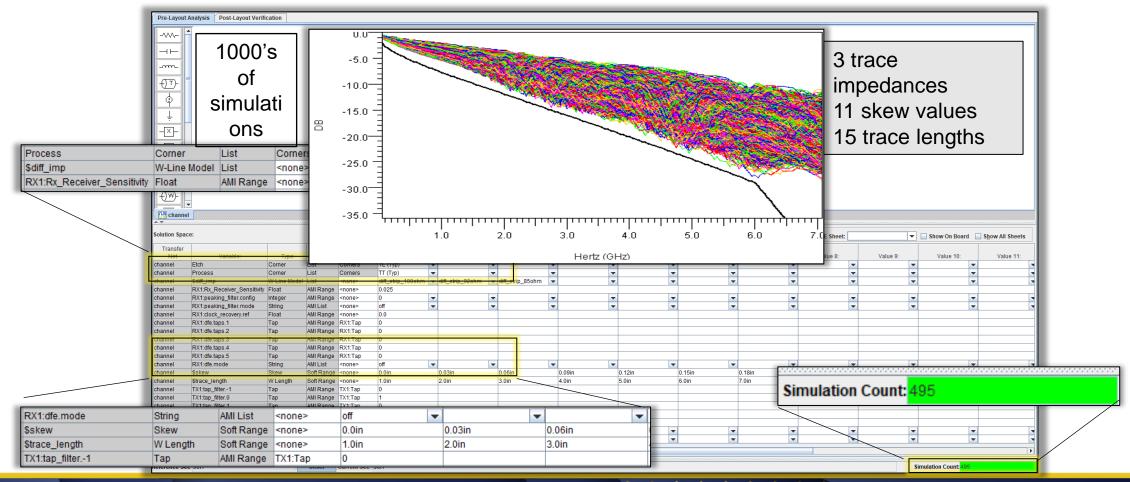

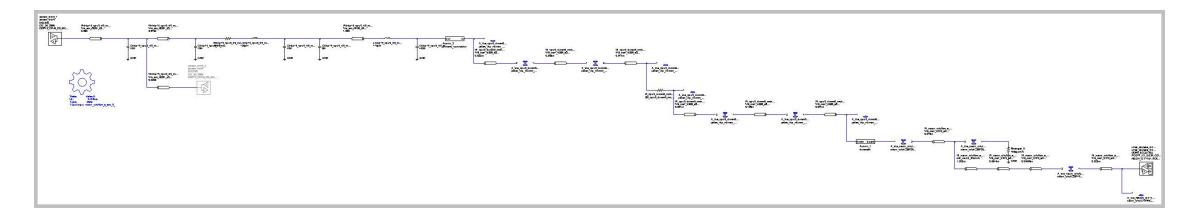

### Pre-layout Analysis workflow

#### • Serial Link

- Determine optimal equalization settings

- Predict operating margins and bit error rates

- Perform network, statistical, and time-domain analysis

#### Parallel Link

- Determine setup/hold timing and voltage margins

- Conduct waveform and timing analysis

- Analyze interfaces for timing and signal integrity compliance

### Pre-layout Analysis: solution space

#### -Top L2--Top L2\_L-X\_ViaDiff1 Default\_Diff\_Via

|                                          | efault.stkup + Pre-L              | ayout Vias         |                     |           |       |                   |                      |            |            |            |                  |         |         |

|------------------------------------------|-----------------------------------|--------------------|---------------------|-----------|-------|-------------------|----------------------|------------|------------|------------|------------------|---------|---------|

| Cursor(-                                 | 35.0.2                            |                    | 5.5 Ohms            |           | Bo    | ard Heigh         | t = 64.2mils         | s Select   | ed Layer(s | ) Thicknes | s = 0.0mils      | 📃 Edit  | t Stack |

|                                          |                                   | Zcm = 2<br>Delay = | 2.7 Ohms<br>11.2 ps |           |       | Layer             |                      | Thickness  |            | Left Via   | <b>Right Via</b> |         |         |

|                                          |                                   |                    | b = 0.0 s           |           |       | ID Name           |                      | (mils)     | Connect    | X-Section  | X-Section        | Connect | 1       |

| Bottom Stub = 0.0 s                      |                                   |                    |                     |           |       | 1                 | Dielectric           | 1.0        |            |            |                  |         |         |

| Cpad = 23.0 fF<br>Exit Trace = 55.0 mils |                                   |                    |                     |           |       | 2 Top             | Signal               | 0.6        | <b>v</b>   |            |                  | ~       |         |

|                                          |                                   | Exit Trac          | ce = 55.0 mils      |           |       | 3                 | Dielectric           | 5.0        |            |            |                  |         |         |

| 4                                        |                                   |                    |                     |           |       | 4 P1              | Plane                | 0.6        |            |            |                  |         |         |

| ►. <del>▼</del>                          |                                   |                    |                     |           | - 1 A | 5                 | Dielectric           | 5.0        |            |            |                  |         |         |

| Model Name Det                           | ault Diff Min                     |                    |                     | -         |       | 5 L2              | Signal<br>Dielectric | 0.6<br>5.0 |            |            |                  |         |         |

|                                          |                                   |                    | D.L.L.              |           |       | 8 P2              | Plane                | 0.6        |            |            |                  |         |         |

| Сору                                     | R                                 | ename              | Delete              |           |       |                   | Dielectric           | 5.0        |            |            |                  |         |         |

| Geometry                                 |                                   |                    |                     | _         |       | 0 L3              | Signal               | 0.6        |            |            |                  |         |         |

| :                                        | Start Layer Top                   |                    |                     | -         |       | 1                 | Dielectric           | 5.0        |            |            |                  |         |         |

| Finished Hel                             | End Layer Bottom<br>Diameter 18.0 |                    |                     | ▼<br>mils | 1     | 2 P3              | Plane                | 0.6        |            |            |                  |         |         |

|                                          | e Diameter 21.0                   |                    |                     | mils      | 1     | 3                 | Dielectric           | 5.0        |            |            |                  |         |         |

|                                          |                                   |                    |                     |           | 1 1   | 4 P4              | Plane                | 0.6        |            |            |                  |         |         |

| Pad<br>Shape Circle                      | Antij                             |                    | Racetrack           |           | 1     | 5                 | Dielectric           | 5.0        |            |            |                  |         |         |

| Diameter 30.0                            | 50.0                              |                    | _                   | mils      | 1     | <mark>6</mark> L4 | Signal               | 0.6        |            |            |                  |         |         |

| Width 30.0                               | 50.0                              |                    | 110.0               | mils      |       | 7                 | Dielectric           | 5.0        |            |            |                  |         |         |

| Height 30.0                              | 50.0                              |                    | 50.0                | mils      |       | 8 P5              | Plane                | 0.6        |            |            |                  |         |         |

| Pads On All Laye                         | ers                               |                    |                     | _         |       | 9                 | Dielectric           | 5.0        |            |            |                  |         |         |

| Differential Via                         | Spacin                            | g 60.0             |                     | mils      |       | 0 L5              | Signal               | 0.6        |            |            |                  |         |         |

| Racetrack                                |                                   |                    |                     | _         | 2     |                   | Dielectric           | 5.0        |            |            |                  |         |         |

| Back Drill                               |                                   |                    |                     |           |       | 2 P6              | Plane                | 0.6        |            |            |                  |         |         |

| Enable                                   | By Stub                           | By Layer           | By Depth            | h         | 1.1   | 3<br>4 Bottom     | Dielectric           | 5.0<br>0.6 | ~          |            |                  | ~       |         |

|                                          | Stub                              |                    | Depth               |           |       | 5 Bottom          | Signal<br>Dielectric | 0.6        | V          |            |                  |         |         |

| Drill                                    | (mils)                            | Layer              | (mils)              |           | ⁴     |                   | Dielecult            | 1.0        |            |            |                  |         |         |

| Drill<br>Side                            |                                   |                    | 0.0                 | <b>^</b>  |       |                   |                      |            |            |            |                  |         |         |

| Side<br>Top                              | 0.0                               |                    |                     |           |       |                   |                      |            |            |            |                  |         |         |

| Side                                     | 0.0                               |                    | 0.0                 |           |       |                   |                      |            |            |            |                  |         |         |

| Side<br>Top                              |                                   |                    | 0.0                 |           |       |                   |                      |            |            |            |                  |         |         |

Building schematic: Configure Via

## Building schematic: Configure Transmission

### Line

|                                                                                                                                                                                                                                                                              |                                          |                                                      | – 🗆 X     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------------------------------------------------------|-----------|

| File Edit                                                                                                                                                                                                                                                                    |                                          |                                                      |           |

| Transmission Line Model = diff_strip_97ohm_2x.mod (Library Model)                                                                                                                                                                                                            |                                          |                                                      |           |

| Single Conductor 💿 Differential                                                                                                                                                                                                                                              |                                          | Height Top ↔                                         |           |

| Coupled Aggressors: 2 Conductors: 6 Reference Plane                                                                                                                                                                                                                          |                                          | t Base<br>Pitch Pitch                                |           |

| Model Type Diff Pair L1 R1 Diff Pair                                                                                                                                                                                                                                         | Etch Shape                               | Tabbed Routing                                       |           |

| ○ Simple Lossy T-Line Calculate S S S S S S S S S S S S S S S S S S S                                                                                                                                                                                                        | Rectangle                                | Enable                                               |           |

| ○ Microstrip     View Model       ✓ W → ↓     Victim                                                                                                                                                                                                                         | 2 Trapezoid                              | Tab Pitch (mils)                                     |           |

| Stripline     Trace T     Dielectric Er                                                                                                                                                                                                                                      | Angle (45 - 90 degrees) Top Width (mils) |                                                      |           |

|                                                                                                                                                                                                                                                                              | 67.5 3.4615223                           | Tab Base Width (mils)                                |           |

| Save Save As Close Reference Plane                                                                                                                                                                                                                                           |                                          | Tab Height (mils)                                    |           |

|                                                                                                                                                                                                                                                                              |                                          |                                                      | -         |

| Coupling Differential Tpd Resistance Inductance Capacitance Conductivity Trac                                                                                                                                                                                                |                                          | f Er at f Loss Table-Driven Differential Conductor R |           |

| Configuration         Impedance(Ohms)         (ps/in)         (mOhms/in)         (nH/in)         (pF/in)         (Meg S/m)         Width (           Adjacent         ▼         94.362         178.141         279.916         11.204         2.893         58.0         4.0 |                                          | (GHZ) Tangent Loss Model Separation (mills) (Micro   |           |

| Adjacent <b>v</b> 94.362 178.141 279.916 11.204 2.893 58.0 4.0                                                                                                                                                                                                               | 0.65 6.5 13.0                            | 1.0 4.25 0.02 None ▼ 4.0 0.1                         | 5 4.0 4.0 |

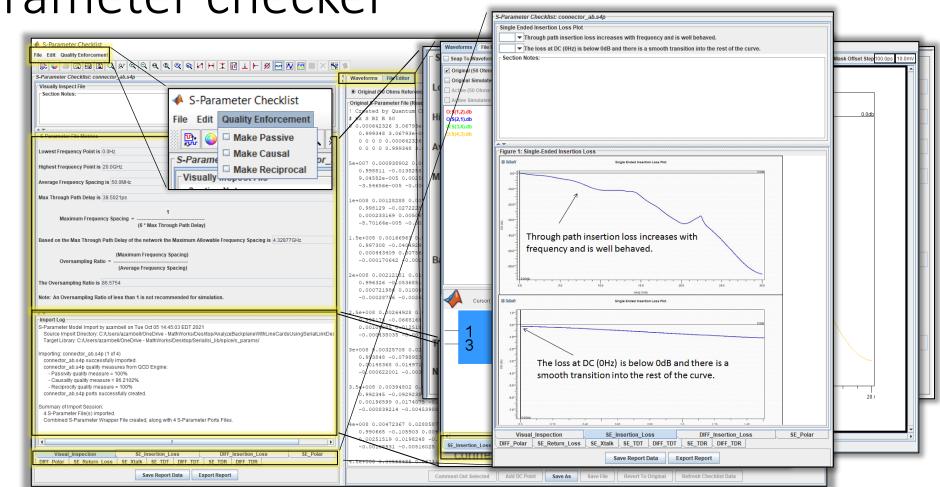

### Importing and Edit s-parameter Models

When importing S-Parameters, use the S-Parameter Checklist to verify their quality before use

### S-parameter checker

### Design Space Exploration – Sweep parameter

### Design Space Exploration - Parallelization

| Prelayout Channel Analysis      Project: backplane_linecard Interface: serdes                                                                                | ×                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Reference Schematic Set: set1 - Process Controls:                                                                                                            | Parallel Computing Toolbox Clusters:                                                                                                    |

| Stop On Error Setup Stop Error Conditions     Backup Before Deleting Data Restore                                                                            | Default Cluster: local         Cluster Selection:       Number of Simulations Per Task:                                                 |

| Simulation Options       Simulation Parameters       Image: Parallel       Configure Parallel         Channel Analysis Steps:       Channel Analysis Summary | SPICE: <default cluster="">        SPICE:       1       *         Channel Analysis:         Channel Analysis:       1       *</default> |

| ✓ Validate         ✓ Generate Netlists         ✓ Include Statistical Analysis         ✓ Include Time Domain Analysis                                         | Parallel Help Test Refresh Clusters                                                                                                     |

| Run SPICE         Perform Channel Analysis         Display Results Spreadsheet         Autoload Results         All Sheets         Current Sheet             | Local to Remote Path Maps:<br>Local Path Remote Path                                                                                    |

| - Channel Analysis Queue Monitor                                                                                                                             |                                                                                                                                         |

| Run Close Errors & Warnings 🔀 Autoload Results                                                                                                               |                                                                                                                                         |

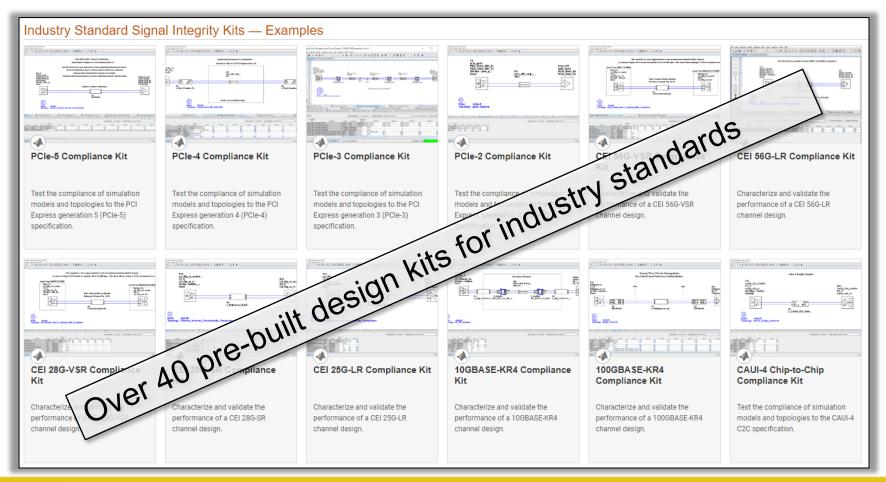

### Design Kit for Industry Standards

### Simulation Technology

- Perform Channel Analysis provides network characterization results which includes un-equalized system responses such as impulse response, step response, pulse response, S-Parameters, transfer functions, and more.

- Include Statistical Analysis results such as statistical eye, BER, bathtub, contour, crosstalk, and more.

- Include Time-Domain Analysis results such as persistent eye, BER, bathtub, contour, deterministic jitter probability function, crosstalk, and more.

| Prelayout Channel Analys<br>Project: backplane_linecard<br>Interface: serdes          | IS         |                   |                       | Show BER ×                        |

|---------------------------------------------------------------------------------------|------------|-------------------|-----------------------|-----------------------------------|

| Reference Schematic Set: set1<br>Process Controls:                                    | Display1   |                   |                       | Show Bathtub                      |

| Stop On Error Setup Stop Er                                                           | ැ<br>Row   | ID                | Transfer Net          | Show BER                          |

| Backup Before Deleting Data                                                           |            | Y©                |                       | Show Persistent Eye               |

|                                                                                       | 1          | 1                 | Single_Channel_BER    | Show Bathtub                      |

| Simulation Options Sin                                                                | 2          | 2                 | Single_Channel_BER    | Show vertical Bathtub             |

| Channel Analysis Steps:                                                               | 3          | 3                 | Single_Channel_BER    | Show D.I                          |

| ✓ Validate                                                                            | 4          | 4                 | Single_Channel_BER    | Show Contours                     |

| Generate Netlists                                                                     | 5          | 5                 | Single_Channel_BER    | -                                 |

| <ul> <li>Include Statistical Analysis</li> <li>Include Time Domain Analysi</li> </ul> | 6          | 6                 | Single_Channel_BER    |                                   |

|                                                                                       | 1          | 7                 | Single_Channel_BER    |                                   |

| Perform Channel Analysis                                                              | 8          | 8                 | Single_Channel_BER    | Show officer fruitsfer            |

| <ul> <li>Display Results Spreadsheet</li> <li>Autoload Results</li> </ul>             | 9          | 9                 | Single_Channel_BER    | Show Drobod Dorejetont Evo        |

| Autoload Results     All Sheets     Curren                                            | 10         | 10                | Single_Channel_BER    |                                   |

| 0.000                                                                                 | 11         | 11                | Single_Channel_BER    | -                                 |

|                                                                                       | 12         | 12                | Single_Channel_BER    |                                   |

|                                                                                       | 13         | 13                | Single_Channel_BER    | Show IDIS-AMI Output Parameters P |

| Channel Analysis Queue Monitor                                                        | 14         | 14                | Single_Channel_BER    | Show Solution Space               |

|                                                                                       | 15         | 15                | Single Channel BER    | Show Results                      |

|                                                                                       | 0: Network | 1: Statistical 2: | Time Domain           |                                   |

|                                                                                       | C. HELWOIN | Ti Statistical    | Time_bomain           | Show On PCB                       |

|                                                                                       | 0: Network | 1: Statistical    | 2: Time_Domain        | Show On PCB                       |

|                                                                                       | Ľ          |                   |                       |                                   |

|                                                                                       |            |                   |                       |                                   |

|                                                                                       | Run C      | Close Errors & V  | Varnings 🛛 🕅 Autoload | Results                           |

#### <u>File Edit Libraries Setup SimData Run Logs Reports Tools DOE</u>

Pre-Layout Analysis Post-Layout Verification

| A. 🔻            |                          |                                                                     |

|-----------------|--------------------------|---------------------------------------------------------------------|

| Solution Space: | Sheet Options: Case Mode | Global Options: 🗌 Incremental Select DOE Sheet: 🔍 💌 🔄 Show On Board |

Reference Set: Set Current Set: Simulation Count:

### Post-layout **Pre-layout**

- Use RF PCB Toolbox to import PCB files ٠

- Compare pre- and post-layout nets to each other .

- Easily identify any issues

- Incorporate fixes and re-simulate

#### Post-layout

- Mentor PADS Layout

- ODB++

- Zuken

IBIS EBD

Intercept Pantheon

### Post-layout to Pre-layout

- Includes etch, vias, connectors, and discrete components for each board

- Topology can now be modified using Pre-Layout GUI to find solution

| CFFE. LapWeights.2 | lap          | AMI LIST   | intel clodeke de |                     |                |                           |       | -                            |

|--------------------|--------------|------------|------------------|---------------------|----------------|---------------------------|-------|------------------------------|

| ch_A/RN83.1.4:R    |              | soft Range | <none></none>    | 10ohm               | 12ohm          | 15ohm                     | 18ohm |                              |

| ecc<0>_1:Length    | W Length     | Soft Range | <none></none>    | 0.750in             | 1.203in        | 1.50in                    |       |                              |

| ecc<0>_1:W_Model   | W-Line Model | List       | <none></none>    | mb_micro_40ohm      | mb_micro_50ohm | wb_micro_65ohm            | -     | <b>v</b>                     |

|                    | 4            |            |                  | and the second have |                |                           |       | •                            |

|                    |              |            |                  |                     |                |                           |       |                              |

| Unset              | Current Set: | set1       |                  |                     |                | STAT Simulation Count: 72 | Bas   | e SPICE Simulation Count: 72 |

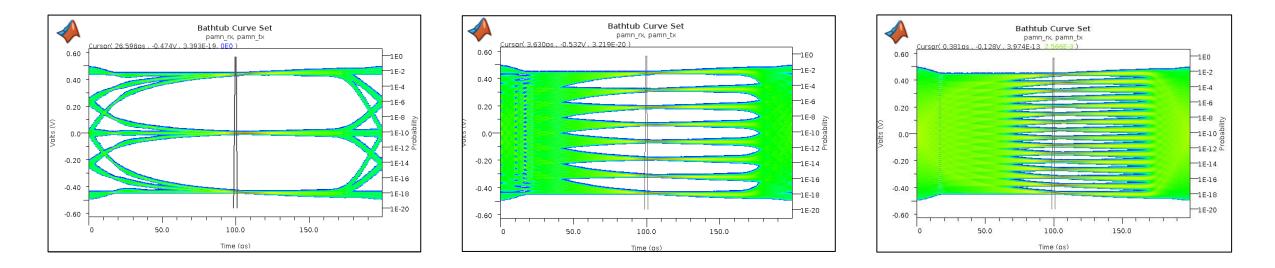

### New for R2022b – PAMn IBIS-AMI Model Support

Now use IBIS-AMI models with PAM3, PAM8, PAM16 modulation for use with next generation USB4, GDDR7, MIPI A-PHY, and Automotive SerDes Alliance Motion Link

## New for R2022b – Design Kits for Industry Standards

## Two DesignCon 2022 Best Paper Award Winners!

Richard Allred, MathWorks Tripp Worrell, MathWorks Barry Katz, MathWorks

Clinton Walker, Alphawave IP

Adrien Auge, Alphawave IP

#### Infineon Accelerates Development of IBIS-AMI Models for SerDes Designs

#### Challenge

Produce a complete IBIS-AMI model of a SerDes system for a key customer on an aggressive schedule

#### **Solution**

Use Simulink and SerDes Toolbox to develop, verify, and deliver an IBIS-AMI model in two weeks

#### **Results**

- Complete IBIS-AMI models delivered in two weeks

- Development ramp-up accelerated

- In-house IBIS-AMI capability developed

#### Infineon semiconductor.

"The process of creating and configuring IBIS-AMI models with SerDes Toolbox is straightforward and fast to learn. After completing it once ourselves, we had full control over IBIS-AMI model creation, and eliminated our dependence on contractors." - Syed Babar Raza, Infineon

#### Link to user story

### Summary

### Key takeaway

- Start with statistical analysis

- Refine model with architectural/circuit-level details

- Generate IBIS-AMI model ensuring equivalence

- Regression testing with different channels

- Make sure there is enough margins in all conditions

- Compliance check with the standard

### Questions?