# Utilization of Emulation for accelerating

# the Functional Verification Closure

Varun Kumar C, Senior Engineer, SSIR, Bangalore (<u>varun.k2@samsung.com</u>) Sekhar Dangudubiyyam, Associate Director, SSIR, Bangalore (<u>sekhar.d@samsung.com</u>) Madhukar Ramegowda, Associate Technical Director, SSIR, Bangalore (<u>madhukar.r@samsung.com</u>)

## **Introduction**

With the increasing complexity of SOC designs for AI, automotive, wearables and mobile applications, the focus on creating robust system stimulus covering all critical interfaces and measurement of functional coverage at SOC level has increased significantly. IP/Sub-system level DV scope covers internal design core with synthetic traffic using bus transactor and often do not see simulation runtime challenges, when the same IP/Sub-system is integrated in SOC, generating real traffic from higher level abstraction poses limitation in covering varieties of scenarios predominantly due to longer runtimes (i.e. verification at SOC level requires compulsive clock initializations and memory initializations). Verification of the SOCs with memory models like HBM3 and multiple instances of Traffic Generators consists of complex concurrent traffic scenarios. Implementing such large data traffic scenarios on the emulation systems which provides rich debug environment and support for functional coverage analysis becomes absolutely necessary, since simulation poses challenges like very long runtimes, complex testbench setup, various initialization requirements, unsteady license availability and license holding, hence blocking us from performing multiple iterations with various functional and address coverage.

## **Proposed Methodology**

Based on the requirement for implementing the concurrent traffic scenario on the emulation system, below objectives were defined :

- To use the emulation methodology for accelerating verification of multimedia, high speed IO and performance verification.

- Implementing complete functional coverage solution with powerful single binding statement providing coverage metrics for all the instances of DMAs and Custom DMAs.

- Complete leverage of existing UVM SV environment for preparing software workloads.

- Use this emulation flow for self checking and UART aided debug.

- Developing software like interrupt service routines for SOC interrupts handling.

- Periodic interrupts from the Multi Core Timer(MCT) for printing the runtime units.

- T32 interface for live monitoring of various IPs and memory models in SOC.

- Developing an emulation image with the SPI transactor for alternate bootflow.

- Capture the waveform for the desired time window of the concurrent activity.

### **Implementation Details**

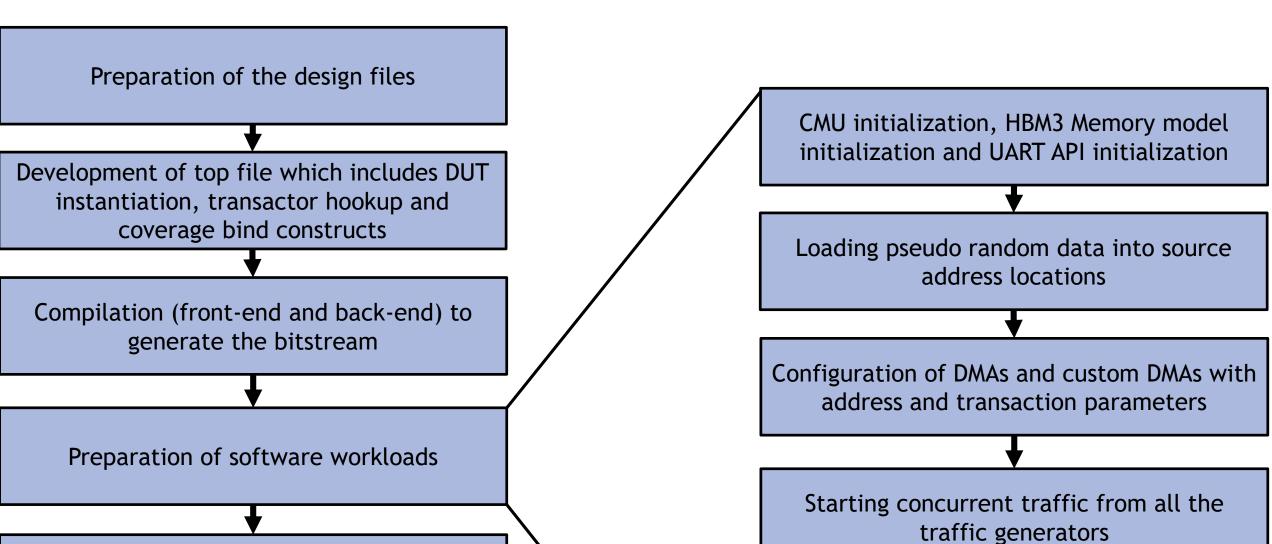

### **Implementation Flow Chart**

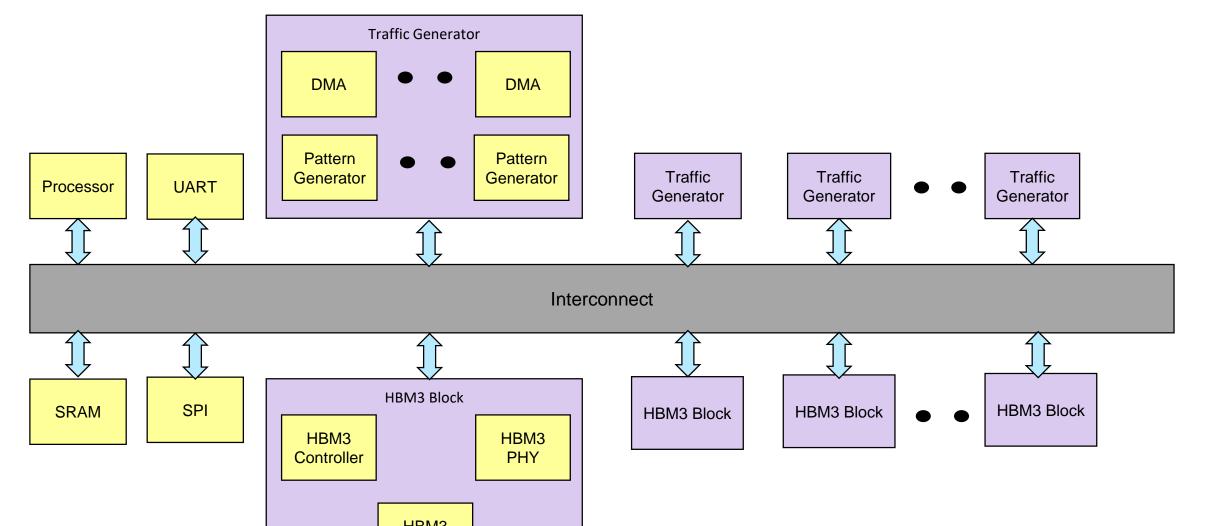

Architectural overview of HBM3 Controller

Above diagram represents the architectural overview of HBM3 Controller.

SRAM memory is used for loading software workloads, which is accessed by the processor. UART API's in the software make use of UART IP and its transactor for message display. SPI IP provides SPI interface for alternate bootflow. We have multiple instances of traffic generators, in each traffic generator we again have multiple instances of DMA330 and the custom DMAs all functioning to generate the traffic for the HBM3 block.

#### Verification on Emulation systems

# **Results Table**

Runtimes were captured for concurrent traffic scenarios, both in simulation and emulation environments and the data is presented in the below table,

| Events             | <b>RTL Simulation</b> | Gate Level<br>Simulation | <b>RTL Emulation</b> | Runtime Efficiency<br>Improvement |

|--------------------|-----------------------|--------------------------|----------------------|-----------------------------------|

| HBM initialization | 69 hours 21 mins      | 415 hours                | <30 secs             | 8000x ~ 50,000x                   |

| DMA Verification   | 15 hours 32 mins      | 163 hours 13 mins        | <10 mins             | 100x ~ 1000x                      |

| Custom DMA runs    | 13 hours 50 mins      | 133 hours 49 mins        | <7 mins              | 100x ~ 1000x                      |

| 1 ms timer run     | 10 mins               | 50 mins                  | <10 secs             | 60x ~ 300x                        |

Runtime comparisons between simulation and emulation

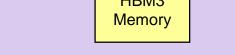

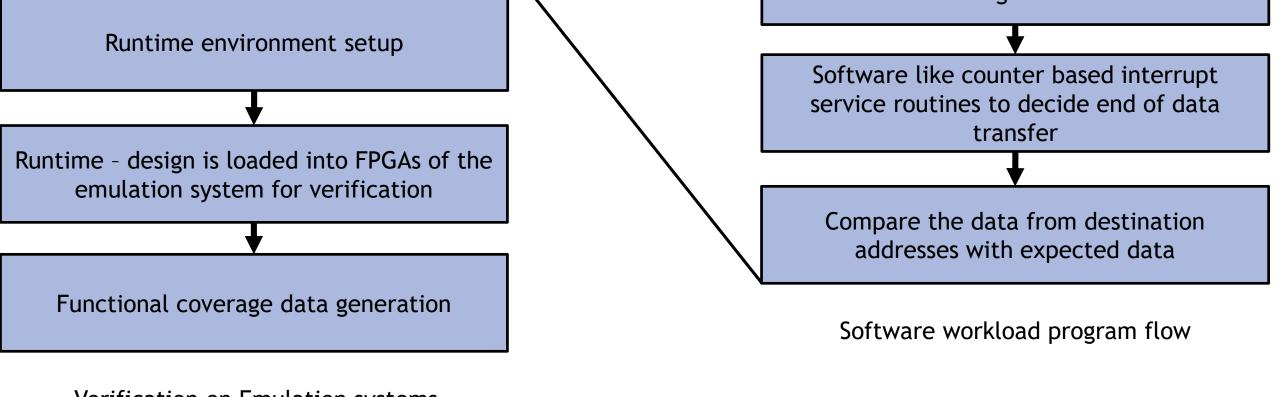

Waveform captured and Functional coverage data collected are given in the figure below,

# **Conclusion**

The methodology discussed has been successfully validated on emulation platform with waveform capture and complete debug capabilities. The future work that has been identified for this methodology are :

- 1. Extending to other High Speed IPs like PCIE, USB etc. Use existing protocol transactors and cover larger traffic test like DMA scenario.

- 2. Backdoor read/write and memory dump operations of emulation system can be used for data capture and comparison.

- 3. Testbench infrastructure can be scaled up to netlist based runs for zero delay GLS. PnR ready netlist based emulation is already proved methodology.

Hence, scaling up the usage of emulation infrastructure in accelerating functional coverage closure of critical interfaces in SOC like power management, DRAM, fabric

| 🔁 🗗 🥆 🖻 🔓 📐                             | 1,207,990,794         | J7,990,794 <u>∧</u> ♥ 0               | x Ions                         | Ву: 🛃 💌                                  | 🌀 Goto: DMA_0 🔽 🕹 🔻          |                                     | i and in the second |

|-----------------------------------------|-----------------------|---------------------------------------|--------------------------------|------------------------------------------|------------------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------|

|                                         | DMA_0                 | 1,1, 254, 750, 000                    |                                | 1,264,800,000 <u>, , , ,</u><br>DMA_2    | 1, 264,850,000<br>           | LCUSTON DMA 0                       | 1, 264, 9 =                                                                                                    |

| = DNA O                                 | onur_o                | enni_r                                |                                | pmi_z                                    | enur_3                       | ousion_ban_o                        | CONTON_DHILT                                                                                                   |

| - 🜆 📴 awaddr [31:0] i) (                | 0 0) (*) (() (*)***** | • DIE DIWIE <mark>DUUE E IE</mark> DO | )   )   8*   *   1   *   *   1 | <b>1</b>                                 | 8050_3f8                     | 0                                   |                                                                                                                |

| - 🔤 📴 wdata[127:0] 👔 (                  |                       |                                       |                                |                                          | 0                            |                                     |                                                                                                                |

| DMA_1                                   |                       |                                       |                                |                                          |                              |                                     |                                                                                                                |

| - 🔤 💽 awaddr [31:0] 👔 (                 | 0 0                   | ( *8* ) * ))                          |                                | ())) (* (* (* (8* ()) * ()) (* ()) (* () |                              | 8050_3f80                           |                                                                                                                |

| - 🔤 📴 wdata[127:0] 🔹 i) (               | 0 0                   |                                       |                                | <u> </u>                                 | <u>() (0</u>                 | 0                                   |                                                                                                                |

| DMA_2                                   |                       |                                       |                                |                                          |                              |                                     |                                                                                                                |

| 🔤 📄 avaddr [31:0] 🛛 i) (                | 0                     | 0                                     |                                |                                          |                              |                                     | £80                                                                                                            |

| 🔤 💽 wdata[127:0] 🚯 (                    | 0                     | 0                                     |                                |                                          |                              | 0                                   |                                                                                                                |

| DMA_3                                   |                       |                                       |                                |                                          |                              |                                     |                                                                                                                |

| - 🔤 📴 awaddr [31:0] (                   | 0                     |                                       | 0                              |                                          |                              |                                     |                                                                                                                |

| 🔤 💽 wdata[127:0] 👔 (                    | 0                     |                                       | 0                              |                                          |                              |                                     |                                                                                                                |

| CUSTON_DMA_0                            |                       |                                       |                                |                                          |                              |                                     | 100 1000                                                                                                       |

| - 🔤 📐 awaddr [63:0] 8) (                | 0                     |                                       | U                              |                                          |                              | *                                   | c100_4000                                                                                                      |

| - 🔤 📴 wdata[255:0] i) (                 | U                     |                                       |                                |                                          |                              |                                     | 18_1111_1d1/_1111_1*                                                                                           |

| : CUSTON_DMA_1<br>🔤 📴 awaddr[63:0] i) ( |                       |                                       |                                | 0                                        |                              |                                     | *)                                                                                                             |

| - 🔤 💽 wdata[255:0] - i) (               |                       |                                       |                                | 0                                        |                              |                                     | 1111111_*)))11*                                                                                                |

| 67                                      |                       |                                       |                                |                                          |                              |                                     |                                                                                                                |

|                                         |                       |                                       |                                |                                          |                              |                                     |                                                                                                                |

|                                         |                       |                                       |                                |                                          |                              |                                     |                                                                                                                |

| <u>.</u>                                | 1, 210, 000, 000      | 1, 220, 000, 000 1, 230, 00           | 0,000 1,240,000,               | 000   1, 250, 000, 000   1, 260, 00      | 0,000 1,270,000,000 1,280,00 | io, ooo   1, 290, opo, ooo   1, 30i | 0, 000, 000   1, 310, qoi   01 🕁                                                                               |

| archy Modules Groups Asserts S                         | lests   |         |          | Cov | erea                                                  | 💌 🤤 🖨 🔤 🔤 🚽                        | Ĺ           |                        |              |               |               |     | Cross 2D Pro |   |

|--------------------------------------------------------|---------|---------|----------|-----|-------------------------------------------------------|------------------------------------|-------------|------------------------|--------------|---------------|---------------|-----|--------------|---|

| Σ *                                                    |         |         | <u> </u> |     | 143                                                   |                                    | •           | Cover Group Item       | Defir        | ition Score   | U +           | C U | С            |   |

| Avg. Group Score:1.04% U+C:1536 U:1520 C:16 X:0        |         |         |          |     | 144                                                   | covergroup axi_pa                  |             | 🗄 🖸 axi_parameter      | top.d        | ut. B         | 100.00%       | 16  | c            |   |

| Avg. Group Inst. Score: 1.04% U+C:1536 U:1520 C:16 X:0 |         |         | π        |     | rameters @(posedge write<br>addr, posedge write data, |                                    | CP cp_awlen |                        |              | 100.00%       | 16            | 0   |              |   |

| 4                                                      | Score   |         |          | A I |                                                       | posedge read addr, posed           |             |                        |              |               |               |     |              |   |

| iodule::axi_parameters                                 | 1.04%   | 1.04%   | 1536     |     |                                                       | <pre>ge read_data);</pre>          |             |                        |              |               |               |     |              |   |

| ).DMA0.bind_dma_axi_functional                         | 0.00%   | 0.00%   | 16       | - 0 | 145                                                   | cp_awlen:                          |             |                        |              |               |               |     |              |   |

| .DMA1.bind_dma_axi_functional                          | 0.00%   | 0.00%   | 16       |     | 140                                                   | coverpoint awlen {                 |             |                        |              |               |               |     |              |   |

|                                                        | 0.009   | 0.00%   | 16       |     | 146                                                   | <pre>ins range[] = {[0:15]};</pre> |             |                        |              |               |               |     |              |   |

| .DMA3.bind_dma_axi_functional                          | 0.009   | 0.00%   | 16       |     | 147                                                   | 147                                | }           |                        |              |               |               |     |              | P |

| .TinyDMA0.bind_tiny_dma_axi_fu                         | 100.009 | 100.00% | 16       |     | 148                                                   | endgroup : axi_pa<br>rameters      | •           | Status Bin Nam∉        | ~            | At Least Size | Hit Count     |     | 4            |   |

| .TinyDMA1.bind_tiny_dma_axi_fu                         | 0.009   | 0.00%   | 16       |     | 149                                                   | 1 dilocorb                         | ⊩           | range_0                | User<br>User | 1             | 1 486         |     |              |   |

| .DMA0.bind_dma_axi_functional                          | 0.009   | 0.00%   | 16       | 0   | 150                                                   | axi_parameters ax                  | ⊩           | range_1<br>→ ✓ range 2 | User         | 1             | 1 203<br>1 98 |     |              |   |

| .DMA1.bind_dma_axi_functional                          | 0.009   | 0.00%   | 16       |     | 151                                                   | i_parameters_inst = new;           | ⊩           | ✓ range_3              | User         | 1             | 1 123         |     |              |   |

| DMA2.bind_dma_axi_functional                           | 0.009   | 0.00%   | 16       |     | 151                                                   | endmodule                          |             |                        | User         | 1             | 1 33          |     |              |   |

|                                                        | 0.009   | 0.00%   | 16       |     |                                                       |                                    |             | range_5                | User         | 1             | 1 43          |     |              |   |

|                                                        | . 0.009 | 0.00%   | 16       |     |                                                       |                                    |             | range_6<br>→ ✓ range_7 | User<br>User | 1             | 1 43          |     |              |   |

|                                                        | . 0.007 |         |          |     |                                                       |                                    |             |                        | 0.301        | ± .           |               |     |              |   |

Waveform capture for 4 instances of DMA330s and 2 instances of Custom DMA

Functional Coverage implementation on Emulation Platform

acceptance/issuing capabilities, coherency, memory management (MMU) and Q/P channel handshake et al. This brings together various aspects of simulation and emulation like hardware implementation of SOC design, peripheral transactors, software workloads, functional verification, functional coverage model and covergroups, trace32 based debug and waveform capture, ultimately helping in overcoming the limitations of simulation and speeding up the verification closure. With the tremendous future works identified, adopting and scaling up of this methodology becomes an absolute necessity.

## **REFERENCES**

- [1] Emulation Synopsys: <u>https://www.synopsys.com/verification/emulation/zebu-server.html</u>

- [2] HBM3 IP solutions: <u>https://www.synopsys.com/designware-ip/interface-ip/hbm.html</u>

- [3] Corelink DMA-330 DMA Controller Technical Reference Manual

- [4] Emulation for accelerating the Functional Verification Closure presentation: <u>https://drive.google.com/file/d/1\_-PRqnHApA\_0jsYgEpX05oPihXkTN6SX/view?usp=drivesdk</u>

# © Accellera Systems Initiative