# Using Mutation Coverage for Advanced Bug Hunting and Verification Signoff

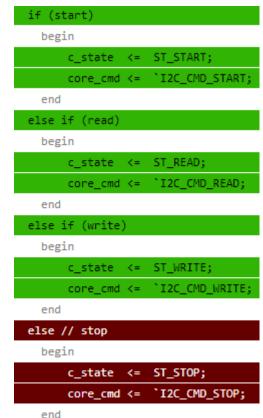

### Nicolae Tusinschi

making electronics reliable

Formal Coverage

- **Example: FIFO Verification**

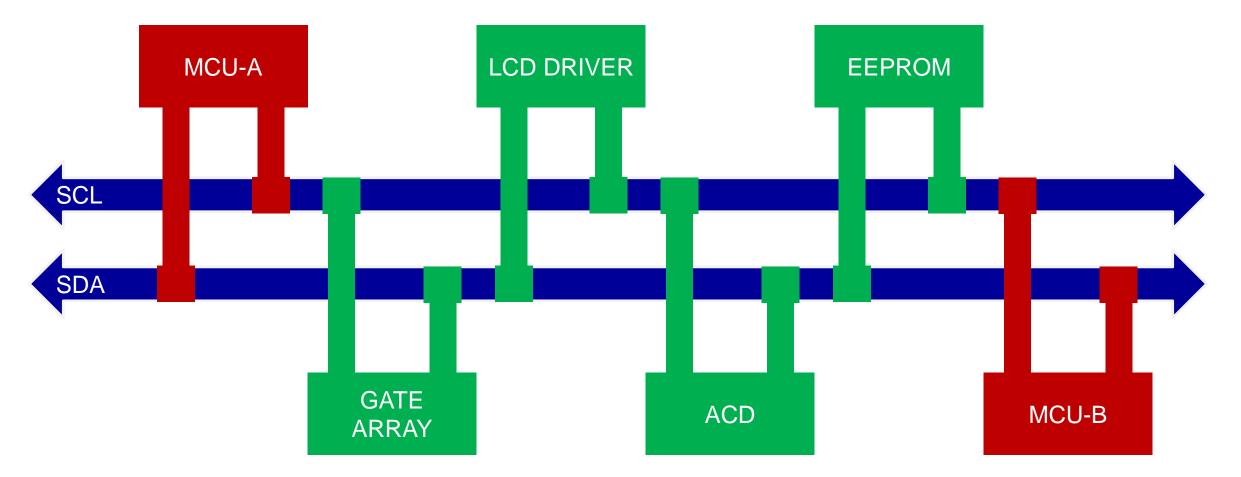

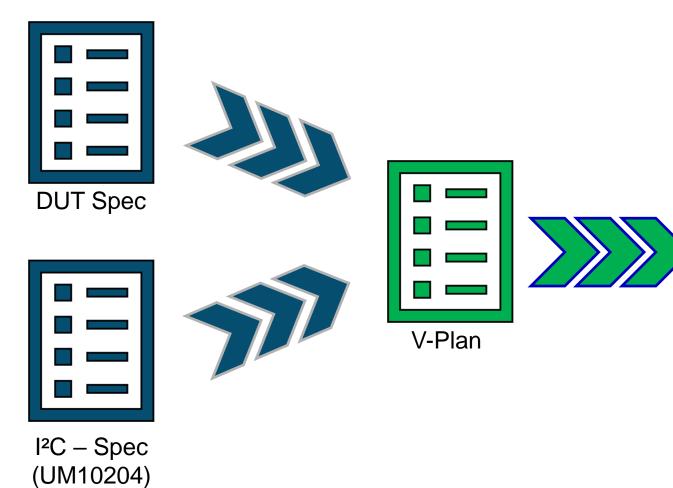

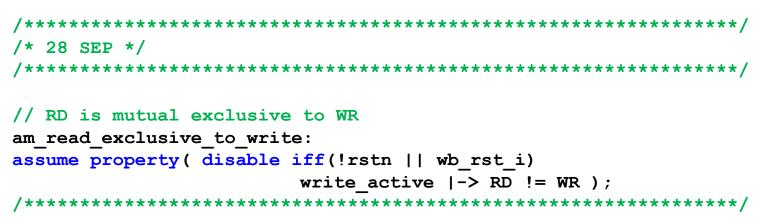

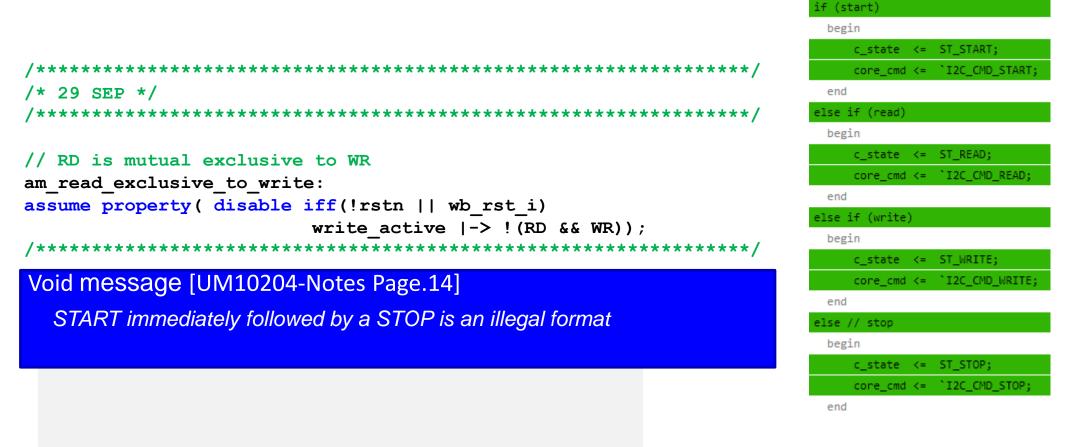

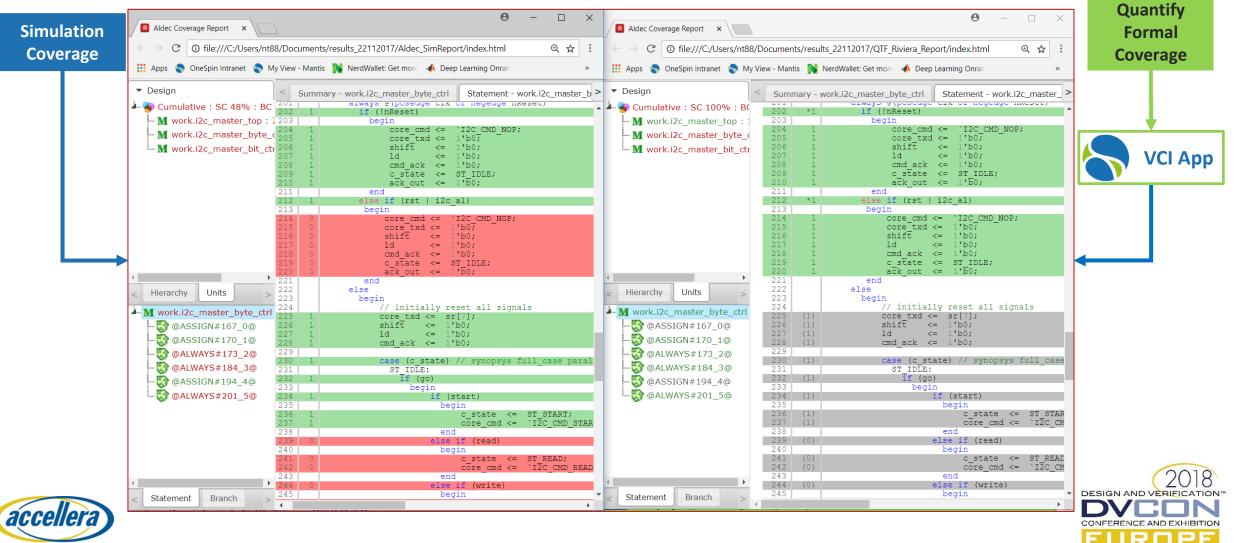

- Case Study: I<sup>2</sup>C Verification

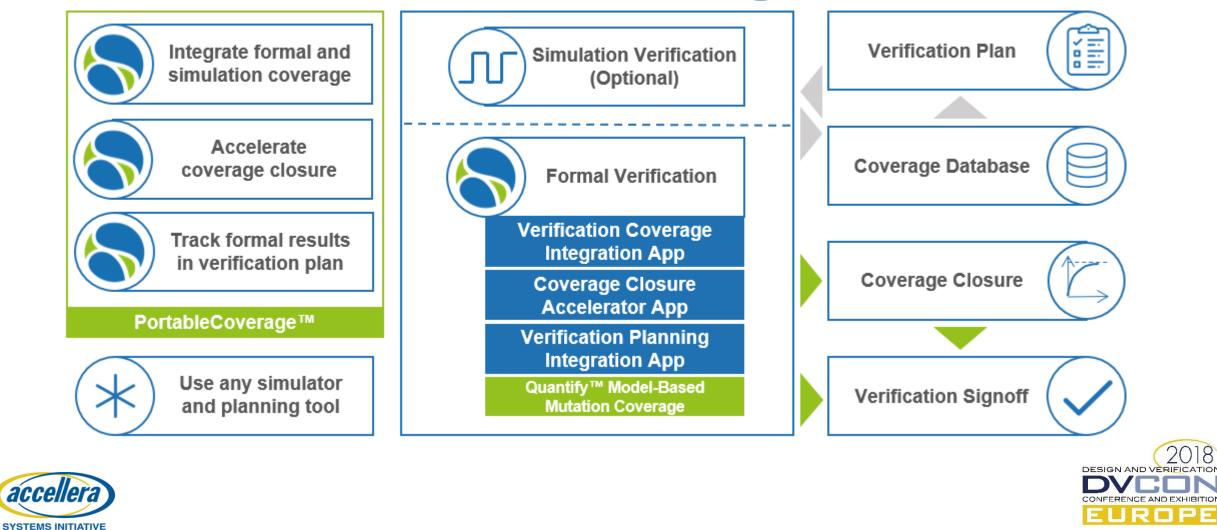

- PortableCoverage

- Summary

Q&A

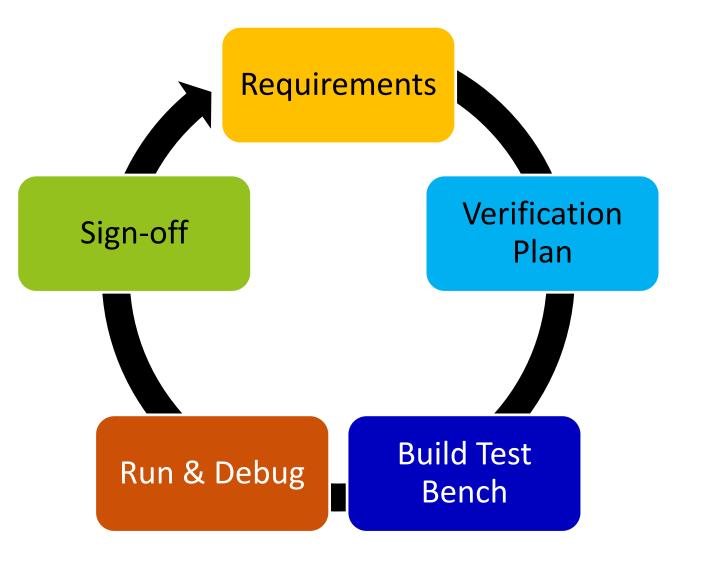

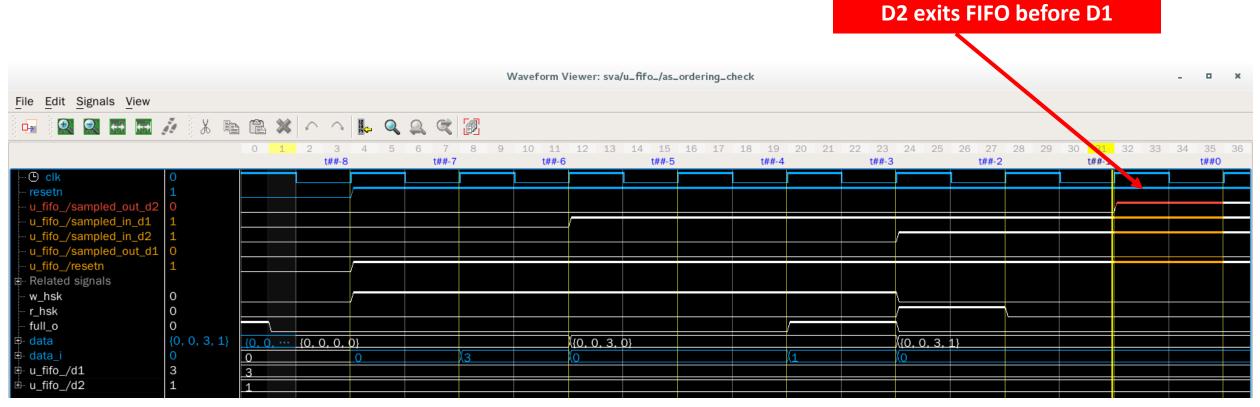

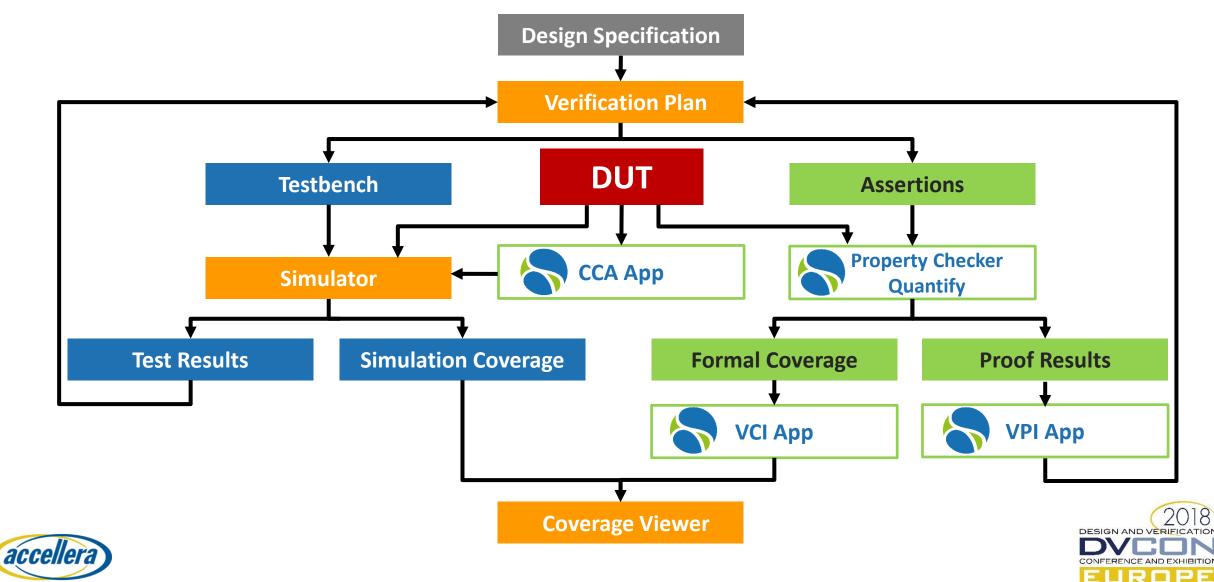

### **The Verification Loop**

# **Assessing the Quality of Verification**

If you don't measure, you don't know

When am I done?

- What part of the design has been exercised by my assertions/covers?

- Have I written **good quality** assertions?

- Which parts of the design have been checked by my assertions?

- Are all specified functions **implemented**?

- Are all specified functions **verified**?

- GapFreeVerification™

# **Coverage & Bug Hunting**

Two sides of the same coin

- Both coverage and bug hunting are important

- Where coverage is *analytical*, bugs are *anecdotal*

- 100% coverage with bugs in the design is unacceptable

- Extracting coverage should be quick and easy

- Report data must be meaningful

# **Inconclusive Formal Coverage**

COI and proof core (ProofCore, FormalCore)

### **Cone-of-Influence**

- Very over-optimistic

- Much logic not relevant for assertion proof

- Proof engines try to trim irrelevant logic

#### **Proof Core**

- Over-optimistic and engine-dependent

- Results hard to interpret\*

- Need support from vendor\*

- Mismatch with abstraction level of other forms of coverage\*

- Makes review process much harder\*

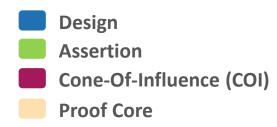

# **Mutation Coverage**

Addressing over optimism of proof core

### **Mutation Analysis Tools**

- Insert mutations into DUT

- **Control**: can the stimulus generator activate the mutation?

- **Observe**: does the mutation propagate to a check that detects it and fails?

Mutation detected == DUT location observed by the testbench

Mutation analysis detects verification errors and gaps

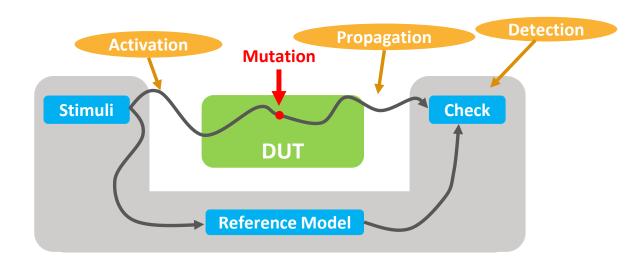

# **Multi-Dimensional Coverage View**

- Has the statement been **activated/controlled**?

- Idea:

- If a statement has not been activated during verification, it can't break a check.

- If a statement has been reached, would a check fail?

- Can measure quality of stimuli

- Has the statement been **detected/observed**?

- Idea:

- If a statement is modified and activated, some checks should fail

- Would any check fail if the statement cannot be reached?

- Can measure quality of checkers

### **Mutation Coverage**

Multi-dimensional view – quantity and quality

Assessing the *quality* of verification by providing a *quantitative* metric

Structural Coverage (Quantity)

Activation & Detection Coverage—provides quantitative assessment

Functional Coverage (Quality)

Assertion Coverage—provides qualitative assessment

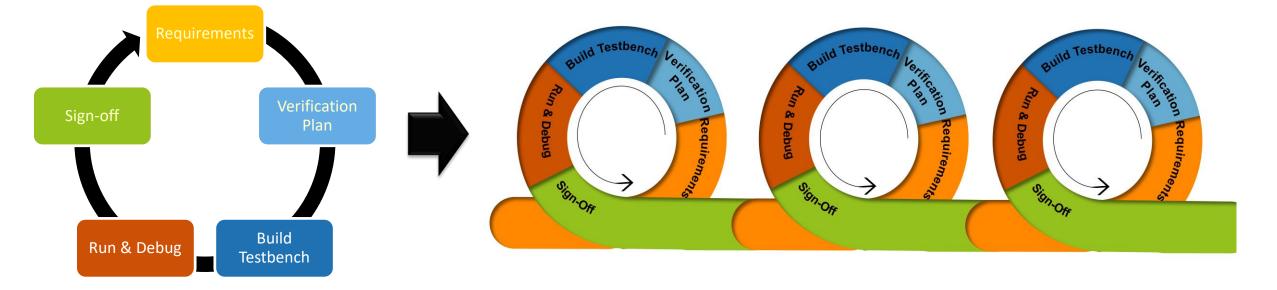

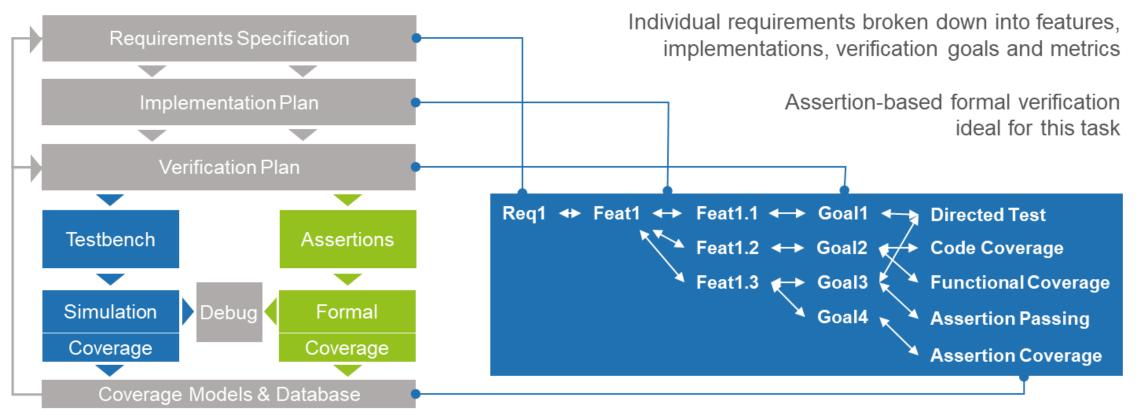

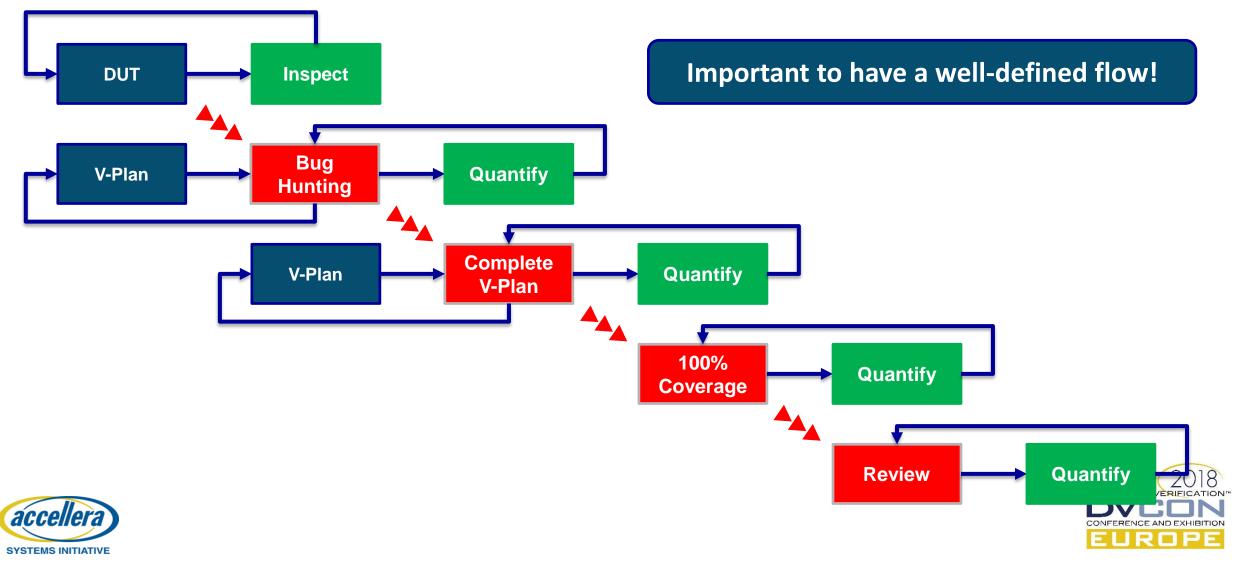

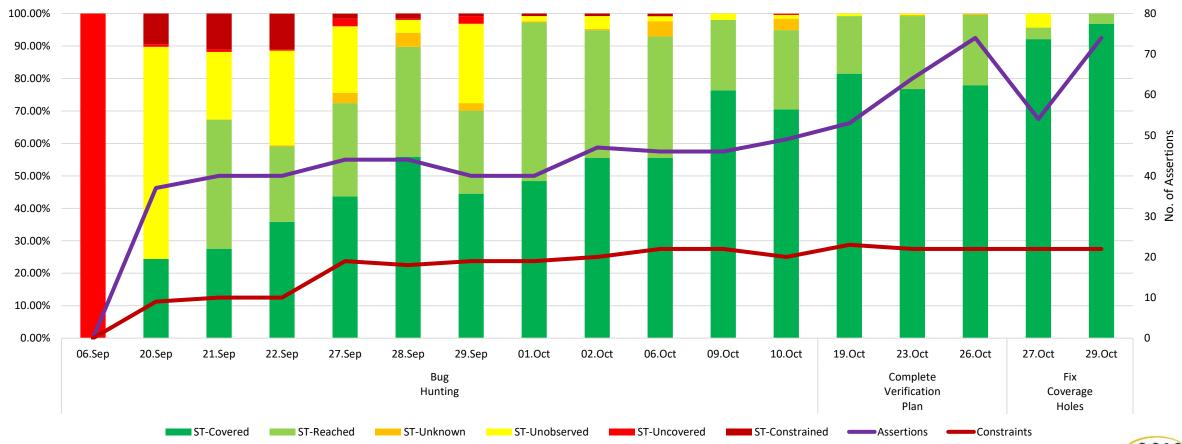

### **Mutation Coverage Use Model for Design Verification**

Iterative signoff flow for bug hunting and 100% coverage

#### **Regular Flow**

### **Iterative Flow**

Used by verification engineers for signoff Can be used both by designers and verification engineers for iterative signoff

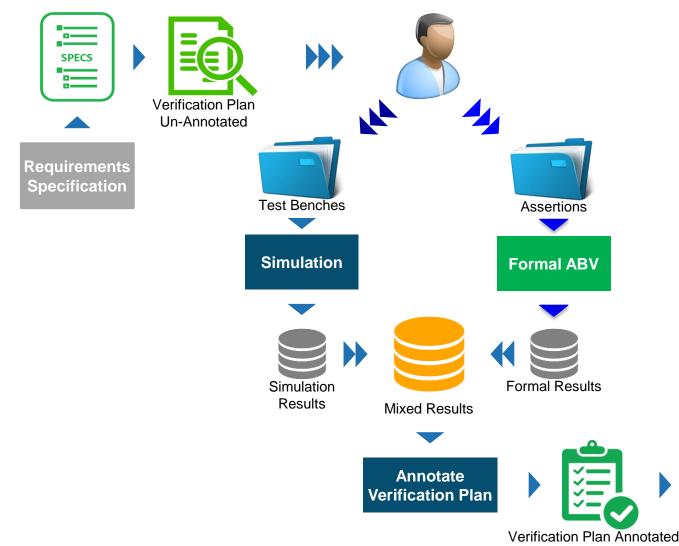

# **Coverage Solution: Provide Meaningful Metrics**

Continuous feedback for design and verification

### **Designer Bring Up: Get feedback on the quality of design**

- Dead code; reachability

- Redundant code

### Verification: When quality and quantity both matter

- Metrics should indicate gaps in verification and show you where these are

- Missing assertions

- Over-constraints

- Find bugs

# **Mutation Coverage Results**

Activation coverage

|                                 | Result      | Meaning                                                |

|---------------------------------|-------------|--------------------------------------------------------|

|                                 | Dead        | Mutation cannot be activated                           |

| Activation /<br>Controllability | Reached     | Mutation activated by at least one assertion (witness) |

|                                 | Constrained | Mutation cannot be activated because of constraints    |

Important to identify which parts of the design are dead and which parts are over-constrained.

As the code is dead or over-constrained, one cannot control it.

# **Mutation Coverage Results**

**Detection coverage**

|                              | Result     | Meaning                                     |

|------------------------------|------------|---------------------------------------------|

|                              | Uncovered  | Mutation not detected by any assertion      |

| Detection /<br>Observability | Covered    | Mutation detected by at least one assertion |

|                              | Unobserved | Mutation activated but not detected         |

Important to assess the *quality* of the assertions

Have we observed all the design signals?

Do we have quality assertions?

# **Additional Coverage Results**

Identify redundant code, report code excluded from analysis

|           | Result       | Meaning                                |

|-----------|--------------|----------------------------------------|

|           | Redundant    | No contribution to design I/O behavior |

| Exclusion | Verification | Only used for verification             |

|           | Excluded     | Excluded by user                       |

### Important to identify redundant code

Assess if the code is redundant in design, or in verification

User can exclude code from coverage analysis

### **Overview of Mutation Coverage Results**

|                                 | Result       |                                       |

|---------------------------------|--------------|---------------------------------------|

|                                 | Reached      |                                       |

| Activation /<br>Controllability | Constrained  |                                       |

|                                 | Dead         | <ul> <li>Verification Hole</li> </ul> |

|                                 | Uncovered    |                                       |

| Detection /<br>Observability    | Unobserved   |                                       |

|                                 | Covered      |                                       |

|                                 | Redundant    |                                       |

| Exclusion                       | Verification |                                       |

|                                 | Excluded     |                                       |

# **Quantify Model-Based Mutation Coverage**

### **User Experience**

- Accurate, familiar metrics

- Detects verification gaps and errors

- Intuitive interface

- Integrates with simulation metrics

- Supports bounded proofs

### **Under The Hood**

- Includes formal-optimised mutation analysis

- Mutations in the model, not RTL

- Parallel mutations and assertions analysis

- Dedicated algorithms

- Patented technology

### **Model-Based Mutations**

- Mutations inserted in the model (post-compile)

- No RTL instrumentation or recompilation required

### **Quantify Dashboard - Key Components**

| Structural Coverage Overview |                               |         |        |              |              |         |                    |              |            |

|------------------------------|-------------------------------|---------|--------|--------------|--------------|---------|--------------------|--------------|------------|

| Status Statements            |                               |         |        |              | Bra          | anche   | es                 |              |            |

| 1                            | covered                       | 12      |        | 80.00%       |              |         |                    | 100.00%      |            |

| R                            | reached                       | 0       | 0.00%  |              |              | 0       | <mark>0.00%</mark> |              |            |

| U                            | unknown                       | 0       | 0.00%  |              |              | 0       | <mark>0.00%</mark> |              |            |

| 0R                           | unobserved                    | 3       |        | 00%          |              | 0       | 0.00%              |              |            |

| 0                            | uncovered                     | 0       | -      |              |              | 0       | 0.00%              |              |            |

| 0C                           | constrained                   | 0       | -      |              |              | 0       | 0.00%              |              |            |

| 0D                           | dead                          | 0       | 0.00%  |              |              | 0       | 0.00%              |              |            |

| Sum                          | quantify targets              | 15      |        |              |              | 4       |                    |              |            |

| Excluded Code Overview       |                               |         |        |              |              |         |                    |              |            |

| Code                         | Status                        | Stateme | nents  |              |              | nches   | 3                  |              |            |

| Xu                           | excluded by user              | 0       | 0.00%  |              |              | 0 0.00% |                    |              |            |

| Xr                           | excluded redundant code       | 0       | 0.00%  |              |              | 0       | 0.00%              |              |            |

| Xv                           | excluded verification code    | 15      |        | 50.00%       |              | 8       | 66.67%             |              |            |

| 0/1/U                        | quantify targets              | 15      |        | 50.00%       |              | 4       | 4 33.33%           |              |            |

| Sum                          | total code                    | 30      |        |              |              | 12      |                    |              |            |

| Asse                         | rtion Coverage                |         |        |              |              |         |                    |              |            |

| ld                           | Property Kind                 |         | Kind   | Proof Result | Proof Radius | С       | over Result        | Cover Radius | Quantified |

| 0                            | sva/as_empty_from_full        | ć       | assert | FORMAL_PROOF | infinite     | С       | OVER_PASS          | 9            | yes        |

| 1                            | sva/as_full_from_empty        | i       | assert | FORMAL_PROOF | infinite     | С       | OVER_PASS          | 1            | yes        |

| 2                            | sva/u fifo /as ordering check |         | assert | FORMAL_PROOF | infinite     |         | OVER_PASS          | 2            | yes        |

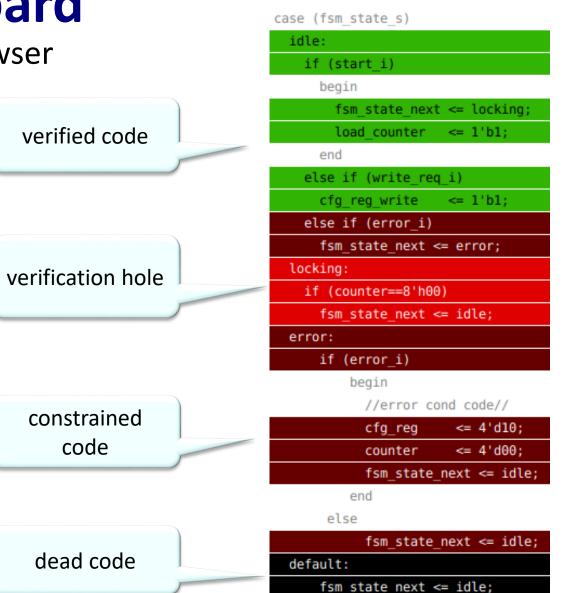

# **Quantify Dashboard**

Directly linked to design browser

endcase

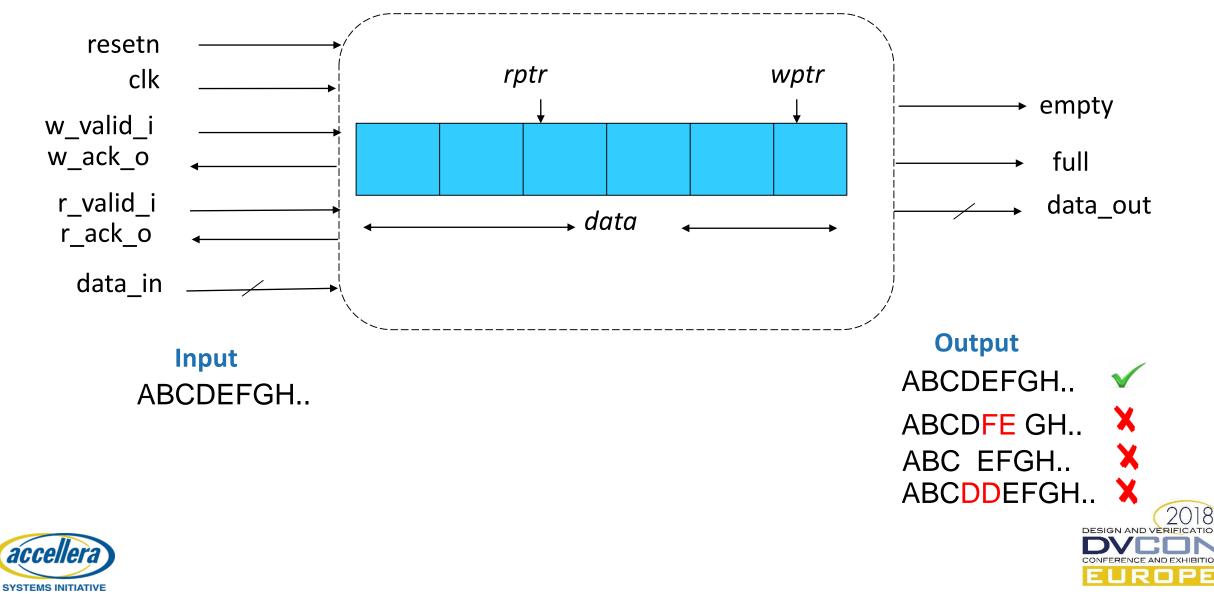

### **Mutation Coverage for Bug Hunting**

**Example: FIFO**

### **FIFO Interface**

### **Requirements for Verification**

### Ordering is correct

No duplication

No data loss

No data corruption

Empty and full flags activation

Must be empty at the right time Must be full at the right time If empty, then eventually full If full, then eventually empty

# Quantify on FIFO Example—I

### With no assertions at all

| Structural Coverage Overview |                  |    |            |   |          |         |  |             |

|------------------------------|------------------|----|------------|---|----------|---------|--|-------------|

| Status                       | Status           |    | Statements |   | Branches |         |  |             |

| 1                            | covered          | 0  | 0.00%      | 0 | 0        | 0.00%   |  |             |

| R                            | reached          | 0  | 0.00%      | 0 | 0        | 0.00%   |  |             |

| U                            | unknown          | 0  | 0.00%      | 0 | 0        | 0.00%   |  |             |

| 0R                           | unobserved       | 0  | 0.00%      | 0 | 0        | 0.00%   |  |             |

| 0                            | uncovered        | 22 | 100.00%    | 7 |          | 100.00% |  | VERIFICATIO |

| 0C                           | constrained      | 0  | 0.00%      | 0 | 0        | 0.00%   |  |             |

| 0D                           | dead             | 0  | 0.00%      | 0 | 0        | 0.00%   |  |             |

| Sum                          | quantify targets | 22 |            | 7 |          |         |  |             |

| Structural Coverage by File |            |          |                   |  |  |  |  |

|-----------------------------|------------|----------|-------------------|--|--|--|--|

| File                        | Statements | Branches |                   |  |  |  |  |

| <u>fifo.v</u>               | 22         | 7        | VERIFICATION HOLE |  |  |  |  |

|                             |            |          |                   |  |  |  |  |

| Assei | rtion Coverage |      |              |              |              |              |            |

|-------|----------------|------|--------------|--------------|--------------|--------------|------------|

| ld    | Property       | Kind | Proof Result | Proof Radius | Cover Result | Cover Radius | Quantified |

| File Status |               |          |        |                                                                  |  |  |  |

|-------------|---------------|----------|--------|------------------------------------------------------------------|--|--|--|

| ld          | File          | Language | Kind   | Full Name                                                        |  |  |  |

| 0           | <u>fifo.v</u> | verilog  | design | /home/onespin/my_labs/fifo_quantify_demo_v2/no_checks/rtl/fifo.v |  |  |  |

### **Quantify on FIFO Example—II**

Design view

| 43       | always @(posedge clk or negedge resetn)                                  |   |

|----------|--------------------------------------------------------------------------|---|

| 44       | if (!resetn)                                                             | 0 |

| 45       | w_sck <= 1'b1;                                                           | 0 |

| 46       | else if (!full)                                                          | 0 |

| 47       | w_ack <= 1'b1;                                                           | 0 |

| 48       | else if (full)                                                           | 0 |

| 49       | w_ack <= 1'b0;                                                           | 0 |

| 50       |                                                                          |   |

| 51       | assign w_ack_o = w_ack;                                                  | 0 |

| 52       | assign r_ack_o = empty ? 1'b0 : (full ? 1'b0 : 1'b1);                    | 0 |

| 53       | assign w_hsk = w_valid_i && w_ack_o;                                     | 0 |

| 54       | assign r_hsk = r_valid_i && r_ack_o;                                     | 0 |

| 55       | assign nxt_wptr = wptr + w_hsk;                                          | 0 |

| 56       | assign nxt_rptr = rptr + r_hsk;                                          | 0 |

| 57       | assign nxt_empty = (empty    r_hsk) && !w_hsk && (nxt_rptr == nxt_wptr); | 0 |

| 58       |                                                                          |   |

| 59       | // Registered calculations for empty, wptr and rptr                      |   |

| 60       | always @(posedge clk or negedge resetn)                                  |   |

| 61       | if (!resetn)                                                             | 0 |

| 62       | begin                                                                    |   |

| 63       | empty <= 1'bl;                                                           | 0 |

| 64       | <pre>wptr &lt;= (DEPTH_BITS(1'b0));</pre>                                | 0 |

| 65       | rptr 🗢 (DEPTH_BITS(1'b0));                                               | 0 |

| 66       | end                                                                      |   |

| 67       | else                                                                     | 0 |

| 68       | begin                                                                    |   |

| 69       | empty <= nxt_empty;                                                      | 0 |

| 70       | wptr <= nxt_wptr;                                                        | 0 |

| 71       | rptr <= nxt_rptr;                                                        | 0 |

| 72       | end                                                                      |   |

| 73       | // Write the data on a w_hsk                                             |   |

| 74       | always @(posedge clk)                                                    |   |

| 75       | if (w_hsk)                                                               | 0 |

| 76       | data[wptr] <= data_i;                                                    | 0 |

| 77       | //··· Read the data on a r_hsk                                           |   |

| 78       | always @(posedge clk)                                                    |   |

| 79       | if (r_hsk)                                                               | 0 |

| 80       | data_int = data[rptr];                                                   | 0 |

| 81       | assign full = !empty && (rptr == wptr);                                  | 0 |

| 82       | assign empty_o = empty;<br>assign full o = full;                         | 0 |

| 83<br>84 | assign full_o = full;<br>assign data_o = data_int;                       | 0 |

| 85       | assign data_o = data_int;<br>endmodule                                   | 0 |

| 00       | enamouste                                                                |   |

# **FIFO Verification Strategy**

Uses symbolic and data abstraction

- Use two symbolic transactions for tracking all possible data values

- Send these symbolic values in a pre-determined order in the FIFO

- Ensure that they come out of the FIFO in the same order

- Use four sampling registers

- sampled\_in\_d1

- sampled\_in\_d2

- sampled\_out\_d1

- sampled\_out\_d2

- One side constraint

- One main ordering assertion

## **FIFO Ordering Properties**

Glue logic

```

//-- Force d1 inside before d2

am_d1_before_d2:

assume property (

@(posedge clk)

!sampled_in_d1 |-> !sampled_in_d2);

```

## **Quantify on FIFO Example—III**

### With just ordering assertion

| Struct | tural Coverage Overview |    |                     |          |                |  |                           |

|--------|-------------------------|----|---------------------|----------|----------------|--|---------------------------|

| Status | Status Statements       |    | Branchos            |          |                |  |                           |

| 1      | covered                 | 14 | 63.64%              | 63.64% 0 | lesign covered |  |                           |

| R      | reached                 | 0  | 0.00%               | 0        | 0.00%          |  |                           |

| U      | unknown                 | 0  | 0.00%               | 0        | 0.00%          |  |                           |

| 0R     | unobserved              | 7  | <mark>31.82%</mark> | 2        | 28.57%         |  | 31.82% Design Unobserved  |

| 0      | uncovered               | 1  | 4.55%               | 4.55% De | sign Uncovered |  | J1.82/0 Design Onobserved |

| 0C     | constrained             | 0  | 0.00%               | 0        | 0.00%          |  |                           |

| 0D     | dead                    | 0  | 0.00%               | 0        | 0.00%          |  |                           |

| Sum    | quantify targets        | 22 |                     | 7        |                |  |                           |

| Exclu       | Excluded Code Overview     |            |        |  |          |        |  |  |

|-------------|----------------------------|------------|--------|--|----------|--------|--|--|

| Code Status |                            | Statements |        |  | Branches | s      |  |  |

| Xu          | excluded by user           | 0          | 0.00%  |  | 0        | 0.00%  |  |  |

| Xr          | excluded redundant code    | 0          | 0.00%  |  | 0        | 0.00%  |  |  |

| Xv          | excluded verification code | 14         | 38.89% |  | 4        | 36.36% |  |  |

| 0/1/U       | quantify targets           | 22         | 61.11% |  | 7        | 63.64% |  |  |

| Sum         | total code                 | 36         |        |  | 11       |        |  |  |

| Structural Coverage by File |            |          |  |  |  |  |  |

|-----------------------------|------------|----------|--|--|--|--|--|

| File                        | Statements | Branches |  |  |  |  |  |

| <u>fifo.v</u>               | 22         | 7        |  |  |  |  |  |

| <u>fifo_sva.sv</u>          | 14         | 4        |  |  |  |  |  |

| Ass | Assertion Coverage              |        |                   |              |              |              |            |

|-----|---------------------------------|--------|-------------------|--------------|--------------|--------------|------------|

| ld  | Property                        | Kind   | Proof Result      | Proof Radius | Cover Result | Cover Radius | Quantified |

| 0   | sva/u fifo /as ordering check   | assert | FORMAL_PROOF      | infinite     | COVER_PASS   | 2            | yes        |

| 1   | sva/u fifo /am d1 before d2     | assume | FORMAL_ASSUMPTION | infinite     | N/A          | 0            | N/A        |

| 2   | <u>sva/u fifo /am intf full</u> | assume | FORMAL_ASSUMPTION | infinite     | N/A          | 0            | N/A        |

| 3   | <u>sva/u fifo /am stable d1</u> | assume | FORMAL_ASSUMPTION | infinite     | N/A          | 0            | N/A        |

| 4   | <u>sva/u fifo /am stable d2</u> | assume | FORMAL_ASSUMPTION | infinite     | N/A          | 0            | N/A        |

| File | File Status   |          |        |                                                                                       |  |  |  |

|------|---------------|----------|--------|---------------------------------------------------------------------------------------|--|--|--|

| ld   | File          | Language | Kind   | Full Name                                                                             |  |  |  |

| 0    | <u>fifo.v</u> | verilog  | design | /home/onespin/my_labs/fifo_quantify_demo_v2/Step2_ordering_check_only/rtl/fifo.v      |  |  |  |

| 1    | fifo_sva.sv   | verilog  | design | /home/onespin/my_labs/fifo_quantify_demo_v2/Step2_ordering_check_only/sva/fifo_sva.sv |  |  |  |

# **Quantify on FIFO Example—IV**

### What is still missing?

accellera

SYSTEMS INITIATIVE

| 41       | if (!resetn)                                                                                                 | 0R       |

|----------|--------------------------------------------------------------------------------------------------------------|----------|

| 41       | w ack <= 1'b1;                                                                                               | 0R<br>0R |

| 42       |                                                                                                              | 0R       |

|          | else if (!full)                                                                                              | 0R       |

| 44       | w_ack <= 1'b1;                                                                                               | 0R       |

| 45       | else if (full)                                                                                               | 0        |

| 46       | w_ack <= 1'b0;                                                                                               | U        |

| 47       |                                                                                                              | 0.0      |

| 48<br>49 | assign w_ack_o = w_ack;                                                                                      | 0R       |

| 49<br>50 | <pre>//assign r_ack_o = empty ? 1'b0: 1'b1;</pre>                                                            | 1        |

| 50       | assign r_ack_o = empty ? 1'b0 : (full ? 1'b0 : 1'b1);                                                        | 0R       |

| 51       | assign w_hsk = w_valid_i && w_ack_o;                                                                         | 1        |

| 52       | assign r_hsk = r_valid_i && r_ack_o;                                                                         | 1        |

| 55       | assign nxt_wptr = wptr + w_hsk;                                                                              | 1        |

| 55       | assign nxt_rptr  = rptr + r_hsk;<br>assign nxt_empty = (empty    r_hsk) && !w_hsk && (nxt_rptr == nxt_wptr); | 1        |

| 56       | // Registered calculations for empty, wptr and rptr                                                          |          |

| 57       | always @(posedge clk or negedge resetn)                                                                      |          |

| 58       | if (lresetn)                                                                                                 | 1        |

| 59       | begin                                                                                                        |          |

| 60       | empty <= 1'b1;                                                                                               | 0R       |

| 61       | wptr <= {DEPTH BITS{1'b0}};                                                                                  | 1        |

| 62       | rptr <= {DEPTH_BITS(1'b0}};                                                                                  | 1        |

| 63       | end                                                                                                          |          |

| 64       | else                                                                                                         | 1        |

| 65       | begin                                                                                                        |          |

| 66       | empty <= nxt_empty;                                                                                          | 1        |

| 67       | <pre>wptr &lt;= nxt_wptr;</pre>                                                                              | 1        |

| 68       | <pre></pre>                                                                                                  | 1        |

| 69       | end                                                                                                          |          |

| 70       | // Write the data on a w hsk                                                                                 |          |

| 71       | always @(posedge clk)                                                                                        |          |

| 72       | if (w hsk)                                                                                                   | 1        |

| 73       | data[wptr] <= data_i;                                                                                        | 1        |

| 74       | // Read the data on a r hsk                                                                                  |          |

| 75       | always @(posedge clk)                                                                                        |          |

| 76       | if (r_hsk)                                                                                                   | 1        |

| 77       | <pre>data_int &lt;= data[rptr];</pre>                                                                        | 1        |

| 78       | assign full = lempty && (rptr == wptr);                                                                      | 1        |

| 79       | assign empty o = empty;                                                                                      | 0R       |

| 80       | assign full o = full;                                                                                        | 0R       |

| 81       | assign data_o = data_int;                                                                                    | 1        |

| 82       | endmodule                                                                                                    |          |

### **Missing Coverage**

- Unobserved

- Uncovered

## **Quantify on FIFO Example—V**

Let's add assertions on full and empty

```

as_empty_to_full:

assert property (@(posedge clk) disable iff (!resetn)

empty_o ##1 (push_i && !pop_i)[*FIFO_DEPTH] |=> full_o);

```

```

as_full_to_empty:

assert property (@(posedge clk) disable iff (!resetn)

full_o ##1 (pop_i && !push_i)[*FIFO_DEPTH] |=> empty_o);

```

```

as_empty_after_reset:

assert property (@(posedge clk) !resetn |=> empty);

```

### **Quantify on FIFO Example—VI**

### Now, how are we doing?

| Struct | structural Coverage Overview |           |        |  |         |                    |                       |

|--------|------------------------------|-----------|--------|--|---------|--------------------|-----------------------|

| Status |                              | Statement | ts     |  | Branche | s                  |                       |

| 1      | covered                      | 16        | 72.73% |  |         |                    | 72.73% design covered |

| R      | reached                      | 0         | 0.00%  |  | 0       | 0.00%              |                       |

| U      | unknown                      | 0         | 0.00%  |  | 0       | <mark>0.00%</mark> |                       |

| 0R     | unobserved                   | 6         | 27.27% |  | 3       |                    | 42.86%                |

| 0      | uncovered                    | 0         | 0.00%  |  | 0       | 0.00%              |                       |

| 0C     | constrained                  | 0         | 0.00%  |  | 0       | 0.00%              |                       |

| 0D     | dead                         | 0         | 0.00%  |  | 0       | 0.00%              |                       |

| Sum    | quantify targets             | 22        |        |  | 7       |                    |                       |

| Exclu       | Excluded Code Overview     |            |        |    |        |  |  |  |  |

|-------------|----------------------------|------------|--------|----|--------|--|--|--|--|

| Code Status |                            | Statements |        |    | ;      |  |  |  |  |

| Xu          | excluded by user           | 0          | 0.00%  | 0  | 0.00%  |  |  |  |  |

| Xr          | excluded redundant code    | 0          | 0.00%  | 0  | 0.00%  |  |  |  |  |

| Xv          | excluded verification code | 14         | 38.89% | 4  | 36.36% |  |  |  |  |

| 0/1/U       | quantify targets           | 22         | 61.11% | 7  | 63.64% |  |  |  |  |

| Sum         | total code                 | 36         |        | 11 |        |  |  |  |  |

| Structural Coverage by File |            |          |  |  |  |  |  |  |

|-----------------------------|------------|----------|--|--|--|--|--|--|

| File                        | Statements | Branches |  |  |  |  |  |  |

| <u>fifo.v</u>               | 22         | 7        |  |  |  |  |  |  |

| fifo_sva.sv                 | 14         | 4        |  |  |  |  |  |  |

| Ass | ertion Coverage                  |        |                   |              |               |              |            |

|-----|----------------------------------|--------|-------------------|--------------|---------------|--------------|------------|

| ld  | Property                         | Kind   | Proof Result      | Proof Radius | Cover Result  | Cover Radius | Quantified |

| 0   | sva/u fifo /as empty after reset | assert | FORMAL_PROOF      | infinite     | COVER_PASS    | 1            | yes        |

| 1   | sva/u fifo /as empty to full     | assert | FORMAL_PROOF      | infinite     | COVER_PASS    | 1            | yes        |

| 2   | sva/u fifo /as full to empty     | assert | FORMAL_VACUOUS    | infinite     | COVER_VACUOUS | infinite     | no         |

| 3   | sva/u fifo /as ordering check    | assert | FORMAL_PROOF      | infinite     | COVER_PASS    | 2            | yes        |

| 4   | sva/u fifo /am d1 before d2      | assume | FORMAL_ASSUMPTION | infinite     | N/A           | 0            | N/A        |

| 5   | <u>sva/u fifo /am intf full</u>  | assume | FORMAL_ASSUMPTION | infinite     | N/A           | 0            | N/A        |

| 6   | <u>sva/u fifo /am stable d1</u>  | assume | FORMAL_ASSUMPTION | infinite     | N/A           | 0            | N/A        |

| 7   | <u>sva/u fifo /am stable d2</u>  | assume | FORMAL_ASSUMPTION | infinite     | N/A           | 0            | N/A        |

| File S | File Status   |          |        |                                                                                          |  |  |  |

|--------|---------------|----------|--------|------------------------------------------------------------------------------------------|--|--|--|

| ld     | File          | Language | Kind   | Full Name                                                                                |  |  |  |

| 0      | <u>fifo.v</u> | verilog  | design | /home/onespin/my_labs/fifo_quantify_demo_v2/Step3_with_empty_full_checks/rtl/fifo.v      |  |  |  |

| 1      | fifo_sva.sv   | verilog  | design | /home/onespin/my_labs/fifo_quantify_demo_v2/Step3_with_empty_full_checks/sva/fifo_sva.sv |  |  |  |

## **Quantify on FIFO Example—VII**

What are the missing coverage targets?

| 42       | if (!resetn)                                                             | 0R |

|----------|--------------------------------------------------------------------------|----|

| 13       | w_ack <= 1'b1;                                                           | 0R |

| 4        | else if (!full)                                                          | 0R |

| 5        | w_ack <= 1'b1;                                                           | 0R |

| 16       | else if (full)                                                           | 0R |

| 17       | w ack <= 1 b0;                                                           | 0R |

| 8        |                                                                          |    |

| 19       | assign w ack o = w ack;                                                  | 0R |

| 50       | assign r_ack_o = empty ? 1'b0 : (full ? 1'b0 : 1'b1);                    | 1  |

| 51       | assign w hsk = w valid i && w ack_o;                                     | 0R |

| 52       | assign r_hsk = r_valid_i && r_ack_o;                                     | 1  |

| 53       | assign nxt_wptr = wptr + w_hsk;                                          | 1  |

| 54       | assign nxt_rptr = rptr + r_hsk;                                          | 1  |

| 55       | assign nxt empty = (empty    r hsk) && lw hsk && (nxt_rptr == nxt_wptr); | 1  |

| 56       | // Registered calculations for empty, wptr and rptr                      |    |

| 57       | always @(posedge clk or negedge resetn)                                  |    |

| 58       | if (lresetn)                                                             | 1  |

| 9        | begin                                                                    |    |

| 60       | empty <= 1'bl;                                                           | 1  |

| 61       | <pre>wptr &lt;= {DEPTH BITS(1'b0)};</pre>                                | 1  |

| 62       | <pre>rptr &lt;= {DEPTH_BITS{1'b0}};</pre>                                | 1  |

| 33       | end                                                                      |    |

| 54       | else                                                                     | 1  |

| 35       | begin                                                                    |    |

| 66       | <pre>empty &lt;= nxt_empty;</pre>                                        | 1  |

| 67       | <pre>wptr &lt;= nxt_wptr;</pre>                                          | 1  |

| 58<br>58 | rptr <= nxt_rptr;                                                        | 1  |

| 59<br>59 | end                                                                      |    |

| 70       | ***                                                                      |    |

| 71       | // Write the data on a w hsk                                             |    |

| 2        | always @(posedge clk)                                                    |    |

| 73       | if (w_hsk)                                                               | 1  |

| 74       | data[wptr] <= data_i;                                                    | 1  |

| 75       | ence[ukci] = ence_t)                                                     |    |

| 76       | // Read the data on a r_hsk                                              |    |

| 7        | always @(posedge clk)                                                    |    |

| '8       | if (r hsk)                                                               | 1  |

| 79       | data_int <= data[rptr];                                                  | 1  |

| 30       | anna-thair a marafrite (1)                                               |    |

| 31       | assign full = !empty && (rptr == wptr);                                  | 1  |

| 32       | assign null = :empty and (ipt) == wpt);                                  | 0R |

| 33       | assign full_o = full;                                                    | 1  |

| 33<br>34 | assign data_o = data_int;                                                | 1  |

| 35       | endmodule                                                                |    |

### **Missing Coverage**

- Unobserved code

- Cannot observe "empty"!

# **Quantify on FIFO Example—VIII**

A closer look

| 42 | if (!resetn)                                         | 0   |

|----|------------------------------------------------------|-----|

| 43 | w_ack <= 1'b1;                                       | 0 🥍 |

| 44 | else if (!full)                                      | 0R  |

| 45 | w_ack <= 1'b1;                                       | 0R  |

| 46 | else if (full)                                       | 0R  |

| 47 | w_ack <= 1'b0;                                       | 0R  |

| 48 |                                                      |     |

| 49 | assign w_ack_o = w_ack;                              | 0R  |

| 50 | assign r_ack_o = empty ? 1'b : (full ? 1'b0 : 1'b1); | 1   |

| 51 | assign w_hsk = w_valid_i && w_ack_o;                 | 0R  |

### This looks buggy ... Let's go and fix it!

### **Quantify on FIFO Example—IX**

After the fix on r\_ack\_o, coverage has increased

| Struct | ural Coverage Overview |           |        |        |                       |         |                        |

|--------|------------------------|-----------|--------|--------|-----------------------|---------|------------------------|

| Status |                        | Statement | ts     | Branch | es                    |         |                        |

| 1      | covered                | 17        | 77.27% |        | 77.27% design covered |         |                        |

| R      | reached                | 0         | 0.00%  | 0      | 0.00%                 |         |                        |

| U      | unknown                | 0         | 0.00%  | 0      | 0.00%                 |         |                        |

| 0R     | unobserved             | 5         | 22.73% | 3      | 42.86%                | Still 2 | 2.7% design unobserved |

| 0      | uncovered              | 0         | 0.00%  | 0      | 0.00%                 |         |                        |

| 0C     | constrained            | 0         | 0.00%  | 0      | 0.00%                 |         |                        |

| 0D     | dead                   | 0         | 0.00%  | 0      | 0.00%                 |         |                        |

| Sum    | quantify targets       | 22        |        | 7      |                       |         |                        |

| Exclu  | Excluded Code Overview     |          |        |  |          |        |  |  |  |  |

|--------|----------------------------|----------|--------|--|----------|--------|--|--|--|--|

| Code S | Status                     | Statemen | ts     |  | Branches | s      |  |  |  |  |

| Xu     | excluded by user           | 0        | 0.00%  |  | 0        | 0.00%  |  |  |  |  |

| Xr     | excluded redundant code    | 0        | 0.00%  |  | 0        | 0.00%  |  |  |  |  |

| Xv     | excluded verification code | 14       | 38.89% |  | 4        | 36.36% |  |  |  |  |

| 0/1/U  | quantify targets           | 22       | 61.11% |  | 7        | 63.64% |  |  |  |  |

| Sum    | total code                 | 36       |        |  | 11       |        |  |  |  |  |

Coverage has increased to 77.27%

| Structural Coverage by File |            |          |  |  |  |  |  |  |

|-----------------------------|------------|----------|--|--|--|--|--|--|

| File                        | Statements | Branches |  |  |  |  |  |  |

| <u>fifo.v</u>               | 22         | 7        |  |  |  |  |  |  |

| <u>fifo_sva.sv</u>          | 14         | 4        |  |  |  |  |  |  |

| Assertion Coverage |                                  |        |                   |              |              |              |            |  |  |

|--------------------|----------------------------------|--------|-------------------|--------------|--------------|--------------|------------|--|--|

| ld                 | Property                         | Kind   | Proof Result      | Proof Radius | Cover Result | Cover Radius | Quantified |  |  |

| 0                  | sva/u fifo /as_empty_after_reset | assert | FORMAL_PROOF      | infinite     | COVER_PASS   | 1            | yes        |  |  |

| 1                  | sva/u fifo /as empty to full     | assert | FORMAL_PROOF      | infinite     | COVER_PASS   | 1            | yes        |  |  |

| 2                  | sva/u fifo /as full to empty     | assert | FORMAL_PROOF      | infinite     | COVER_PASS   | 5            | yes        |  |  |

| 3                  | sva/u fifo /as ordering check    | assert | FORMAL_PROOF      | infinite     | COVER_PASS   | 2            | yes        |  |  |

| 4                  | sva/u fifo /am d1 before d2      | assume | FORMAL_ASSUMPTION | infinite     | N/A          | 0            | N/A        |  |  |

| 5                  | <u>sva/u fifo /am intf_full</u>  | assume | FORMAL_ASSUMPTION | infinite     | N/A          | 0            | N/A        |  |  |

| 6                  | sva/u fifo /am stable d1         | assume | FORMAL_ASSUMPTION | infinite     | N/A          | 0            | N/A        |  |  |

| 7                  | sva/u fifo /am stable d2         | assume | FORMAL_ASSUMPTION | infinite     | N/A          | 0            | N/A        |  |  |

| Fi | File Status   |          |        |                                                                                                                 |  |  |  |  |  |

|----|---------------|----------|--------|-----------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| ld | File          | Language | Kind   | Full Name                                                                                                       |  |  |  |  |  |

| 0  | <u>fifo.v</u> | verilog  | design | /home/onespin/my_labs/fifo_quantify_demo_v2/Step4_ordering_empty_and_full_checks_but_fix_rack_o/rtl/fifo.v      |  |  |  |  |  |

| 1  | fifo_sva.sv   | verilog  | design | /home/onespin/my_labs/fifo_quantify_demo_v2/Step4_ordering_empty_and_full_checks_but_fix_rack_o/sva/fifo_sva.sv |  |  |  |  |  |

### But still missing 22.7%!

## Quantify on FIFO Example—X

Let's dig deeper to find out why

| 42   | if (!resetn)                                                             | 0R                  |

|------|--------------------------------------------------------------------------|---------------------|

| 43   | w_ack <= 1'b1;                                                           | OR OR               |

| 44   | else if (!full)                                                          | OR                  |

| 45   | w_ack <= 1'b1;                                                           |                     |

| 46   | else if (full)                                                           |                     |

| 47   | w_ack <= 1'b0;                                                           |                     |

| 48   |                                                                          |                     |

| 49   | assign w_ack_o = w_ack;                                                  |                     |

| 50   | // Let's fix the r_ack_o                                                 |                     |

| 51   | assign r_ack_o = empty ? 1'b0 : 1'b1;                                    |                     |

| 52   | assign w_hsk = w_valid_i && w_ack_o;                                     |                     |

| 53   | assign r_hsk = r_valid_i && r_ack_o;                                     |                     |

| 54   | assign nxt_wptr = wptr + w_hsk;                                          |                     |

| 55   | assign nxt_rptr = rptr + r_hsk;                                          |                     |

| 56   | assign nxt_empty = (empty    r_hsk) && !w_hsk && (nxt_rptr == nxt_wptr); |                     |

| 57   | // Registered calculations for empty, wptr and rptr                      |                     |

| 58   | always @(posedge clk or negedge resetn)                                  |                     |

| 59   | if (!resetn)                                                             | Missing covorage on |

| 60   | begin                                                                    | Missing coverage on |

| 61   | empty <= 1'b1;                                                           |                     |

| 62   | <pre>wptr &lt;= {DEPTH_BITS{1'b0}};</pre>                                |                     |

| 63   | <pre>rptr &lt;= {DEPTH_BITS{1'b0}};</pre>                                | w_ack and w_hsk     |

| 64   | end                                                                      |                     |

| 65   | else                                                                     |                     |

| 66   | begin                                                                    |                     |

| 67   | empty <= nxt_empty;                                                      |                     |

| 68   | <pre>wptr &lt;= nxt_wptr;</pre>                                          | 1                   |

| 69   | <pre>rptr &lt;= nxt_rptr;</pre>                                          |                     |

| 70   | end                                                                      | Unobserved code     |

| 71   | // Write the data on a w_hsk                                             |                     |

| 72   | always @(posedge clk)                                                    |                     |

| 73   | if (w hsk)                                                               |                     |

| 74   | data[wptr] <= data i;                                                    |                     |

| 75   | // Read the data on a r_hsk                                              |                     |

| 76   | always @(posedge clk)                                                    |                     |

| 77   | if (r hsk)                                                               |                     |

| 78   | data int <= data[rptr];                                                  |                     |

| 79   | assign full = !empty && (rptr == wptr);                                  |                     |

| 80   | assign empty_o = empty;                                                  |                     |

| 81   | assign full_o = full;                                                    |                     |

| 82   | assign data_o = data_int;                                                |                     |

| 83   | endmodule                                                                | CONFERENCE AND E    |

| - 00 | chamodate                                                                |                     |

EXHIBIT

SYSTEMS INITIATIVE

## **Quantify on FIFO Example—XI**

Let's add the remainder properties

# **Quantify on FIFO Example—XII**

### How are we doing now?

| Branches                                | Statements                                          | Stateme                                                                                                     | Status State                                                                                 |                                     |  |

|-----------------------------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------|--|

| 90.91%                                  | 20 90                                               | e <b>d</b> 20                                                                                               | covered                                                                                      | 1                                   |  |

| 6                                       | 0.00%                                               | d 0                                                                                                         | reached                                                                                      | R                                   |  |

| δ0 0 0.                                 | 0.00%                                               | vn 0                                                                                                        | unknown                                                                                      | U                                   |  |

| Still 9.09% de                          | 2 9.09%                                             | erved 2                                                                                                     | unobserved                                                                                   | 0R                                  |  |

|                                         | 0 0.00%                                             | ored 0                                                                                                      | uncovered                                                                                    | 0                                   |  |

|                                         | 0.00%                                               | ained 0                                                                                                     | constrained                                                                                  | 0C                                  |  |

| 6 0 <mark>0</mark> .                    |                                                     |                                                                                                             |                                                                                              | 00                                  |  |

| -                                       | 0 0.00%                                             | 0                                                                                                           | dead                                                                                         | 0D                                  |  |

| -                                       | 0 0.00%<br>22                                       | fy targets 22                                                                                               | quantify targets                                                                             | Sum                                 |  |

| 6 0 0.<br>7 7                           | 22                                                  | fy targets 22<br>de Overview                                                                                | quantify targets                                                                             | Sum<br>Exclue                       |  |

| 6 0 0.<br>7 7<br>Branches               | 22<br>Statements                                    | fy targets 22<br>de Overview Stateme                                                                        | quantify targets<br>ded Code Overview<br>itatus                                              | Sum<br>Exclue<br>Code S             |  |

| 6 0 0.<br>7 5<br>6 0 0 0                | 22<br>Statements<br>0 0.00%                         | ty targets 22<br>de Overview<br>Stateme<br>ed by user 0                                                     | quantify targets<br>ded Code Overview<br>status<br>excluded by user                          | Sum<br>Exclue<br>Code S<br>Xu       |  |

| 6 0 0<br>7 2<br>6 0 0<br>6 0 0<br>6 0 0 | 22 Statements 0 0.00% 0 0.00%                       | ty targets 22<br>de Overview<br>Stateme<br>ed by user 0                                                     | quantify targets<br>ded Code Overview<br>itatus                                              | Sum<br>Exclue<br>Code S             |  |

| 6 0 0.<br>7 5<br>6 0 0 0                | 22 Statements 0 0.00% 0 0.00%                       | ty targets 22<br>de Overview<br>Stateme<br>ed by user 0<br>ed redundant code 0                              | quantify targets<br>ded Code Overview<br>status<br>excluded by user                          | Sum<br>Exclue<br>Code S<br>Xu       |  |

| 6 0 0<br>7 2<br>6 0 0<br>6 0 0<br>6 0 0 | 22<br>Statements<br>0 0.00%<br>0 0.00%<br>14 38.89% | ty targets 22<br>de Overview<br>Stateme<br>ed by user 00<br>ed redundant code 00<br>ed verification code 14 | quantify targets<br>ded Code Overview<br>status<br>excluded by user<br>excluded redundant of | Sum<br>Exclue<br>Code S<br>Xu<br>Xr |  |

| Structural Coverage by | by File    |          |  |  |  |  |  |  |  |

|------------------------|------------|----------|--|--|--|--|--|--|--|

| File                   | Statements | Branches |  |  |  |  |  |  |  |

| <u>fifo.v</u>          | 22         | 7        |  |  |  |  |  |  |  |

| fifo_sva.sv            | 14         | 4        |  |  |  |  |  |  |  |

| ld | Property                             | Kind   | Proof Result      | Proof Radius | Cover Result | Cover Radius | Quantified |

|----|--------------------------------------|--------|-------------------|--------------|--------------|--------------|------------|

| 0  | sva/u_fifo_/as_empty_after_reset     | assert | FORMAL_PROOF      | infinite     | COVER_PASS   | 1            | yes        |

| 1  | sva/u_fifo_/as_empty_to_full         | assert | FORMAL_PROOF      | infinite     | COVER_PASS   | 1            | yes        |

| 2  | sva/u_fifo_/as_full_to_empty         | assert | FORMAL_PROOF      | infinite     | COVER_PASS   | 5            | yes        |

| 3  | sva/u_fifo_/as_ordering_check        | assert | FORMAL_PROOF      | infinite     | COVER_PASS   | 2            | yes        |

| 4  | sva/u_fifo_/as_rhsk_infinitely_often | assert | FORMAL_PROOF      | infinite     | COVER_PASS   | 2            | yes        |

| 5  | sva/u_fifo_/as_whsk_infinitely_often | assert | FORMAL_PROOF      | infinite     | COVER_PASS   | 2            | yes        |

| 6  | sva/u_fifo_/am_d1_before_d2          | assume | FORMAL_ASSUMPTION | infinite     | N/A          | 0            | N/A        |

| 7  | sva/u_fifo_/am_fair_rvalid           | assume | FORMAL_ASSUMPTION | infinite     | N/A          | 0            | N/A        |

| 8  | sva/u_fifo_/am_fair_wvalid           | assume | FORMAL_ASSUMPTION | infinite     | N/A          | 0            | N/A        |

| 9  | sva/u_fifo_/am_intf_full             | assume | FORMAL_ASSUMPTION | infinite     | N/A          | 0            | N/A        |

| 10 | sva/u_fifo_/am_stable_d1             | assume | FORMAL_ASSUMPTION | infinite     | N/A          | 0            | N/A        |

| 11 | <u>sva/u fifo /am stable_d2</u>      | assume | FORMAL_ASSUMPTION | infinite     | N/A          | 0            | N/A        |

| File Status |               |          |        |                                                                   |  |  |  |

|-------------|---------------|----------|--------|-------------------------------------------------------------------|--|--|--|

| ld          | File          | Language | Kind   | Full Name                                                         |  |  |  |

| 0           | <u>fifo.v</u> | verilog  | design | /home/onespin/my_labs/fifo_quantify_demo_v3/Step5/rtl/fifo.v      |  |  |  |

| 1           | fifo_sva.sv   | verilog  | design | /home/onespin/my_labs/fifo_quantify_demo_v3/Step5/sva/fifo_sva.sv |  |  |  |

### **Coverage has increased to 90.91%**

At this stage, if we didn't have Quantify we would most certainly signoff the verification as we have:

- Exhaustive Proofs

- No conflicting constraints

- No vacuous proofs

- A very high metric in 90.91%

#### But last 10% unobserved makes us think!

• Cannot signoff yet!

# **Quantify on FIFO Example—XIII**

So, what's going on?

| 43 | if (!resetn)    | 0R |

|----|-----------------|----|

| 44 | w_ack <= 1'b1;  | 0R |

| 45 | else if (!full) | 1  |

| 46 | w_ack <= 1'b1;  | 1  |

| 47 | else if (full)  | 0R |

| 48 | w_ack <= 1'b0;  | 0R |

In the cycle, if the FIFO is full, then we should not accept another write.

However, we only delay the write in the following cycle.

So it looks like we are allowing the write to a full FIFO!

But ... my proofs should have failed .... Why didn't the ordering proof fail?

## **Quantify on FIFO Example—XIV**

Let's look at the constraints

| 33 |                                                                           |

|----|---------------------------------------------------------------------------|

| 34 | // Interface contraints                                                   |

| 35 | <pre>am_intf_full: assume property (full_o  -&gt; !w_hsk    r_hsk);</pre> |

| 36 |                                                                           |

When the FIFO is full, this constraint forces a read in the same cycle when there is a write.

Let's take this constraint away ... and rerun the proofs.

### **Quantify on FIFO Example—XV**

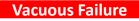

What happens to the proofs? Two assertions fail!

| 🗟 Design Exp  | Iorer 🗵 🛛 🗟 Lint Browser 🗵 🛛 🗑 Auto Checks 🗵      | 🗑 Dead-Code                 | Checks 🗵 🛛 👇 Asse                                                          | rtion Checks 🔯            |

|---------------|---------------------------------------------------|-----------------------------|----------------------------------------------------------------------------|---------------------------|

| 🧭 Proof Sta   | itus: mixed Validity: up to date                  |                             |                                                                            |                           |

| nstance /     | Name                                              | A Proof Sta                 | tus Nitness Statu:                                                         | Validity                  |

| - 🗄 [top]     |                                                   | ▼ ! <any p="" st<=""></any> | atu: 👻 ! 🛛 <any si="" td="" 👻<=""><td>! <any validity=""></any></td></any> | ! <any validity=""></any> |

|               | Assertions                                        |                             |                                                                            |                           |

|               | sva/u_fifo_/as_empty_after_reset                  | hold                        | pass (1)                                                                   | up_to_date                |

|               | sva/u_fifo_/as_empty_to_full                      | fail (1                     | pass (1)                                                                   | up_to_date                |

|               | sva/u_fifo_/as_full_to_empty                      | hold                        | pass (5)                                                                   | up_to_date                |

|               | sva/u_fifo_/as_ordering_check                     | fail (8                     | pass (2)                                                                   | up_to_date                |

|               | sva/u_fifo_/as_rhsk_infinitely_often              | hold                        | pass (2)                                                                   | up_to_date                |

|               | sva/u_fifo_/as_whsk_infinitely_often              | hold                        | pass (2)                                                                   | up_to_date                |

|               |                                                   |                             |                                                                            |                           |

|               |                                                   |                             |                                                                            |                           |

|               | •                                                 |                             | *****                                                                      |                           |

| 1 items total | 11 selected by filter                             |                             |                                                                            |                           |

|               |                                                   |                             |                                                                            |                           |

|               |                                                   |                             | seesee Shell seeseese                                                      |                           |

| 🕑 Shell 🛛 🚺   | Messages IIII Progress                            |                             |                                                                            |                           |

|               | itness for 'sva/u fifo /as rhsk infinitely often' |                             |                                                                            |                           |

mv>

### **Quantify on FIFO Example—XVI**

Let's look at the failing ordering property

### **Quantify on FIFO Example—XVII**

#### What does our coverage look like?

| Struc  | Structural Coverage Overview |          |                    |  |          |                  |

|--------|------------------------------|----------|--------------------|--|----------|------------------|

| Status |                              | Statemen | ts                 |  | Branche  | es               |

| 1      | covered                      | 14       | 63.64%             |  | 3        | 42.86%           |

| R      | reached                      | 0        | 0.00%              |  | 0        | 0.00%            |

| U      | unknown                      | 0        | <mark>0.00%</mark> |  | 0        | 0.00%            |

| 0R     | unobserved                   | 8        | 36.36%             |  | 3        | 6.36% unobserved |

| 0      | uncovered                    | 0        | 0.00%              |  |          |                  |

| 0C     | constrained                  | 0        | 0.00%              |  | 0        | 0.00%            |

| 0D     | dead                         | 0        | 0.00%              |  | 0        | 0.00%            |

| Sum    | quantify targets             | 22       |                    |  | 7        |                  |

|        |                              |          |                    |  |          |                  |

| Exclu  | ded Code Overview            |          |                    |  |          |                  |

| Code   | Status                       | Statemen | ts                 |  | Branches | s                |

| Xu     | excluded by user             | 0        | 0.00%              |  | 0        | 0.00%            |

| Xr     | excluded redundant code      | 0        | 0.00%              |  | 0        | 0.00%            |

| Xv     | excluded verification code   | 14       | 38.89%             |  | 4        | 36.36%           |

|        |                              |          | 04 4400            |  | 7        | 63.64%           |

| 0/1/U  | quantify targets             | 22       | 61.11%             |  |          | 03.04%           |

| Structural Coverage by File |            |          |  |  |  |  |  |  |

|-----------------------------|------------|----------|--|--|--|--|--|--|

| File                        | Statements | Branches |  |  |  |  |  |  |

| <u>fifo.v</u>               | 22         | 7        |  |  |  |  |  |  |

| fifo_sva.sv                 | 14         | 4        |  |  |  |  |  |  |

#### Coverage reduced..... from 90.91% to 63.64%

Just as we were about to signoff at 90.91% we see coverage drop to 63.64% and failing properties and more design bugs!

| ld | Property                             | Kind   | Proof Result      | Proof Radius | Cover Result | Cover Radius | Quantified |

|----|--------------------------------------|--------|-------------------|--------------|--------------|--------------|------------|

| 0  | sva/u_fifo_/as_empty_after_reset     | assert | FORMAL_PROOF      | infinite     | COVER_PASS   | 1            | yes        |

| 1  | sva/u_fifo_/as_empty_to_full         | assert | FORMAL_NONE       | 0            | COVER_PASS   | 1            | witness    |

| 2  | sva/u_fifo_/as_full_to_empty         | assert | FORMAL_PROOF      | infinite     | COVER PASS   | 5            | yes        |

| 3  | sva/u_fifo_/as_ordering_check        | assert | FORMAL_NONE       | 0            |              | NO           | PROOF      |

| 4  | sva/u_fifo_/as_rhsk_infinitely_often | assert | FORMAL_PROOF      | infinite     | COVER_PASS   | 2            | yes        |

| 5  | sva/u_fifo_/as_whsk_infinitely_often | assert | FORMAL_PROOF      | infinite     | COVER_PASS   | 2            | yes        |

| 6  | sva/u_fifo_/am_d1_before_d2          | assume | FORMAL_ASSUMPTION | infinite     | N/A          | 0            | N/A        |

| 7  | sva/u_fifo_/am_fair_rvalid           | assume | FORMAL_ASSUMPTION | infinite     | N/A          | 0            | N/A        |

| 8  | sva/u_fifo_/am_fair_wvalid           | assume | FORMAL_ASSUMPTION | infinite     | N/A          | 0            | N/A        |

| 9  | sva/u_fifo_/am_stable_d1             | assume | FORMAL_ASSUMPTION | infinite     | N/A          | 0            | N/A        |

| 10 | sva/u_fifo_/am_stable_d2             | assume | FORMAL_ASSUMPTION | infinite     | N/A          | 0            | N/A        |

| File | File Status   |          |        |                                                                                                |  |  |  |

|------|---------------|----------|--------|------------------------------------------------------------------------------------------------|--|--|--|

| ld   | File          | Language | Kind   | Full Name                                                                                      |  |  |  |

| 0    | <u>fifo.v</u> | verilog  | design | /home/onespin/my_labs/fifo_quantify_demo_v2/Step4_looknig_for_bugs_over_constr/rtl/fifo.v      |  |  |  |

| 1    | fifo_sva.sv   | verilog  | design | /home/onespin/my_labs/fifo_quantify_demo_v2/Step4_looknig_for_bugs_over_constr/sva/fifo_sva.sv |  |  |  |

|      |               |          |        |                                                                                                |  |  |  |

### **Quantify on FIFO Example—XVIII**

Fix the bug, prove, then Quantify

| 40 | assign w_ack_o = full ? 1'b0 : 1'b1;  |

|----|---------------------------------------|

| 41 | assign r_ack_o = empty ? 1'b0 : 1'b1; |

#### **Quantify on FIFO Example—XVIII**

| 40 | assign w_ack_o = full ? 1'b0 : 1'b1;                                     | 1 |

|----|--------------------------------------------------------------------------|---|

| 41 | assign r_ack_o = empty ? 1'b0 : 1'b1;                                    | 1 |

| 42 | assign w_hsk = w_valid_i && w_ack_o;                                     | 1 |

| 43 | assign r_hsk = r_valid_i && r_ack_o;                                     | 1 |

| 44 | assign nxt_wptr = wptr + w_hsk;                                          | 1 |

| 45 | assign nxt_rptr = rptr + r_hsk;                                          | 1 |

| 46 | assign nxt_empty = (empty    r_hsk) && !w_hsk && (nxt_rptr == nxt_wptr); | 1 |

| 47 |                                                                          |   |

| 48 | // Registered calculations for empty, wptr and rptr                      |   |

| 49 | always @(posedge clk or negedge resetn)                                  |   |

| 50 | if (!resetn)                                                             | 1 |

| 51 | begin                                                                    |   |

| 52 | empty <= 1'b1;                                                           | 1 |

| 53 | <pre>wptr &lt;= {DEPTH_BITS{1'b0}};</pre>                                | 1 |

| 54 | <pre>rptr &lt;= {DEPTH_BITs{1'b0}};</pre>                                | 1 |

| 55 | end                                                                      |   |

| 56 | else                                                                     | 1 |

| 57 | begin                                                                    |   |

| 58 | empty <= nxt_empty;                                                      | 1 |

| 59 | wptr <= nxt_wptr;                                                        | 1 |

| 60 | <pre>rptr &lt;= nxt_rptr;</pre>                                          | 1 |

| 61 | end                                                                      |   |

| 62 |                                                                          |   |

| 63 | // Write the data on a w_hsk                                             |   |

| 64 | always @(posedge clk)                                                    |   |

| 65 | if (w_hsk)                                                               | 1 |

| 66 | data[wptr] <= data_i;                                                    | 1 |

| 67 |                                                                          |   |

| 68 | // Read the data on a r_hsk                                              |   |

| 69 | always @(posedge clk)                                                    |   |

| 70 | if (r_hsk)                                                               | 1 |

| 71 | <pre>data_int &lt;= data[rptr];</pre>                                    | 1 |

| 72 |                                                                          |   |

| 73 | assign full = !empty && (rptr == wptr);                                  | 1 |

| 74 | assign empty_o = empty;                                                  | 1 |

| 75 | assign full_o = full;                                                    | 1 |

| 76 | assign data_o = data_int;                                                | 1 |

| 77 | endmodule                                                                |   |

#### 100% Covered!

No over-constraints No design bugs All design statements observed Quality of assertions is good Ready for signoff

### **Quantify on FIFO Example—XIX**

#### What happened to our constraint?

| Struct | Structural Coverage Overview |           |         |         |         |  |

|--------|------------------------------|-----------|---------|---------|---------|--|

| Status |                              | Statement | 5       | Branche | es      |  |

| 1      | covered                      | 19        | 100.00% | 4       | 100.00% |  |

| R      | reached                      | 0         | 0.00%   | 0       | 0.00%   |  |

| U      | unknown                      | 0         | 0.00%   | 0       | 0.00%   |  |

| 0R     | unobserved                   | 0         | 0.00%   | 0       | 0.00%   |  |

| 0      | uncovered                    | 0         | 0.00%   | 0       | 0.00%   |  |

| 0C     | constrained                  | 0         | 0.00%   | 0       | 0.00%   |  |

| 0D     | dead                         | 0         | 0.00%   | 0       | 0.00%   |  |

| Sum    | quantify targets             | 19        |         | 4       |         |  |

| Exclu  | Excluded Code Overview     |           |        |      |      |        |

|--------|----------------------------|-----------|--------|------|------|--------|

| Code S | Status                     | Statement | s      | Bran | nche | s      |

| Xu     | excluded by user           | 0         | 0.00%  |      | 0    | 0.00%  |

| Xr     | excluded redundant code    | 0         | 0.00%  |      | 0    | 0.00%  |

| Xv     | excluded verification code | 14        | 42.42% |      | 4    | 50.00% |

| 0/1/U  | quantify targets           | 19        | 57.58% |      | 4    | 50.00% |

| Sum    | total code                 | 33        |        |      | 8    |        |

Constraints are no longer required

The design is guaranteed not to accept new data when full, and cannot be read out when empty

| Let's check that this is indeed the |  |

|-------------------------------------|--|

| case                                |  |

| Let's add | additional | assertions |

|-----------|------------|------------|

| Let's add | additional | assertions |

| Structural Coverage by File |            |          |  |  |  |  |  |

|-----------------------------|------------|----------|--|--|--|--|--|

| File                        | Statements | Branches |  |  |  |  |  |

| <u>fifo.v</u>               | 19         | 4        |  |  |  |  |  |

| fifo_sva.sv                 | 14         | 4        |  |  |  |  |  |

| ld | Property                             | Kind   | Proof Result      | Proof Radius | Cover Result | Cover Radius | Quantified |

|----|--------------------------------------|--------|-------------------|--------------|--------------|--------------|------------|