# Unleash the Full Potential of Your Waveforms From Extra-functional Analysis to Functional Debug via Programs on Waveforms

Daniel Große, Lucas Klemmer Institute for Complex Systems (ICS) Web: jku.at/ics | wal-lang.org Email: daniel.grosse@jku.at, lucas.klemmer@jku.at DESIGN AND VERIFICATION TO DOCOMPERENCE AND EXHIBITION CONFERENCE AND EXHIBITION MUNICH, GERMANY DCTOBER 15-16, 2024

# ... Potential of Your Waveforms ...

JYU JOHANNES KEPLER UNIVERSITY LINZ

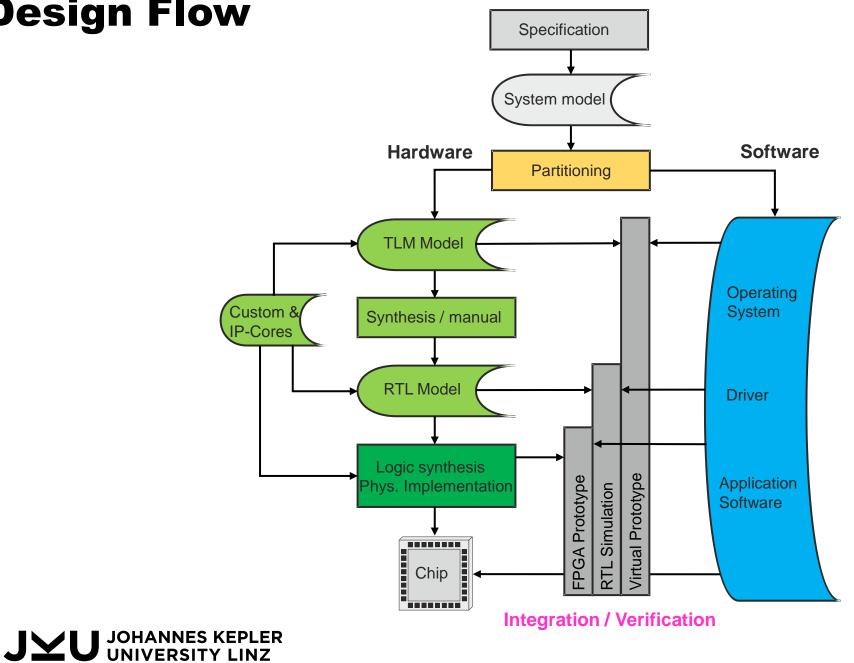

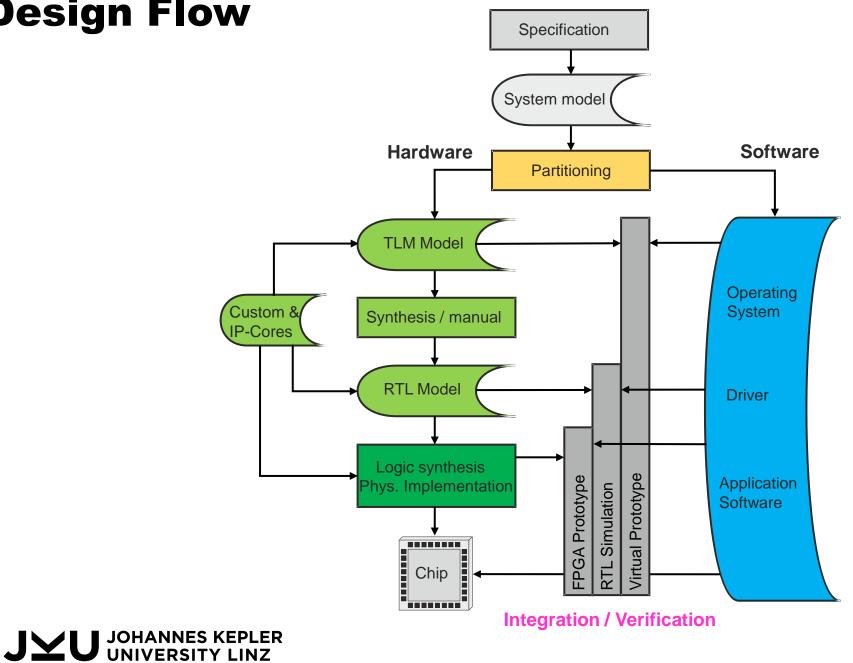

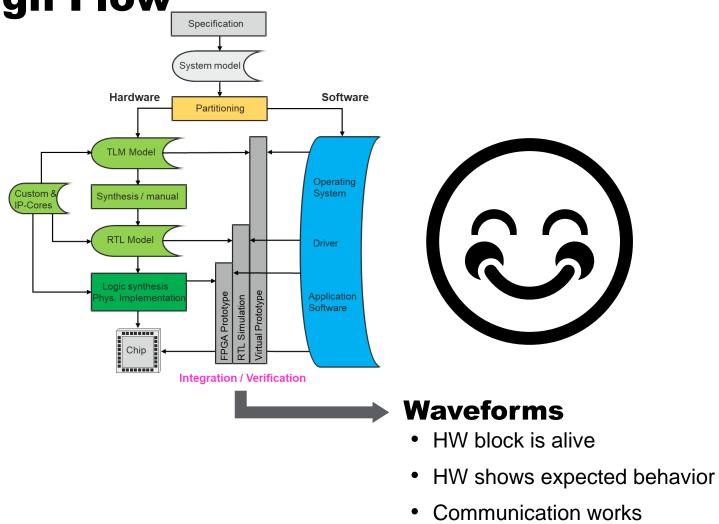

#### **Design Flow**

#### **Design Flow**

#### **Design Flow**

- Assembler instructions run

- Performance as expected

• ...

#### Waveforms

- Waveforms are great!

- A central data format for HW development

- ° Produced by simulators, formal tools, logic analyzers, ...

- They contain incredible amounts of information

performance, correctness, data/control flow, optimization, ...

- However

- ° 100% manual process

- ° Only small slice of data visible at once

- Only for "simple" signal relations

- ° Analysis not automated

JOHANNES KEPLER UNIVERSITY LINZ

• Data without analysis just noise

#### **WAL: Waveform Analysis Language**

- WAL is *Domain Specific Language* (DSL) to express HW analysis problems

- Specialized language constructs for HW domain:

Waveform signals, Time, Hierarchy, Signal relations (bus interfaces)

- Not just true/false expressions, much more than SVA, PSL, ...

- Full capabilities of scripting languages (functions, external libraries, ...)

- Quickly analyze waveforms

- Alternative to

- Custom testbench extensions

- Custom scripts

#### **How to Read WAL Expressions**

- This is a **number** • 5

- These are also numbers

0xff, 0b1101

- This is a variable

° my\_var

- And these are also variables

RD-START, top.core1.run

- This is a **string** • "hello, DVCON Europe!"

° 0xff, 0b1101

° my\_var

- ° RD-START, top.core1.run?

- ° "hello, DVCON Europe!"

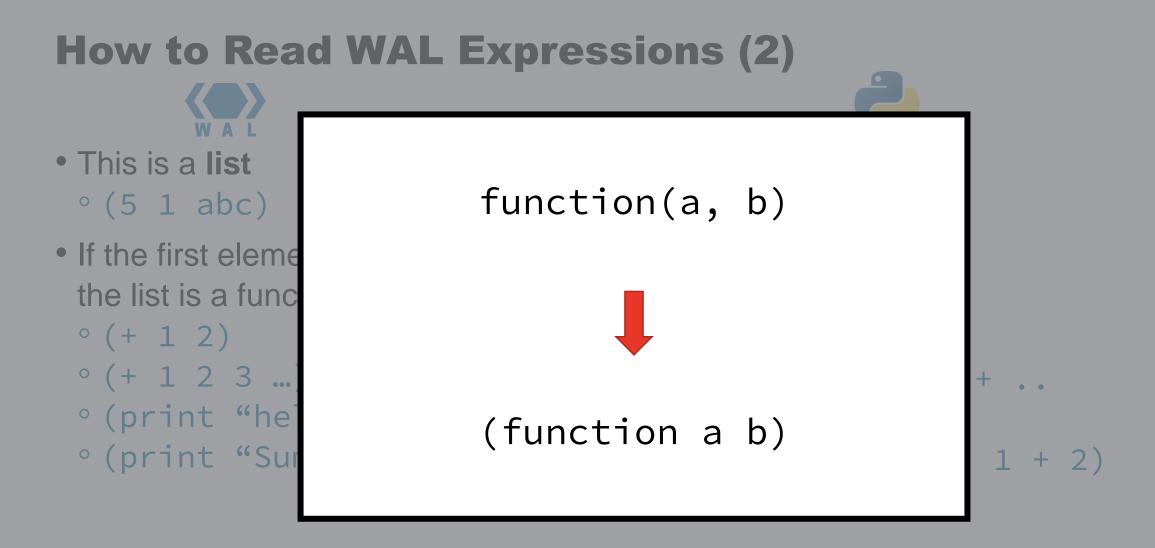

### How to Read WAL Expressions (2)

• This is a **list**

° (5 1 abc)

• If the first element is a function name the list is a function application

° (+ 1 2)

o (print "Sum: " (+ 1 2))

• The same in Python • [5, 1, abc]

#### **Arithmetic and Logic Operators**

- Arithmetic Operators

- Logic Operators

- !, &&, | |, =, !=, >, <, >=, <=

(&& #t #t) => #t

(! (&& #t #t)) => #f

(> 5 4) => #t

#### How to get WAL

- The "original" WAL Interpreter

- Written in Python

- Basis for our research

- Easy to extend, experiment

- Limited performance but proven to be useful

- <u>https://github.com/ics-jku/wal/</u>

- The "new" Interpreter

- Written in Rust

- Goals: Top performance and usability

- Focus on real-life problems

- Wider range of platforms

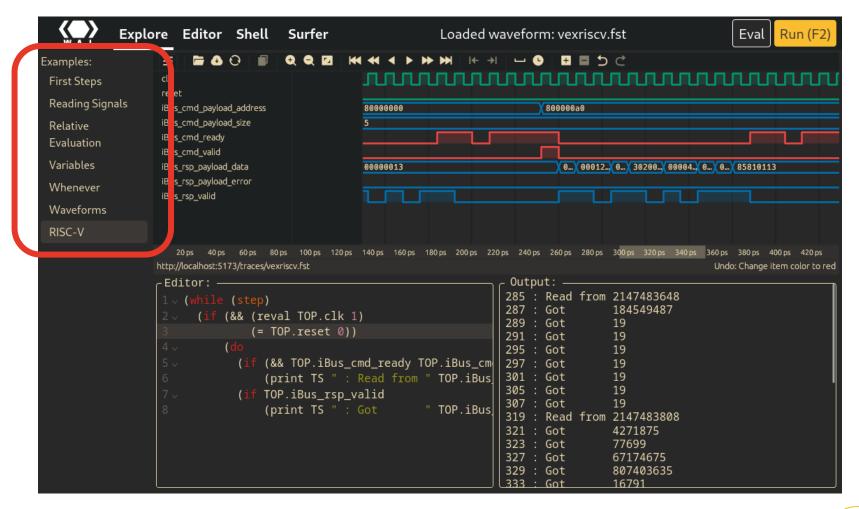

- This tutorial is very hands on

- Online Waveform Explorer

- Integrated waveform viewer

- Prepared examples

- ° Run programs, read output

- Everything runs locally

- Drop in your own waveforms

- No installation, no downloads

- Enabled by web assembly and Rust

- Runs on phones too!

Install the Python version to follow examples

| Explo                                     | re Editor Shell Surfer                                                                | Loaded wavef                                                                                                                                               | orm: vexriscv.fst                                                     | Eval Run (F2)                                       |

|-------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------|

| Examples:<br>First Steps                  |                                                                                       |                                                                                                                                                            |                                                                       | www                                                 |

| Reading Signals<br>Relative<br>Evaluation | iBus_cmd_payload_address<br>iBus_cmd_payload_size<br>iBus_cmd_ready<br>iBus_cmd_ready | 80000000<br>5                                                                                                                                              | X 800000a0                                                            |                                                     |

| Variables<br>Whenever<br>Waveforms        | iBus_rsp_payload_data<br>iBus_rsp_payload_error<br>iBus_rsp_valid                     | 00000013                                                                                                                                                   | X 0 X 00012 X 0 X 30200 X 00004 X 0 X 0 X 0 X 0 X 0 X 0 X 0 X 0 X 0 X | 85810113                                            |

| RISC-V                                    | http://localhost:5173/traces/vexriscv.fst                                             |                                                                                                                                                            |                                                                       | 380 ps 400 ps 420 ps<br>o: Change item color to red |

|                                           | 6 (print TS " :<br>7∨ (if TOP.iBus_rsp_                                               | 1)<br>285<br>287<br>289<br>291<br>295<br>297<br>Read from " TOP.iBus_cm<br>valid<br>Got " TOP.iBus<br>301<br>305<br>307<br>319<br>321<br>323<br>327<br>329 | <pre>put:</pre>                                                       |                                                     |

| Explo                                                                 | ore Editor Shell                                                                                            | Surfer                                          | Loaded w                                                     | vaveform: vexriscv.fst                                                                                          | Eval Run (F2)                 |

|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------|

| Examples:<br>First Steps<br>Reading Signals<br>Relative<br>Evaluation | Clk<br>reset<br>iBus_cmd_payload_address<br>iBus_cmd_payload_size<br>iBus_cmd_ready                         | Q Q 12 H                                        |                                                              |                                                                                                                 |                               |

| Variables<br>Whenever<br>Waveforms<br>RISC-V                          | iBus_cmd_valid<br>iBus_rsp_payload_data<br>iBus_rsp_payload_error<br>iBus_rsp_valid                         |                                                 | 00000013                                                     | <u> </u>                                                                                                        | <u>(0)(0)(85810113</u>        |

|                                                                       | Editor:<br>1 ~ (while (step)<br>2 ~ (if (&& (red)<br>3 (= 1)<br>4 ~ (do<br>5 ~ (if (%<br>6 ()<br>7 ~ (if To | val TOP.clk 1<br>TOP.reset 0))<br>&& TOP.iBus_c | .)<br>:md_ready TOP.iBus_cm<br>Read from " TOP.iBus<br>valid | Ops         240 ps         260 ps         280 ps         300 ps         320 ps         340 ps           Output: | s 360 ps 380 ps 400 ps 420 ps |

| Expl                                                         | ore Editor Shell Surfer                                                                                                                                                                                                                 | Loaded waveform: vexri                                                                                                                                                 | iscv.fst Eval Run (F2)                                                                                                                            |

|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Examples:<br>First Steps<br>Reading Signals                  | clk<br>reset<br>iBus_cmd_payload_address                                                                                                                                                                                                | 30000000 X800000a0                                                                                                                                                     |                                                                                                                                                   |

| Relative<br>Evaluation<br>Variables<br>Whenever<br>Waveforms | iBus_cmd_payload_size<br>iBus_cmd_ready<br>iBus_cmd_valid<br>iBus_rsp_payload_data<br>iBus_rsp_payload_error<br>iBus_rsp_valid                                                                                                          | 5<br>00000013<br>00000013<br>00000013                                                                                                                                  | 0012\ 0\ 30200\ 00004\ 0\ 0\ 85810113                                                                                                             |

| RISC-V                                                       | http://linearchine.com/         Editor:         1 ~ (while (step))         2 ~ (if (&& (reval TOP.clk :         3 (= TOP.reset 0)         4 ~ (do         5 ~ (if (&& TOP.iBus_c         6 (print TS " :         7 ~ (if TOP.iBus_rsp_) | Output:<br>285 : Read f<br>287 : Got<br>289 : Got<br>289 : Got<br>291 : Got<br>295 : Got<br>295 : Got<br>297 : Got<br>297 : Got<br>301 : Got<br>305 : Got<br>307 : Got | 80 ps 300 ps 320 ps 340 ps 360 ps 380 ps 400 ps 420 ps<br>Tom 2147483648<br>184549487<br>19<br>19<br>19<br>19<br>19<br>19<br>19<br>19<br>19<br>19 |

| Expl                   | ore Editor Shell Surfer                                                                                                                                                   | Loaded waveform: vexriscv.fst                                                                                                                                                                                                                | ival Run (F2)                                 |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Examples:              | E & O I & Q Q I                                                                                                                                                           |                                                                                                                                                                                                                                              |                                               |

| First Steps            | clk                                                                                                                                                                       | ຠຠຠຠຠຠຠຠຠຠຠຠຠຠຠ                                                                                                                                                                                                                              | mmm                                           |

| Reading Signals        | reset<br>iBus_cmd_payload_address                                                                                                                                         | 80000000                                                                                                                                                                                                                                     |                                               |

| Relative<br>Evaluation | iBus_cmd_payload_size<br>iBus_cmd_ready<br>iBus_cmd_valid                                                                                                                 |                                                                                                                                                                                                                                              |                                               |

| Variables              | iBus_rsp_payload_data                                                                                                                                                     | 00000013 <u>(0)</u> 00012) 0) 30200) 00004) 0) 85                                                                                                                                                                                            | 810113                                        |

| Whenever               | iBus_rsp_payload_error<br>iBus_rsp_valid                                                                                                                                  |                                                                                                                                                                                                                                              |                                               |

| Waveforms              | ing?", the family                                                                                                                                                         |                                                                                                                                                                                                                                              | ·                                             |

| RISC-V                 |                                                                                                                                                                           |                                                                                                                                                                                                                                              |                                               |

|                        | <pre>http://localhost:5173/traces/vexriscv.fst Editor: 1 ~ (while (step) 2 ~ (if (&amp;&amp; (reval TOP.clk 3 (= TOP.reset 0 4 ~ (do 5 ~ (if (&amp;&amp; TOP.iBus) </pre> | Output:<br>285 : Read from 2147483648<br>287 : Got 184549487<br>289 : Got 19<br>291 : Got 19<br>291 : Got 19<br>295 : Got 19<br>297 : Got 19<br>301 : Got 19<br>301 : Got 19<br>305 : Got 19<br>305 : Got 19<br>307 : Got 19<br>307 : Got 19 | 0 ps 400 ps 420 ps<br>hange item color to red |

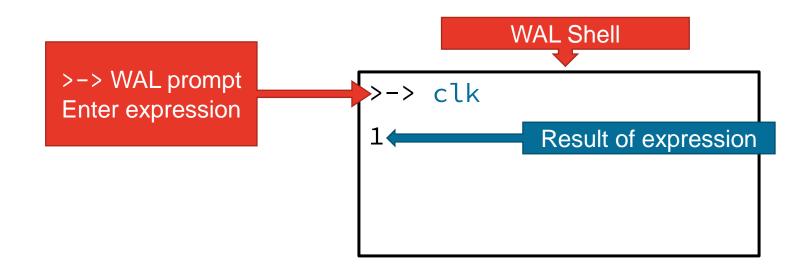

#### **Hands-On: Shell Examples**

#### **Hands-On: First Steps**

>-> 1 1 >-> (+ 1 2) 3 >-> (= 1 2) #f

#### Selecting a different example:

| Explo                  | ore            | Editor                           | Shell         | Su            | ırfer |       |    |

|------------------------|----------------|----------------------------------|---------------|---------------|-------|-------|----|

| Examples:              |                | 🖬 🕹                              | 0             | Ð             | Q 🗹   | K     | •  |

| First Steps            | clk            |                                  | 1             |               |       |       |    |

| Reading Signals        | resel<br>iBus_ | :md_paylı                        | 0<br>80000000 | (56906        | 62e0  |       |    |

| Relative<br>Evaluation |                | :md_read                         | 5<br>0<br>0   | 5             |       |       |    |

| Variables              | iBus_<br>iBus_ | :md_valid<br>:sp_paylo;          | 00000013      | <b>983</b> b6 | 6b10  |       |    |

| Whenever               | iBus_<br>iBus  | rsp_paylo;<br>rsp_valid          | 0<br>0        |               |       |       | _  |

| Waveforms              |                |                                  |               |               |       |       |    |

| RISC-V                 |                |                                  |               |               |       |       |    |

|                        |                | 0 ps       40 ps<br>localhost:51 |               |               |       | 20 ps | 1. |

#### **Side note: Surfer Waveform Viewer**

| = 🖬 🕹 😔 🗐 🔍 🔍 🖬                           | <b>₩ 4 4 &gt;</b> | > >> >> >> >> >> >> >>> >>> >>>>>>>>>> | ) ⊔ 🕒        | ±∎5 Č          |                 |             |

|-------------------------------------------|-------------------|----------------------------------------|--------------|----------------|-----------------|-------------|

| Time                                      | ps 10 ps          | 20 ps 30 ps                            | 40 ps 50 ps  | 60 ps 70 ps 80 | ps 90 ps 100 ps | 110 ps 120  |

| clk                                       |                   |                                        | mmmmm        | mmmmm          | wwwwww          | սոսուս      |

| reset                                     |                   |                                        |              |                |                 |             |

| iBus_cmd_payload_address                  | 569062e0          |                                        |              |                |                 |             |

| iBus_cmd_ready                            |                   |                                        | u            |                |                 | U U         |

| iBus_cmd_valid                            |                   |                                        | _            |                |                 |             |

| iBus_rsp_valid                            | 08366640          |                                        |              |                |                 |             |

| iBus_rsp_payload_data                     | <b>983b6b10</b>   |                                        |              |                |                 |             |

|                                           |                   |                                        |              |                |                 |             |

|                                           |                   |                                        |              |                |                 |             |

|                                           |                   |                                        |              |                |                 |             |

|                                           |                   |                                        |              |                |                 |             |

|                                           |                   |                                        |              |                |                 |             |

|                                           |                   |                                        |              |                |                 |             |

|                                           |                   |                                        |              |                |                 |             |

|                                           |                   |                                        |              |                |                 |             |

|                                           |                   |                                        |              |                |                 |             |

|                                           |                   |                                        |              |                |                 |             |

|                                           |                   |                                        |              |                |                 |             |

|                                           |                   |                                        |              |                |                 |             |

|                                           |                   |                                        |              |                |                 |             |

|                                           |                   |                                        |              |                |                 |             |

|                                           |                   |                                        |              |                |                 |             |

|                                           |                   |                                        |              |                |                 |             |

| 10 ps 20 ps 30 ps 40 ps 50                | x 60 ps           | 70 ps 80 ps                            | 90 ps 100 ps | 110 ps 120 ps  | 130 ps 140 ps   | 150 ps 160  |

| http://localhost:5173/traces/vexriscv.fst | 50 p3             | 10 ps 00 ps                            | 100 p3       | 1000           |                 | 100 par 100 |

- Modern open-source waveform viewer

- Co-developed with LIU, Sweden

- Very fast, customizable, flexible

- Traditional mouse based navigation

- OR

- Keyboard driven UI

- VSCode inspired command line

- press <SPACE>

- variable\_add ...

- scope\_add ...

- Visit <u>https://surfer-project.org</u>

• This is a signal access!

- Free variables are signals in waveforms

- Value depending on:

- ° Loaded waveform

- ° Time index in the waveform

- In simple terms:

- WAL programs run over a waveform and collect information

• What does this do?

Traceback (most recent call last):

File "error.py", line 2, in <module>

print(a + b)

NameError: name 'b' is not defined

Ouch!

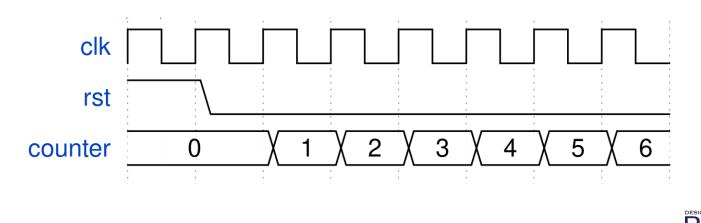

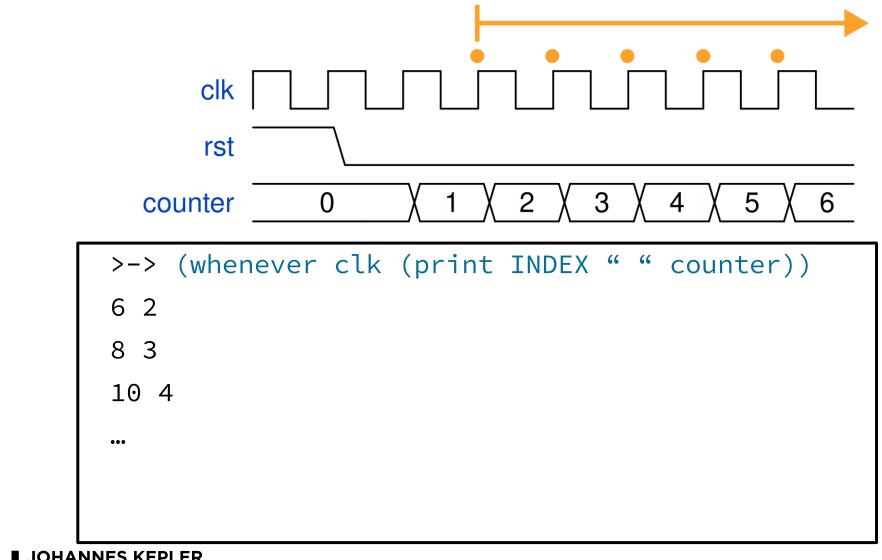

#### **Reading Signal Values (Example)**

- We have a simple counter

- index = 0, after waveform is loaded

- Read a signal by typing it's name

- Move the index with (step)

- 0:>-> clk⇒1 >-> (step 1)

- 1:>-> clk  $\Rightarrow$  0 >-> (step 5)

- $\begin{array}{l} 6: >-> \ \text{clk} \Rightarrow 1 \\ >-> \ \text{counter} \Rightarrow 2 \end{array}$

#### **Hands-On: Reading Signal Values**

>-> clk 1 >-> (step 1) #t >-> INDEX 1 >-> clk 0 >-> (step 5) #t >-> counter

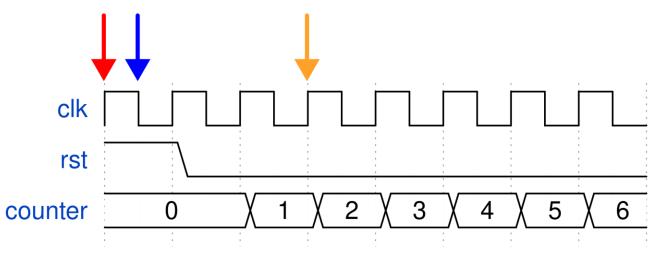

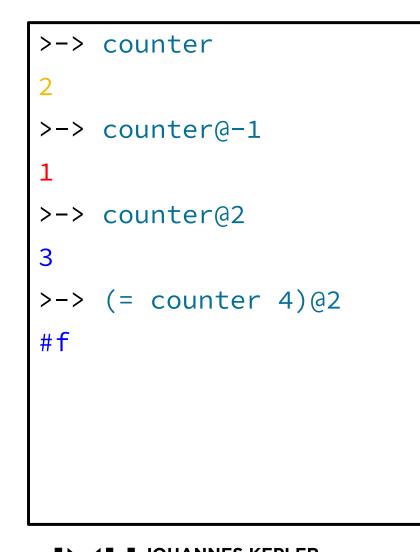

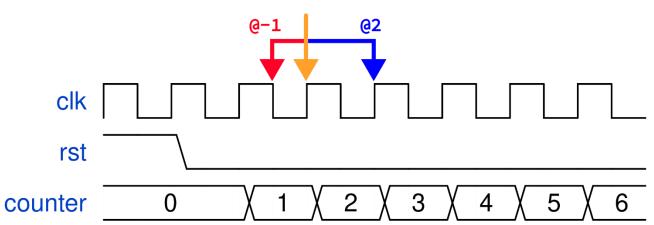

#### **Relative Evaluation**

- Index can be locally modified with expr@offset syntax

- Evaluate at next timestamp signal@1

Detect value change (!= signal signal@1)

- @ can be applied to every expression (not just signals)

- Is x larger than 5 two indices ahead?  $\longrightarrow$  (> x 5)@2

#### **Hands-On: Relative Evaluation**

#### Variables

- Define a new variable using define

o (define x 5)

- Change variables using set!

o (set! [x 22])

- Create local bindings using let

- o (let ([x 10]) x)

- ° (let ([x 10] [y 20]) (+ x y))

#### **Hands-On: Variables**

```

>-> (define x 5)

5

>-> x

5

>-> (+ x 1)

6

>-> (set! x "DVCON")

"DVCON"

>-> x

"DVCON"

>-> (+ x 1)

"DVCON1"

```

JOHANNES KEPLER UNIVERSITY LINZ

29

#### **Special Functions**

- Signal events

- ° (rising x) => (&& (= x 1) (= x@-1 0))

- ° (falling x) => (&& (= x 0) (= x@-1 1))

- o (stable x) => (= x x@-1)

- Step over waveform and evaluate body whenever condition is true

- Starts at the current INDEX

- ° (whenever condition body+)

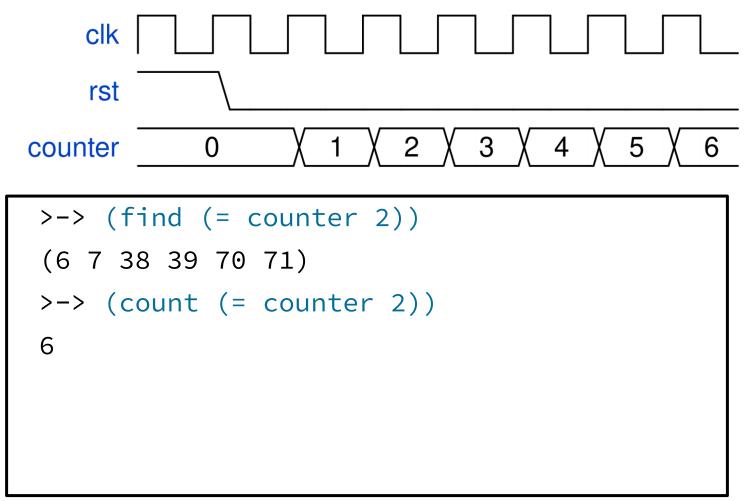

- Find all indices at which condition is true

(find condition)

- Count how often condition is true

- ° (count condition)

#### **Hands-On: Whenever**

JYU JOHANNES KEPLER UNIVERSITY LINZ

#### Hands-On: Find, Count

JYU JOHANNES KEPLER UNIVERSITY LINZ

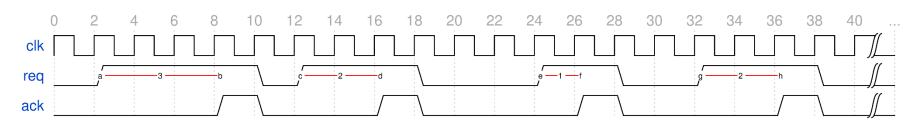

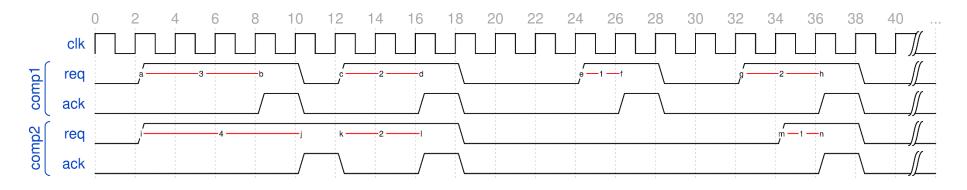

#### **Example: Average Delay**

- Calculate average delay on handshaking bus

- Two states:

- ° Waiting: (&& req (! ack))

- Sending: (&& req ack)

- Count states

- Result = |waiting| / |sending|

(whenever clk

... always evaluated when clk = 1 ...)

#### **Example: Average Delay (1)**

- Calculate average delay on handshaking bus

- Two states:

- ° Waiting: (&& req (! ack))

- ° Sending: (&& req ack)

- Count states

- Result = |waiting| / |sending|

| (wh | enever (rising clk)                                                                              |  |

|-----|--------------------------------------------------------------------------------------------------|--|

|     | (when (&& req (! ack)) (inc wait))                                                               |  |

|     | <pre>(when (&amp;&amp; req (! ack)) (inc wait)) (when (&amp;&amp; req ack) (inc packets)))</pre> |  |

|     |                                                                                                  |  |

| (pr | <pre>int (/ wait packets))</pre>                                                                 |  |

(3+2+1+2)/4 = 8/4 = 2

#### Groups

- HW designs ideal for writing generic code!

- Handshaking is common

- ° Standardized interfaces (AXI, AHB, Wishbone, SPI, ...)

- For example, two instances of the handshaking bus

- Write expressions only using the shared suffix of the name

- Expand #suffix to full name

- ° #req => either compl.req or comp2.req

- clk

- compl.req

- compl.ack

- comp2.req

- comp2.ack

- comp1.

- comp2.

#### **Hands-On: Groups**

```

>-> SIGNALS

```

```

(... "comp1.clk" "comp1.ready" "comp1.valid"

"comp2.clk" "comp2.ready" "comp2.valid")

>-> (groups clk ready valid)

("comp1." "comp2.")

>-> (groups clk)

("" "comp1." "comp2.")

```

#### **Example: Average Delay (2)**

- Wrap analysis in in-groups function

- Expression evaluated in each group

- #signal expanded to full name

0

clk

rea

ack

rea

ack

(groups req ack)  $\Rightarrow$  (comp1. comp2.)

comp1

comp2

#### **Other WAL Features**

- Data Structures

- Lists:

- (first list), (second list), (rest list), ...

- list[i], list[h:l]

- fold, map, for , ...

- Hashmaps:

- (geta symbol key1 key2 ...)

- (seta symbol key1 key2 ... data)

- Extracting bits from signals

signal[i], signal[h:l]

- WAL as a compilation target from other languages

#### **Applications: Reports of Processors, Buses**

| Core     | Configuration            | IPC  | Stalled Cycles |

|----------|--------------------------|------|----------------|

| SERV     | Servant                  | 0.02 | Not pipelined  |

| PicoRv32 | Default                  | 0.24 | Not pipelined  |

| VexRiscv | MicroNoCsr               | 0.33 | 63%            |

| VexRiscv | Smallest                 | 0.33 | 66%            |

| VexRiscv | SmallAndProductive       | 0.42 | 54%            |

| VexRiscv | SmallAndProductiveICache | 0.47 | 51%            |

| VexRiscv | TwoThreeStage            | 0.47 | 48%            |

| VexRiscv | Secure                   | 0.57 | 42%            |

| VexRiscv | Linux                    | 0.59 | 38%            |

| VexRiscv | Full                     | 0.57 | 35%            |

| VexRiscv | FullNoMmuMaxPerf         | 0.63 | 33%            |

| IBEX     | Default                  | 0.63 | 48%            |

| IBEX     | Icache                   | 0.89 | 19%            |

| TGC      | 3-Stage                  | 0.61 | 64%            |

| TGC      | 4-Stage v1               | 0.72 | 49%            |

| TGC      | 4-Stage v2               | 0.70 | 45%            |

| TGC      | 4-Stage v3               | 0.70 | 44%            |

| TGC      | 4-Stage v4               | 0.68 | 43%            |

| TGC      | 5-Stage                  | 0.78 | 40%            |

```

"tb.dut.mem_wrapper.axi4_source1": {

transactions: [

ſ

"id": 0,

"start": 1511,

"addr": f028,

"duration": 5234,

. . .

"id": 1,

"start": 1541,

"addr": f032,

"duration": 3234,

. . .

"tb.dut.mem_wrapper.axi4_source2": {

transactions: [

. . .

}

```

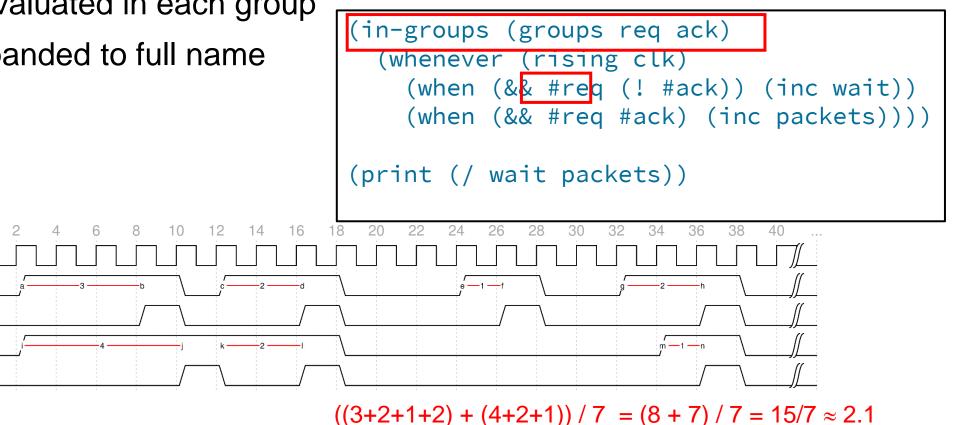

#### **Applications: Pipeline Explorer**

(require pipeline) (stage fetch (value tb.dut.dp.instrf@1) (stall tb.dut.dp.stallf) (log stallf tb.dut.dp.stallf) (log pc tb.dut.dp.pcf)) (stage decode (update (! tb.dut.dp.stalld)) (stall tb.dut.dp.stalld) (flush tb.dut.dp.flushd) (log pc fetch-pc@-1) (log rd tb.dut.dp.rdd) (log rs1 tb.dut.dp.rs1d) (log rs2 tb.dut.dp.rs2d)) (stage execute (update (! tb.dut.dp.flushe)) (flush tb.dut.dp.flushe) (log pc decode-pc@-1)) (stage memory)

(stage writeback)

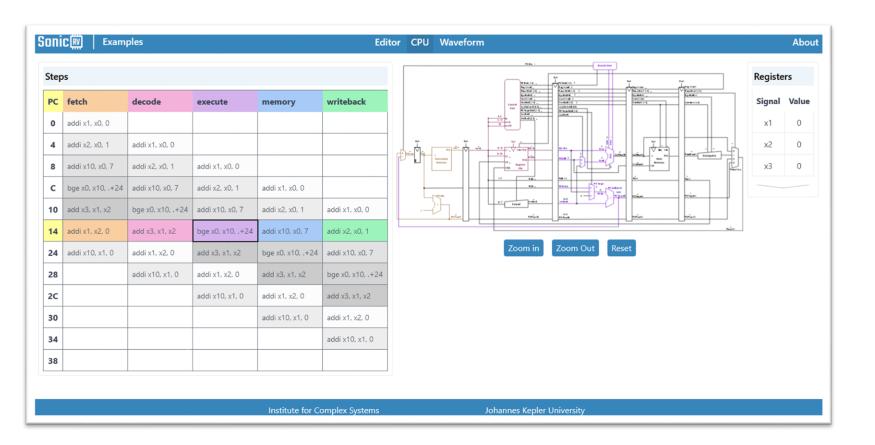

#### **Applications: SVA on Waveforms**

| File Run                         |                                                                                   |                                           |

|----------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------|

|                                  |                                                                                   |                                           |

| Trace examples/ics-sc/ics-sc.fst | SVA Callbacks                                                                     | Verification Results                      |

| Trace examples/ics-sc/ics-sc.isc |                                                                                   | reg_10_update_on_write                    |

| Time TS@MAX-INDEX                | define OP_LUI b0110111                                                            | reg_4_update_on_write                     |

| Inter ISENACIADEA                | 'define OP_AUIPC 'b0010111                                                        | <ul> <li>reg_1_update_on_write</li> </ul> |

| Indices MAX-INDEX                | define OP_ARITH b0010011                                                          | ▼ Fails at                                |

|                                  | 'define OP_LOAD 'b0000011                                                         | 8600000000 -> 8610000000                  |

|                                  | define OP_STORE b0100011                                                          | reg_7_update_on_write                     |

|                                  | define OF_JAL b100111                                                             | reg_2_no_change_on_other_write            |

|                                  | deline OF_AC BHOTTH                                                               | reg.8.no_change_on_other_write            |

|                                  | 'define F7 BRANCH 'b1100011                                                       | reg.5_no_change_on_other, write           |

|                                  | deline F/_BRANCH DT1000TT                                                         | reg_10_no_change_on_other_write           |

|                                  |                                                                                   | reg_6_update_on_write                     |

|                                  | `define F3_BEQ 'b000                                                              |                                           |

|                                  | 'define F3_BNE 'b001                                                              | reg_3_update_on_write                     |

|                                  | 'define F3_BLTS 'b100                                                             | reg_7_no_change_on_other_write            |

|                                  | `define F3_BGES 'b101                                                             | reg_9_update_on_write                     |

|                                  | `define F3_BLTU 'b110                                                             | reg_1_no_change_on_other_write            |

|                                  | `define F3_BGEU 'b111                                                             | reg_4_no_change_on_other_write            |

|                                  |                                                                                   | reg_11_update_on_write                    |

|                                  | `define reg_update_on_write(REGN) \                                               | reg_3_no_change_on_other_write            |

|                                  | reg_REGN_update_on_write: assert property( \                                      | <ul> <li>reg_8_update_on_write</li> </ul> |

|                                  | @(posedge testbench.clk) \                                                        | ✓ Fails at                                |

|                                  | disable iff(testbench.reset) \                                                    | 8610000000 -> 8620000000                  |

|                                  | (testbench.dut.rvsingle.dp.rf.we3 && (testbench.dut.rvsingle.dp.rf.a3 == REGN)) \ | reg_6_no_change_on_other_write            |

|                                  | (residentification sangle-applitives) case (construction sangle-applitas) =       | reg_2_update_on_write                     |

|                                  | ):                                                                                | reg.9 no_change_on_other_write            |

|                                  |                                                                                   | reg_5_update_on_write                     |

|                                  | Nation real and shares an other units (PECND)                                     | ✓ reg_13_update_on_write                  |

|                                  | `define reg_no_change_on_other_write(REGN) \                                      | ▼ Fails at                                |

|                                  | reg_REGN_no_change_on_other_write: assert property(\                              | 470000000 → 48000000                      |

|                                  | @(posedge testbench.clk) \                                                        | reg_11_no_change_on_other_write           |

| Design Hierarchy                 | <ul> <li>disable iff(testbench.reset) \</li> </ul>                                |                                           |

| standard                         | (testbench.dut.rvsingle.dp.rf.we3 && (testbench.dut.rvsingle.dp.rf.a3 != REGN)) \ | reg_16_update_on_write                    |

| textio                           | => \$stable(testbench.dut.rvsingle.dp.rf.xREGN) \                                 | reg_14_no_change_on_other_write           |

| std_logic_1164                   |                                                                                   | reg_17_no_change_on_other_write           |

| numeric_std_unsigned             |                                                                                   | reg_19_update_on_write                    |

| numeric_std                      | `reg_update_on_write(1)                                                           | reg_20_no_change_on_other_write           |

| env                              | `reg_no_change_on_other_write(1)                                                  | reg_13_no_change_on_other_write           |

| std_logic_textio                 | `reg_update_on_write(2)                                                           | reg_14_update_on_write                    |

| ▼ testbench                      | `reg_no_change_on_other_write(2)                                                  | ✓ Fails at                                |

|                                  | `reg_update_on_write(3)                                                           | 48000000 -> 49000000                      |

| dataadr                          | `reg_no_change_on_other_write(3)                                                  | reg_12_update_on_write                    |

| reset                            | `reg_update_on_write(4)                                                           | reg_18_update_on_write                    |

| memwrite                         | `reg_no_change_on_other_write(4)                                                  | reg_16_no_change_on_other_write           |

| writedata                        | reg_update_on_write(5)                                                            | reg_15_update_on_write                    |

| clk                              | reg_no_change_on_other_write(5)                                                   | reg_19_no_change_on_other_write           |

| ✓ testbench.dut                  | reg_update_on_write(6)                                                            | reg_21_update_on_write                    |

| writedata                        | reg_no_change_on_other_write(6)                                                   | reg_22_update_on_write                    |

| reset                            |                                                                                   | reg_17_update_on_write                    |

| memwrite                         | 'reg_update_on_write(7)                                                           | reg_12_no_change_on_other_write           |

| instr                            | 'reg_ued_to ge_wrive(7)                                                           | reg_18_no_change_o_other_write            |

| clk                              | 'reg_update_on_write(8)                                                           | reg_15_no_change_on_other_write           |

| dataadr                          | reg_no_change_on_other_write(8)                                                   | reg_20_update_on_write                    |

| memsel                           | reg_update_on_write(9)                                                            | reg_21_no_change_on_other_write           |

| pc                               | 'reg_no_change_on_other_write(9)                                                  | reg_2z_no_change_on_other_write           |

| readdata                         | reg_update_on_write(10)                                                           | reg_28_update_on_write                    |

| ✓ testbench.dut.rvsingle         | `reg_no_change_on_other_write(10)                                                 |                                           |

| signexten                        | `reg_update_on_write(11)                                                          | reg_23_no_change_on_other_write           |

| regwrite                         | `reg_no_change_on_other_write(11)                                                 | reg_29_no_change_on_other_write           |

| aluresult                        | `reg_update_on_write(12)                                                          | reg_25_update_on_write                    |

| writedata                        | `reg_no_change_on_other_write(12)                                                 | reg_26_no_change_on_other_write           |

| memselint                        | `reg_update_on_write(13)                                                          | reg_31_update_on_write                    |

| mensel                           | `reg_no_change_on_other_write(13)                                                 | reg_23_update_on_write                    |

| pc                               | `reg_update_on_write(14)                                                          | reg_30_update_on_write                    |

| readdata                         | `reg_no_change_on_other_write(14)                                                 | reg_24_update_on_write                    |

| alucontrol                       | 'reg_update_on_write(15)                                                          | reg_27_update_on_write                    |

| alucontrol                       | `reg_no_change_on_other_write(15)                                                 | reg_28_no_change_on_other_write           |

| clk                              | `reg_update_on_write(16)                                                          | reg_25_no_change_on_other_write           |

|                                  | 'reg_nc_change_on_other_write(16)                                                 | reg_31_no_change_on_other_write           |

| alusrc                           | reg_update_on_write(17)                                                           | reg_27_no_change_on_other_write           |

| immsrc                           | reg_no_change_on_other_write(17)                                                  | reg_29_update_on_write                    |

| less                             | reg_update_on_write(18)                                                           | reg_26_update_on_write                    |

| zero                             | reg-aporte_on_mine(rd)                                                            |                                           |

#### You tried WAL and we listened

- WAL is available now for 3+ years

- We got a lots of feedback since then

- Now we want to make production-ready waveform analysis real

- We are working on a new Product based on your feedback

- Intuitive C-style syntax

- Support for much larger waveforms

- ° Ready-to-use libraries (AMBA, Ethernet, ...)

- Tight waveform viewer integration

- Initial release early next year

- Interested, ideas, wishes? Let's talk over a coffee/beer later!

#### **Take-home Message**

# If you work with waveforms try WAL online or the Python version, reach out, and stay tuned!

# Unleash the Full Potential of Your Waveforms From Extra-functional Analysis to Functional Debug via Programs on Waveforms

Daniel Große, Lucas Klemmer Institute for Complex Systems (ICS) Web: jku.at/ics | wal-lang.org Email: daniel.grosse@jku.at, lucas.klemmer@jku.at DESIGN AND VERIFICATION TO DOCOMPERENCE AND EXHIBITION CONFERENCE AND EXHIBITION MUNICH, GERMANY DCTOBER 15-16, 2024

#### **Papers**

- Lucas Klemmer and Daniel Große. An Extensible and Flexible Methodology for Analyzing the Cache Performance of Hardware Designs. In FDL, 2024. <u>https://ics.jku.at/files/2024FDL\_WAL-Cache-Performance-Analysis.pdf</u>

- Lucas Klemmer and Daniel Große. WAVING Goodbye to Manual Waveform Analysis in HDL Design With WAL. In IEEE Transactions on Computer Aided Design of Circuits and Systems (TCAD), 2024. <u>https://ieeexplore.ieee.org/document/10496480</u> (open access PDF).

- Lucas Klemmer and Daniel Große. Towards a highly interactive design-debug-verification cycle. In ASP-DAC, 2024. <u>https://ics.jku.at/files/2024ASPDAC\_WAL-VirtualSignals.pdf</u>

- Lucas Klemmer, Frans Skarman, Oscar Gustafsson, and Daniel Große, "Surfer: a waveform viewer as dynamic as RISC-V," In RISC-V Summit Europe, 2024. <u>https://ics.jku.at/files/2024RISCVSummit\_Surfer.pdf</u>

- Daniel Große, Lucas Klemmer, and Dominik Bonora, "Using formal verification methods for optimization of circuits under external constraints," in DATE, 2024. <u>https://ics.jku.at/files/2024DATE\_FSYN.pdf</u>

- Lucas Klemmer and Daniel Große. Waveform-based performance analysis of RISC-V processors: late breaking results. In DAC, pages 1404-1405, 2022. <u>https://ics.jku.at/files/2022DAC\_LBR-Waveform-based-Performance-Analysis-for-RISC-V.pdf</u>

- Lucas Klemmer, Eyck Jentzsch, and Daniel Große. Programmable analysis of RISC-V processor simulations using WAL. In *DVCon Europe*, 2022. <u>https://ics.jku.at/files/2022DVCon\_Programmable\_Analysis\_of\_RISC-V\_Processor\_Simulations\_using\_WAL.pdf</u>

- Lucas Klemmer and Daniel Große. A DSL for visualizing pipelines: A RISC-V case study. In RISC-V Summit Europe, 2023. <u>https://ics.jku.at/files/2023RISCVSummit\_DSLforVisualizingPipelines.pdf</u>

- Frans Skarman, Lucas Klemmer, Oscar Gustafsson, and Daniel Große. Enhancing compiler-driven HDL design with automatic waveform analysis. In FDL, 2023. <u>https://ics.jku.at/files/2023FDL\_Enhancing-Compiler-Driven-HDL-Design-with-WAL.pdf</u>

- Lucas Klemmer and Daniel Große. WAL: a novel waveform analysis language for advanced design understanding and debugging. In ASP-DAC, pages 358-364, 2022. <u>https://ics.jku.at/files/2022ASPDAC\_WAL.pdf</u>

#### JYU JOHANNES KEPLER UNIVERSITY LINZ