# IP-XACT IEEE-1685 入門から最新情報まで

Koji Nakamura (Arteris IP)

# Agenda

- Why IP-XACT and why we need Tools?

- Why IP-XACT 2022?

2023/06/22

# Why IP-XACT?

why we need it and why we need tools

# Why IP Reuse?

- Too complex to do it by hand

- Reuse work to save time and effort (and avoid errors)

- Simplify the delivery of IP to stakeholders

# Why IP-XACT?

- Standard to exchange and retarget IP to multiple vendors

- Electronic documentation (easy to parse and process)

- Automate the repetitive tasks by writing Portable generators (using standard API: TGI)

- Easier to certify flows

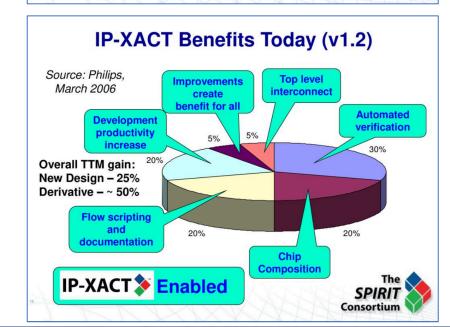

# IP-XACT: the origins

- 20 years old (started in 2003)

- The first (Spirit) consortium was created with IP providers (ARM, Synopsys), SoC integrators (NXP, ST) and EDA vendors (Cadence, Mentor, Synopsys)

- Original XML schema donated by Mentor

- Main objective was to give a SW view of a HW SoC to align the SW (memory) architecture with the HW (structural) architecture

- Schema updated to cover 2 main additional objectives:

- Early SoC assembly (required by the SoC integrators)

- Single source of IP information (required by the IP Vendors) to avoid N qualification of the same IP for N different EDA Vendors

### **The SPIRIT Consortium Vision (2003)**

- The SPIRIT Consortium was announced at DAC 2003

- The original Vision upon which the Consortium was formed:

Achieve an open standard for a development framework upon which an SoC development flow, from components to chip, can be built allowing distribution and use of IP from varied sources as well as the free choice of tools used in the SoC development

IPXACT: Why / How / What WHAT

**WHY**

- Simplify IP Exchange and Reuse

- Automate tedious and low interest tasks

- Manage Growing complexity

- Limit dependency to IP / EDA providers

- IEEE standard

- Create a semantic <u>descriptive</u> model

- Promote a large adoption

- Enhance and coexist with other languages

- IEEE 1685-20xx PDF

- Semantic model description

- Semantic Rules

- API

- Accellera

- XML Schema + TGI WSDL/OpenAPI

- XSLT for up conversion

- Examples

- User guide

- Official extensions

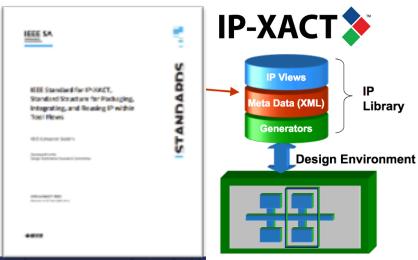

## IP-XACT Basics - Quick Reminder

## **IEEE IEEE Standard for IP-XACT.** Standard Structure for Packaging, Integrating, and Reusing IP within **Tool Flows IEEE Computer Society** IEEE Standards Association Corporate Advisory Group Sponsored by the Design Automation Standards Committee IEEE Std 1685™-2009 18 February 2010 Authorized licensed use limited to: NXP Semiconductors. Downloaded on February 25:2010 at 10:44:33 EST from IEEE Xplore. Restrictions and

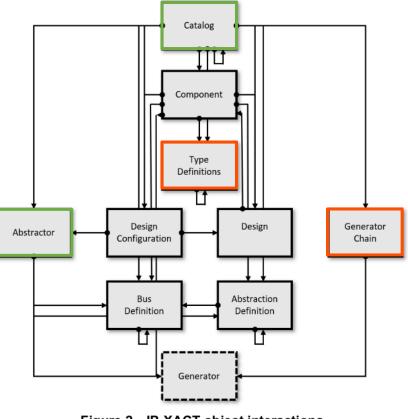

Figure 2—IP-XACT object interactions

Each object identified by a Unique ID: **VLNV**

### **IP-XACT Concepts:**

- BusDefinition

- AbstractionDefinition

- Component / Abstractor

- Ports

- BusInterface

- Registers / Fields

- Filesets / Files

- Views

- Modes

- Design

- Component instances

- AdhocConnection

- Interconnection

- DesignConfiguration

- View selection

- Parameters configuration

- TypeDefinitions

- GeneratorChain + TGI

- Catalog

## IP-XACT Basics - Quick Reminder

Why is this so important?

IP shall be integrated in different D&V flows using different Tool Vendors

## The IP-XACT Specification

- Is design language neutral

- Is design tool neutral

- Is efficient

- Is proven

- Is built on the existing XML (W3C) standard

- Includes a standardized API for generator integration (TGI)

- Validated and released in accordance with the IEEE policies

- IP-XACT is Not Yet Another Electronic Language

- Does not replace existing HDL (VHDL, Verilog, SystemVerilog, SystemC, C++...). But refers to them.

- Forms an electronic databook exposing IP most significant characteristics

- Provides independence over EDA Tools thanks to its standard language neutral API: **TGI**

## IP-XACT is an XML format...

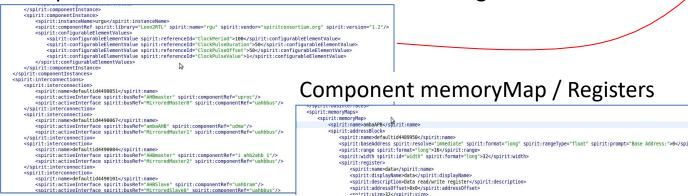

### Component instances and connections in a Design

```

<spirit:instanceName>urqu</spirit:instanceName>

<spirit:componentRef spirit:library="Leon2RTL" spirit:name="rgu" spirit:vendor="spiritconsortium.org" spirit:version="1.2"/>

<spirit:configurableElementValues>

<spirit:configurableElementValue spirit:referenceId="ClockPeriod">100</spirit:configurableElementValue>

<spirit:configurableElementValue spirit:referenceId="ClockPulseDuration">50</spirit:configurableElementValue>

<spirit:configurableElementValue spirit:referenceId="ClockPulseOffset">50</spirit:configurableElementValue>

<spirit:configurableElementValue spirit:referenceId="ClockPulseValue">1</spirit:configurableElementValue>

</spirit:configurableElementValues>

</spirit:componentInstance>

</spirit:componentInstances>

<spirit:interconnections>

<spirit:interconnections</pre>

Component memoryMap / Registers

<spirit:name>defaultid4490051</spirit:name>

<spirit:activeInterface spirit:busRef="MHEmaster" spirit:componentRef="uproc"/>

<spirit:activeInterface spirit:busRef="MirroredMaster0" spirit:componentRef="uproc"/>

<spirit:interconnections</pre>

<spirit:name>defaultid4490067</spirit:name>

<spirit:name>ambaAPB</spirit:name>

<spirit:activeInterface spirit:busRef="ambaAHB" spirit:componentRef="udma"/>

<spirit:addressBlock>

<spirit:activeInterface spirit:busRef="MirroredMaster1" spirit:componentRef="uahbbus"/>

<spirit:name>defaultid4489950</spirit:name>

<spirit:baseAddress spirit:resolve="immediate" spirit:format="long" spirit:rangeType="float" spirit:prompt="Base Address:">0</spi

</pre>

<spirit:interconnection>

rittindrection=

cspirit:name>defaultid4490084</spirit:name>

<spirit:activeInterface spirit:busRef="AHBmaster" spirit:componentRef="i ahb2ahb 1"/>

<spirit:range spirit:format="long">16</spirit:range>

<spirit:width spirit:id="width" spirit:format="long">32</spirit:width>

<spirit:activeInterface spirit:busRef="MirroredMaster2" spirit:componentRef="uahbbus"/>

<spirit:register>

</spirit:interconnection>

<spirit:name>data</spirit:name>

<spirit:interconnection>

<spirit:displayName>data</spirit:displayName>

<spirit:description>Data read/write register</spirit:description>

"spirit:name>defaultid4490101</spirit:name>

<spirit:activeInterface spirit:busRef="AHBSlave" spirit:componentRef="uahbram"/>

<spirit:addressOffset>0x0</spirit:addressOffset>

<spirit:activeInterface spirit:busRef="MirroredSlave8" spirit:componentRef="uahbbus"/>

<cnirit:size>32</spirit:size>

it:volatile>true</spirit:volatile>

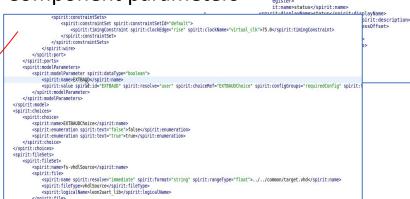

Component parameters

it:access>read-write</spirit:access>

register>

it:name>status</spirit:name>

use/spirit-displayName>

rit:description>

<spirit:constraintSet spirit:constraintSetId="default">

soffset>

<spirit:timingConstraint spirit:clockEdge="rise" spirit:clockName="virtual clk">75.0</spirit:timingConstraint>

</spirit:constraintSet>

</spirit:constraintSets>

</spirit:port>

</spirit:ports>

<spirit:modelParameters>

<spirit:modelParameter spirit:dataType="boolean">

<spirit:name>EXTBAUD</spirit:name>

<spirit:value spirkt:id="EXTBAUD" spirit:resolve="user" spirit:choiceRef="EXTBAUDChoice" spirit:configGroups="requiredConfig" spirit</pre>

</spirit:modelParameter>

</spirit:modelParameters>

</spirit:model>

<spirit:choices>

<spirit:choice>

<spirit:name>EXTBAUDChoice</spirit:name>

<spirit:enumeration spirit:text="false">false</spirit:enumeration>

<spirit:enumeration spirit:text="true">true</spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration></spirit:enumeration

c/snirit-choices>

<spirit:fileSets>

<spirit:fileSet>

<spirit:name>fs-vhdlSource</spirit:name>

<spirit:name spirit:resolve="immediate" spirit:format="string" spirit:rangeType="float">../../common/target.vhd</spirit:name>

<spirit:fileType>vhdlSource</spirit:fileType>

<spirit:logicalName>leon2uart lib</spirit:logicalName</pre>

```

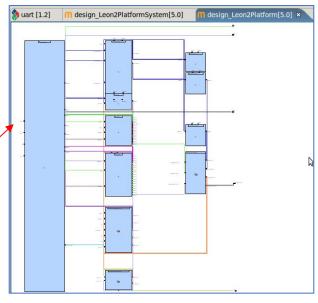

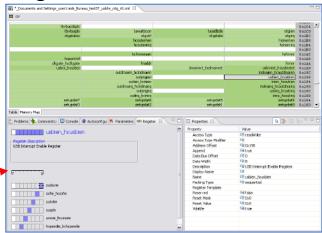

# IP-XACT is an XML format... you do not want to edit by hand

### Component instances and connections in a Design

#### **IP-XACT Editor**

### Component parameters

### **Connectivity Editor**

### Register Editor

it:volatile>true</spirit:volatile>

it:access>read-write</spirit:access>

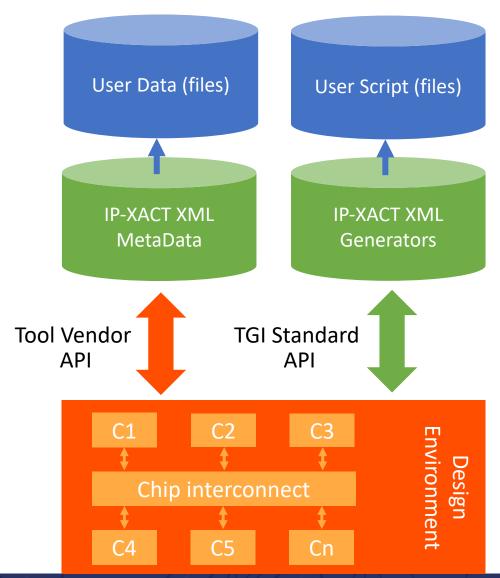

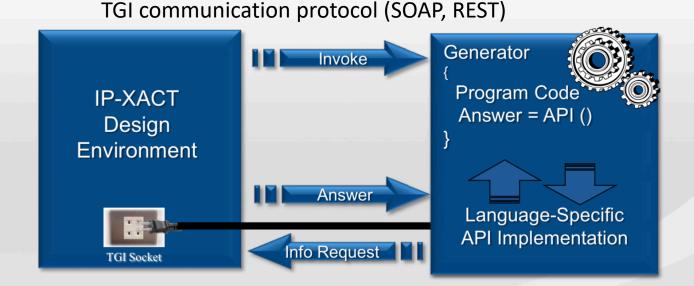

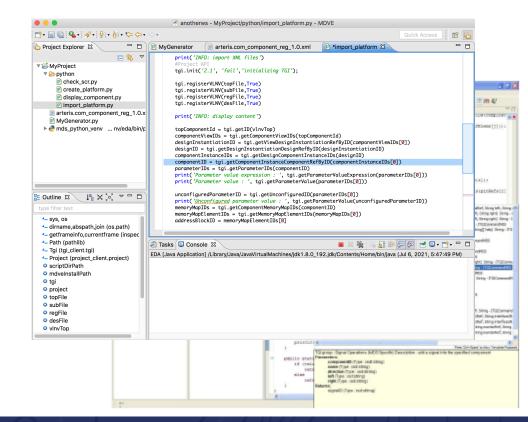

# IP-XACT is an XML format... you can process

You can write Portable (standard)

Generators that can be plugged in

any IP-XACT Design Environment

All IP-XACT Compliant tool shall support the TGI

Generators can be used to expand / customize the Tool features as you desire

# IP-XACT processing using TGI

- Generators can be grouped into generator Chains and invoked from the Design Environment

- Combining individual generators enables the creation of a custom functionality or flow

- Generators can also be attached to Components

- Only activated when the component is added to a Design

Generators are program modules that process IP-XACT XML data into 'something useful' for the design

Key portable mechanism for encapsulating specialist design knowledge Enables designers to deploy specialist knowledge in their design

# Need tools to help writing (TGI) generators

- Write scripts or code (generators) to automate the flow

- The tool provides

- Code writing assistance with integrated documentation.

- On the fly compilation: no syntax errors

- Native TGI API support

- Java + Python + TCL development environment providing:

- Completion assistance,

- debugging environment (Step by Step, tracing, hot code replace...)

# Why IP-XACT 2022?

THE NEW Standard

## From IEEE 1685-2009 to 2014 to 2022

## IP-XACT 2022 benefits for users

- Why adopting the new IP-XACT standard IEEE 1685-2022?

- More straightforward and more complete schema to support todays and tomorrow's complex IP and SoCs

- Includes all of 2009 and 2014

- Why IEEE 1685-2014 was not broadly adopted?

- Conditionality was complex to implement and validate (more specifically at design level)

- Still many features were missing to represent complex memory and connectivity objects

- Limited support from IP and Tool vendors

- Compared to IP-XACT 2009, the new proposed IP-XACT standard includes

- Better support of Memory objects definition

- external definitions, arrays, conditional accesses, resets, sharing, aliasing and broadcasting...

- Better support of Connectivity

- tie, broadcast, SystemVerilog interfaces, structs and unions, VHDL records, SystemC sockets...

- Better support of Parameters propagation and Expressions

- replace Xpath by SystemVerilog expressions, mix multiple IP views

- Support of editing API

- TGI extended

# IP-XACT 2022 major features (vs. 2009)

## New root objects:

- Catalog: like the Magillem 2009 catalog, but now in standard

- TypeDefinitions: new object including (nested) definitions of all memory objects

#### 9.1 Type definitions

An IP-XACT typeDefinitions is the central placeholder for the definition of memory-related objects metadata. A typeDefinitions lists definitions of field access policies, fields, registers, register files, address blocks, banks, memory maps, and memory remaps. These definitions can be configured and referenced in components and other typeDefinitions.

## General changes:

- Expressions (ŠV vs. XPath)

- Added Assertions

- Added support for multiple leaf and hierarchical views

- Added AMS and Power support (added power domains and links)

- Generalize Vendor Extensions

- Conditionality (isPresent) defined as a Vendor Extension

- Added name group (with VLNV, displayName, shortDescription and description), on all top-level objects

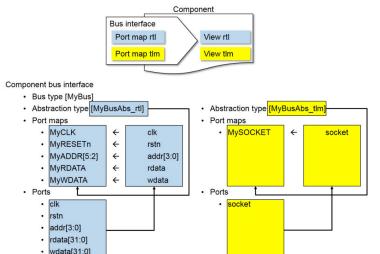

Figure 3.3-Graphical representation of a component with RTL and TLM view and view-specific port maps

# IP-XACT 2022 major features (vs. 2009)

- Changes in Protocols (abstractionDef):

- Support Serial and Multiplexed busses (add packets on logical ports)

- Describe matching widths

- Added new qualifiers on logical ports (isValid, isInterrupt, isRequest, isResponse...)

- Changes in Component ports, interfaces and views:

- Added Structured Ports (to support SVI, Unions and VHDL Records) -> Example

- Added Qualifiers on Ports (isInterrupt, isReset, isClock...)

- Added Parameters on Ports

- Changed Transactional ports to support SystemC TLM sockets

- Linked Ports and register Fields -> Example

- Added HDL properties in views (packageName, libraryName, architectureName...)

- Added Runtime model parameters

- View dependant interfaces/ports and parameters

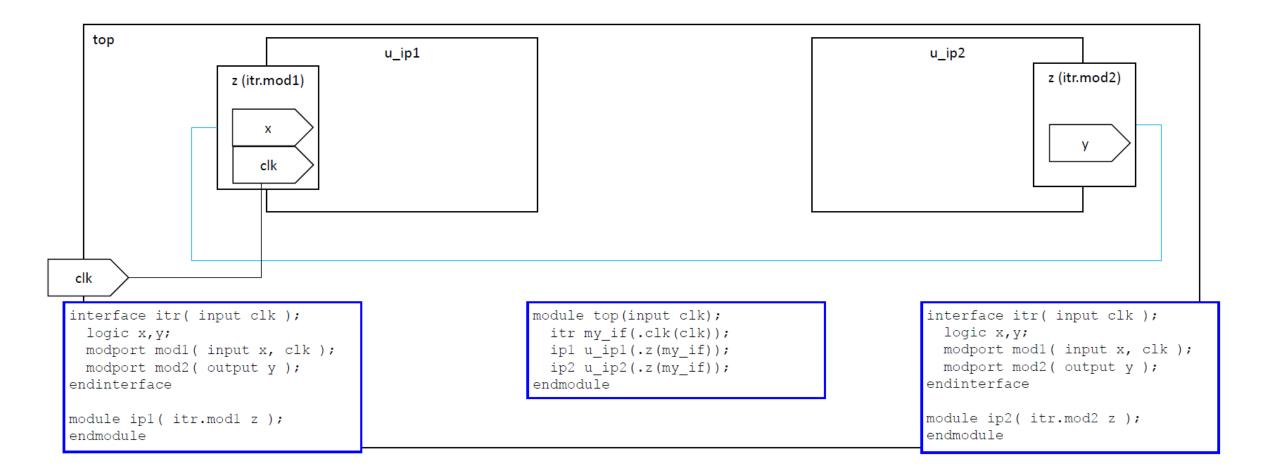

# Example: Structured port – SV interface

### SV interface

```

name=z

structured

interface

subPort, isIO=true

name=<mark>clk</mark>

wire

direction=in

subPort

name=x

wire

direction=inout

structPortTypeDef

typeName=itr

role=mod1

```

```

interface itr(input clk);

logic x,y;

modport mod1(input x, clk);

modport mod2(output y);

endinterface

module ip(itr.mod1 z);

endmodule

```

## Example: Structured port – SVI connection

2023/06/22

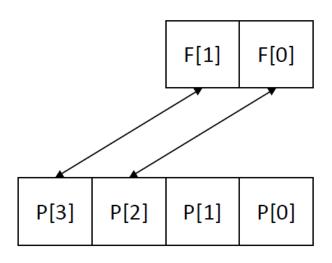

# Example: Field map

```

register

name=<mark>R</mark>

field

name=<mark>F</mark>

bitOffset=0

bitWidth=2

port

name=P

vector=[3:0]

fieldMap

fieldSlice

registerRef=R

fieldRef=<mark>F</mark>

range=[3:2]

modeRef=FUNC

```

# IP-XACT 2022 major features (vs. 2009)

- Changes in Component Memory objects:

- Improved HDL access Handle, including string expressions with index variables

- Added modes, modes condition (using SV expression) and mode references permitting the support of secure registers -> Example

- Added access policies and access restrictions

- Added field and register aliasing & broadcasting

- Extended fields enumerated values, and added enumerations references

- Added Reset at bitField level + support for Multiple resets

- Added CPU memory map using references to addressSpaces and segments of addressSpaces

- Added arrays (dim), indices, stride and bitStride to memory objects

## Example: Mode-dependent register access

## component modes

```

mode

name=TEST

portSlice=myPortSlice

portRef=test_mode

condition=$ipxact_port_value(myPortSlice)==1

mode

name=FUNC

portSlice=myPortSlice

portRef=test mode

condition=$ipxact_port_value(myPortSlice)==0

```

## register access policy

```

register

name=myReg

addressOffset=0

size=32

access Policy

modeRef=TEST

access=read-write

accessPolicy

modeRef=FUNC

access=read-only

```

A condition expression can contain terms for port slice values, register field slice values, and mode condition values

# IP-XACT 2022 major features (vs. 2009)

- Changes in Design connectivity and Design configuration:

- Improved Design connections: top feedthrough, top tied ports, interconnections (N vs. 2)...

- Support exclude logical port mechanism in interface connection

- Support is Virtual instance (that should not be netlisted)

- Added Parameters propagation through hierarchy

## TGI

- Base (get)

- Extended (create/set/add/remove)

- Supports REST (in addition to SOAP) communication protocol

## SCRs

- + 100 SCR added vs. 2009

# 質疑応答