#### Tutorial 7 Tutorial on RISC-V Design and Verification

Kevin McDermott - Imperas Software Ltd.

Zdenek Prikryl - Codasip Ltd. Peter Shields - UltraSoC Technologies Ltd.

# **Tutorial on RISC-V Design and Verification**

- Speakers:

- Kevin McDermott Imperas Software Ltd:

- Zdenek Prikryl Codasip Ltd.

- Peter Shields UltraSoC Technologies Ltd.

- RISC-V Tutorial overview

- 1. Introduction to RISC-V ISA & The RISC-V Foundation: ISA Freedom & innovation

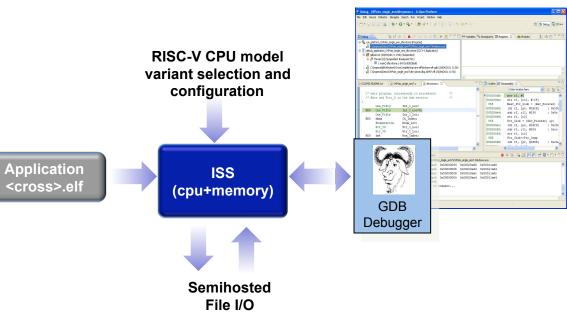

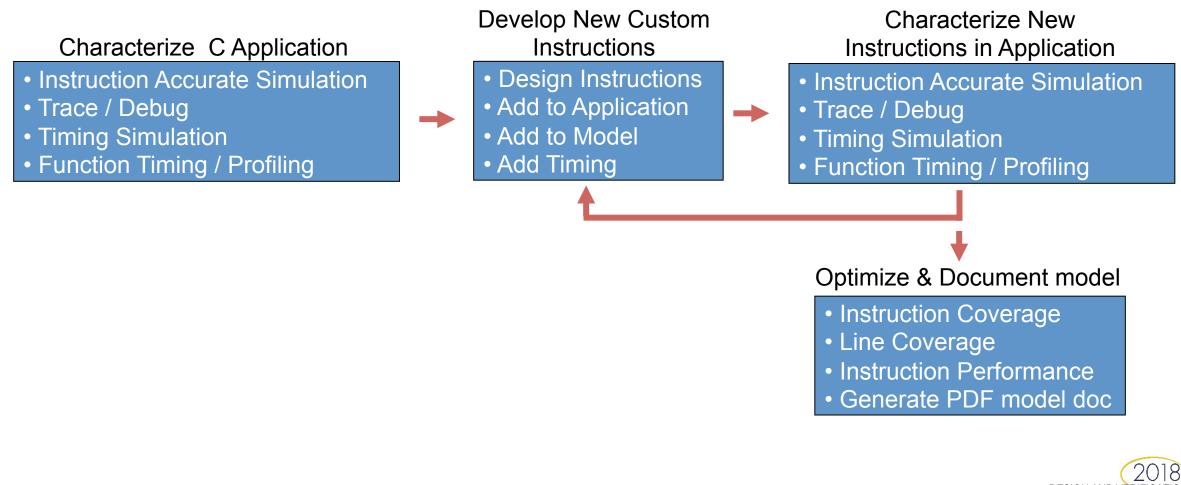

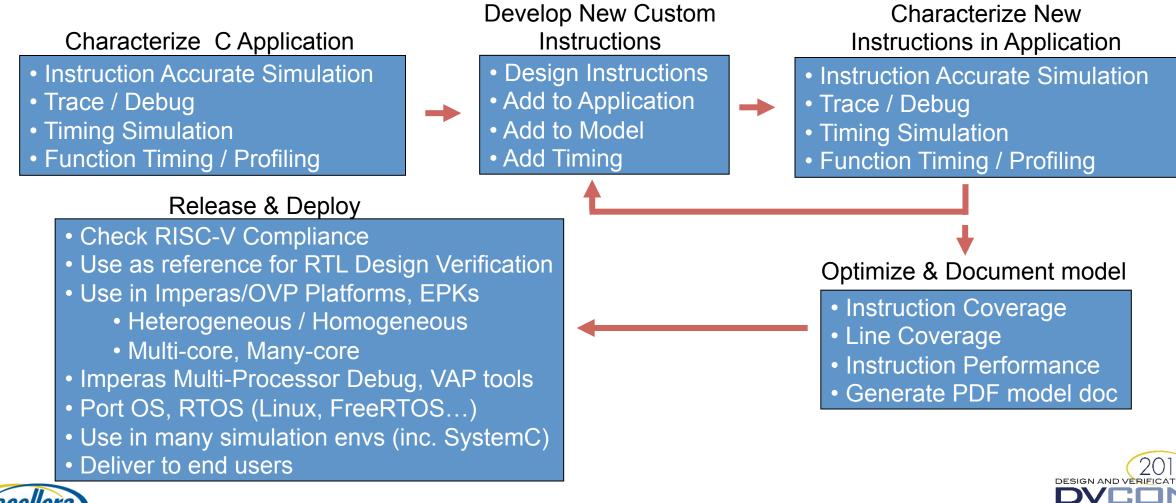

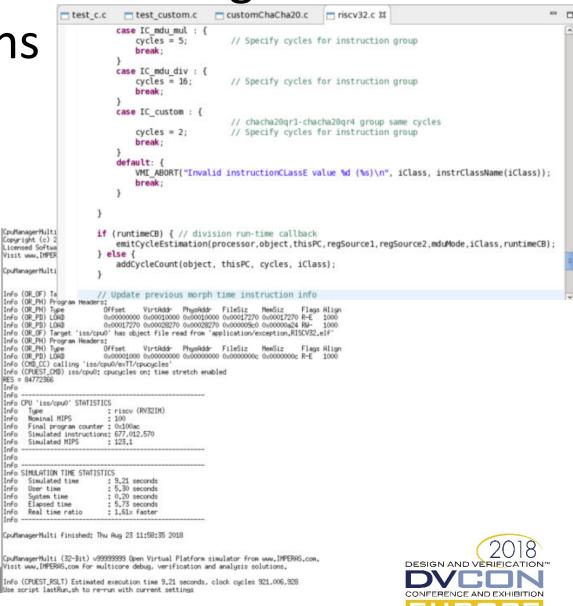

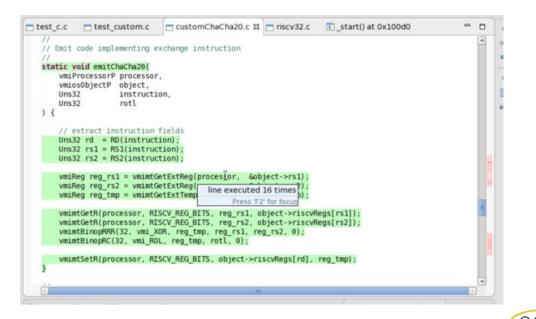

- 2. Imperas: adding RISC-V custom instructions for software development

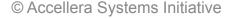

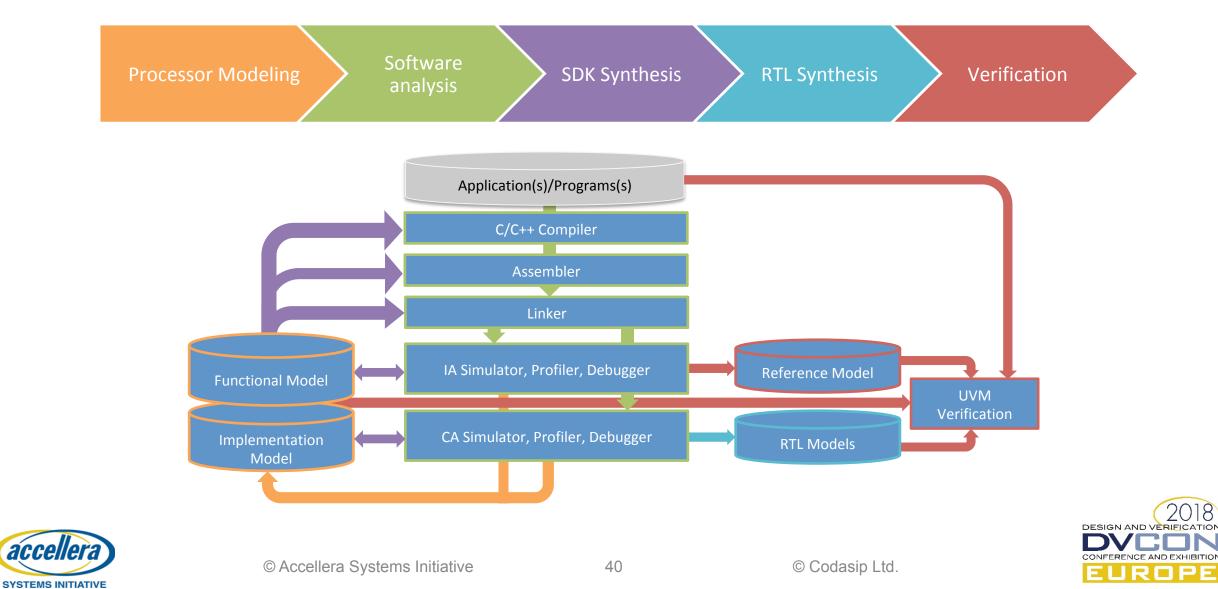

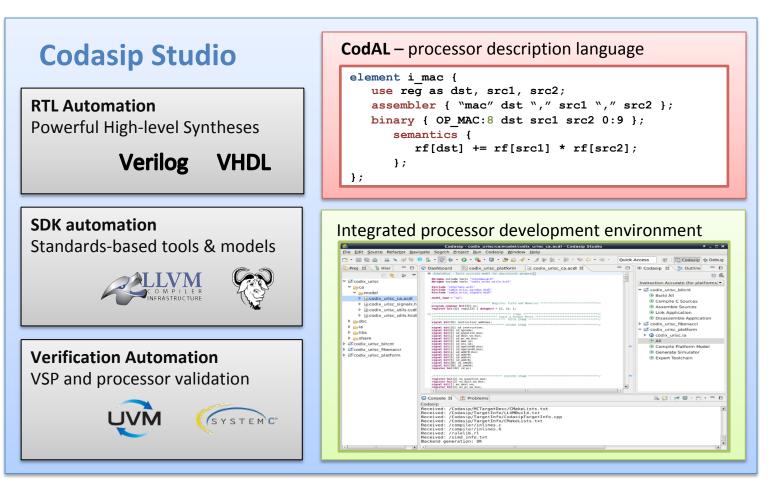

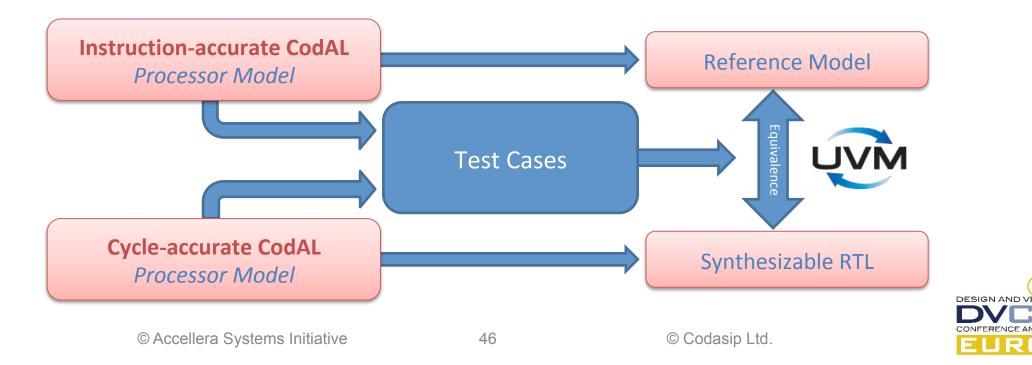

- 3. Codasip: hardware design flow for RISC-V IP core and extensions

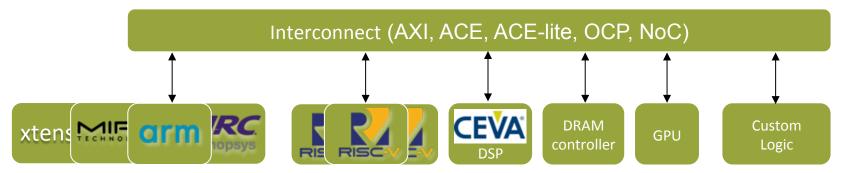

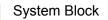

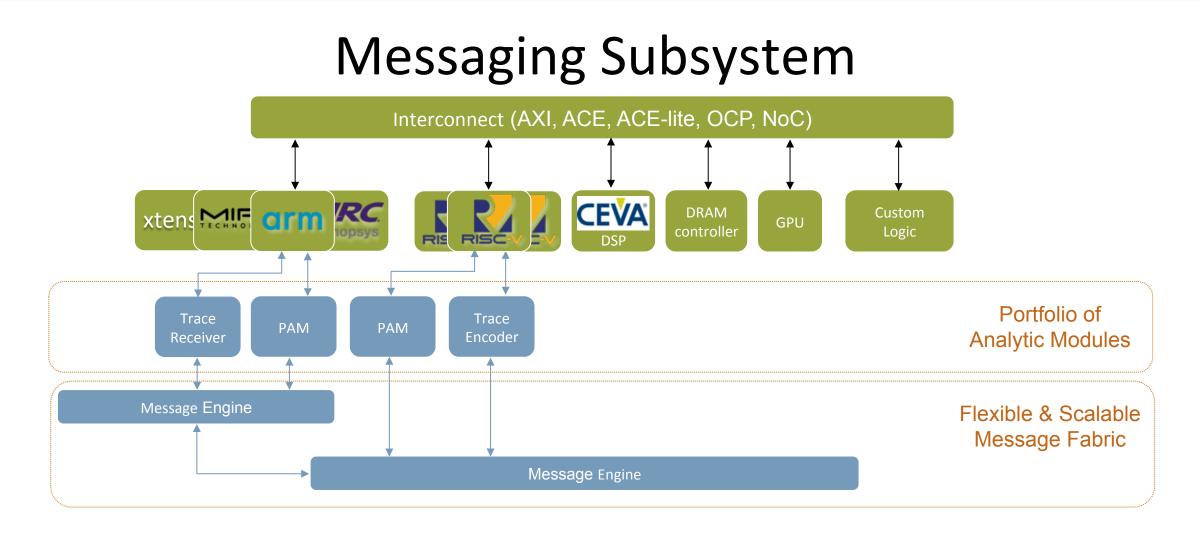

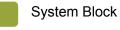

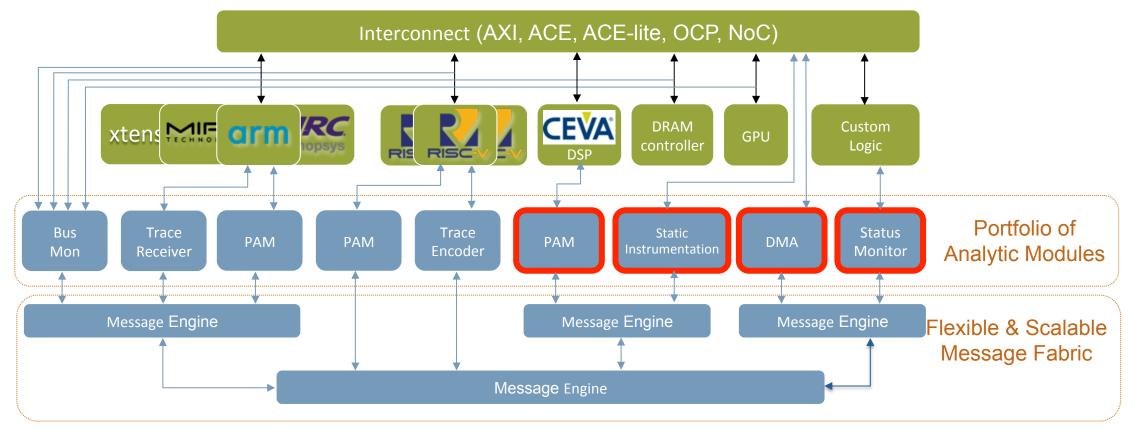

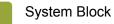

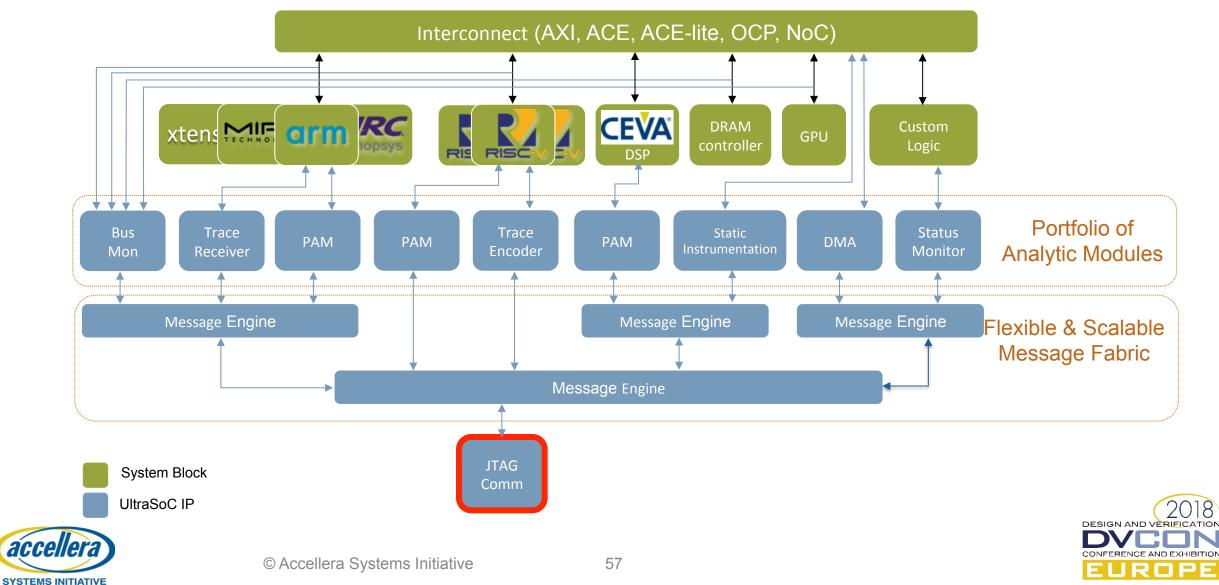

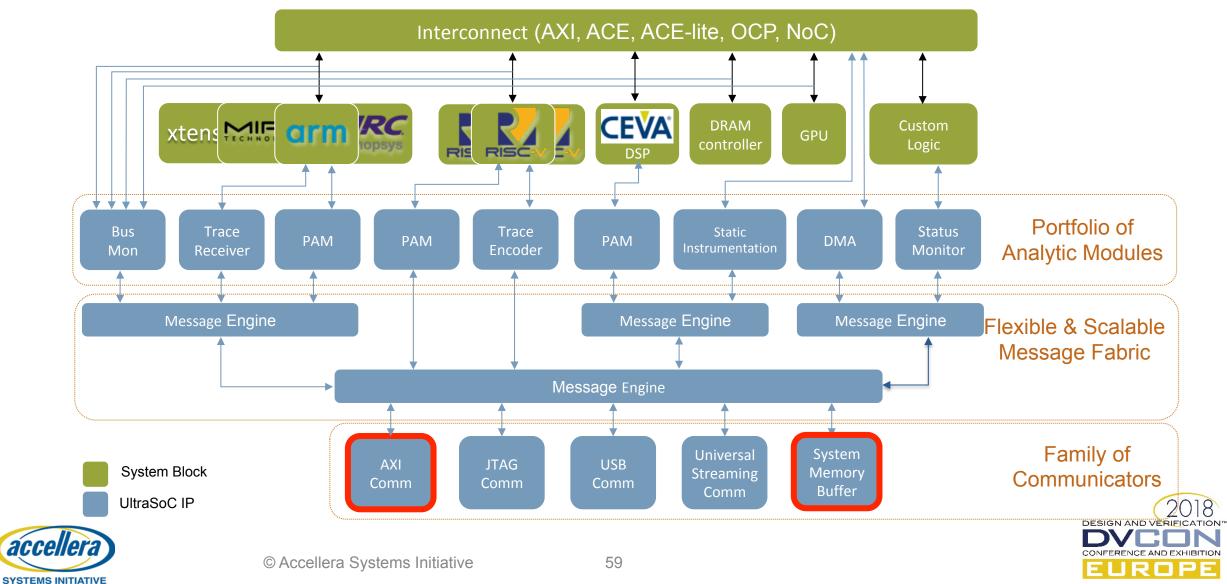

- 4. UltraSoC: on-chip Analytics for SoC, and heterogeneous architectures

#### Introduction to RISC-V ISA

#### • <u>https://riscv.org</u>

RISC-V (pronounced "risk-five") is an open, free ISA enabling a new era of processor innovation through open standard collaboration. Born in academia and research, RISC-V ISA delivers a new level of free, extensible software and hardware freedom on architecture, paving the way for the next 50 years of computing design and innovation.

#### **RISC-V Background**

- In 2010, after many years and many projects using MIPS, SPARC, and x86 as basis of research, it was time for the Computer Science team at UC Berkeley to look at what ISAs to use for their next set of projects

- Obvious choices: x86 and ARM

- x86 impossible too complex, IP issues

- ARM mostly impossible complex, IP issues

- So UC Berkeley started "3-month project" during the summer of 2010 to develop their own clean-slate ISA

# RISC-V Background (cont'd)

- Four years later, in May of 2014, UC Berkeley released frozen base user spec

- many tapeouts and several research publications along the way

- The name RISC-V (pronounced *risk-five*), was chosen to represent the fifth major RISC ISA design effort at UC Berkeley

- RISC-I, RISC-II, SOAR, and SPUR were the first four projects with the original RISC-I publications dating back to 1981

- In August 2015, articles of incorporation were filed to create a nonprofit RISC-V Foundation to govern the ISA

### What's Different about RISC-V?

- Simple

- Far smaller than other commercial ISAs

- Clean-slate design

- Clear separation between user and privileged ISA

- Avoids µarchitecture or technology-dependent features

- A modular ISA

- Small standard base ISA

- Multiple standard extensions

- Designed for *extensibility/specialization*

- Variable-length instruction encoding

- Vast opcode space available for instruction-set extensions

- Stable

- Base and standard extensions are frozen

- Additions via optional extensions, not new versions

#### **RISC-V Base Plus Standard Extensions**

- Four base integer ISAs

- RV32E, RV32I, RV64I, RV128I

- Only <50 hardware instructions needed for base</li>

- Standard extensions

- M: Integer multiply/divide

- A: Atomic memory operations (AMOs + LR/SC)

- F: Single-precision floating-point

- D: Double-precision floating-point

- G = IMAFD, "General-purpose" ISA

- Q: Quad-precision floating-point

- C: compressed 16b encodings for 32b instructions

- All the above are a fairly standard RISC encoding in a fixed 32-bit instruction format

#### **RV32I / RV64I / RV128I**

| Base Integer 1         |     |               |                 |

|------------------------|-----|---------------|-----------------|

| Category Name          |     |               | 4 128)I Base    |

| Loads Load Byte        | I   | LB            | rd,rs1,imm      |

| Load Halfword          | I   | LH            | rd,rs1,imm      |

| Load Word              |     | $L\{W D Q\}$  | rd,rs1,imm      |

| Load Byte Unsigned     |     | LBU           | rd,rs1,imm      |

| Load Half Unsigned     | I   | L{H W D}U     | rd,rs1,imm      |

| Stores Store Byte      | S   | SB            | rs1,rs2,imm     |

| Store Halfword         | -   | SH            | rs1,rs2,imm     |

| Store Word             |     | S{W D Q}      | rs1,rs2,imm     |

| Shifts Shift Left      | R   | $SLL\{ W D\}$ | rd,rs1,rs2      |

| Shift Left Immediate   | I   | $SLLI{ W D}$  | rd,rs1,shamt    |

| Shift Right            |     | SRL{ W D}     | rd,rs1,rs2      |

| Shift Right Immediate  | Ι   | SRLI{ W D}    | rd,rs1,shamt    |

| Shift Right Arithmetic |     | SRA{ W D}     | rd,rs1,rs2      |

| Shift Right Arith Imm  | Ι   | SRAI{ W D}    | rd,rs1,shamt    |

| Arithmetic ADD         | R   | ADD{ W D}     | rd,rs1,rs2      |

| ADD Immediate          | Ι   | ADDI{ W D}    | rd,rs1,imm      |

| SUBtract               | R   | SUB{ W D}     | rd,rs1,rs2      |

| Load Upper Imm         | U   | LUI           | rd,imm          |

| Add Upper Imm to PC    | U   | AUIPC         | rd,imm          |

| Logical XOR            | R   | XOR           | rd,rs1,rs2      |

| XOR Immediate          | Ι   | XORI          | rd,rs1,imm      |

| OR                     | R   | OR            | rd,rs1,rs2      |

| OR Immediate           | Ι   | ORI           | rd,rs1,imm      |

| AND                    | R   | AND           | rd,rs1,rs2      |

| AND Immediate          | Ι   | ANDI          | rd,rs1,imm      |

| Compare Set <          | R   | SLT           | rd,rs1,rs2      |

| Set < Immediate        | Ι   | SLTI          | rd,rs1,imm      |

| Set < Unsigned         | R   | SLTU          | rd,rs1,rs2      |

| Set < Imm Unsigned     | Ι   | SLTIU         | rd,rs1,imm      |

| Branches Branch =      | SB  | BEQ           | rs1,rs2,imm     |

| Branch ≠               | SB  | BNE           | rs1,rs2,imm     |

| Branch <               | SB  | BLT           | rs1,rs2,imm     |

| Branch ≥               | SB  | BGE           | rs1,rs2,imm     |

| Branch < Unsigned      | SB  | BLTU          | rs1,rs2,imm     |

| Branch $\geq$ Unsigned | SB  | BGEU          | rs1,rs2,imm     |

| Jump & Link J&L        | UJ  | JAL           | rd,imm          |

| Jump & Link Register   | I   | JALR          | ,<br>rd,rs1,imm |

| Synch Synch thread     | Ι   | FENCE         |                 |

| Synch Instr & Data     | I   | FENCE.I       |                 |

| System System CALL     | Ι   | SCALL         |                 |

| System BREAK           | I   | SBREAK        |                 |

| Counters ReaD CYCLE    | I   | RDCYCLE       | rd              |

| ReaD CYCLE upper Half  | I   | RDCYCLEH      | rd              |

| ReaD TIME              | Ī   | RDTIME        | rd              |

| ReaD TIME upper Half   | -   | RDTIMEH       | rd              |

|                        | · • |               |                 |

| ReaD INSTR RETired     | I   | RDINSTRET     | rd              |

+14 Privileged 2

+ 8 for M

+ 34 for F, D, Q

+ 46 for C

**RISC-V Reference Card** ④

3

+ 11 for A

32-bit Instru

| ction Formats |         |           |       |         |        |     |     |       |       |         |         |     |     |

|---------------|---------|-----------|-------|---------|--------|-----|-----|-------|-------|---------|---------|-----|-----|

|               | l       |           |       |         |        |     |     |       |       |         |         |     | _   |

| R             | 31      | 30 2      | 5 24  | 21      | 20     | 19  | 15  | 14    | 12 11 | 8       | 7       | 6   | 0   |

|               | fı      | inct7     |       | rs2     |        | rs1 |     | funct | 3     | r       | d       | opo | ode |

| I             |         | imm[]     | 11:0  |         |        | rs1 |     | funct | 3     | r       | d       | opo | ode |

| S             | jm      | n[11:5]   |       | rs2     |        | rs1 |     | funct | 3     | imm     | 4:0     | opo | ode |

| SB            | imm 🖸   | imm[10:5] |       | rs2     |        | rs1 |     | funct | 3 ir  | nm[4:1] | imm[11] | opo | ode |

| U             |         |           | im    | im[31:1 | 2]     |     |     |       |       | r       | d       | opo | ode |

| UJ            | imm[20] | imm[]     | 10:1] | ir      | nm[11] | im  | m[1 | 9:12] |       | r       | d       | opo | ode |

|               |         |           | _     | _       | _      |     | _   | _     | _     |         |         | _   | _   |

© Accellera Systems Initiative

DESIGN AND VER

#### RV32I / RV64I / RV128I + M, A, F, D, Q, C

|                             |       | <u>5C</u> | -                        |                        |                        |                | (2010)                  | 2                                 |                    |                           | 3                                      |               |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | e Card 4                 |

|-----------------------------|-------|-----------|--------------------------|------------------------|------------------------|----------------|-------------------------|-----------------------------------|--------------------|---------------------------|----------------------------------------|---------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Base Intege                 |       |           |                          |                        | -                      |                | (32 64 128)<br>nnemonic | Catego                            |                    | Extensions: R             | <b>RV32{F\D\Q}</b><br>D\Q} (HP/SP,DP,Q |               |                          | essed Instr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | uctions: RVC             |

| ategory Nan<br>Dads Load By | -     | 1         | 2 64 128)I Base          | Category<br>CSR Access | Name<br>Atomic R/W     |                |                         |                                   | ry Nam<br>Lo       |                           |                                        | ,             |                          | CL C.LW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RVC                      |

| Load Halfwo                 |       |           | rd,rs1,imm<br>rd,rs1,imm |                        | Read & Set Bi          |                |                         | rs1 Load<br>rs1 Store             | Sto                |                           |                                        |               | Load Word<br>Load Word S | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | rd',rs1',imm<br>? rd,imm |

| Load Wo                     |       |           |                          |                        | ead & Clear Bi         |                |                         | rs1 Arithm                        |                    | DD R FADD. $\{s \mid d\}$ |                                        |               | Load Word S              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | rd',rs1',imm             |

| Load Byte Unsign            |       |           | rd,rs1,imm               |                        | omic R/W Imm           |                | · · ·                   |                                   | SUBtra             |                           |                                        |               | Load Double S            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |

| Load Half Unsign            |       |           | }U rd,rs1,imm            |                        | & Set Bit Imm          |                |                         |                                   | MULtip             |                           | 0 0 rd, rs1, rs                        |               |                          | d CL C.LQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          |

| tores Store By              |       |           | rs1,rs2,imm              | Atomic Read &          |                        |                |                         |                                   | DIVid              |                           |                                        |               |                          | P CI C.LOSP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                          |

| Store Halfwo                |       |           | rs1,rs2,imm              | Change Leve            |                        |                |                         |                                   | SOuare Roo         |                           | D 0} rd,rs1                            |               |                          | d CL C.LBU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | rd',rsl',imm             |

| Store Wo                    |       | S{W D Q   |                          | _                      | ent Breakpoint         |                |                         | Mul-Ad                            |                    |                           |                                        | <u>ລ່ / ໄ</u> | Float Load Wor           | 10 million (10 mil | rd',rs1',imm             |

| hifts Shift Le              | -     |           | <pre>D} rd,rs1,rs2</pre> |                        | onment Return          |                |                         |                                   | Multiply-SUBtrac   |                           | D 0} rd,rs1,rs2                        | 153           | Float Load Doubl         | e CL C.FLD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | rd',rsl',imm             |

| Shift Left Immedia          |       |           | D} rd,rs1,shamt          | Trap Redirec           |                        |                |                         | Negativ                           | e Multiply-SUBtrac |                           | D 0} rd,rs1,rs2                        | TST FL        | oat Load Word S          | P CI C.FLWS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                          |

| Shift Rid                   |       |           | D} rd,rs1,rs2            |                        | to Hyperviso           |                |                         |                                   | ative Multiply-AD  |                           | DQ rd,rs1,rs2                          |               | at Load Double S         | P CI C.FLDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SP rd. imm               |

| Shift Right Immedia         |       |           | D} rd,rs1,shamt          | Hypervisor Trap        |                        |                |                         |                                   | nject SiGN sour    |                           | D Q} rd,rs1,rs                         |               | Store Word               | CS C.SW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | rs1'.rs2'.imm            |

| Shift Right Arithme         |       |           | D} rd,rs1,rs2            | Interrupt Wa           |                        |                |                         |                                   | gative SiGN source |                           | D Q} rd,rs1,rs                         |               | Store Word S             | P CSS C.SWSF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | rs2,imm                  |

| Shift Right Arith Im        |       |           | D} rd,rs1,shamt          |                        | pervisor FENC          |                | CE.VM rs1               |                                   | Xor SiGN source    |                           |                                        |               | Store Doub               | e CS C.SD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | rs1',rs2',imm            |

| rithmetic A                 | _     | -         | D} rd,rs1,rs2            | Optional               | Multiply-D             | Divide Ext     | ension: RV32M           | Min/M                             |                    |                           |                                        |               | Store Double S           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | rs2,imm                  |

| ADD Immedia                 |       |           | D} rd,rs1,imm            | Category               | Name Fmt               |                | 32M (Mult-Div)          |                                   | MAXimur            |                           |                                        |               | Store Qua                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | rs1',rs2',imm            |

| SUBtra                      |       |           | D} rd,rs1,rs2            |                        | MULtiply R             | MUL{ W D}      | } rd,rs1,rs2            | Compa                             | re Compare Floa    |                           |                                        |               | Store Quad S             | P CSS c.sosp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | rs2,imm                  |

| Load Upper Im               |       |           | rd,imm                   | MULtiply up            |                        | MULH           | rd,rs1,rs2              |                                   | Compare Float      |                           |                                        | 2             | Float Store Wor          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | rd',rs1',imm             |

| Add Upper Imm to            |       |           | rd,imm                   | MULtiply Half S        |                        | MULHSU         | rd,rs1,rs2              |                                   | Compare Float      |                           |                                        | 2             | loat Store Doubl         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | rd',rs1',imm             |

| ogical XC                   |       |           | rd,rs1,rs2               | MULtiply upper         |                        | MULHU          | rd,rs1,rs2              | Catego                            | orize Classify Ty  |                           |                                        | Fic           | at Store Word S          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SP rd, imm               |

| XOR Immedia                 | te I  | XORI      | rd,rs1,imm               | Divide                 | DIVide R               | DIV{ W D}      |                         |                                   | Move from Integ    |                           | rd,rs1                                 | Float         | t Store Double S         | P CSS C.FSDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | P rd, imm                |

| O                           |       | OR        | rd,rs1,rs2               | DIVide U               | Insigned R             | DIVU           | rd,rs1,rs2              |                                   | Move to Intege     |                           | rd,rs1                                 | Arithme       | tic ADD                  | CR C.ADD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | rd,rs1                   |

| OR Immedia                  | te I  | ORI       | rd,rs1,imm               | RemainderRE            |                        | REM{  W D}     |                         | Conve                             | rt Convert from 1  |                           | Q}.W rd,rs1                            |               | ADD Wor                  | d CR C.ADDW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | rd',rs2                  |

| A                           | D R   | AND       | rd,rs1,rs2               | REMainder U            | Insigned R             | REMU{  W D     | D} rd.rs1.rs2           | Convert                           | from Int Unsigne   | d R FCVT. {S D            | Q}.WU rd,rs1                           |               | ADD Immediat             | e CI C.ADDI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | rd,imm                   |

| AND Immedia                 | te I  | ANDI      | rd,rs1,imm               | Optional               | Atomic In              | struction      | Extension: RV           | 4                                 | Convert to Ir      | TR FCVT.W.{S              | D Q} rd,rs1                            |               | ADD Word Imr             | n CI C. ADDI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | W rd,imm                 |

| ompare Set                  |       |           | rd,rs1,rs2               | Category               | Name Fm                | t RV{32        | 64 128}A (Atomi         | c) Conv                           | ert to Int Unsigne | d R FCVT.WU.{             | S D Q} rd,rs1                          |               | ADD SP Imm * 1           | 6 CI C.ADDI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 16SP x0,imm              |

| Set < Immedia               | te I  | SLTI      | rd,rs1,imm               | Load Load R            | Reserved R             | LR. (W D )     | Q} rd,rs1               |                                   | uration Read St    |                           | rd                                     |               | ADD SP Imm *             | 4 CIW C.ADDI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4SPN rd', imm            |