# Streamlining Low Power Verification: From UPF to Signoff

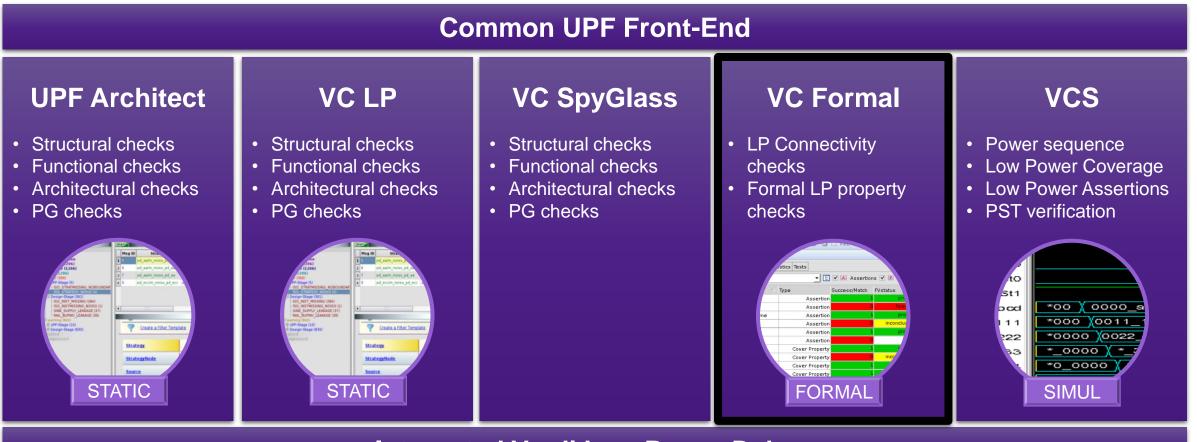

# Synopsys' Low Power Verification

Find Power Bugs Pre-Silicon

### **Integrated Verdi Low Power Debug**

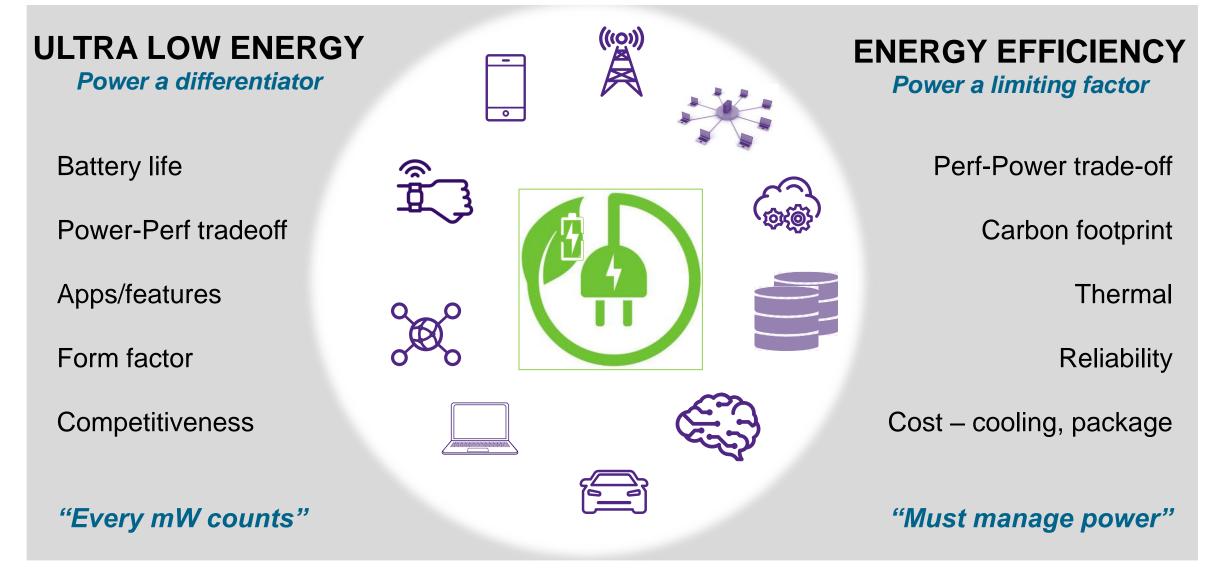

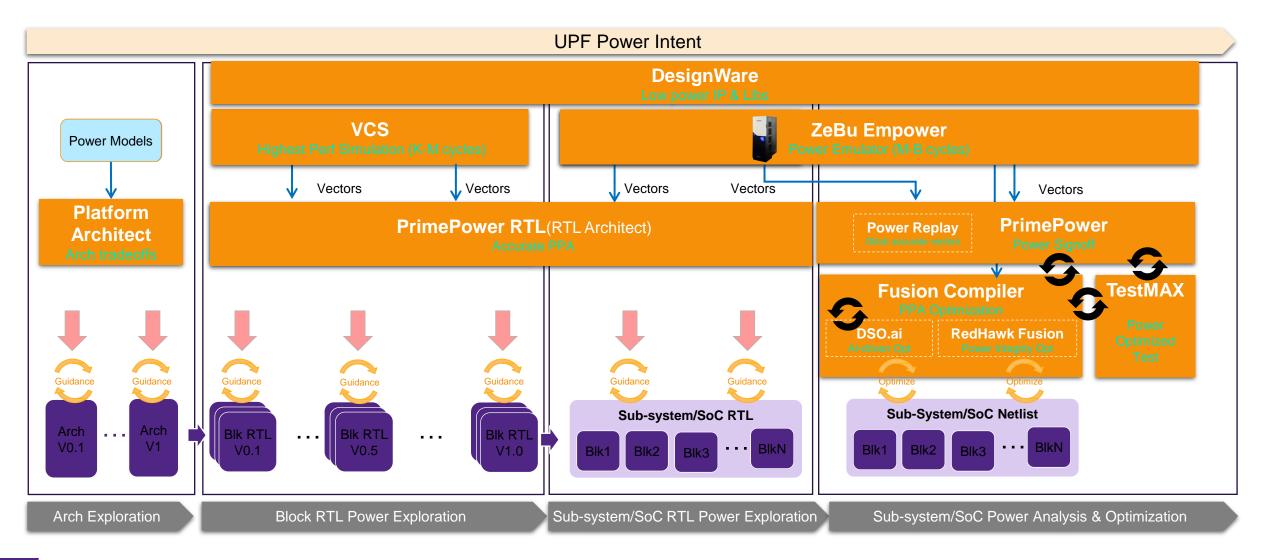

## Market Needs Driving E2E Power Flow

**Synopsys**<sup>®</sup>

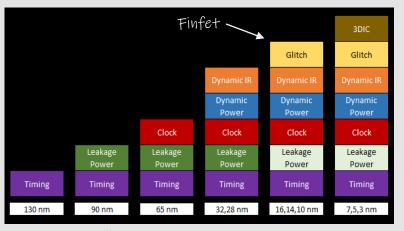

### Power – The Next Generation Challenges

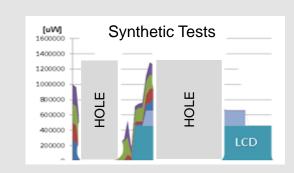

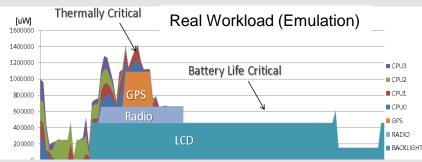

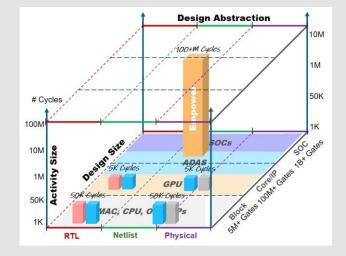

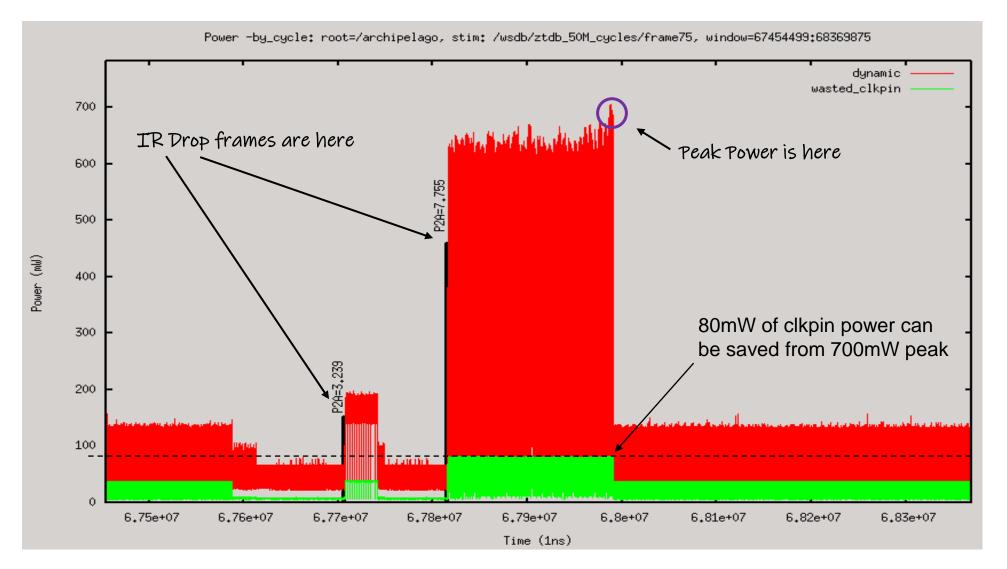

Shrinking technology nodes have increased chip power density, IR drop problem, and a significant jump in glitch power. Synthetic simulation vectors often miss cross IP power bugs, firmware bugs, and overestimate peak power. This necessitates use of real workloads for power analysis and signoff. Growth in design and workload sizes makes cycle power analysis very memory and compute intensive, necessitating scalable distributed Power Analysis solution

Technology Nodes ----

### **Typical Low Power ASIC Design Flow**

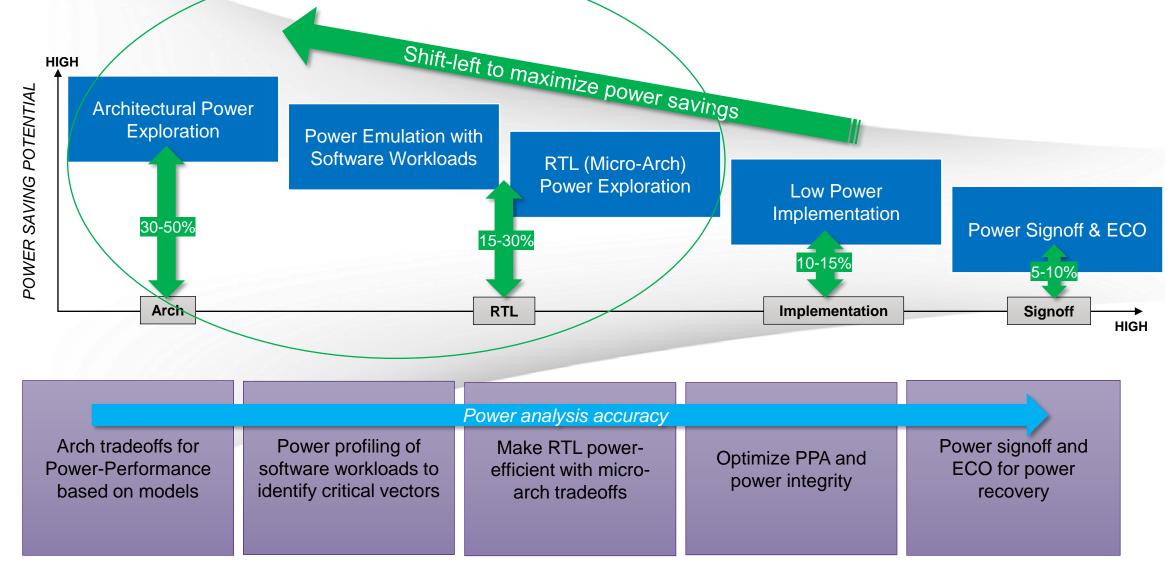

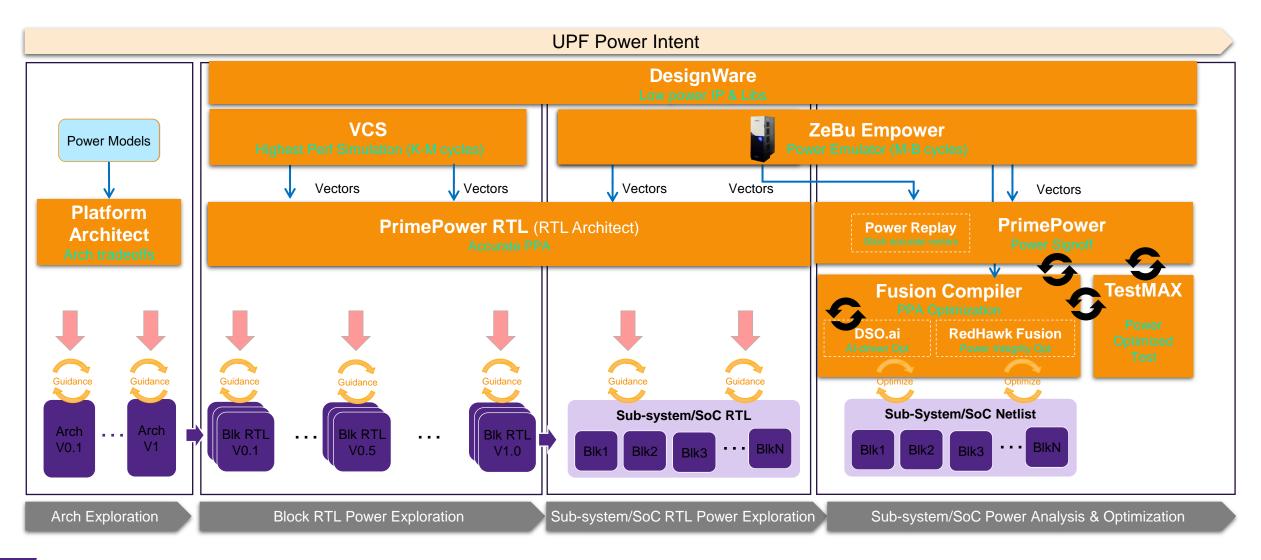

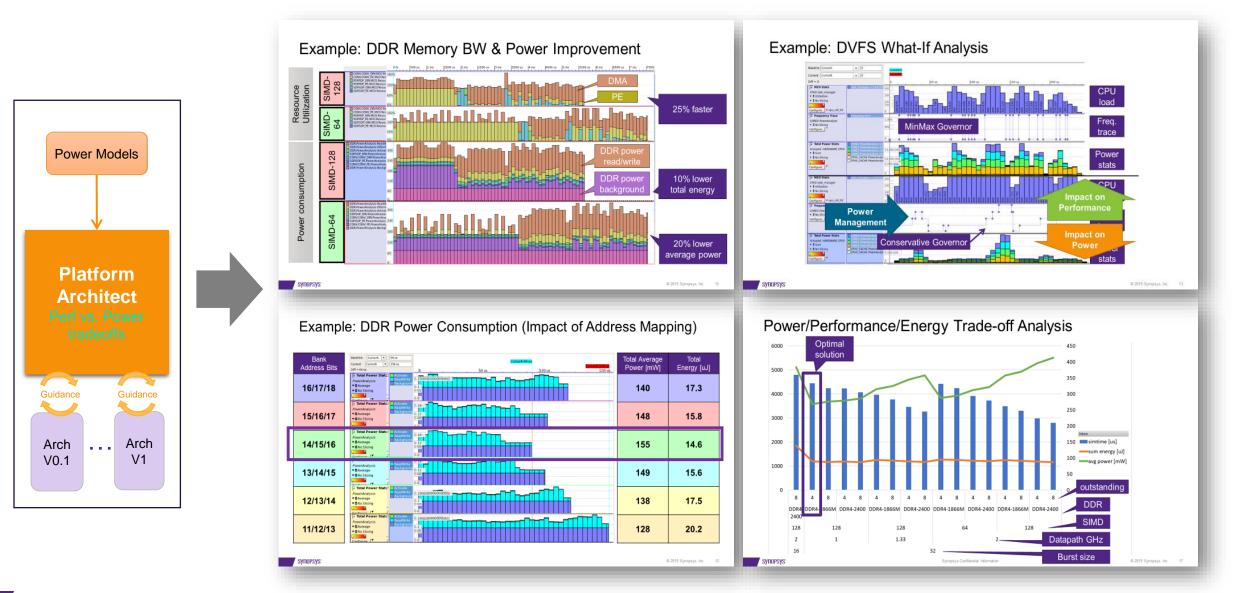

### Software-Driven Power Exploration, Analysis & Optimization

**Synopsys**<sup>®</sup>

# Key Areas for Low Power Design

- Architectural Analysis and Power Efficient Macro Architecture Selection

- Workload Analysis/Profiling/Selection

- RTL Power Analysis and Optimization Guidance

- Power Optimization during Synthesis/P&R and ECO

- Power Signoff and Design Closure

### **Architectural Performance/Power Exploration**

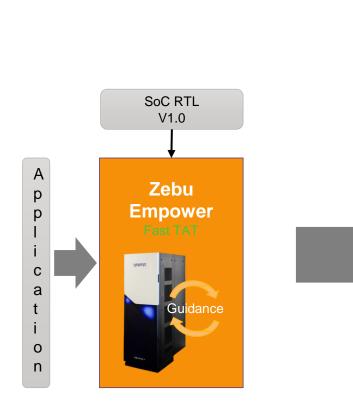

### Workload Analysis/Profiling/Selection Through Emulation

10000 Clock Pin toggles

1500

20000

Vectors for Analysis and Optimization

3000

100

ъ

### Vector Profiling Using Emulation Workloads

#### ′ synopsys°

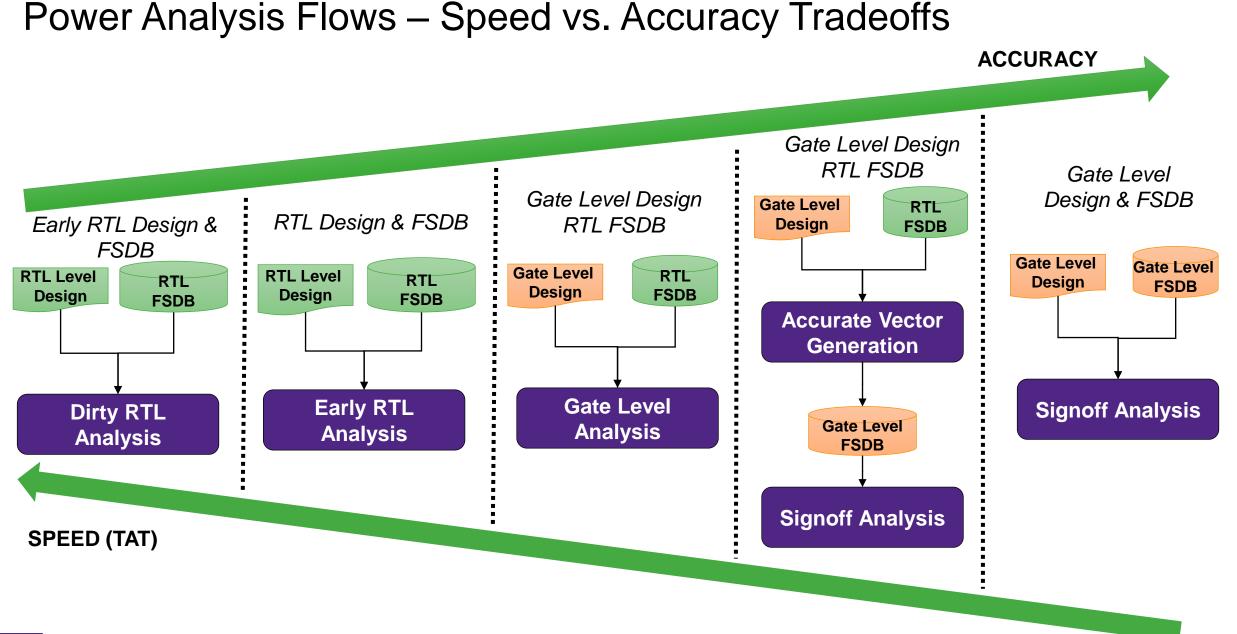

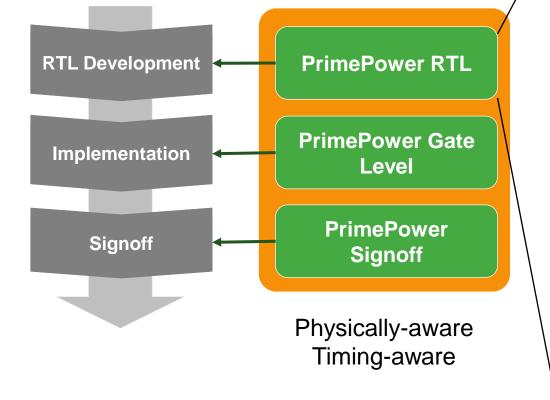

### **RTL Power Analysis/Exploration**

Multiple views to identify hot spots

**Power linting –** structural linting rules

Glitch power - source identification & ranking

Clock gating efficiency – per design hierarchy

Register gating efficiency – CGE & Q/Clk ratios

Clock tree efficiency - cascaded CGE

XOR, STC, ODC gating with power saving

Memory profiling with power saving

Micro-architectural explorations (DW, FSM, Fmax/Vmin)

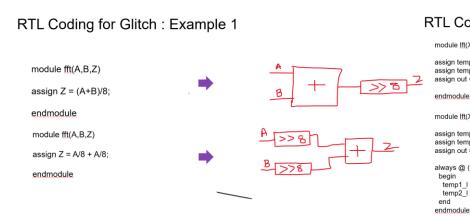

# Power Efficient RTL Coding Guidelines

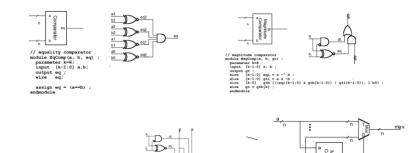

#### RTL Coding for Multiplexer : Example 6 (One Hot/Gray/Binary)

RTL Coding for Comparator : Example 7 (Magnitude/Equality)

Power Consumption: Without gillches: 951.7 vW With gillches: 1357.7 vV

# Synopsys°

# **RTL Power Analysis/Exploration**

Multiple views to identify hot spots

**Power linting –** structural linting rules

### Glitch power - source identification & ranking

Clock gating efficiency – per design hierarchy

**Register gating efficiency** – CGE & Q/Clk ratios

**Clock tree efficiency** – cascaded CGE

XOR, STC, ODC gating with power saving

Memory profiling with power saving

**Micro-architectural explorations** (DW, FSM, Fmax/Vmin)

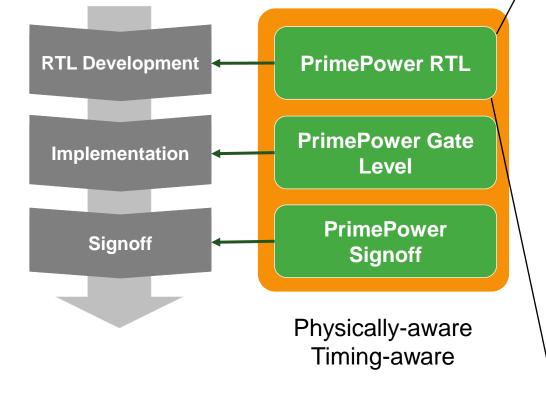

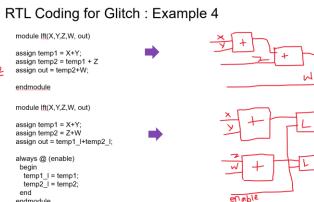

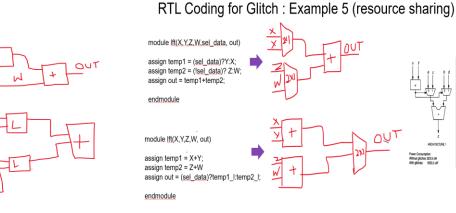

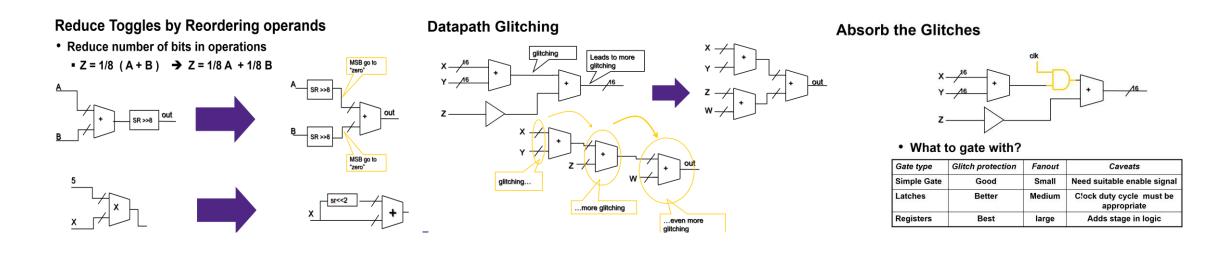

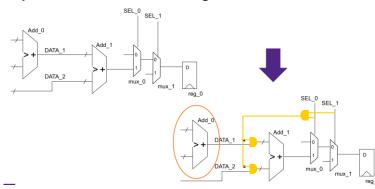

### Glitch Power Optimization, by changing Architecture

**Operand Isolation/Data Gating**

#### **Resource Sharing**

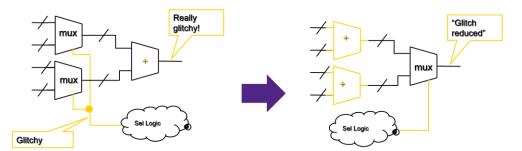

### Low Power Technologies in Fusion Compiler

**SYNOPSYS**<sup>®</sup>

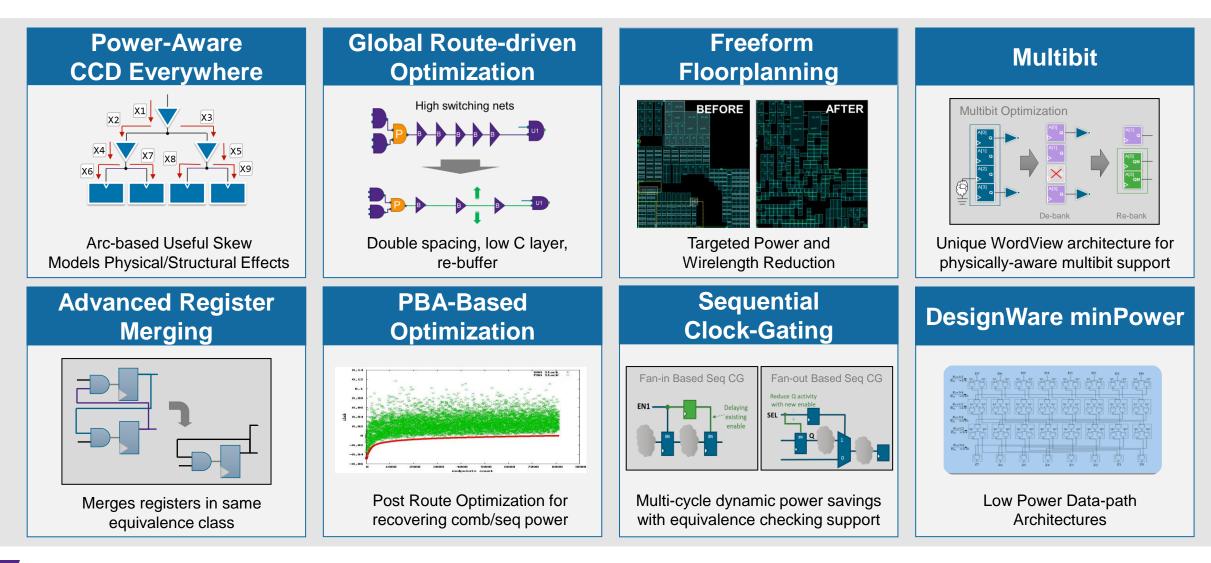

### **UPF** Technologies in Fusion Compiler

**SYNOPSYS**<sup>®</sup>

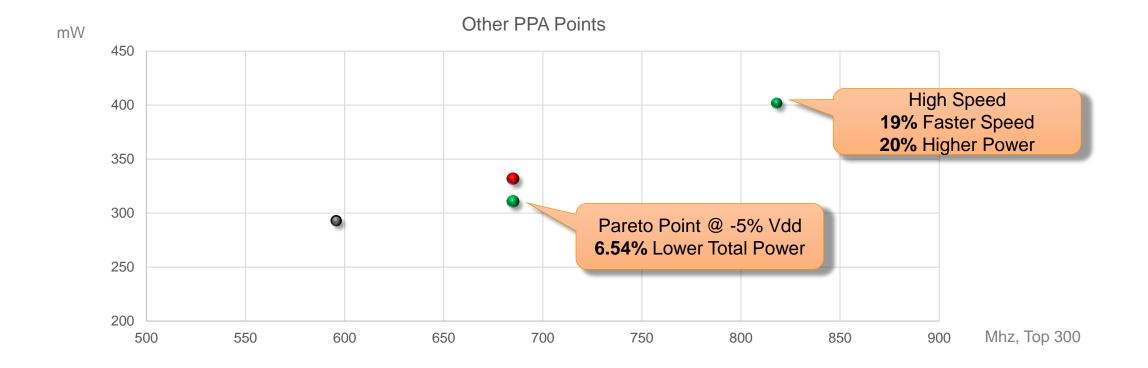

# Finding Optimal Voltage for Timing/Power

Alternative solutions with timing/power tradeoffs, depending on designer goals

## PrimeShield Improves Power on Low-Power Designs

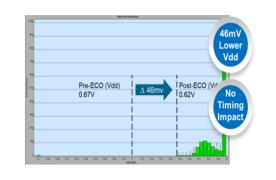

Voltage Slack Analysis (VSA) & Robustness Optimization reduces Vdd to improve power

#### Improved Power & Robustness maintaining performance

#### Silicon Accurate voltage slack predicted with VSA

#### Lower Dynamic Power on PrimeShield optimized AI core

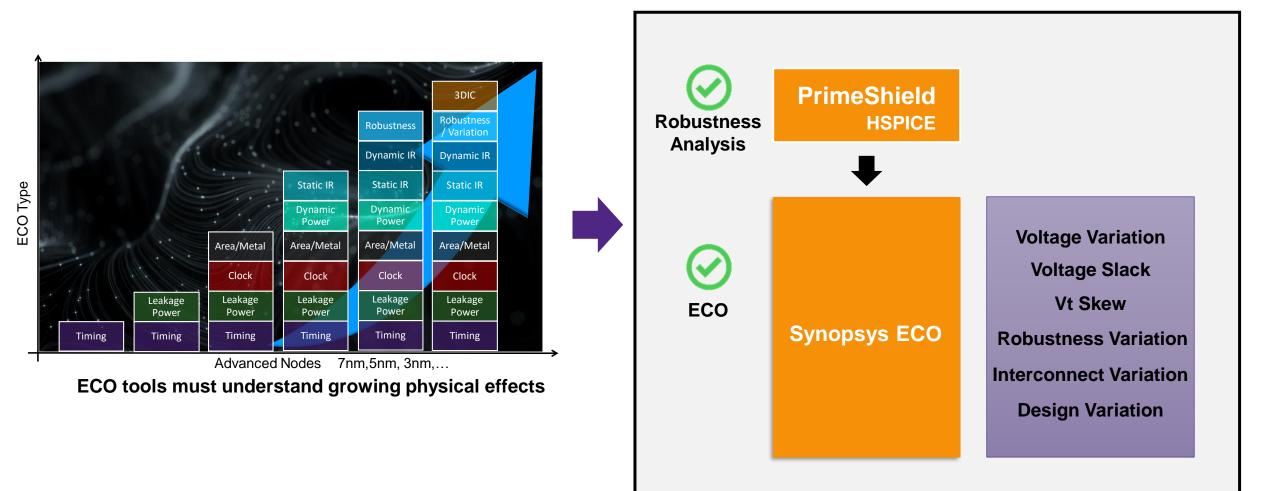

# Power Closure using Synopsys ECO

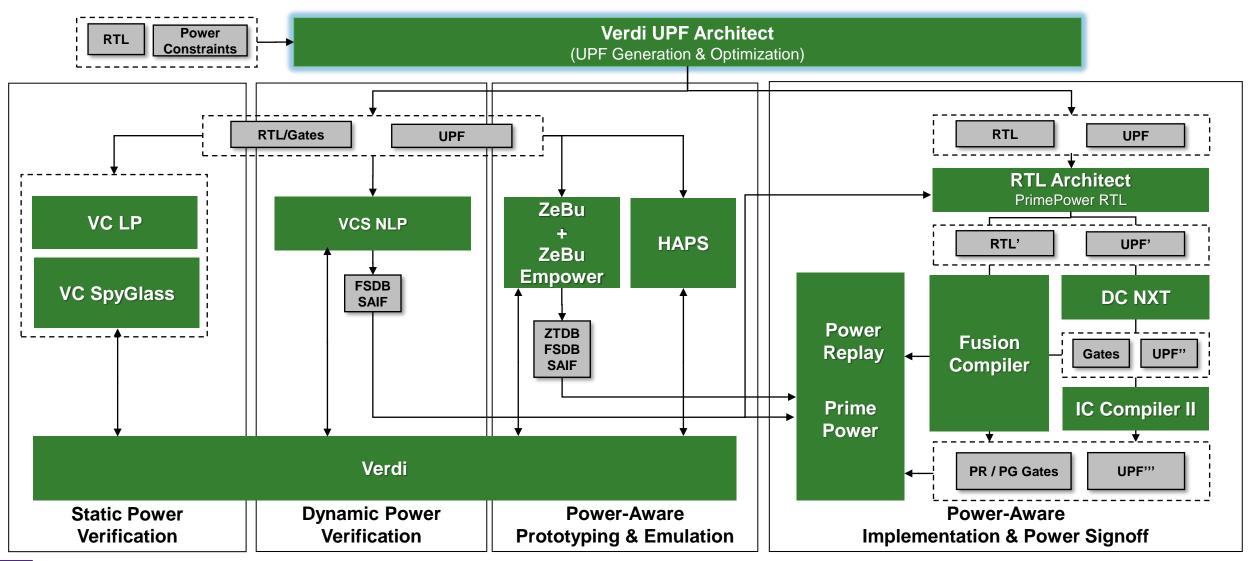

### UPF-Based Power Verification, Implementation & Signoff

#### ′ synopsys°

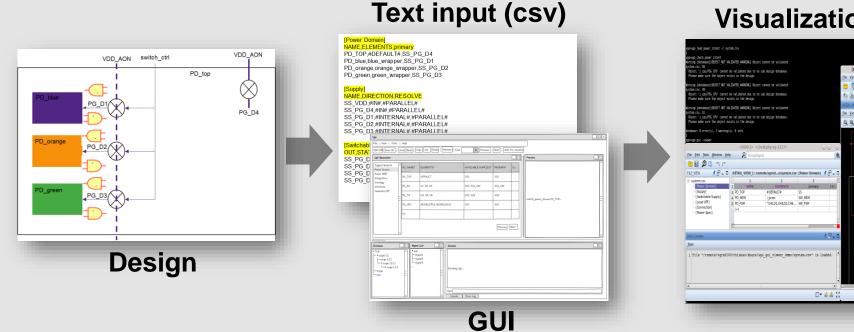

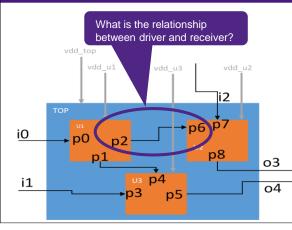

### Verdi UPF Architect for Automated UPF Generation

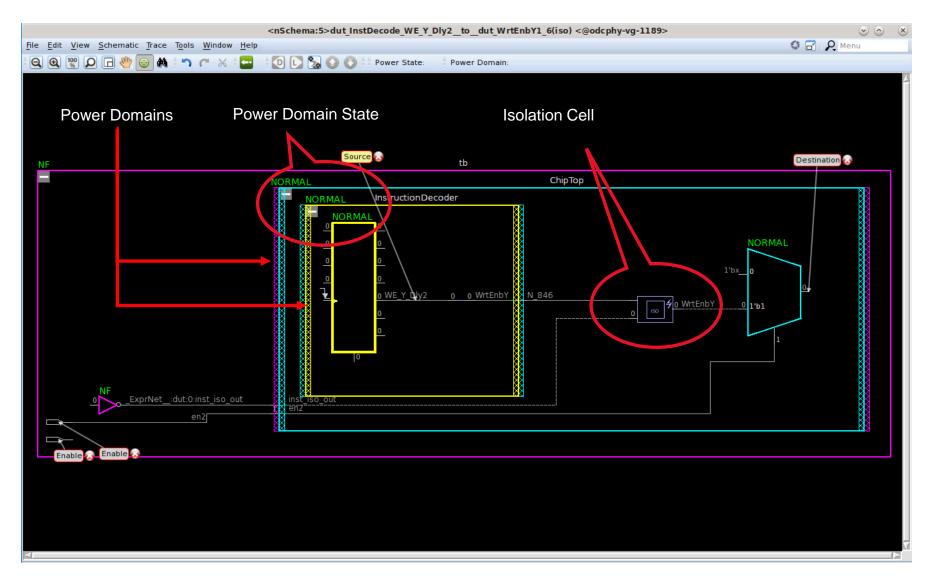

### **Visualization & Debug**

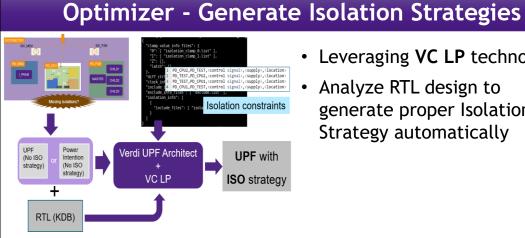

### UPF Generation, Integration and Optimization

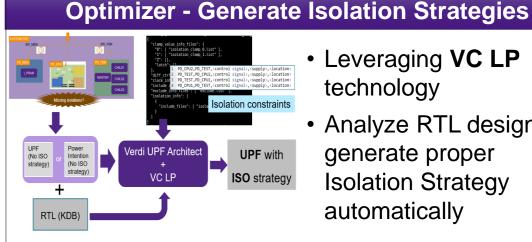

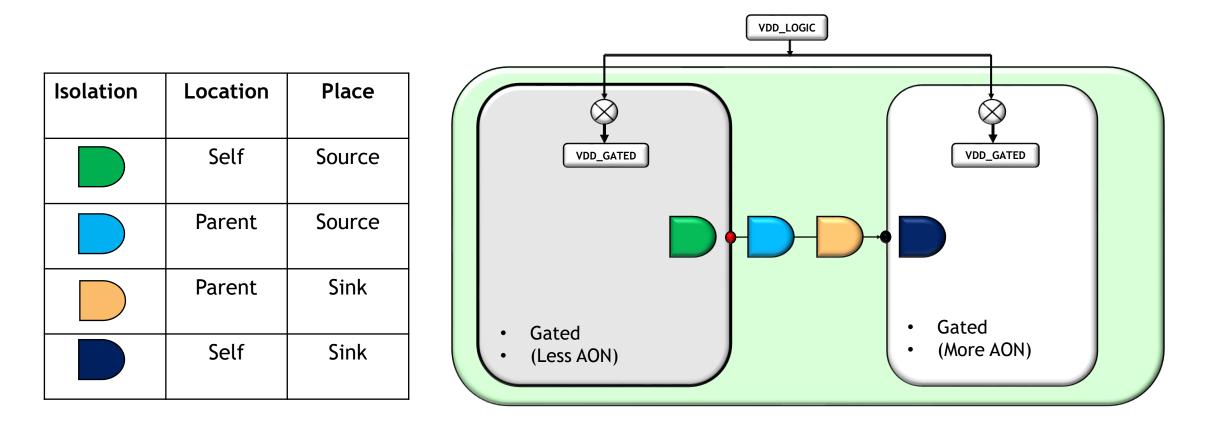

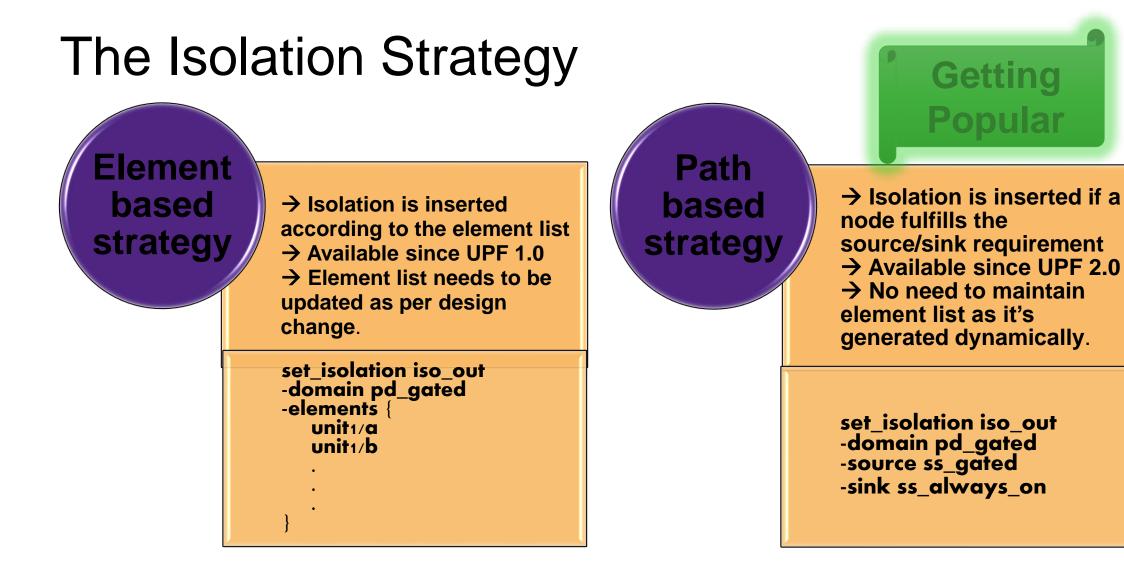

# UPF Optimization using Verdi's UPF Architect

- Leveraging VC LP technology

- Analyze RTL design to generate proper **Isolation Strategy** automatically

### **Optimizer – UPF Budgeting**

- Budgeting sub blocks in top UPF

- Existing UPF for blocks, generate **SPA** (set\_port\_attribute) in top level

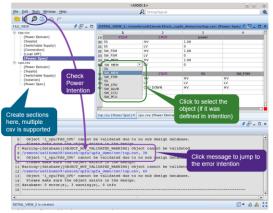

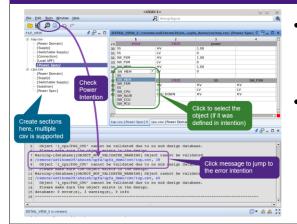

### **GUI - The Power Intent Editor**

### Input intention in xls-like GUI

- Intention is syntax/version free

- Check power intention

- Mismatch objects across the intentions

- Mismatch objects between intention and design

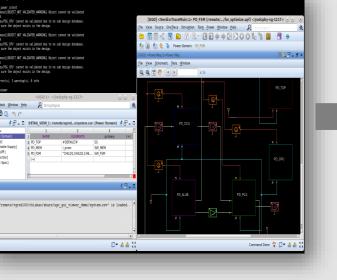

### **GUI - Interactive with Verdi**

- View and debug intentions in Verdi

- Hierarchical Power Domain Tree

- Power Map: Power domains, ISO, level-shifters...

### Synopsys Low Power Solution Summary

#### Synopsys®

Automating and Optimizing UPF generation from Higher Level Power Intent through UPF Architect

Santhana Krishnan Meta

### Introduction

### GOAL: Socially Acceptable and All-Day Wearable

$\succ$  Reality Labs silicon team works in developing Virtual and Augmented reality hardware.

- > Driving state-of-the-art forward.

- >AR devices require extreme computing power.

- $\succ$  Optimize power starting from the transistor through architecture & software.

- > Power Gating is the key technology for silicon power benefits.

### **Problem Statement:**

Translating Power Intent from Architecture spec.

- Capturing Power Intent in a user-friendly format

#### UPF versions

- Maintaining the UPF that works across all EDA tools.

#### Modeling power domain Interfaces

- Associating interfaces with supply attributes based on connectivity & functionality.

#### Analog Macros

- Deriving the PG pin information from the datasheet

#### Power State Table

- Solving complex power states and deriving isolation strategies.

### Motivation:

### Addressing Power Management Challenges: Build or Buy?

- □ Challenges with Building your solution:

- > Maintaining UPF syntax

- > Deriving power control signals

- > Managing analog macro connections

- Handling multiple voltage corner cases

- > Implementing level shifters and retention registers

### □ Buying off the shelf:

- Limited EDA tool options for UPF generation

- □ Partnering with Synopsys for UPF generation:

- Offers Verdi UPF Architect

- > Engagement from early concept to production release.

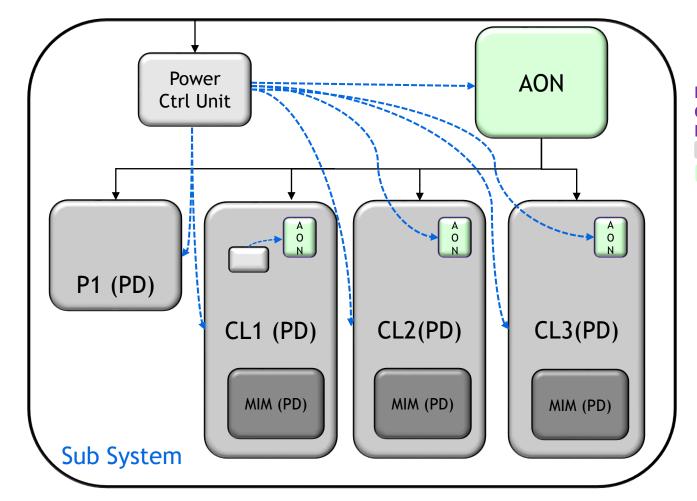

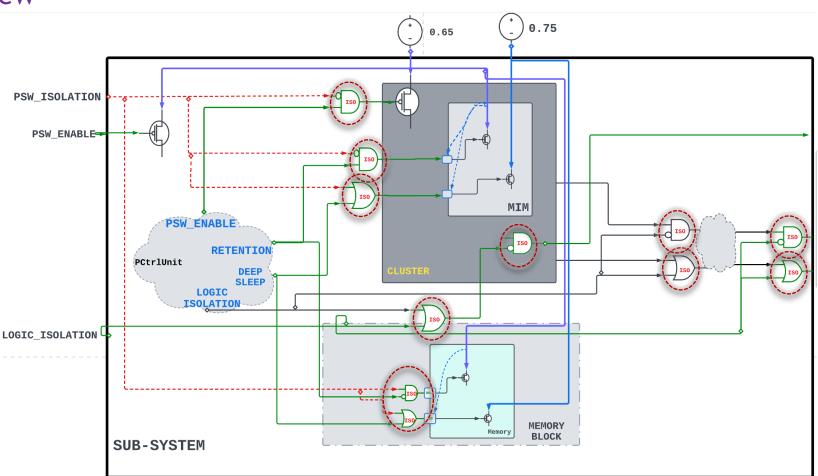

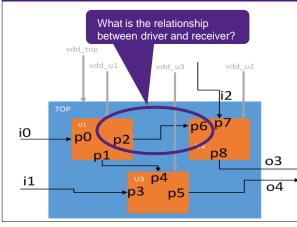

# Design (Sub-System)

### Logical View

- Sub-System with three levels of nested hierarchy

- RTL Module for each power domain

- Gated Power Control Unit of Sub-System

- Gated MIM Partition instantiated in the cluster

- Each power domain can be turned ON/OFF individually

P\* -> Partition CL\* -> Cluster PD -> Power Domain -> Power Gated -> Always On

# Design (Sub-System)

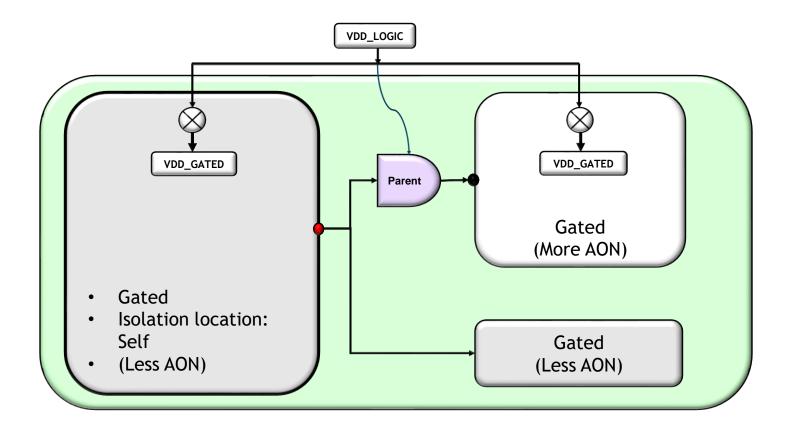

### Physical Power Domain View

- A physical floorplan view of the power domains

- Each power domain represented as a voltage area

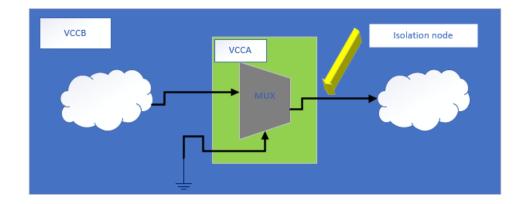

- Power states of the design require Isolation cells at multiple levels

- Gated Power Ctrl Unit demands Isolation on Isolation and power-enable signals.

Numerous Isolations at various levels of hierarchy! How do I solve this strategy ??

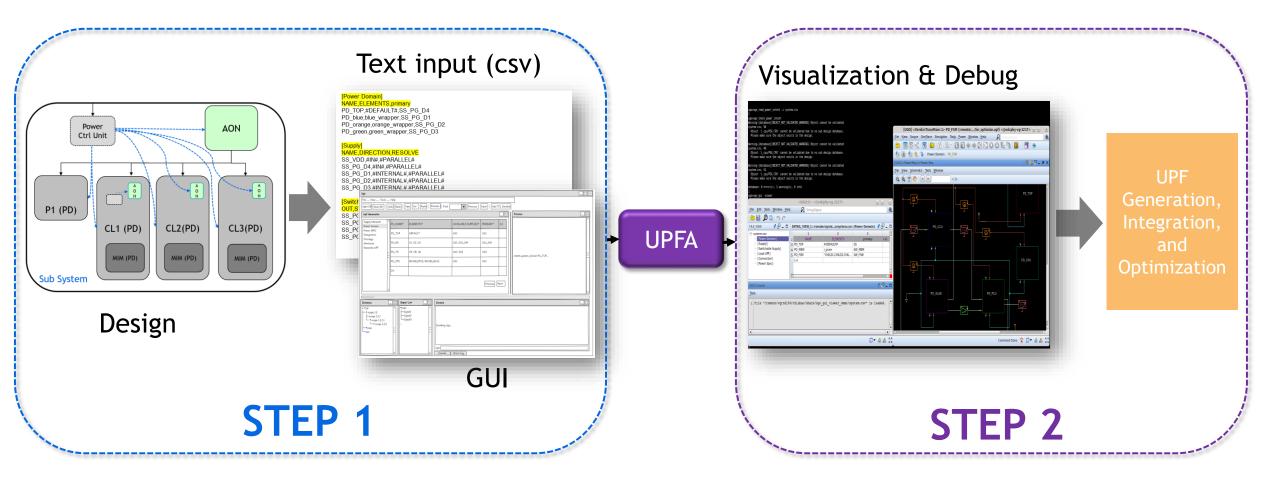

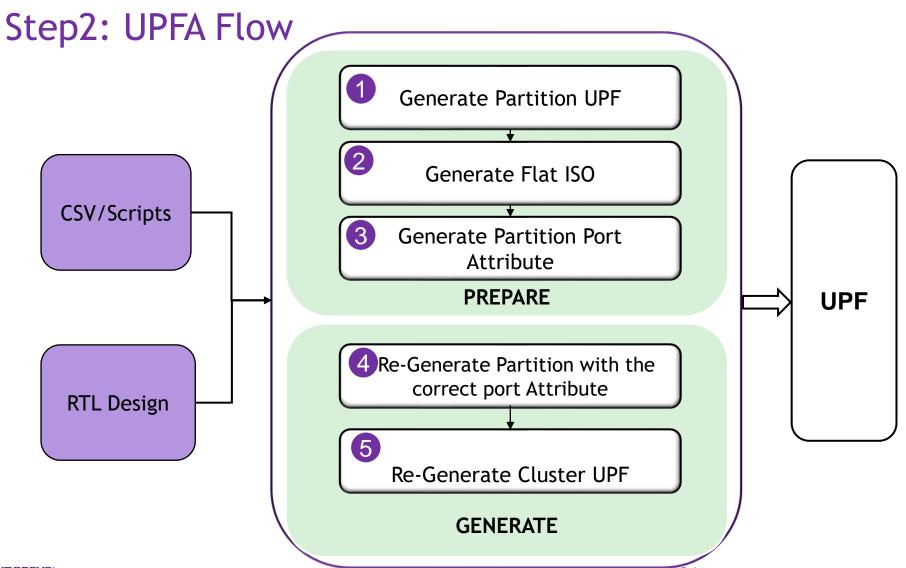

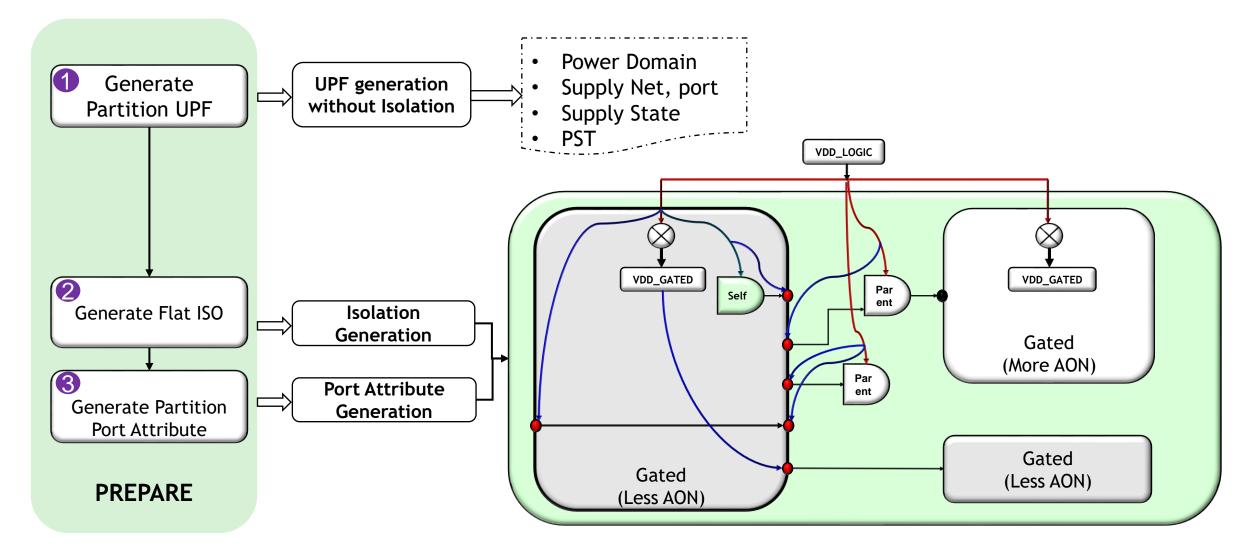

### Verdi UPF Architect flow steps

#### Generates UPF compliant with EDA/SNPS Tools, simplifies UPF integration from block to sub-system to chip

#### **Synopsys**°

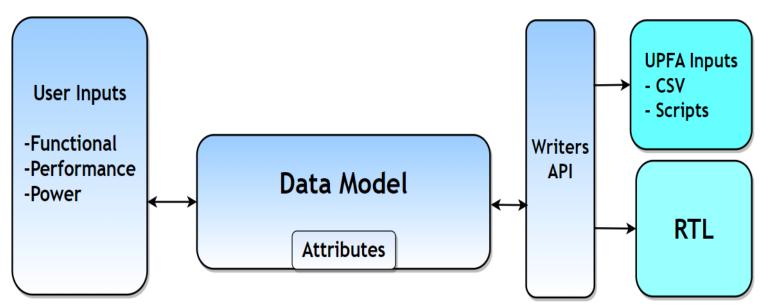

# Meta's collateral generation flow Step 1: Generation

- Instantiates and configures thirdparty and proprietary IP to produce integrated designs

- User inputs include functional, performance, and power attributes

- Generates RTL + associated collateral for verification, FW & physical design.

Input files for UPFA (CSV's)

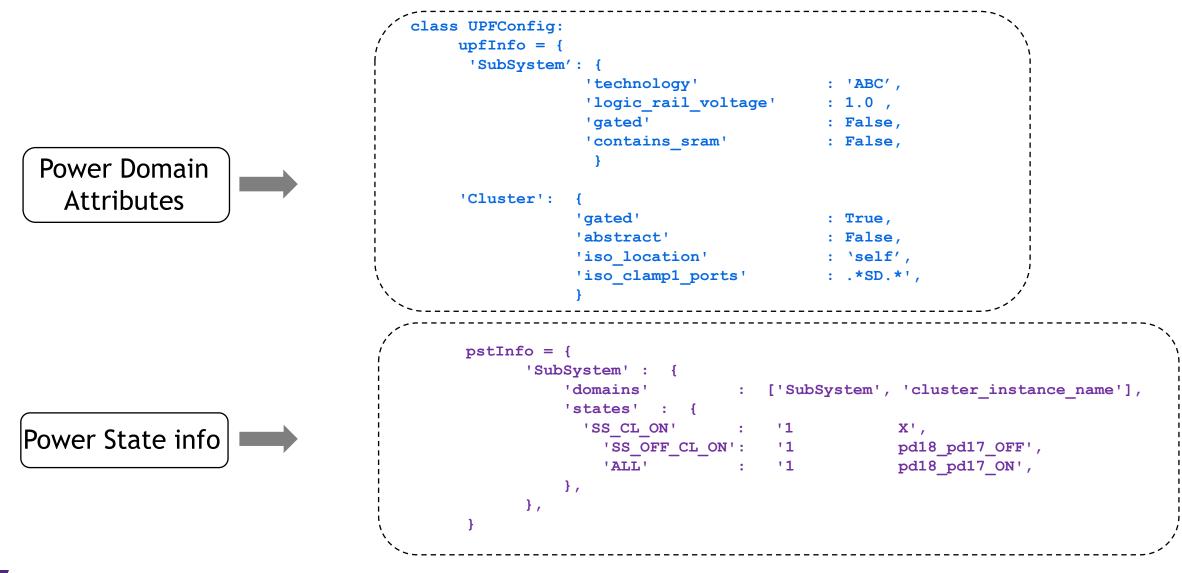

### Input to the Generator: Python Dictionary

# Output of the Generator: CSV format

### Auto Derive

- Control signals

- Supply set

- Power Switch Model

- Isolation cell type based on location

- Supply sets

### Translate

- PST

- Clamp Ports

- Location

- Technology

| [Supply]             |              |            |            |              |              |           |          |        |

|----------------------|--------------|------------|------------|--------------|--------------|-----------|----------|--------|

| NAME                 | RESOLVE      | power      | ground     | nwell        | pwell        |           |          |        |

| SS_LOGIC             | #UNRESOLVED# | VDD_TURING | VSS        | VDD_TURING   | VSS          |           |          |        |

|                      |              |            |            |              |              |           |          |        |

| [Power Domain]       |              |            |            |              |              |           |          |        |

| NAME                 | primary      | ELEMENTS   |            |              |              |           |          |        |

| PD_partition         | SS_GATED     | #DEFAULT#  |            |              |              |           |          |        |

|                      |              |            |            |              |              |           |          |        |

| [ISOGEN Config]      |              |            |            |              |              |           |          |        |

| SRC_PD               | SINK_PD      | ISO_SIGNAL | ISO_SUPPLY | ISO_LOCATION | ISO_SENSE    | ISO_CLAMP | ISO_CELL | PORTS  |

| PD_partition         | *            | iso_logic  | SS_LOGIC   | #SELF#       | #HIGH#       | 1         | XYZ      | Signal |

|                      |              |            |            |              |              |           |          |        |

| [Power Spec]         |              |            |            |              |              |           |          |        |

| #SS#                 | STATE        | power      | ground     | nwell        | pwell        | SIMSTATE  |          |        |

| SS_LOGIC             | ON           | 0.65       | 0          | 0.65         | 0            | NORMAL    |          |        |

|                      |              |            |            |              |              |           |          |        |

| [Power Spec]         |              |            |            |              |              |           |          |        |

| #PSG#                | STATE        | SS_LOGIC   | SSH_SRAM   | SS_GATED     | SS_PERIPHERY | SS_CORE   |          |        |

| PST_PD_partition     | S1           | ON         | ON         | ON           | ON           | ON        |          |        |

|                      |              |            |            |              |              |           |          |        |

| [Supply Port Intent] |              |            |            |              |              |           |          |        |

| NAME                 | DIRECTION    | NET        |            |              |              |           |          |        |

| VDD_TURING           | #IN#         | VDD_TURING |            |              |              |           |          |        |

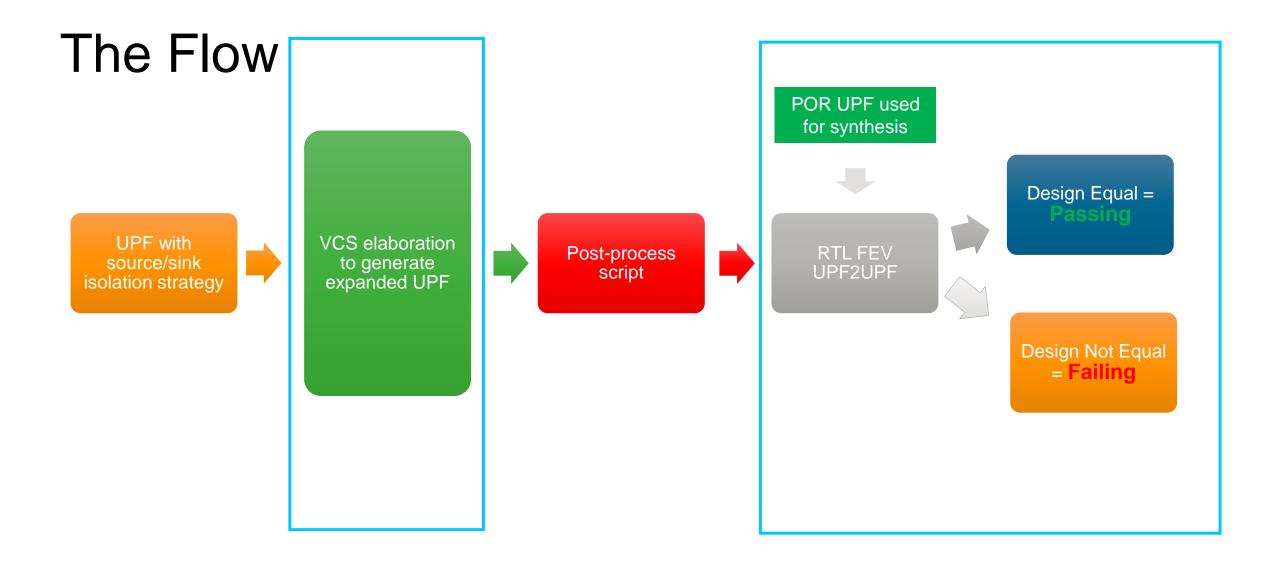

# Integrating UPFA into Meta's Flow

## **PREPARE: Steps to derive Port Attributes**

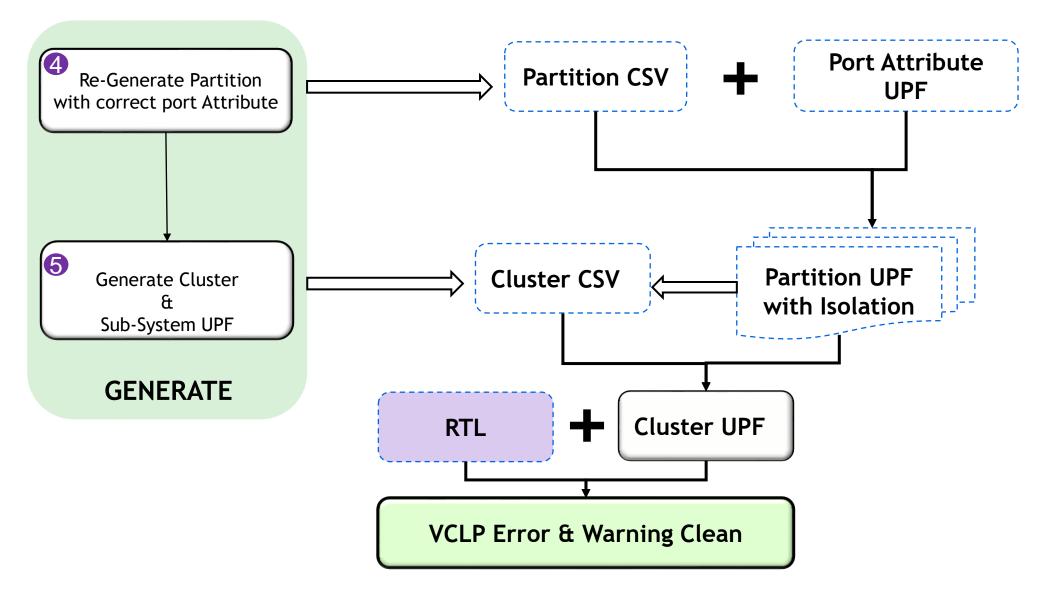

# **GENERATE:** Final UPF generation

## **UPFA features:** Derive Macro UPF

> Auto generates UPFs for Analog macro instantiated in the design (from .lib)

- > Variable to enable Macro CSV generation

- ugo\_dump\_macro\_pg\_pin\_report -csv macro.csv -a

| [Connection]         |                      |              |                |              |            |          |

|----------------------|----------------------|--------------|----------------|--------------|------------|----------|

| -<br>HIGH_CONN       | SCOPE                | LOW_CONN     |                |              |            |          |

| SS_ANA_AVDD12.powe   | er instance_name/ANA | AVDD12       |                |              |            |          |

| SS_ANA_DVDD.power    | instance_name/ANA    | DVDD         |                |              |            |          |

| [Supply]             |                      |              |                |              |            |          |

| NAME                 | DIRECTION            | power        | ground         | nwell        | pwell      |          |

| SS_ANA_AVDD12        | #IN#                 | ANA_AVDD12   |                | ANA_AVDD12   |            |          |

| SS_ANA_DVDD          | #IN#                 | ANA_DVDD     |                | ANA_DVDD     |            |          |

| [Power Spec]         |                      |              |                |              |            |          |

| #SS#                 | STATE                | power        | ground         | nwell        | pwell      | SIMSTATE |

| SS_ANA_AVDD12        | ON                   | 1.2          | 0              | 1.2          | 0          | NORMAL   |

| SS_ANA_DVDD          | ON                   | 0.75         | 0              | 0.75         | 0          | NORMAL   |

| #PSG#                | STATE                | SS_ANA_AVDD1 | 2 SS_ANA_AVDD1 | 5 SS_ANA_DVD | D SS_ANA_D | VDD      |

| PST_MACRO_TOP        | MACRO_ALL_ON         | ON           | ON             | ON           | ON         |          |

| [Supply Port Intent] |                      |              |                |              |            |          |

| NAME                 | DIRECTION            | NET          |                |              |            |          |

| ANA_AVDD12           | #IN#                 | ANA_AVDD12   |                |              |            |          |

| ANA_DVDD             | #IN#                 | ANA_DVDD     |                |              |            |          |

| ANA_DVSS             | #IN#                 | ANA_DVSS     |                |              |            |          |

ססעס

(0.0V)

(0.0V)

**AVDD 12**

$\Delta VDD 15$

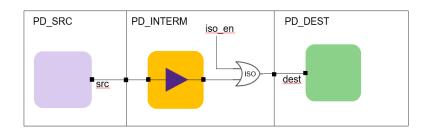

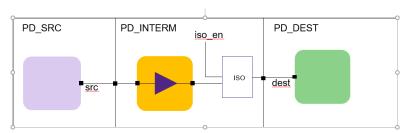

# **UPFA features: Hetero Fanout**

- Hetero fanout: Gated power domain driving multiple sink power domain

- UPFA Optimizer smartly identifies the case of hetero fanout nets, which may lead to additional redundant isolations

- Solves it by adding on the destination domain's input (Though self-style isolation was specified)

# **UPFA features:** Flexible ISO locations

# Summary of UPF Architect Features

### Leveraging VC LP technology

Analyze RTL design to generate proper Isolation Strategy automatically

### **Optimizer - UPF Budgeting**

- Budgeting sub blocks from top UPF

- Existing UPF for blocks, generate SPA (set\_port\_attribute) in top level

### **GUI** - The Power Intent Editor

- Input intention in xls-like GUI

- Intention is syntax/version free

- Check power intention

- Mismatch objects across the intentions

- Mismatch objects between intention and design

### **GUI - Interactive with Verdi**

- View and debug intentions in Verdi

- Hierarchical Power Domain Tree

- Power Map: Power domains, ISO, levelshifters...

## **UPFA** Next steps

>Auto generate level shifter strategy commands based on supply connections

Add support for Full chip integration

- Black Box models

- ➢ IO PADs connection

≻Reduce hierarchical runtime by the recursive reading of CSV's without the need for intermediate UPFs.

>Enhance Error and Warning reporting.

> Support to read 3<sup>rd</sup> party UPFs and auto-resolve the strategies at the SS level.

$\triangleright$ A more simplistic interface rather than a CSV

# Summary

- Generate Analog Macro UPFs. Impact:

- Reduced manual update for every release of RTL

- 90% reduction in turnaround time for structurally clean UPF generation Impact:

- Automate hierarchical UPF generation as part of the regression

- Single source of truth Impact:

- Seamless usage of UPF across all EDA tools.

• Modeling port attributes for dynamically changing interface

Impact:

Reduced manual update for every release of RTL

# Streamlining Low-Power Verification: From UPF to Sign Off

Neeraj Mishra(Google)

Nishant Patel(Synopsys)

Bhaumik Matholia (Synopsys)

Confidential + Proprietary

## Agenda

**Predictive VC LP Vefn**

- Introduction

- Instrumentation Checks

- Common Issue Resolved

- Benefits & Results

- Future Work

**Hierarchical VC LP Vefn**

- Why Hier Lp Vefn

- Various Hier VC LP Flows

- SAM Model based Flow

- Qor Analysis

- Benefits & Results

### ML Aided VC LP Vefn

- ML-RCA Overview

- Results

- Conclusion Future Work

## Agenda

**Predictive VC LP Vefn**

### **Hierarchical VC LP Vefn**

### ML Aided VC LP Vefn

- Introduction

- Instrumentation Checks

- Common Issue Resolved

- Benefits & Results

- Future Work

Why Hier Lp Vefn Various Hier VC LP Flows SAM Model based Flow Qor Analysis Benefits & Results ML-RCA Overview Results Conclusion Future Work

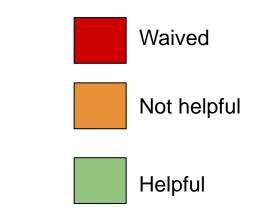

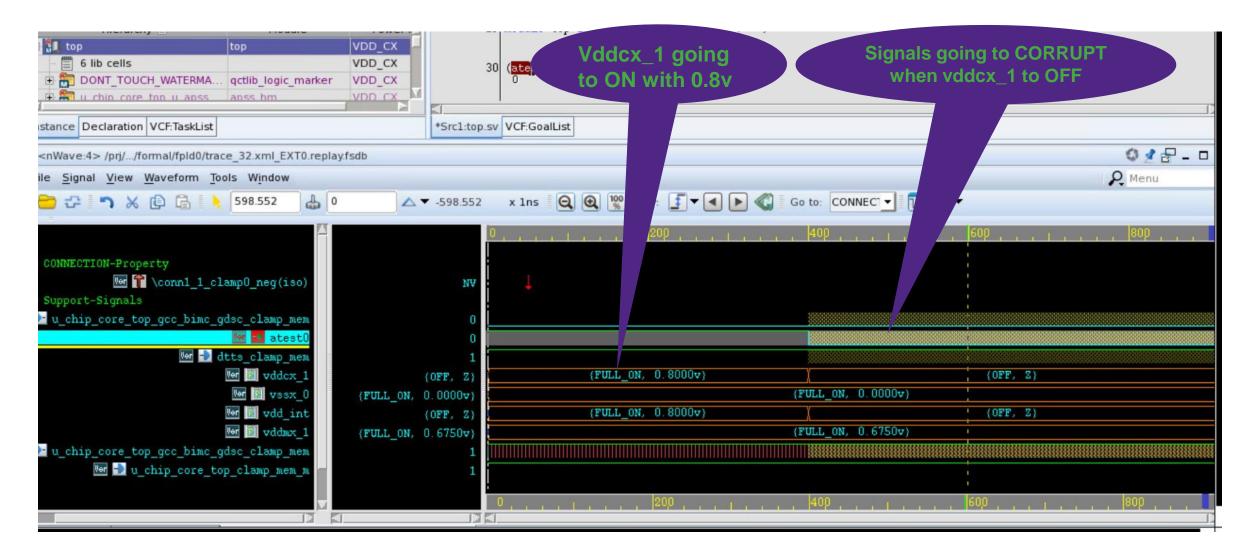

# **Predictive VC LP Vefn**

- Problem Statement -

- Seeing Inaccurate/Inconsistent violations in Rtl Vclp vs Syn Vclp

- At RTL stage, VC LP checks do not consider isolation/level-shifter/retention/power-switch cells on the paths where strategies are getting applied

- post-synthesis electrical or functional issues are introduced due to inserted MV cells

- Difficulty in finding real violations

- LP violations identified later in netlist stage has significant cost

- Very costly to push Rtl fix at late stage

- Might require upf update and re-synthesis

- Impacts overall convergence time.

- Shift Left needed for all Lp checks

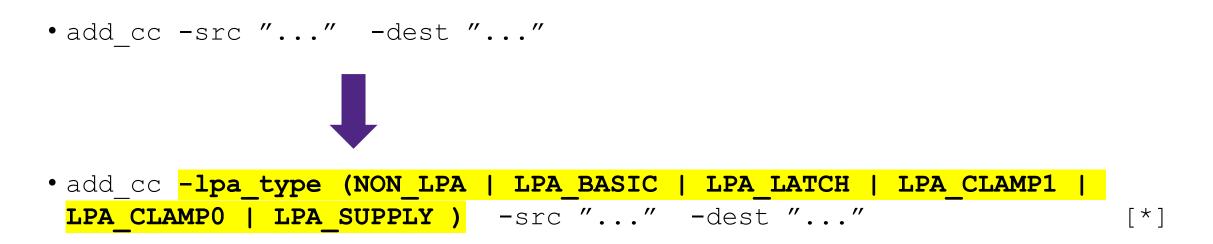

- Solution New Instrumentation Checks feature of Vclp

- Tool inserts and predicts the position of LP cells in netlist based on provided Rtl

- Runs Vclp check based on these virtual isolation/LS cells

- Close collaboration with Snps led to almost 80% reduction in noisy violations for Rtl Level Full flat Soc Run

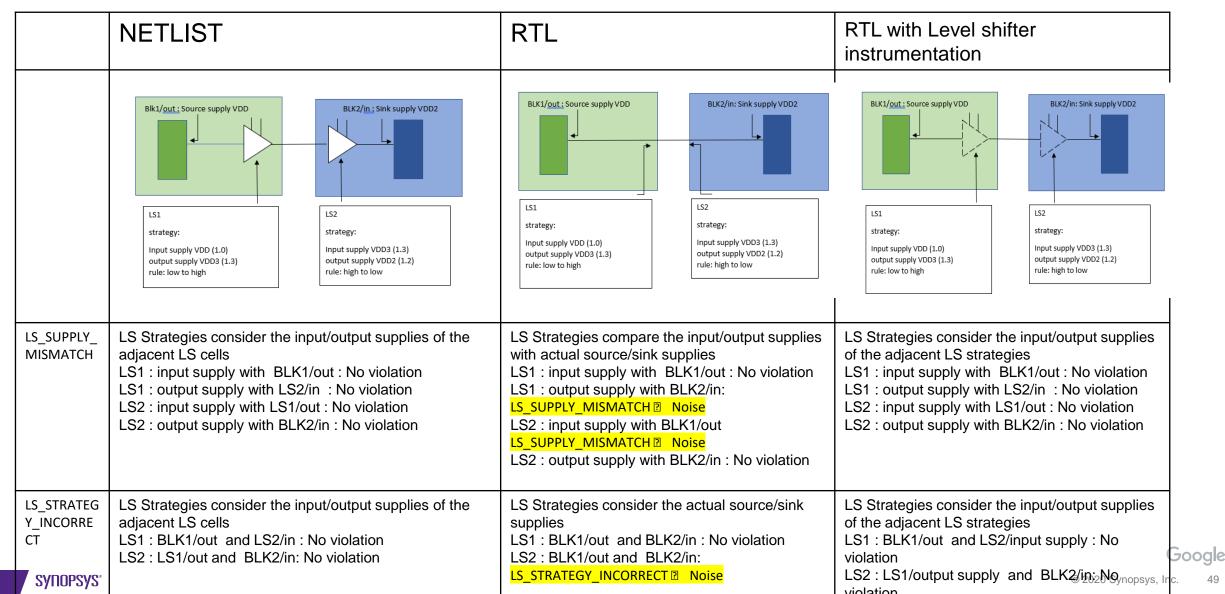

## **Common Issues Fixed** (The LS checks are considered as noise violations and are ignored at netlist and predictive stage)

LS\_SUPPLY\_MISMATCH/LS\_STRATEGY\_INCORRECT/LS\_SUPPLY\_UNAVAIL

# **Benefits & Results**

- Collaborative Work with Synopsys to evaluate this feature began 2 years ago

- Tested over 3 generations of a Mobile Soc with increasing benefit and noise reduction

### 2020 build was giving 65% reduction in false violations (Soc-1) 2022 build gave upto 75% reduction in false (Soc-1.1)

| Stage | - Tag -                 | 2020.12 - Orig 🔹 | 2020.12 with Instrumenation 👻 | Stage - | Tag -                      | 2020.12 - Orig 👻 | 2022.06 with Instrumenation - |

|-------|-------------------------|------------------|-------------------------------|---------|----------------------------|------------------|-------------------------------|

| UPF   | ISO_STRATEGY_MISSING    | 156              | 156                           | UPF     | ISO_DATA_RESET             |                  | 1383                          |

| UPF   | ISO_STRATMISSING_NOBOU  | 2                | 2                             | UPF     | ISO_MACRO_CLAMP            |                  | 1                             |

| UPF   | LS_STRATEGY_HETERO      | 6                | 6                             | UPF     | ISO_STRATEGY_MISSING       | 27131            | 167                           |

| UPF   | LS_STRATEGY_INCORRECT   | 50135            | 24956                         | UPF     | ISO_STRATEGY_NOISO,        | 21               | 2                             |

| UPF   | LS_STRATEGY_MISSING     | 248              | 255                           | UPF     | LS_STRATEGY_MISSING        | 37585            | 21026                         |

| UPF   | LS_STRATMISSING_NOBOUM  | 1                | 1                             | UPF     | LS_STRATEGY_NOSHIFT        | 57               | 155                           |

| UPF   | LS_SUPPLY_MISMATCH      | 28818            | 3853                          | UPF     | LS_STRATMISSING_NOBOUNDARY | 9                | 19                            |

| UPF   | LS_SUPPLY_UNAVAIL       | 25023            | 171                           | UPF     | LS_SUPPLY_MISMATCH         | 270666           | 6024                          |

| UPF   | PSW_ACK_FANOUT          | 8                | 8                             | UPF     | LS_SUPPLY_STATE            |                  | 12                            |

| UPF   | UPF_BUFINV_ORDER        | 1                | 1                             | UPF     | UPF_BUFINV_ORDER           | 1                | 1                             |

| UPF   | UPF_OBJECT_UNDEF        | 5                | 5                             | UPF     | UPF_CSN_UNAVAIL            | 567              | 567                           |

| UPF   | ISO_CONTROL_VOLTDIFF    | 9                | 0                             | UPF     | UPF_MACRO_NOSTATE          | 15408            | 15408                         |

| UPF   | ISO_LOCATION_IMPOSSIBLE | 1                | 0                             | UPF     | ISO_ASSOC_DIFFER           | 2485             | 10478                         |

| UPF   | ISO_STRATCLAMP_MISMAT   | 18               | 18                            | UPF     | ISO_CONTROL_VOLTDIFF       | 109              | 59                            |

| UPF   | ISO_STRATCONTROL_GLITCH | 8                | 8                             | UPF     | ISO_LOCATION_IMPOSSIBLE    | 2241             |                               |

| UPF   | ISO_STRATEGY_MULTIPLE   | 2287             | 0                             | UPF     | ISO_STRATEGY_CONFLICT      |                  | 3                             |

| UPF   | ISO_STRATEGY_REDUND     | 7                | 7                             | UPF     | ISO_STRATEGY_MULTIPLE,     | 12               | 36                            |

| UPF   | LS_STRATEGY_MULTIPLE    | 21936            | 21930                         | UPF     | ISO_STRATEGY_REDUND,       | 2520             | 2908                          |

| UPF   | LS_STRATEGY_REDUND      | 7207             | 1775                          | UPF     | LS_ASSOC_DIFFER            |                  | 17312                         |

| UPF   | PST_BIASON_STATE        | 23               | 23                            | UPF     | LS_STRATEGY_FORCE          | 460              | 464                           |

| UPF   | PSW_CONTROL_GLITCH      | 38               | 38                            | UPF     | LS_STRATEGY_MULTIPLE       | 9590             | 39                            |

| UPF   | UPF_ATTR_INVALID        | 6                | 6                             | UPF     | LS_STRATEGY_REDUND         | 9136             | 6788                          |

| UPF   | UPF_SPARECEIVER_STATE   | 47908            | 7421                          | UPF     | UPF_SPADRIVER_STATE        | 42395            | 12138                         |

| UPF   | UPF_SPASUPPLY_VOLTAGE   | 1131             | 267                           | UPF     | UPF_SPARECEIVER_STATE      | 142996           | 27694                         |

|       |                         |                  |                               | UPF     | UPF_SPASUPPLY_VOLTAGE      | 51906            | 15075                         |

| Total |                         | 184982           | 60907                         | Total   |                            | 654908           | 175486                        |

|       |                         |                  | 05.000                        |         |                            |                  |                               |

Google

50

# **Future Work**

- Continuous improvement for better correlation w.r.t Synthesis runs (Soc-1.2)

- Dec'23 rel-Vclp 22.07 build giving ~80% reduction compared to 2020 build

| TAGS -                | 22.06-SP2-6 - | 22.06-SP2-6-B4 - | 22.07-SP2-7 Nov-Pre 👻 | CHANGE - | PERCENTAGE - |

|-----------------------|---------------|------------------|-----------------------|----------|--------------|

| ISO_STRATEGY_MISSING  |               | 601              | 593                   | -8       | -0.013311148 |

| LS_STRATEGY_MISSING   | 23032         | 21565            | 2795                  | -18770   | -81.50%      |

| LS_SUPPLY_MISMATCH    | 48535         | 16067            | 12932                 | -3135    | -6.46%       |

| ISO_CONTROL_VOLTDIFF  | 109           | 59               | 52                    | -7       | -6.42%       |

| UPF_SPADRIVER_STATE   | 12135         | 12069            | 644                   | -11425   | -94.15%      |

| UPF_SPARECEIVER_STATE | 28301         | 27676            | 27676                 | 0        | 0.00%        |

| UPF_SPASUPPLY_VOLTAGE | 20980         | 14094            | 9215                  | -4879    | -23.26%      |

| LS_ASSOC_DIFFER       | 18280         | 17441            | 17487                 | 46       | 0.25%        |

| LS_STRATEGY_REDUND    | 13206         | 3582             | 4289                  | 707      | 5.35%        |

|                       | 164578        | 112553           | 75090                 | -37463   | -22.76%      |

- Major update in VC LP 2023.12 Design based instrumentation

- No need to modify vclp internal db limiting scope miscorelation

# Agenda

### Hierarchical VC LP Vefn

- Why Hier LP Vefn

- Various Hier VC LP Flows

- SAM Model based Flow

- Qor Analysis

- Benefits & Results

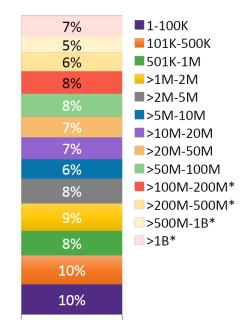

# Why Hierarchical VC LP Flow?

### • Increasing design sizes

- Considerable number of designs are > 100M

- LP Signoff in Flat SoC takes a long time

- For our designs more than 140 hours

- Next generation SoCs are expected to be even larger and cannot rely on full-flat run

- Integration of large number of IPs with standalone UPF files validated at block level

- Existing hierarchical flows do not cover all aspects of Signoff

Engineers need a methodology to handle next generation chip signoff with considerably better performance and capacity, and **NO** loss in QoR or signoff confidence.

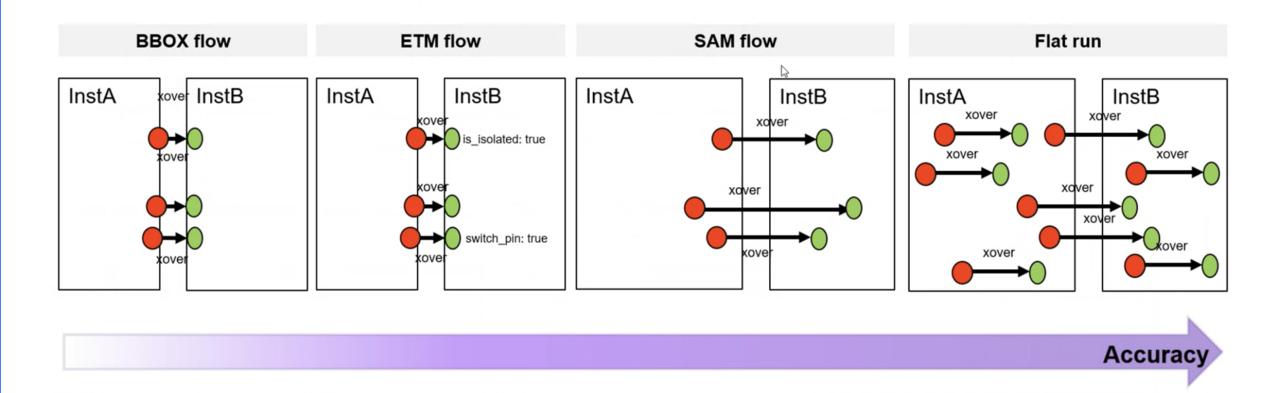

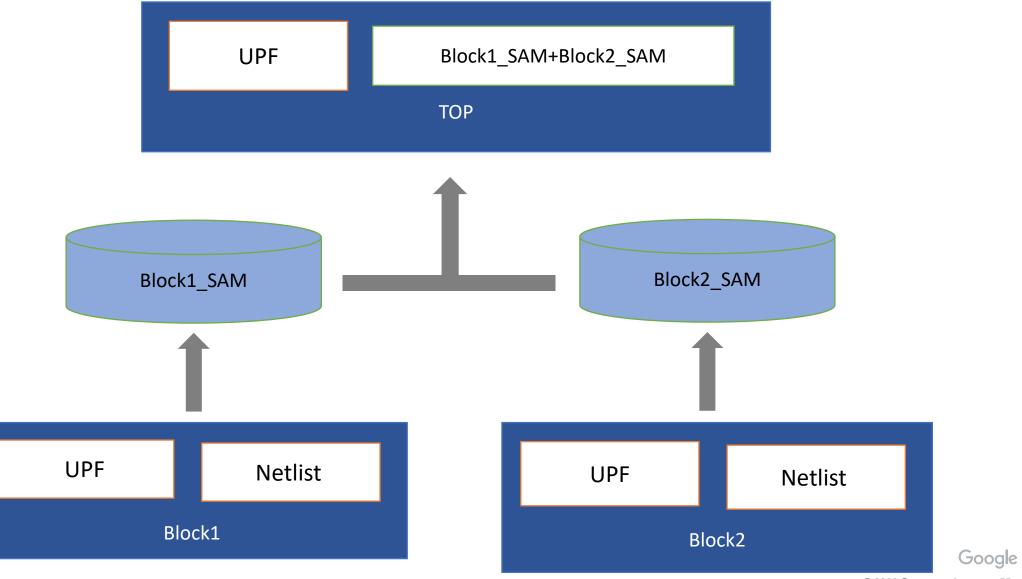

# **BBOX/ETM/SAM/FLAT VC LP Flows**

**Synopsys**®

## **SAM Model based Flow**

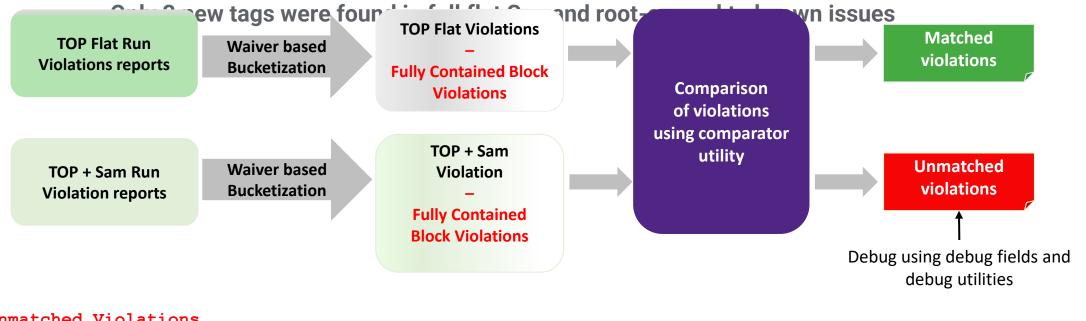

## **Qor Analysis - Subtractive QoR Flow**

**Ran Full Flat Vclp run for Entire Soc - Compared against SAM** model based VCLP

#### Unmatched Violations

| UPF    | UPF_OBJECT_UNDEF        | 275 |

|--------|-------------------------|-----|

| Design | ANALOG_NET_INCORRECT    | 18  |

| UPF    | ISO STRATCONTROL GLITCH | 37  |

~ ok. UPF reference IP internal ports, not present in SAM run 0  $\leftarrow$  ok. Not real violation and flagged by other waived checks. 106 ← warning on iso ctrl signal thru dft mux-wouldn't find in SAM 153

Gooale

## **Benefits & Results**

- Large Improvement in Runtime and memory making daily batch run feasible

- No Impact on QOR

| Design | Runtime<br>Flat | Runtime<br>Top+SAM |     | Peak Memory<br>Flat (MB) | Peak Memory<br>Top+SAM (MB) | Mem Gain |

|--------|-----------------|--------------------|-----|--------------------------|-----------------------------|----------|

| SOC 1  | 148 hours       | 13 hours           | 11x | 840540                   | 152624                      | 5.5x     |

### Agenda

### ML Aided VC LP Vefn

- ML-RCA Overview

- Evaluation Results

- Conclusion & Future Work

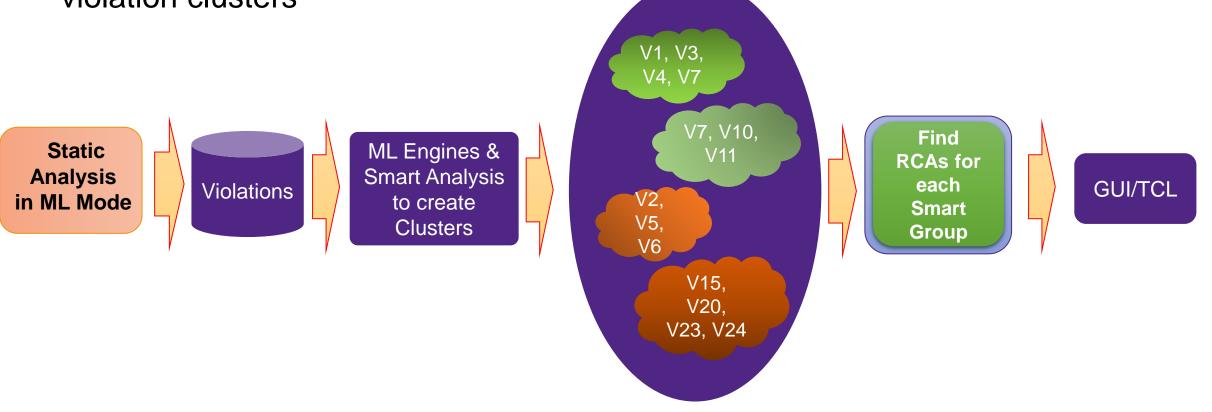

# **ML RCA Overview**

- Uses ML to cluster violations in different categories

- Performs Root Cause analysis to identify reasons for violation clusters

## **Results - IP TOP, Pre-Waiver**

- Stage: Post Synthesis

- Initial violation count: 264139

- Errors: **7667**

- Pre RCA categories: 14

- Warnings: 255681

- Pre RCA categories: **32**

- Post RCA Clustering:

- Clusters: 21

- Coverage: **4.23%**

# **Analysis of Clusters**

• Was able to identify the most obvious violations:

| Rootcause              | Clusters | Total Coverage (%) |

|------------------------|----------|--------------------|

| DEBUG_SETUP_CO<br>NST  | 7        | 1.45               |

| UPF_SPASUPPLY_C<br>ONN | 7        | 0.32               |

| DEBUG_PST_STATE        | 4        | 2.1                |

| DEBUG_ISO_OPTIO<br>N   | 3        | 0.4                |

## **Results - IP Top, Post-Waiver**

- Stage: Post Synthesis

- Initial violation count: **1156**

- Errors: **227**

- Pre RCA categories: 6

- Warnings: **314**

- Pre RCA categories: 6

- Post RCA Clustering:

- Clusters: 6

- Coverage: **43.48%**

# **Analysis of Clusters**

- Helpful in identifying rootcauses of some categories:

- Generic problems identified for majority  $\rightarrow$  no specific cause

| Root Cause            | Clusters | Total Coverage (%) |

|-----------------------|----------|--------------------|

| DEBUG_ISO_MISSI<br>NG | 2        | 4.55               |

| DEBUG_ISO_REDU<br>ND  | 2        | 5.93               |

| DEBUG_ISO_SETUP       | 1        | 31.62              |

| DEBUG_PST_STATE       | 1        | 1.38               |

# Conclusion

- ML cluster friendly design → Many violations with fewer root causes instead of Few violations with multiple root causes instead of

- Coverage improvement with Waivers using ML RCA = 43.48%

- Not particularly helpful for dirty designs. Best used after initial analysis and waiver of Noisy Violations.

# **Thanks & Questions**

# VC SpyGlass CDC – UPF Aware CDC Power-aware CDC

Synopsys Product Team Sept 2022

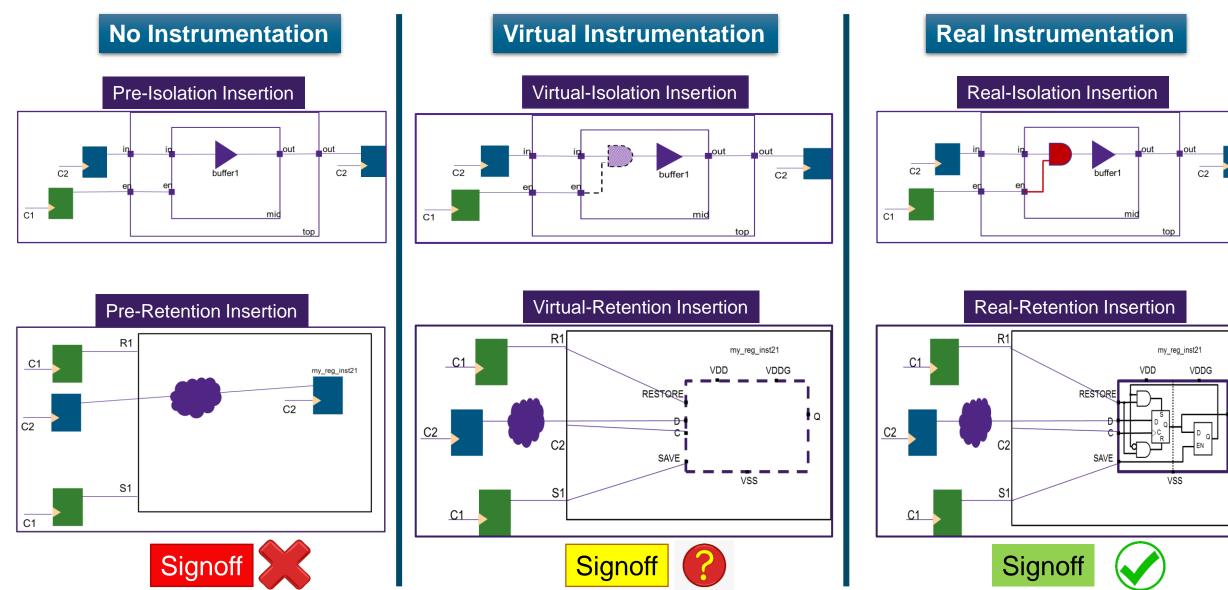

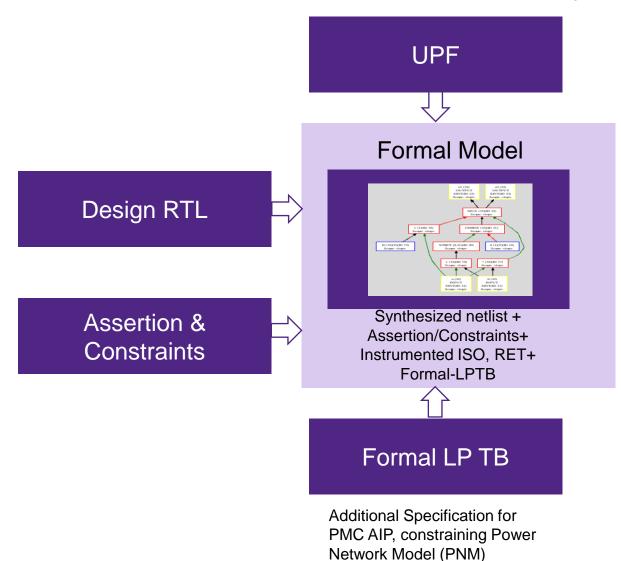

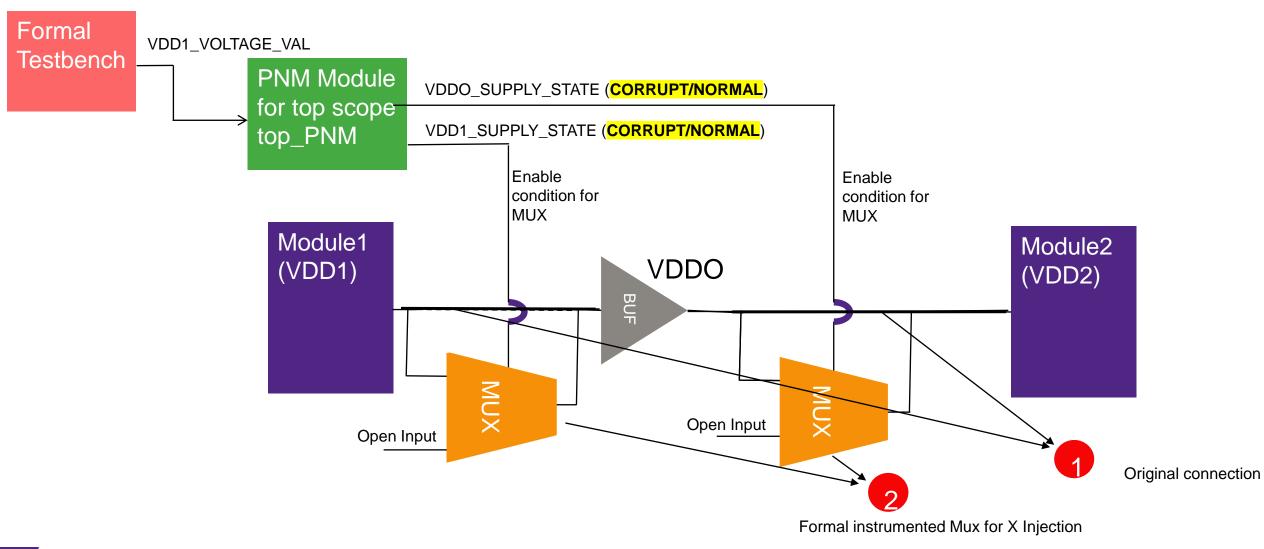

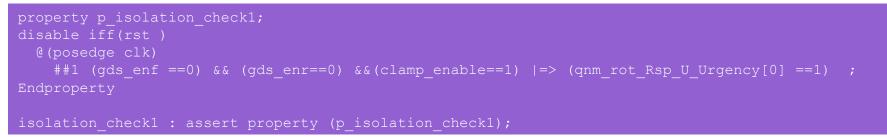

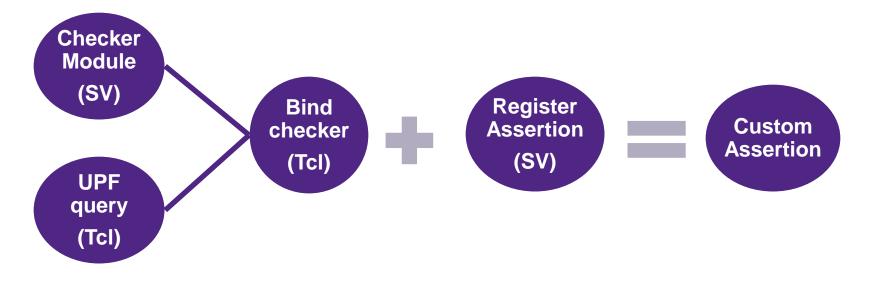

# **UPF** Aware Instrumentation

**Synopsys**°

## **Power-aware Static Verification**

Leverage industry-proven VC LP engines to detect Static bugs due to UPF instrumentation

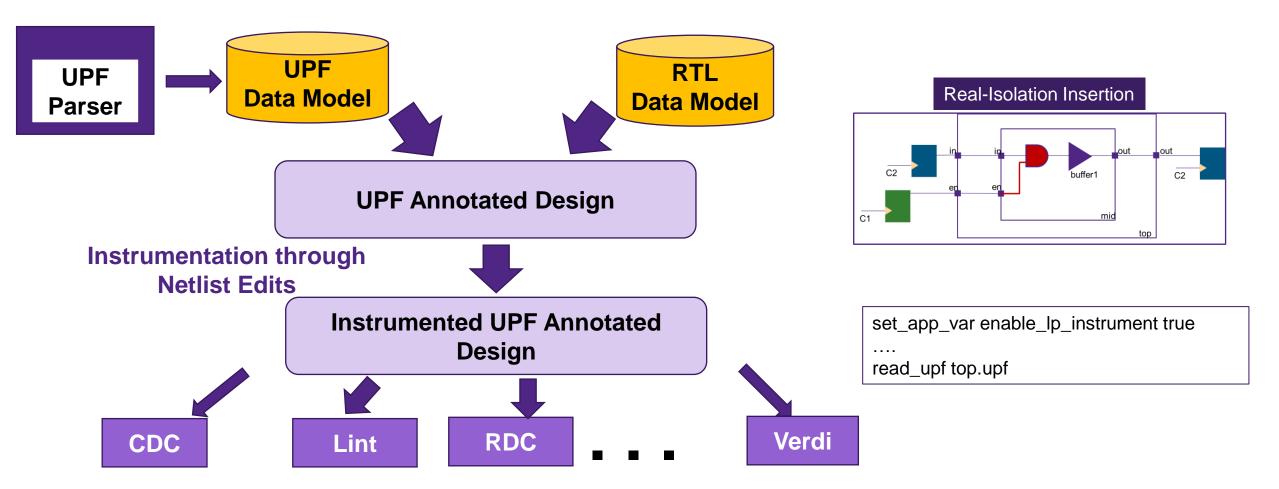

# Consistent UPF Analysis is Crucial

- ISO policy precedence analysis must be done exactly same as what DC/ICC will do

- Otherwise potential bugs will be missed in RTL, or false negative violation

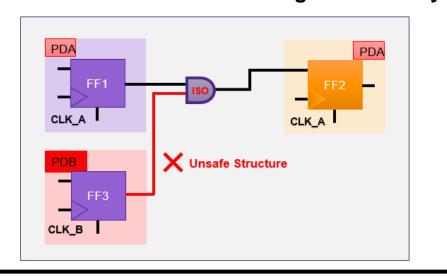

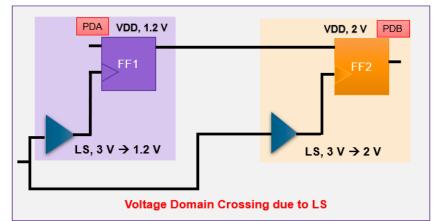

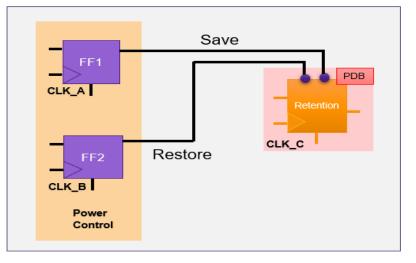

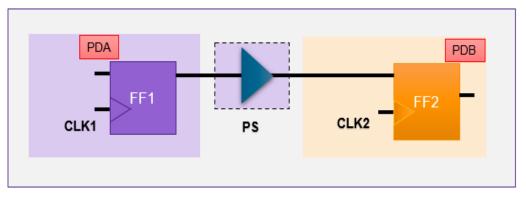

# CDC Verification Scenarios on UPF Instrumented Logic

### **Isolation Cell Insertion Causing Metastability**

Level-shifters causing New Clock-domain

### **CDC on Save-restore pins of Retention Flops**

#### Logic Connect Net introducing New CDC Path

SYNOPSYS

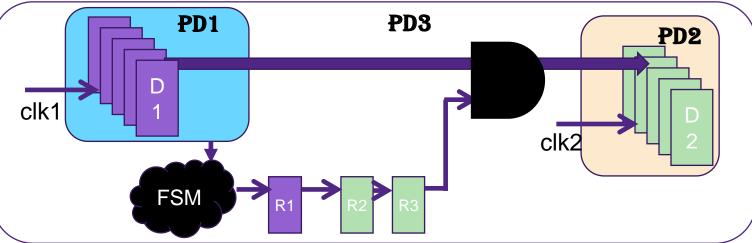

# Case Study: Graphics Sub System

Detecting LP aware CDC paths at Netlist

- Requirements : Identify all CDC paths which cross power domains

- Solution:

- VC Static Platform contains both VC SpyGlass CDC and VC LP (LP Signoff tool)

- CDC algorithm identifies all clock domain crossing paths (get\_cdc\_paths -from clk1\* -to clk2\*)

- VC LP Algorithm identifies power domain crossing (get\_crossover -source net1 -sink net2)

- CDC Path with power domain crossing can be identified with small enhancement

- get\_cdc\_paths -from clk1\* -to clk2\* -filter "power\_domain\_crossing==true"

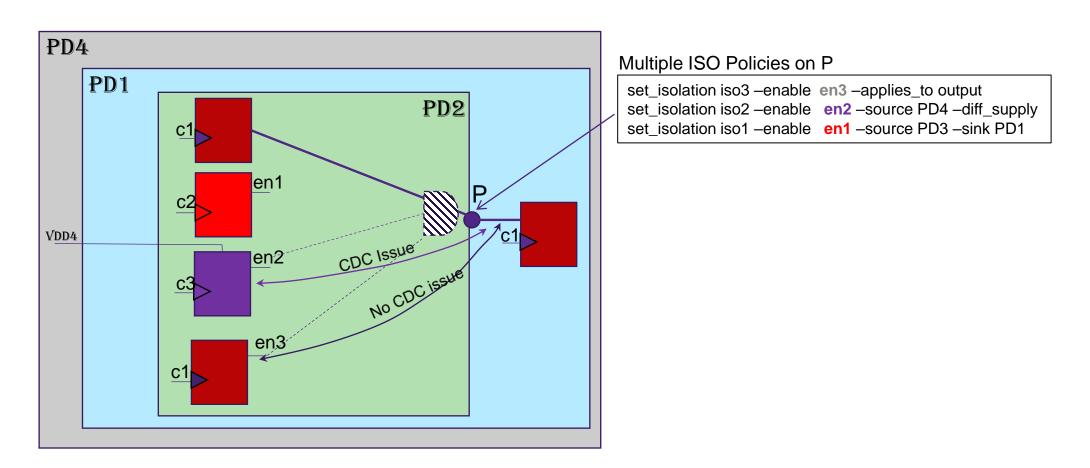

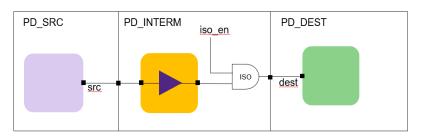

# PA CDC Violations Debug in VC SpyGlass

- VC SpyGlass supports in all the checks No separate rules

- Reports reason code for the violations on UPF instrumented logic

- Verdi highlights the instrumented logic in different color

| <b>V</b>                                                   | VCst Activity View (or                     | attoemt571)                                                          | _ <b>—</b> ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------------------------------------------|--------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ActivityPath: 🔇 🔍 VC Static   Verification   CDC/RDC   Ope | en   error   Sync-Stage   SYNCCDC_CTRLPATH | PARTIAL                                                              | VCst <verdi:container:1> (on attoemt571)</verdi:container:1>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| □ VC Static (VCst)<br>□ Design Setup (29)                  | Search: Live DestObject                    | ► >= ► BLK_INST34/outla/Q                                            | VCst <nschema 2="">466_SYNCCDC_CTRUATH_MARTIAL</nschema>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 🛱 Open (29)                                                | GroupCount Msg ID 🔺                        | DestObject ReasonInfoList                                            | File Edit View Schematic Trace Tools Window                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                            | 🕑 1-1 < 🕩 20 164                           | BLK_INST12/test_in_flop/Q NFF_SYNC_AND_DST_CLK_DOMAIN_DIFF •••• BLK_ | NST1 🔍 🔍 🖫 💭 🗔 🖑 構 🦙 🕐 🗶 🔛 🚺 🖸 🗘 🍢 🕢 🔇 Power Domain: dip_top MASTER_CLK: Vtop Power Signal Type:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| info (2)<br>⊕ UPF (2)                                      | 🖃 2-1 🔩 🗊 2 459                            | BLK_INST21/nff1/out1/Q SYNC_BY_NFF *** BLK_                          | CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC_CTRL/MIH_SOC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| - Waived                                                   | • 2-2 <                                    | BLK_INST21/nff1/out1/Q SYNC_BY_NFF **** BLK_                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| - Acknowledged<br>Needsinfo                                | □ 3-1 << D 2 466                           | BLK_INST34/outla/Q SYNC_BY_NFFTR                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 🗄 Verification (493)                                       | <b>3-2 3</b> -2 <b>1</b> 467               | BLK_INST34/out1a/Q UPF_INSTRUMENTED ···· iso_e                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| □ CDC/RDC (493) □ Open (493)                               | □ 4-1 << D 2 465                           | BLK_INST34/out2a/Q SYNC_BY_NFF ····TR                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ⊖ error (370)<br>⊖ Setup-Stage (42)                        | • 4-2 <                                    | BLK_INST34/out2a/Q UPF_INSTRUMENTED ···· iso_e                       | n MO out2 in2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| - SETUP_ASYNC_CLOCK_OVERLAP (10)                           | 5 <b>C</b> 1 453                           | BLK_INST31/src1/Q NFF_SYNC_AND_DST_CLK_DOMAIN_DIFF DATA              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SETUP_RESET_UNDECL (1)                                     | 6 <b>C</b> 1 480                           | BLK_INST29/src/Q NFF_SYNC_AND_DST_CLK_DOMAIN_DIFF DATA               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SETUP_INPUT_MULTICLK_LOAD (9)                              | 7 3 1 479                                  | BLK_INST23/src/Q NFF_SYNC_AND_DST_CLK_DOMAIN_DIFF DATA               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SETUP_OUTPUT_MULTICLK_DRIVER (4)                           | 8 4 1 451                                  | BLK_INST31/src3/Q NFF_SYNC_AND_DST_CLK_DOMAIN_DIFF DATA              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SETUP_PORT_PARTIALLY_CONSTRAINED (2)                       |                                            |                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SYNCCDC_CTRLPATH_PARTIAL (13 groups,35)                    |                                            |                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| GlitchCheck-Stage (7)                                      | Error - SYNCCDC_CTRLPATH                   | PARTIAL                                                              | Update with Single Click 🔹                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 🛱 warning (4)                                              | Partially matched control syn              | chronization scheme found for CDC path from <b>iso_en</b> to         | Preventian found for CDC path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                            |                                            | ng from _AUTO_VCLK_PORT_1_:33 to MASTER_CLK:12 . 💷 <u>H</u>          | B Basic Hessage: raising machine come systems of the CPART 1.35 to 1<br>B Basic B |

| 🛱 Setup-Stage (112)                                        | New Violation Schema                       | tic                                                                  | Type net MASTER CLK12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |