# Reusing Sequences in a Multi-Language environment using UVM-ML OA

Hannes Fröhlich, Cadence Design Systems, UK Kishore Sur, Cadence Design Systems, India

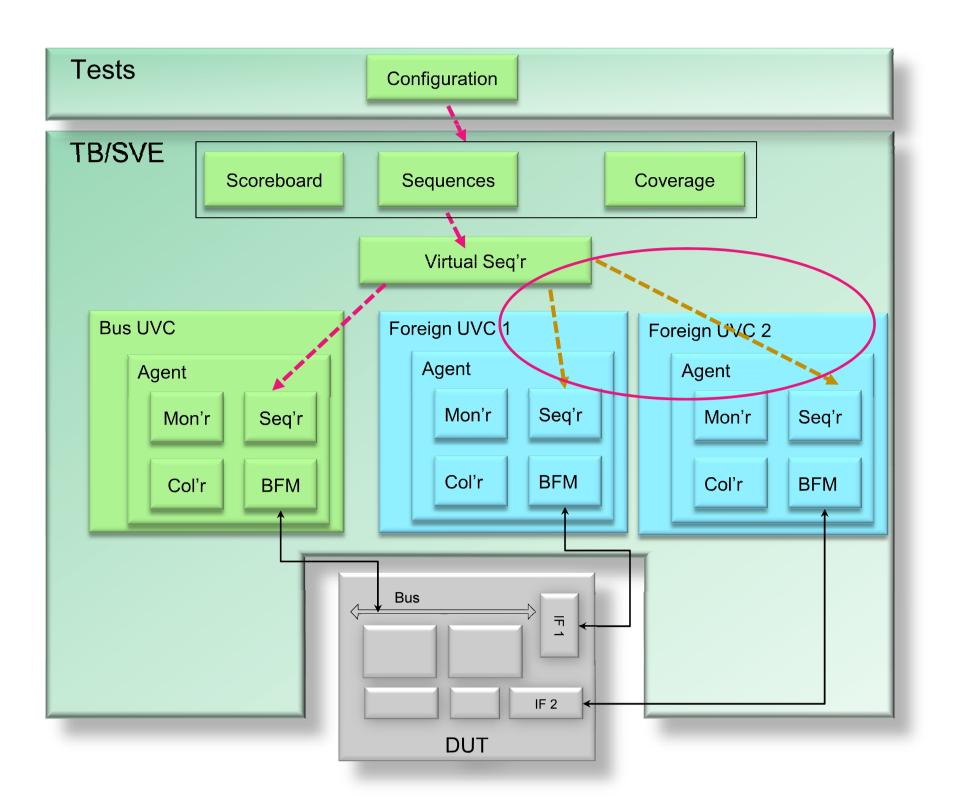

#### Sequence Reuse in multi-language Verification Environments

How can it be done?

# **UVM-ML Open Architecture Library**

Cadence has provided a broad UVM-ML solution since 2009

- + Provided on OVM first, and then on UVM

- + Enables integration of 3 languages (SV, e, SC)

- Part of Cadence® Incisive® Functional Verification Platform

In 2013, Cadence (w/ AMD) expand multi-language offering significantly

- UVM-ML Open Architecture (UVM-ML OA)

Open source, standardization ready (submitted to MLV-WG for consideration)

- Simulator independent

- Available on Accellera download

- Main features

Modular and extensible architecture

- TLM communication (TLM1 and TLM2)

- Unified hierarchy solution

- Multi-language configuration

- Multi-language sequence layering

- Coordinated initialization

- Pre-/post-/runtime phase synchronization

## <u>Sequence reuse – Choose Use Model that fits best</u>

| Use Model                                                                                              | Controllability                                                                                                                                       | Integration Effort                                                                                                            |

|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Side by Side  - instantiate VIPs in parallel and configure locally                                     | <ul> <li>No interaction with top level sequencer</li> <li>Users need to carefully import files to make sure correct sequences are selected</li> </ul> | • Least effort                                                                                                                |

| Unified Configuration  - use the UVM-ML  configuration mechanism  to select the default/MAIN  sequence | <ul> <li>Only the topmost sequence can be selected</li> <li>=&gt; might be sufficient in some cases</li> </ul>                                        | <ul> <li>Medium Effort</li> <li>Users need to use UVM-ML         OA library and use unified         hierarchy     </li> </ul> |

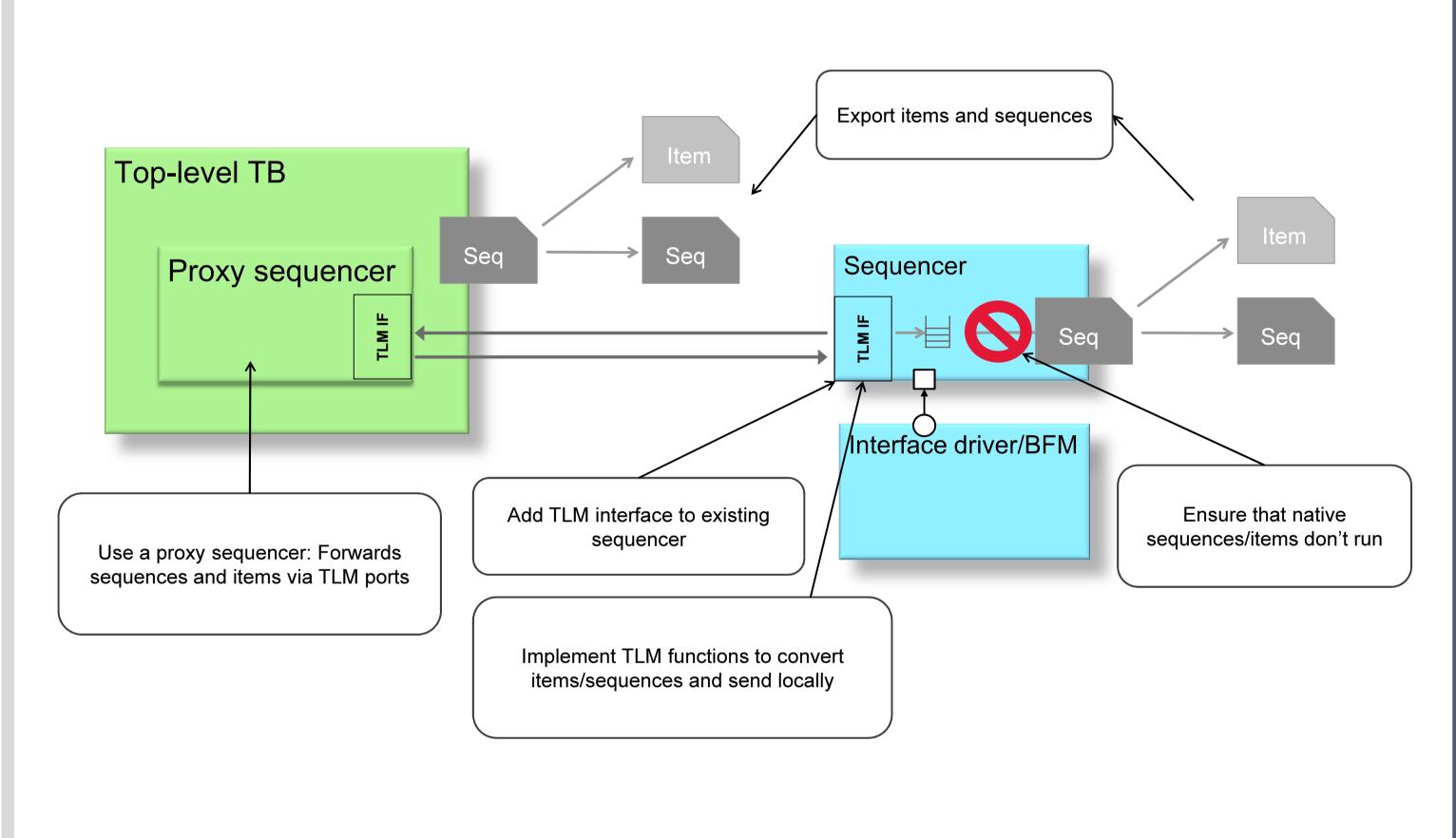

| Unified Control  - use UVM-ML proxy sequencer and TLM solution                                         | <ul> <li>Full control for sequences and items</li> <li>Ability to integrate in virtual sequencer</li> </ul>                                           | <ul> <li>High Effort</li> <li>Requires type mapping for sequences and items</li> </ul>                                        |

# <u>Unified Control – using proxy sequencers and TLM ports</u>

#### **CONCLUSIONS**

Sequence reuse can be achieved in multiple ways

+ Trade off between <u>integration effort</u> and top-level <u>controllability</u> of sequences and items

UVM-ML OA library has infrastructure and features to enable users to chose different sequence reuse use models

- Multi-language configuration can be used for low controllability solution

- Multi-language TLM communication and proxy sequencer types/templates can be used to achieve <u>fine grained control</u> of sequence and sequence items

### REFERENCES

- [1] UVM-ML Open Architecture (Overview and download) <a href="http://forums.accellera.org/files/file/65-uvm-ml-open-architecture">http://forums.accellera.org/files/file/65-uvm-ml-open-architecture</a>

- [2] B. Sniderman, V Yankelevich, "Multi-Language Verification: Solutions for Real World Problems", DVCon 2014, San Jose, CA <a href="http://events.dvcon.org/2014/proceedings/papers/12\_1.pdf">http://events.dvcon.org/2014/proceedings/papers/12\_1.pdf</a>

© 2014 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo, and Incisive are registered trademarks of Cadence Design Systems, Inc. in the United States and other countries. All other trademarks are the property of their respective owners.

Additional questions or support

Cadence Design Systems, UVM-ML support mail alias: <a href="mailto:support\_uvm\_ml@cadence.com">support\_uvm\_ml@cadence.com</a> Hannes Fröhlich <a href="mailto:hannes@cadence.com">hannes@cadence.com</a>

Kishore Sure <u>kishore@cadence.com</u>