## Requirements Driven Design Verification Flow Tutorial

#### Ateş BERNA – Managing Partner Ahmet JORGANXHI – Design & Verification Eng.

## About Electra IC

- Founded in 2014

- Headquarter in Istanbul, Turkey

- Branch office in Ankara

- Total 20 people

- ASIC/FPGA D&V Services

- ASIC/FPGA/EmbSys Training Services

#### Requirement

Requirements are definitions of "what" hardware must do.

Design Engineer

#### Requirement

Source: Airborne Electronic Hardware Design Assurance R. Fullton & R.Vandermolen, 2015

DESIGN AND VERIF

CONFERENCE AND EXHIBITION

## **Properly Captured Requirement Format**

| The {output or verifiable aspect}                                           |

|-----------------------------------------------------------------------------|

| shall                                                                       |

| {always, unconditionally, only}                                             |

| {assert, deassert, set to value}                                            |

| {before, after, when, during, within}                                       |

| <pre>{xnsec, the next rising edge of a clock, read/write asserts low}</pre> |

| when {inputs are set to a combination of high/low,                          |

| a sequence of events has occurred or                                        |

| a timed period elapses}                                                     |

|                                                                             |

6

## **Properly Captured Requirement Sample**

```

EIC_IP_CORE_FR_001:

The {dscrt_out}

shall

{always}

{assert to logic HIGH}

{within 40 nanoseconds}

when {dscrt_in is asserted to logic HIGH}

```

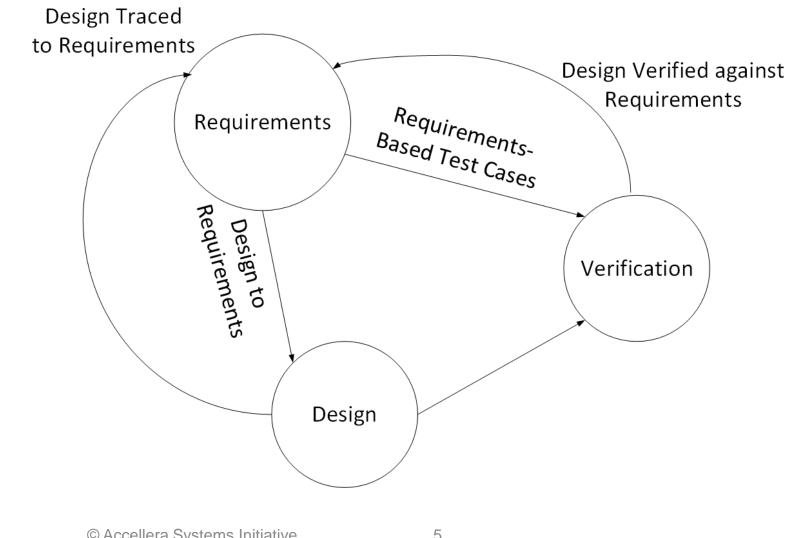

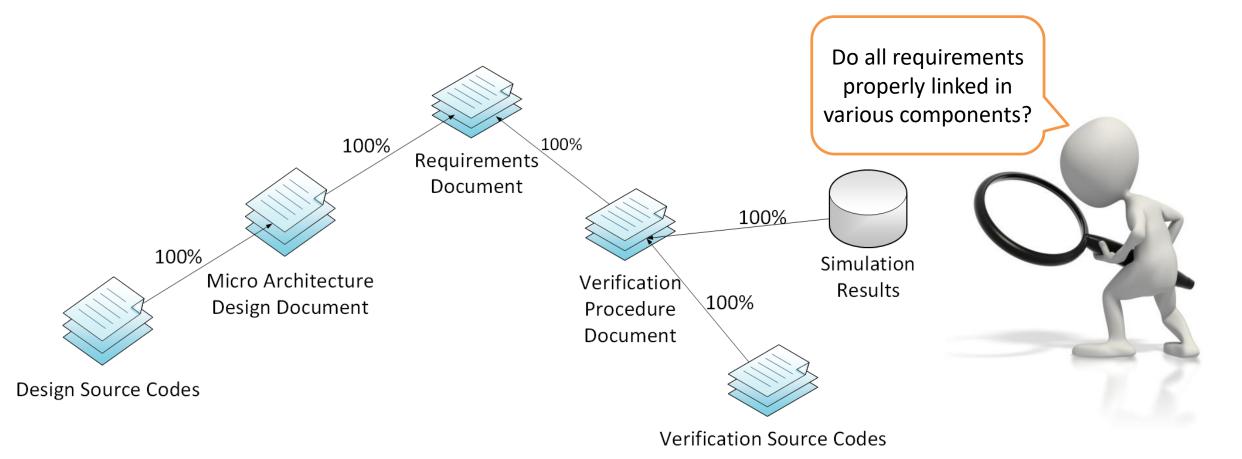

## **Requirement Tracing** 100% Requirements Document 100% Micro Architecture **Design Document**

#### **Design Source Codes**

© Accellera Systems Initiative

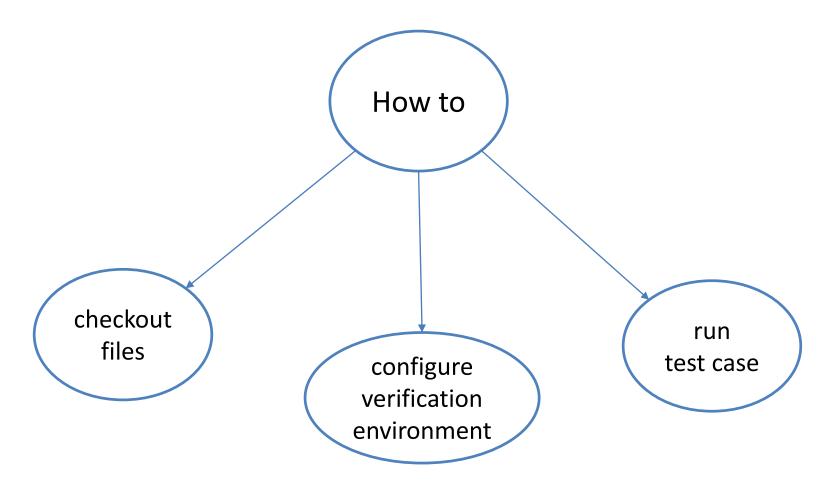

#### Introduction to Verification

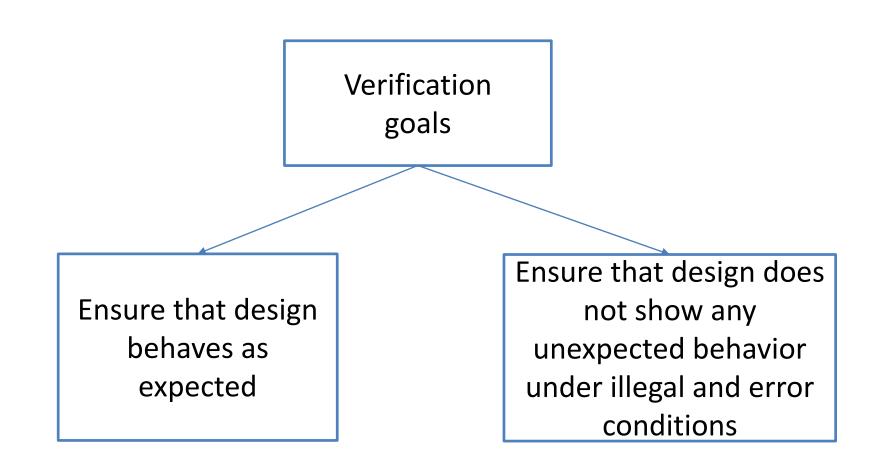

#### **Goals of Verification**

## Verification Methodologies Comparison

| Features                                   | Classic VHDL | SV/UVM | UVVM/OSVVM |

|--------------------------------------------|--------------|--------|------------|

| OOP                                        | -            | +      | -          |

| Ease of use for whose who knows VHDL       | +            | -      | +          |

| Ease of use for whose who knows<br>Verilog | -            | +      | -          |

| Code Coverage                              | +            | +      | +          |

| Functional Coverage                        | -            | +      | +          |

| Development Tool Advantages                | +            | -      | +          |

| IEEE Standard                              | +            | +      | -          |

| Extensive Verification IP Support          | _            | +      | _          |

DESIGN AND VE

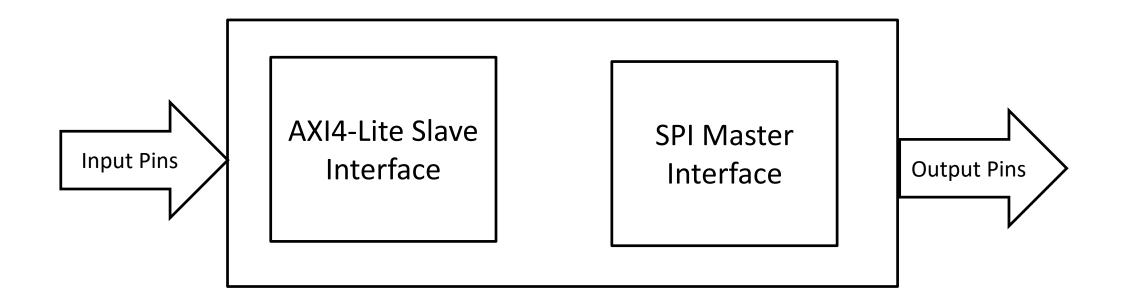

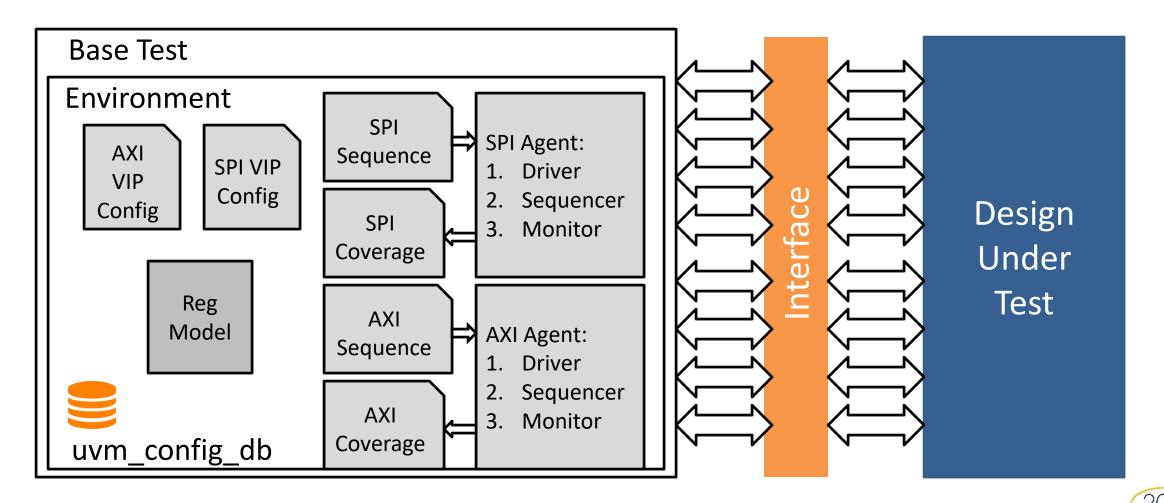

## SV/UVM Verification Methodology

- Sequence Methodology

- Factory Mechanism

- Config Mechanism

- UVM Phase

- Modularity and Re-Usability

- Verification Environment

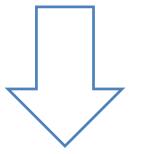

- For each testcase:

- Description

- Coverpoints

- Test Steps

ESIGN AND VE

DESIGN AND VE

NCE AND EXHIBI

[EIC\_IP\_CORE\_FR\_002] *spi\_cs\_n* shall assert to logic LOW and remain for 24.5\*T<sub>spi\_sclk</sub> ± 1% when any of the Active State conditions of *spi\_mosi* are satisfied. (Tspi\_sclk = 10 MHz)

[EIC\_IP\_CORE\_FR\_005] *spi\_sclk* shall assert to clock signal with the period 10 MHz when any of the Active State conditions of *spi\_mosi* are satisfied.

[EIC\_IP\_CORE\_FR\_008] *spi\_mosi* shall assert to opcode and data value where;

- Opcode : 0x04

- Data : SPI CONF DATA REG 2(15:0)

within  $500^*T_{s_{axi_{aclk}}} \pm 1\%$  when SPI CONF DATA REG 2(31) is logic HIGH. ( $T_{s_{axi_{aclk}}} = 100$  MHz, SPI CONF DATA REG is register at address 0x8)

TC\_ProjectName\_FunctionalElement\_Feature\_CHECK

#### TC\_PRJX\_SPI\_PORT\_CHECK

© Accellera Systems Initiative

#### Description

This test case verifies active state of output ports of SPI Master Interface which are listed below.

- spi\_cs\_n

- spi\_sclk

- spi\_mosi

As test scenario after applied reset, AXI4 Write Transfer to SPI CONF DATA REG 2 register which is located at address 0x8 with 31<sup>st</sup> of Write Data set to 1 and (30:0) set to a random value will be initiated. Then, at required time, active states of spi\_cs\_n, spi\_sclk and spi\_mosi output ports are verified.

**Pass/Fail Criteria:** Assertions and checkers of requirement checking mechanism of test class should pass.

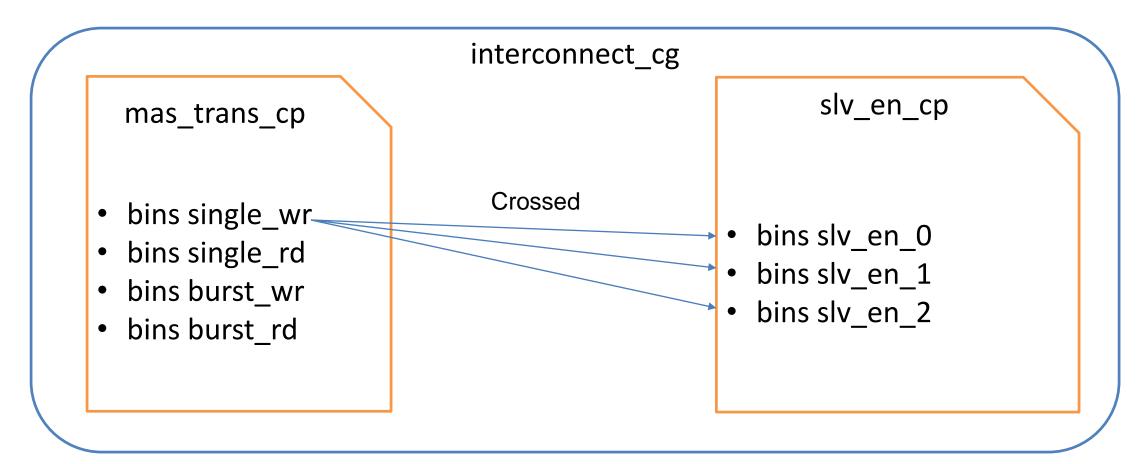

Coverpoints

spi\_master\_cg: spi\_cs\_cp

spi\_master\_cg: spi\_opcode\_cp

spi\_master\_cg: spi\_trans\_type\_cp

axi4\_slave\_cg: axi4\_trans\_type\_cp

reg\_cg: spi\_conf\_reg2\_cp

© Accellera Systems Initiative

| Action                                                                                  | Expected Result | Assertion | Requirement Links |

|-----------------------------------------------------------------------------------------|-----------------|-----------|-------------------|

| <ol> <li>Apply clock signal<br/>with period of 100<br/>MHz to sys_clk input.</li> </ol> |                 |           |                   |

| 2. Set reset_n to logic LOW.                                                            |                 |           |                   |

| 3. Wait for 4 to 10 sys_clk cycles.                                                     |                 |           |                   |

| 4. Set reset_n to logic<br>HIGH                                                         |                 |           |                   |

| Action                           | Expected Result | Assertion | Requirement Links |

|----------------------------------|-----------------|-----------|-------------------|

| 5. Initiate AXI4 Write           |                 |           |                   |

| Transfer to address              |                 |           |                   |

| 0x8 with 31 <sup>st</sup> bit of |                 |           |                   |

| write data set to 1              |                 |           |                   |

| and (30:0) bits of               |                 |           |                   |

| write data set to                |                 |           |                   |

| random value.                    |                 |           |                   |

| Action                                                                         | Expected Result                                                                                                                                                        | Assertion | Requirement Links  |

|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------------|

| <ul><li>6. Perform steps 6.1-</li><li>6.3 in parallel</li><li>manner</li></ul> |                                                                                                                                                                        |           |                    |

| 6.1 Within<br>500*sys_clk± 1%<br>cycles check<br>spi_mosi.                     | spi_mosi should<br>assert<br>respectively to<br>opcode and data<br>byte in order:<br>Opcode : 0x04<br>Data Byte : (15:0)<br>bits of write data<br>initiated in step 5. |           | EIC_IP_CORE_FR_008 |

SYSTEMS INITIATIVE

accel

| Action                                                                                       | Expected Result                                                           | Assertion                                 | Requirement Links  |

|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------|--------------------|

| 6.2 Within<br>500*sys_clk± 1%<br>check spi_cs_n.<br>Keep checking for<br>24.5*Tspi_sclk± 1%. | spi_cs_n should<br>assert and<br>remain at logic<br>LOW.                  | eic_ip_core_fr<br>_003_spi_cs_n<br>_check | EIC_IP_CORE_FR_003 |

| 6.3 Within<br>500*sys_clk± 1%<br>check spi_sclk.                                             | spi_sclk should<br>assert to clock<br>signal with<br>period of 10<br>MHz. | eic_ip_core_fr<br>_005_spi_sclk_<br>check | EIC_IP_CORE_FR_005 |

CONFERENCE AND EXHIBI

#### **Requirement Tracing**

#### **Requirement Verification**

Verification with:

- Assertion

- Self-Checking

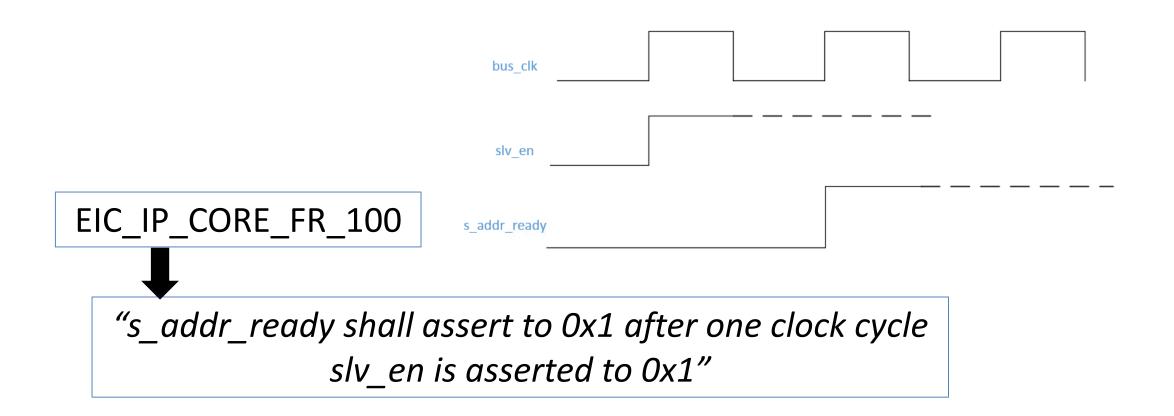

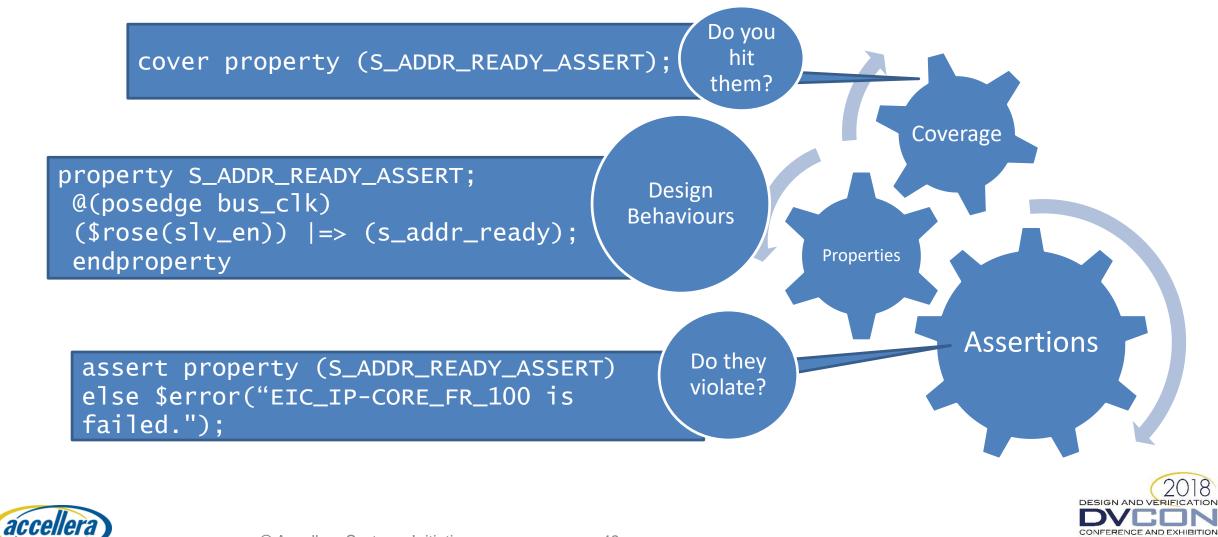

#### Verification with Assertion

© Accellera Systems Initiative

#### Verification with Assertion

cover property (S\_ADDR\_READY\_ASSERT);

```

property S_ADDR_READY_ASSERT;

@(posedge bus_clk)

($rose(slv_en)) |=> (s_addr_ready);

endproperty

```

assert property (S\_ADDR\_READY\_ASSERT)

else \$error("EIC\_IP\_CORE\_FR\_100 has failed.");

EIC\_IP\_CORE\_FR\_102

"i2c\_sda shall assert to I2C Write Transfer Sequence within 5us after reset n is set to logic HIGH with the following conditions:"

- *Slave Address : 7b1101010*

- Register Address : 0xC4

- Write Data Byte in order: 0xD0, 0xC1 and 0xAA

Task which verifies:1. Time when i2c\_sda isdeasserted after reset.2. Asserted value of thei2c\_sda

"i2c\_sda shall assert to I2C Write Transfer Sequence within 5us after reset\_n is set to logic HIGH with the following conditions:"

- Slave Address : 7b1101010

- Register Address : 0xC4

- Write Data Byte in order: 0xD0, 0xC1 and 0xAA

"i2c\_sda shall assert to I2C Write Transfer Sequence **within 5us** after reset\_n is set to logic HIGH with the following conditions:"

- Slave Address : 7b1101010

- Register Address : 0xC4

- Write Data Byte in order: 0xD0, 0xC1 and 0xAA

*"i2c\_sda shall assert to I2C Write Transfer Sequence within 5us after reset\_n is set to logic HIGH with the following conditions:"*

- Slave Address : 7b1101010

- Register Address : 0xC4

- Write Data Byte in order: 0xD0, 0xC1 and 0xAA

wait(dut\_if.reset\_n == 1);

tinit = \$time;

DESIGN AND VE

#### check\_i2c\_write (EIC\_IP\_CORE\_FR\_102,7b1101010, 8hC4, 8hD0, 8hC1, 8hAA, tinit, 5us)

check\_i2c\_write

(Req. ID, Slave Addr., Register Addr., Write Data, Starting Time, Req. Time)

"i2c\_sda shall assert to I2C Write Transfer Sequence **within 5us** after reset\_n is set to logic HIGH with the following conditions:"

- Slave Address : 7b1101010

- Register Address : 0xC4

- Write Data Byte in order: 0xD0, 0xC1 and 0xAA

# wait(m\_i2c\_seq.ev0.triggered); tfinal = \$time;

© Accellera Systems Initiative

"i2c\_sda shall assert to I2C Write Transfer Sequence within 5us after reset\_n is set to logic HIGH with the following conditions:"

- Slave Address : 7b1101010

- Register Address : 0xC4

- Write Data Byte in order: 0xD0, 0xC1 and 0xAA

wait(m\_i2c\_seq.ev0.triggered); slv\_addr = m\_i2c\_seq.data\_buf; wait(m\_i2c\_seq.ev0.triggered);

"i2c\_sda shall assert to I2C Write Transfer Sequence within 5us after reset\_n is set to logic HIGH with the following conditions:"

- Slave Address : 7b1101010

- Register Address : 0xC4

- Write Data Byte in order: 0xD0, 0xC1 and 0xAA

- Register Address  $\rightarrow$  reg\_addr

- First Write Data Byte  $\rightarrow$  wr\_data[0]

- Second Write Data Byte  $\rightarrow$  wr\_data[1]

- Third Write Data Byte  $\rightarrow$  wr\_data[2]

"i2c\_sda shall assert to I2C Write Transfer Sequence within 5us after reset\_n is set to logic HIGH with the following conditions:"

- Slave Address : 7b1101010

- Register Address : 0xC4

- Write Data Byte in order: 0xD0, 0xC1 and 0xAA

if(({Slave Addr, 1b0} == slv\_addr) && (Register Addr == reg\_addr) &&

(Write Data [0] == wr\_data[0]) && (Write Data [1] == wr\_data[1]) &&

(Write Data [2] == wr\_data[2]) && (tfinal - tinit <= Req. Time))

`uvm\_info("req\_pass", \$sprint("Requirement: %s has passed", Req.ID), UVM\_LOW)

else

`uvm\_error("req\_fail", \$sprint("Requirement: %s has failed", Req. ID))</pre>

#### EIC\_IP\_CORE\_FR\_103

Control Register should assert to **write data byte of the AHB Write Transfer within 2 clk cycles**, after all of the following conditions are satisfied:

- reset\_n is set to logic HIGH

- AHB Write Transfer to Control Register address is completed

#### **Register Class**

SYSTEMS INITIATIVE

```

class Control_Reg extends uvm_reg;

function new(string name = "Control_Reg")

super.new(name, 16, UVM_NO_COVERAGE)

endfunction

Register width

```

virtual function void build();

```

Control_Reg = uvm_reg_field::type_id::create("Control_Reg");

Control_Reg.configure(this, 16, 0, "RW", 0, 16'h0000, 1, 1, 1);

endfunction

Size

Isb

Volatility

Macellera Systems Initiative

```

In the test class register block is defined

REG block m\_reg\_block;

Control Register should assert to write data byte of the AHB Write Transfer within 2 clk cycles, after all of the following conditions are satisfied:

- reset\_n is set to logic HIGH

- AHB Write Transfer to Control Register address is completed

wait(dut\_if.reset\_n == 1); m\_reg\_block.Control\_Register\_h.write(status, write\_value);

© Accellera Systems Initiative

Control Register should assert to **write data byte** of the AHB Write Transfer within 2 clk cycles, after all of the following conditions are satisfied:

- reset\_n is set to logic HIGH

- AHB Write Transfer to Control Register address is completed

#### get\_value = m\_reg\_block.Control\_Register\_h.get(status);

Control Register should assert to write data byte of the **AHB Write Transfer within 2 clk cycles**, after all of the following conditions are satisfied:

- reset\_n is set to logic HIGH

- AHB Write Transfer to Control Register address is completed

#### repeat(2) @(posedge bus\_if.clk); m\_reg\_block.Control\_Register\_h.read(status, read\_value);

© Accellera Systems Initiative

Control Register should assert to **write data byte of the AHB Write Transfer within 2 clk cycles**, after all of the following conditions are satisfied:

- reset\_n is set to logic HIGH

- AHB Write Transfer to Control Register address is completed

```

If(read_value == get_value)

`uvm_info("req_pass", $sprint("Requirement EIC_IP_CORE_FR_103

has passed"), UVM_LOW)

else

`uvm_error("req_fail", $sprint("Requirement: EIC_IP_CORE_FR_103

has failed", Req. ID))

```

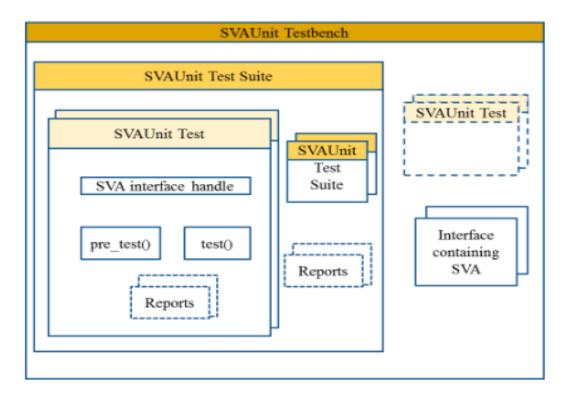

# Verification of Assertion with SVA Unit

Source:

Socianu.A & Ciocirlan.I (2015, April 29) SystemVerilog Assertion Verification with SVAUnit Retrieved from: https://www.amiq.com

## Verification of Assertion with SVA Unit

# Verification of Assertion with SVA Unit

|                                 |              |               | SVAUnit cl | hecks      |        |           |        |

|---------------------------------|--------------|---------------|------------|------------|--------|-----------|--------|

|                                 | CHECK_SVA_EX | ISTS CHECK_SV | LENABLED C | HECK_SVA_P | ASSEDC | CHECK_SVA | FAILED |

| S<br>V<br>A<br>I2C_CLK_SVA<br>s | . ✓          |               | /          | ✓          |        | 1         |        |

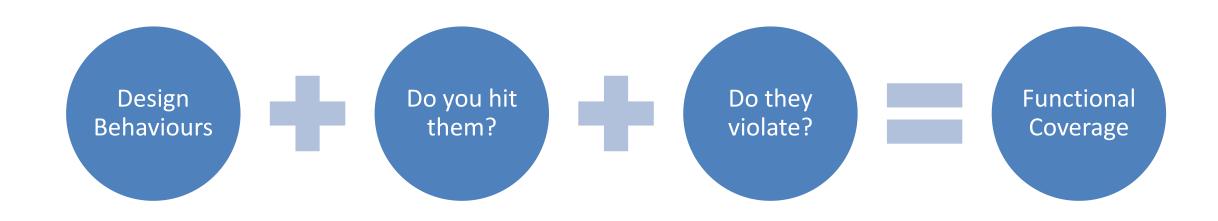

## **Coverage Analysis**

We need metrics for...

# **Coverage Analysis**

- Functional Coverage

- Code Coverage

- Other Coverage Types

- Linting (quality of RTL code)

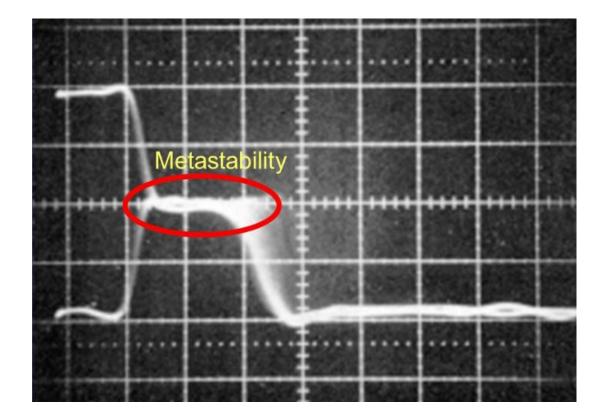

- Clock Domain Crossing (metastability)

© Accellera Systems Initiative

20

DESIGN AND VERIFICA

CONFERENCE AND EXHIBITION

IRO

© Accellera Systems Initiative

SYSTEMS INITIATIVE

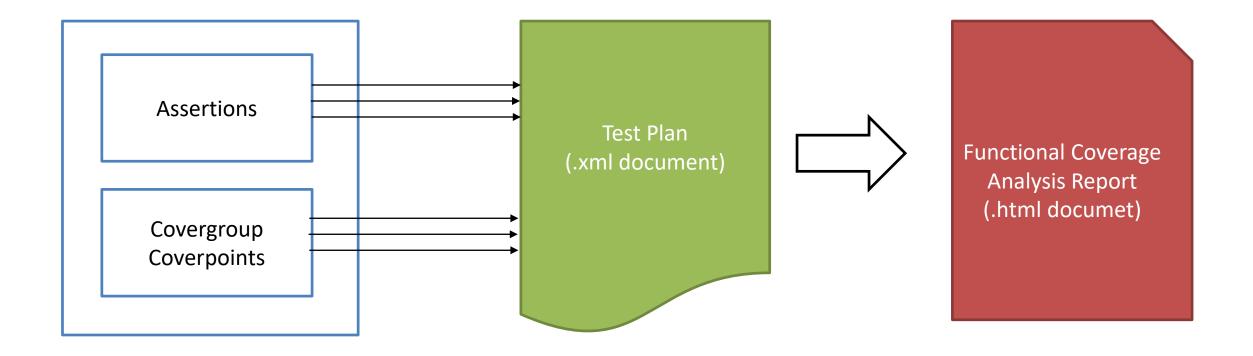

| 3.2.1   | TC_PRJX_SPI_PORT_CHECK     |                                                                                                                                          | 1 | 100 |

|---------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------|---|-----|

| 3.2.1.1 | TC_PRJX_SPI_PORT_CHECK_1cp | spi_master_cg:spi_cs_cpspi_master_cg:spi_opcode_cpspi_master_cg:spi_trans_type_cpaxi4_slave_cg:axi4_trans_type_cpreg_cg:spi_conf_reg2_cp | 1 | 100 |

| 3.2.1.2 | TC_PRJX_SPI_PORT_CHECK_2a  | eic_ip_core_fr_003_spi_cs_n_check<br>eic_ip_core_fr_005_spi_sclk_check Assertion                                                         | 1 | 100 |

| 3.2.1.3 | TC_PRJX_SPI_PORT_CHECK_3cd | eic_ip_core_fr_003_spi_cs_n_cov<br>eic_ip_core_fr_005_spi_sclk_cov                                                                       | 1 | 100 |

#### **Coverage Summary by Testplan Section:**

| Scope <                            | Coverage < | % of Goal ৰ |

|------------------------------------|------------|-------------|

| 3.2.1 TC_PRJX_SPI_PORT_CHECK       | 100.00%    | 100.00%     |

| 3.2.1.1 TC_PRJX_SPI_PORT_CHECK_1cp | 100.00%    | 100.00%     |

| 3.2.1.2 TC_PRJX_SPI_PORT_CHECK_2a  | 100.00%    | 100.00%     |

| 3.2.1.3 TC_PRJX_SPI_PORT_CHECK_3cd | 100.00%    | 100.00%     |

DESIGN AND VE

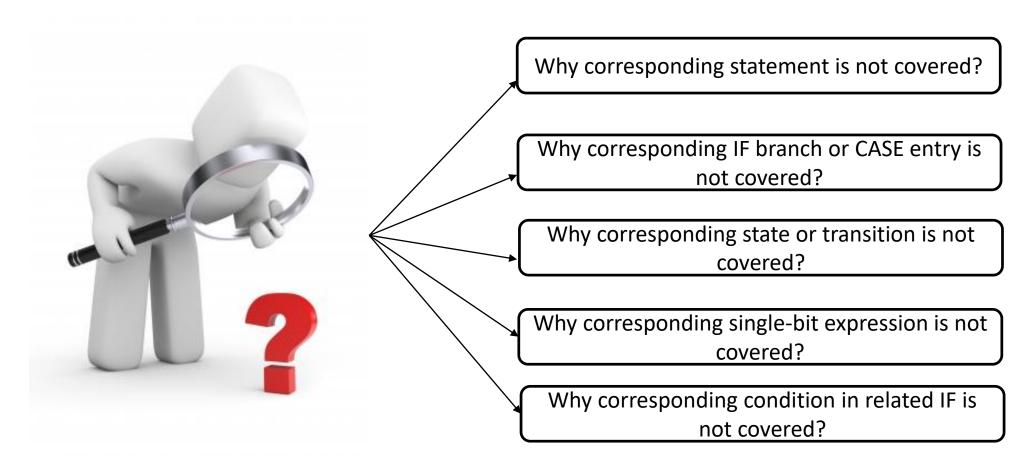

- **S**tatement—Did we cover every statement?

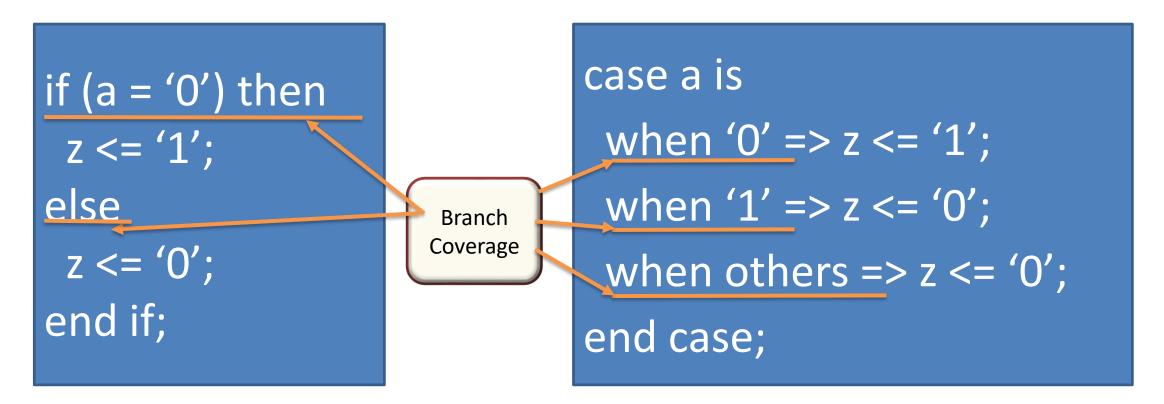

- **B**ranch—Did we cover every IF branch and CASE entry?

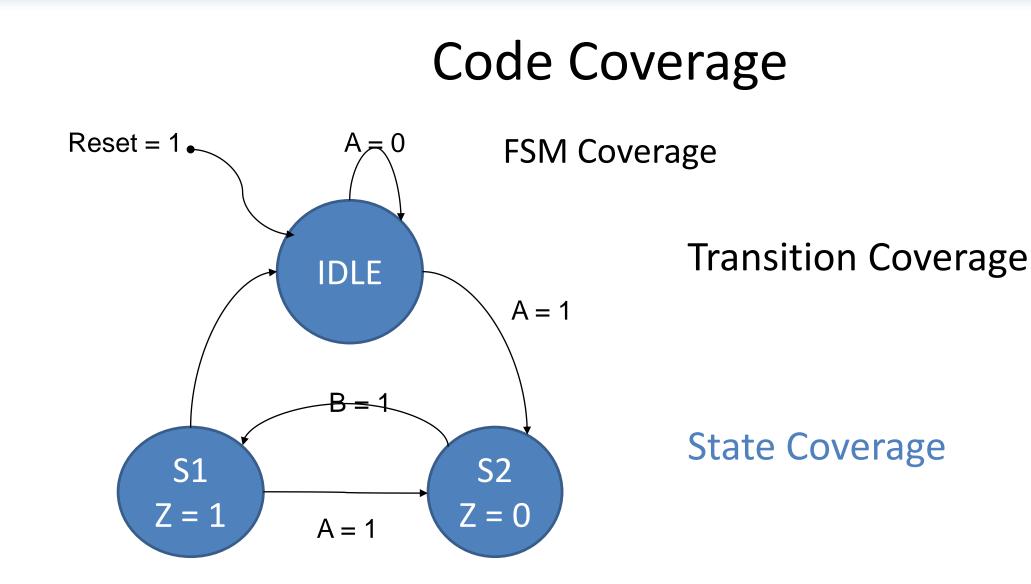

- **F**inite State Machine—Did we cover all states and transitions?

- **E**xpression—Did we fully test our single-bit expressions?

- **C**ondition—Did we test all the conditions in our IF statements?

Statement Coverage

Statement Coverage process (a)

begin

z <= '0'; if (a = 0) then z <= '1';

end process;</pre>

Line Coverage

#### **Branch Coverage**

© Accellera Systems Initiative

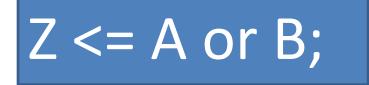

**Condition Coverage**

• Condition 1 -> a = 1

**Expression Coverage**

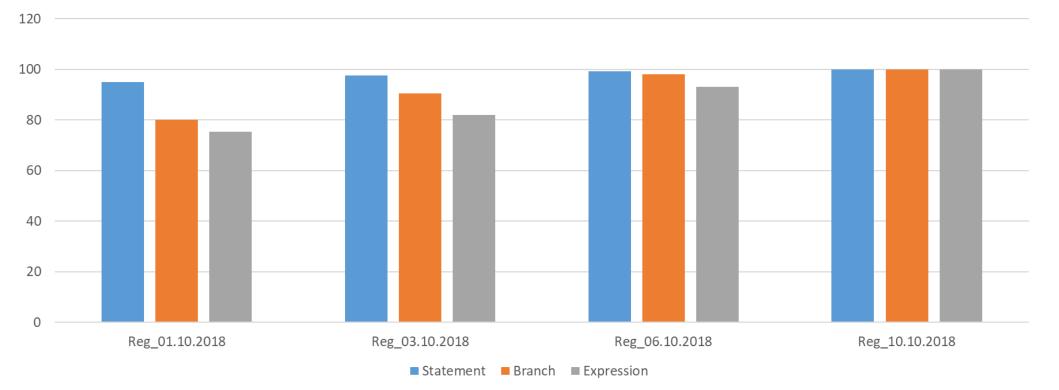

- Reason of the code coverage holes:

- Unused Codes Lines

- Missing Test Scenario

Code Coverage Improvement Graphics

DESIGN AND VERI

CONFERENCE AND EXHIBITION

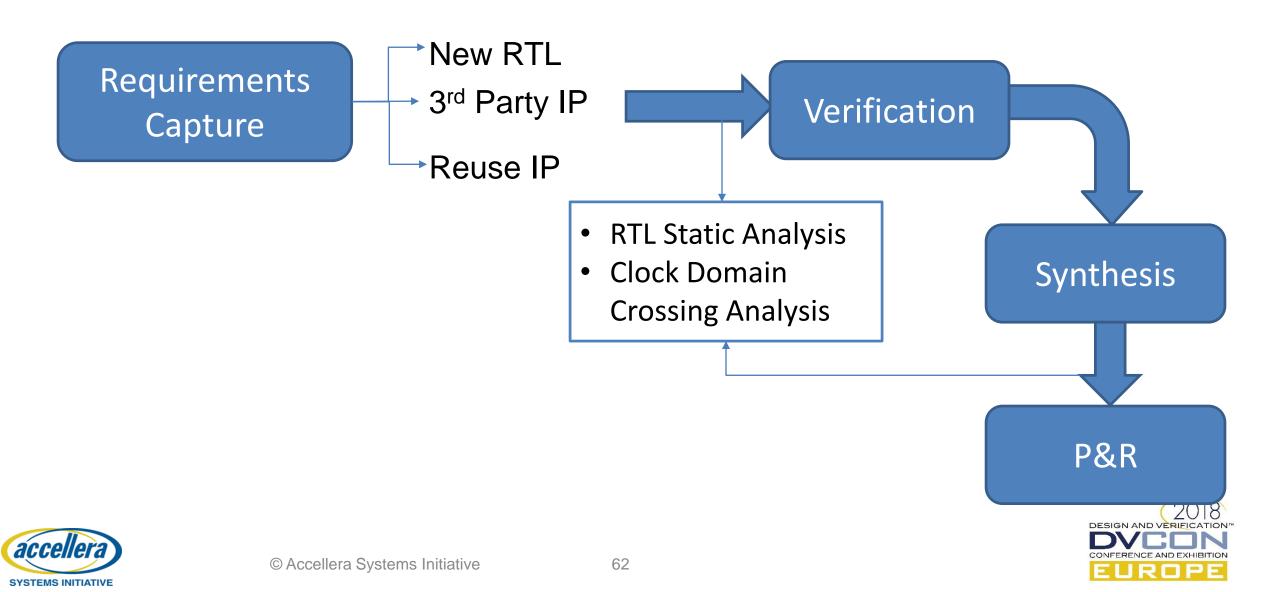

# **RTL Analysis**

# **RTL Analysis**

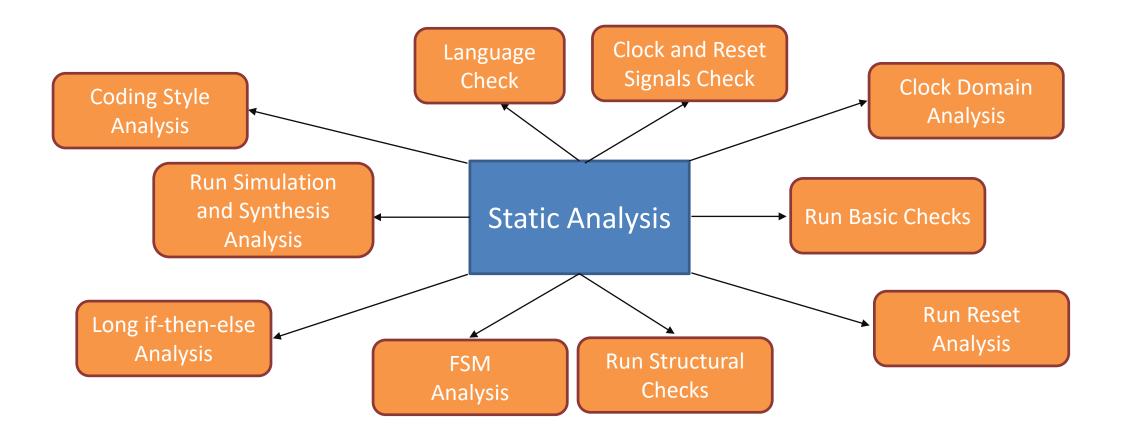

# RTL Analysis – Static Checks

| <ul> <li>No X-source problems</li> <li>Clocks</li> </ul>                                             | ^   | Package: DO-254                                                                                                                                        | ^ |

|------------------------------------------------------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| <ul> <li>Clock Domain Crossings</li> <li>Advanced Clock Environment</li> <li>Coding style</li> </ul> |     | <b>Description:</b> This package includes checks that aid in compliance with the DO-254 military standard.                                             |   |

| <ul> <li>Coding conventions</li> <li>Assignment Checks</li> </ul>                                    | - 1 | Checks:                                                                                                                                                |   |

| <ul> <li>Simulation/Synthesis</li> <li>No implied_latches</li> </ul>                                 |     | <ul> <li><u>GRST</u> (Gated reset)</li> <li><u>HCCC</u> (Do not hard-code constants)</li> </ul>                                                        |   |

| Case statements                                                                                      |     | • <u>REGO</u> (Register all module outputs)                                                                                                            |   |

| <ul> <li>No size conflicts</li> <li>Naming</li> </ul>                                                |     | <ul> <li><u>UNREACHABLE_STATE</u> (Report Unreachable states)</li> <li><u>MCD</u> (No case default)</li> </ul>                                         |   |

| Signal Identification     Comments                                                                   |     | <ul> <li><u>MDA</u> (Missing case default assignment)</li> <li><u>CSL</u> (Complete sensitivity lists)</li> </ul>                                      |   |

| > FSM Checks                                                                                         |     | <u>MEB</u> (Missing else block)                                                                                                                        |   |

| <ul> <li>Miscellaneous checks</li> <li>SDC Verification</li> </ul>                                   |     | <ul> <li><u>ETB</u> (Empty then block)</li> <li><u>LEC</u> (Little endian checks)</li> </ul>                                                           | 1 |

| Cycle Based Simulation     Input IP                                                                  |     | <ul> <li><u>CCLP</u> (Infinite and 0-count loops)</li> <li><u>SLCC</u> (Separate lines for commands)</li> </ul>                                        |   |

| > New RTL                                                                                            |     | <u>INT_TRI</u> (Internal tristate objects)                                                                                                             |   |

| <ul> <li>Image: Golden RTL</li> <li>Image: Image: Golden RTL</li> </ul>                              |     | <u>COMMENT_END_STMNTS</u> (Comment end statements) <u>MCA</u> (Missing case item assignment)                                                           |   |

| <ul> <li>Principles of Verifiable RTL</li> <li>Reuse Methodology Manual</li> </ul>                   |     | <u>MIA</u> (Missing if assignment)                                                                                                                     |   |

| Semiconductor Reuse Standard                                                                         |     | <ul> <li><u>LATCH_CREATED</u> (Report on every latch created or inferred)</li> <li><u>COMMENT_NET_DEC</u> (Comment net declarations)</li> </ul>        |   |

| <ul> <li>DO-254</li> <li>STARC</li> </ul>                                                            |     | <ul> <li><u>STATE_VAR_NAME</u> (Run name analysis on FSM state variable names)</li> <li><u>COMMENT_PORT_DEC</u> (Comment port declarations)</li> </ul> |   |

| UltraFast Design Methodology for Vivado                                                              |     | <u>RST</u> (All flip-flops resettable)                                                                                                                 |   |

| <ul> <li>Quartus II Best Practices</li> <li>Microsemi RTG4 Best Practices</li> </ul>                 | ~   | <ul> <li><u>RESET_POLARITY</u> (Check reset polarity consistency)</li> <li><u>FOREIGN_LANGUAGE_KWD</u> (Report usage of Foreign Language</li> </ul>    | ~ |

CONFERENCE AND EXHIBIT

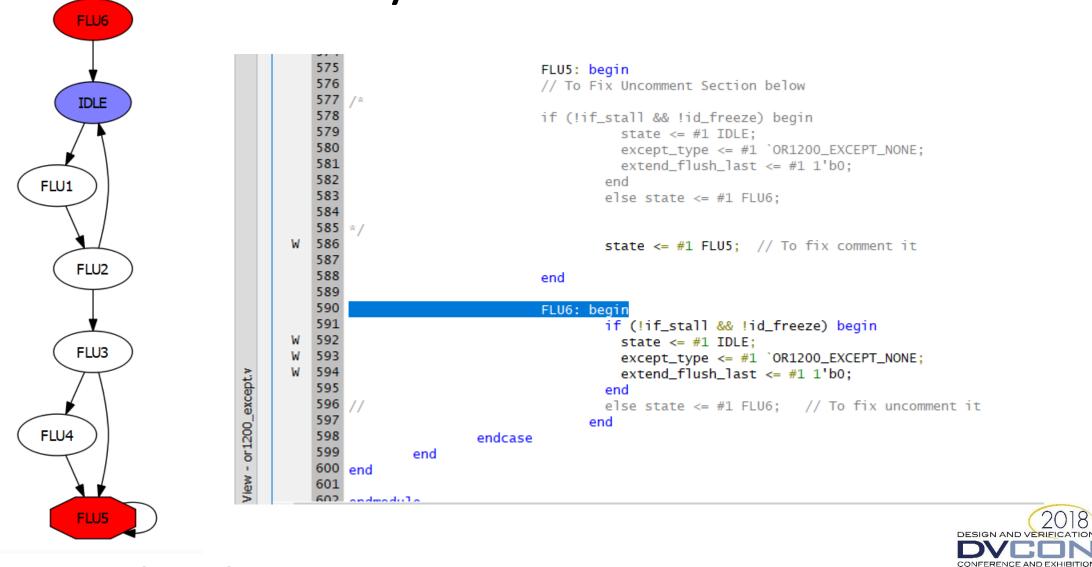

#### **RTL Analysis – FSM Checks**

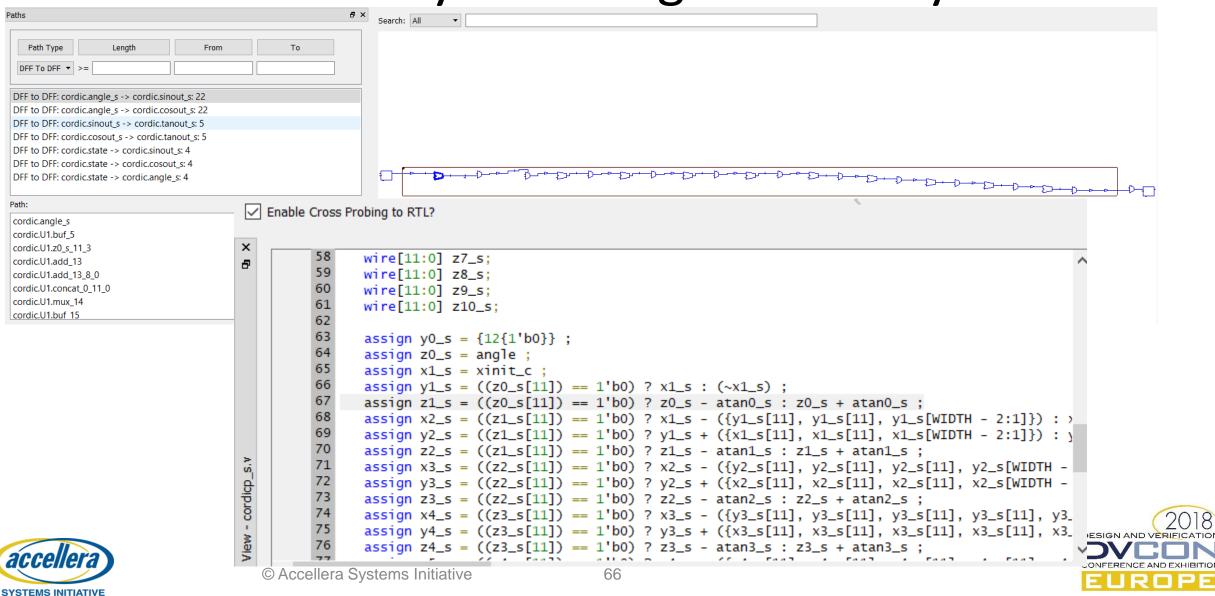

#### RTL Analysis – Long Path Analysis

## **RTL Analysis**

#### 2016 Industry research reports Clocking/CDC Errors are the #2 cause of respins

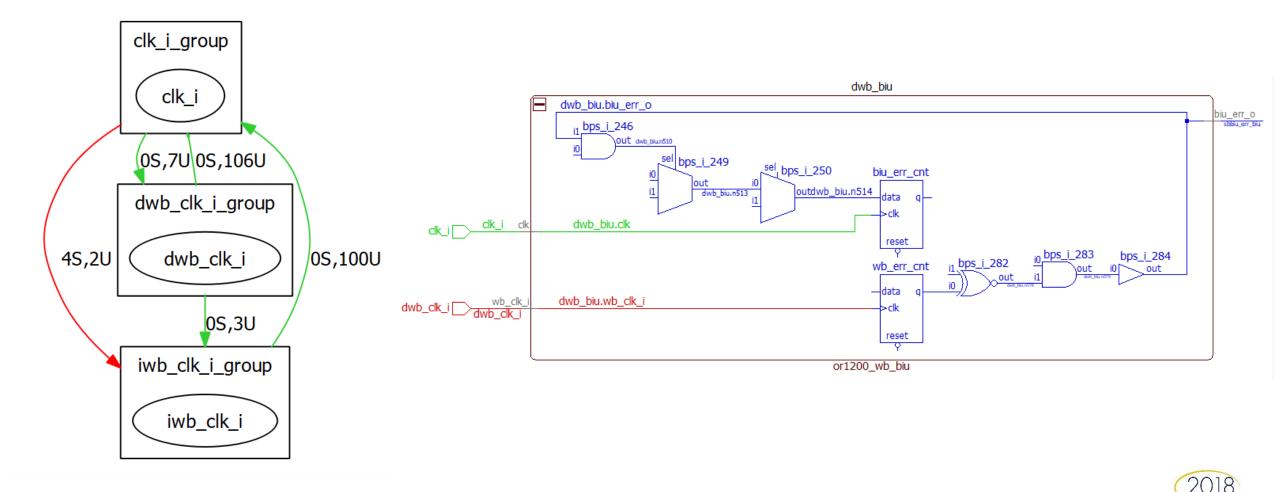

#### **RTL Analysis - CDC**

© Accellera Systems Initiative

DESIGN AND VERIFIC

CONFERENCE AND EXHIBITION

JROP

## Questions