#### 2022 DESIGN AND VERIFICATION<sup>™</sup> DVCDDN CONFERENCE AND EXHIBITION

#### UNITED STATES

#### Problematic Bi-Directional Port Connections: How Well is Your Simulator Filling the UPF LRM Void?

**Brandon Skaggs**

Cypress Semiconductor, An Infineon Technologies Company

## Agenda

- Motivation and Contributions of this Paper

- Common Bi-directional Port Issues

- Common Bi-directional Port Modeling Approaches

- Test Setup / Scenarios

- Results

- Analysis & Concluding Remarks

#### Motivation

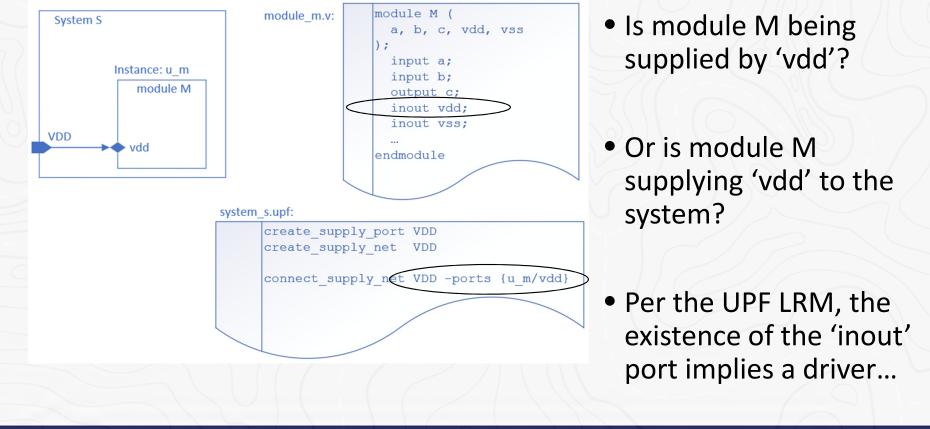

- The UPF LRM does not describe in detail the handling of bi-directional (inout) HDL port connections—leaving this open to interpretation of EDA tool vendors.

- How tools interpret proper behavior of bi-directional port semantics can have an impact on best practices for designing hierarchical power intent and writing effective models for simulation.

- An understanding of how contemporary commercial simulators handle these ports can inform best practices – and possibly suggest improvements in future IEEE 1801 revisions.

### Contribution

- This paper presents a systematic survey of the behavior of three contemporary power-aware digital simulators in handling bidirectional ports.

- This presentation will:

- Discuss two common bi-directional supply port modeling scenarios.

- Present three methods for modeling bi-directional connections—and review the support of each method by each simulator.

- Present the problem statement and test scenarios under study

- Review final results and concluding remarks—including possible enhancements to future UPF LRM revisions

## Common Bi-Directional Port Modeling Scenarios

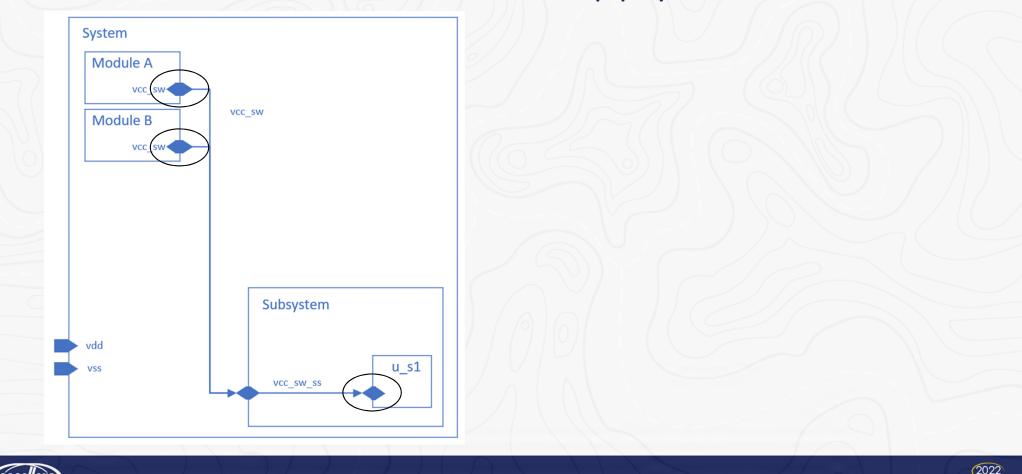

#### Scenario 1: Inout HDL to Supply Net

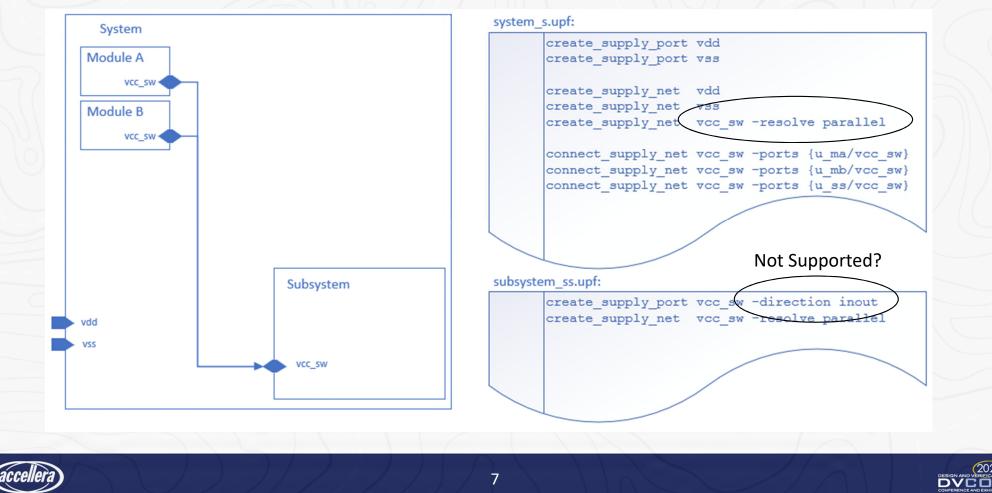

#### Scenario 2: Hierarchical Supply Nets

# **Bi-Di Port Modeling Approaches**

#### Method 1: Compiler Directives

```

module my macro ( a, b, c

`ifdef USE MACRO PG PINS

, vdd macro

, vss macro

`endif

);

input a;

input b;

output c;

`ifdef USE MACRO PG PINS

`ifdef USE MACRO IO PINS

inout vdd macro;

inout vss macro;

else

input vdd macro;

input vss macro;

`endif

else

supply1 vdd macro;

supply0 vss macro;

endif

. . .

```

- Well-defined Verilog behavior

- Can require modification of IPprovided models.

### Method 2: Custom Resolution Functions

- UPF provides several built-in resolution functions for resolving multiple-driver situations—which often occur when bi-directional ports are involved

- 'unresolved' resolves to UNDETERMINED if more than one source is connected/possible (default)

- 'one\_hot' allows multiple drivers, but only one can be active at a time.

- 'parallel' expects multiple drivers, and is only FULL\_ON if all sources are FULL\_ON

- 'parallel\_one\_hot' combination of 'one\_hot' and 'parallel': only one root supply can be active, but all derived supplies must be FULL\_ON for FULL\_ON resolution.

- For more complex interactions, a *SystemVerilog* function can be used instead to resolve the supply net in a custom manner.

#### Method 2: Custom Resolution Functions

function automatic supply net type MultiSourceResolution (input supply net type sources[]); supply net type ResolvedValue; int FullOnVolts = 0; int PartOnVolts = 0: int FullOnCount = 0: create supply net my sply net -resolve resolve::MultiSourceResolution int PartOnCount = 0: int UndetCount = 0: foreach (sources[i]) begin if (sources[i].state==UNDETERMINED) begin UndetCount++; end else if (sources[i].state==FULL ON) begin FullOnVolts += sources[i].voltage; FullOnCount++; end else if (sources[i].state==PARTIAL ON) begin PartOnVolts += sources[i].voltage; PartOnCount++; end end if (UndetCount > 0) begin ResolvedValue.state = UNDETERMINED; ResolvedValue.voltage = 0; // representing ¿unknown¿ end else if (FullOnCount > 0) begin ResolvedValue.state = FULL ON; ResolvedValue.voltage = FullOnVolts / FullOnCount; // average value end else if (PartOnCount > 0) begin ResolvedValue.state = PARTIAL ON; ResolvedValue.voltage = PartOnVolts / PartOnCount; // average value end else begin ResolvedValue.state = OFF: ResolvedValue.voltage = 0; // representing irrelevant end return (ResolvedValue); endfunction

- Well-defined SystemVerilog behavior

- UPF 3.x only

- No inherently-defined way of distinguishing the multiple sources being resolved

- No 'name' field to reference, so arguments must be kept track of positionally.

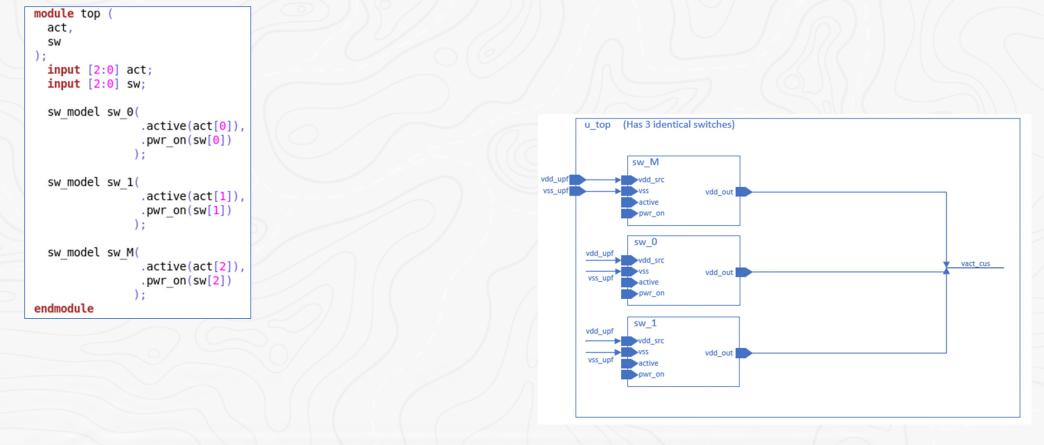

Rather than use the UPF-provided resolution functions, supply nets can be resolved in HDL directly by:

- 1. Intentionally removing/omitting 'normally resolved' UPF supply net connection

- 2. Including in testbench 'bound in' code that resolves the various HDL sources (using HDL values and signal strengths) to a single HDL resolution.

- 3. Connecting the resolved HDL signal to the UPF supply net within the UPF.

| <pre>act,<br/>sw<br/>);<br/>input [2:0] act;</pre>     | <pre>module bind_res (     v_inM,v_in1,v_in2, </pre>                                                                                                                                       |                    |                                                                                                                                                                                                                                 |                                                                                          |

|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| <pre>input [2:0] sw;<br/>sw_model sw_0(</pre>          | <pre>v_out ); input v_inM; input v_in1; input v_in2; output reg v_out;</pre>                                                                                                               |                    | u_top (Has 3 identical switches)                                                                                                                                                                                                |                                                                                          |

| sw_model sw_1(<br>.act<br>.pwr<br>);<br>sw_model sw_M( | <pre>always @(v_inM,v_in1,v_in2) begin     if (v_inM !== 1'bz) begin         v_out &lt;= v_inM;     end     else begin</pre>                                                               | vdd_upf<br>vss_upf | vdd_src<br>vss vdd_out<br>active<br>pwr_on<br>sw_0                                                                                                                                                                              |                                                                                          |

| act<br>.pwr<br>);                                      | <pre>if (v_in1 === 1'bx    v_in2 === 1'bx) begin     v_out &lt;= 'bx; end else if (v_in1 === 1'b1 &amp;&amp; v_in2 === 1'b1) begin     v_out &lt;= 'b1; end</pre>                          |                    | vdd_src<br>vss_upf vss vdd_out<br>active<br>pwr_on<br>vdd_upf                                                                                                                                                                   | vact_cus                                                                                 |

|                                                        | <pre>else begin     v_out &lt;= 1'b0;     end     end end end endmodule</pre>                                                                                                              |                    | vss_upf active<br>pwr_on                                                                                                                                                                                                        |                                                                                          |

|                                                        | <pre>sw<br/>);<br/>input [2:0] act;<br/>input [2:0] sw;<br/>sw_model sw_0(<br/>.act<br/>.pwr<br/>);<br/>sw_model sw_1(<br/>.act<br/>.pwr<br/>);<br/>sw_model sw_M(<br/>.act<br/>.pwr</pre> | <pre>act,</pre>    | <pre>act,<br/>sw<br/>);<br/>input [2:0] act;<br/>input [2:0] sw;<br/>);<br/>sw_model sw_0(<br/>.act<br/>.pwr<br/>);<br/>sw_model sw_1(<br/>.act<br/>.pwr<br/>);<br/>sw_model sw_1(<br/>.act<br/>.pwr<br/>);<br/>endmodule</pre> | <pre>act,<br/>sw<br/>);<br/>input [2:0] act;<br/>input [2:0] sw;<br/>w_undel sw_0(</pre> |

| <pre>input [2:0] act;<br/>input [2:0] sw;<br/>sw_model sw_0(</pre> | <pre>module bind_res (     v_inM,v_in1,v_in2,     v_out</pre>                                                                                                   | <pre># Connect input supplies to the bound module<br/>connect_logic_net vsrc1 -ports { sw_M/vdd_out1 }<br/>connect_logic_net vsrc2 -ports { sw_1/vdd_out1 }<br/>connect_logic_net vsrc3 -ports { sw_0/vdd_out1 }<br/># Connect resolved supply net to bound module<br/>connect_supply_net vact_cus -ports {u_binding/v_out } -vct SV_LOGIC2UPF<br/>u_top (Has 3 identical switches)</pre> |

|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| .act<br>.pwr<br>);                                                 | <pre>input v_in2;<br/>output reg v_out;</pre>                                                                                                                   | sw_M                                                                                                                                                                                                                                                                                                                                                                                      |

| <pre>sw_model sw_1(     .act     .pwr );</pre>                     | <pre>always @(v_inM,v_in1,v_in2) begin if (v_inM !== 1'bz) begin v_out &lt;= v_inM; end</pre>                                                                   | vdd_upf<br>vss_upf<br>vss_upf<br>vss_vss<br>vdd_out<br>vss_vss<br>vdd_out<br>vss_upf<br>vss_upf<br>vss_vss<br>vss<br>vss<br>vss<br>vss<br>vss<br>vss                                                                                                                                                                                                                                      |

| sw_model sw_M(<br>.act<br>.pwr<br>);                               | <pre>else begin     if (v_in1 === 1'bx    v_in2 ===         v_out &lt;= 'bx;     end     if (v_in1 === 1'bx    v_in2 ====================================</pre> | vss_upf active v_in2                                                                                                                                                                                                                                                                                                                                                                      |

| endmodule                                                          | <pre>else if (v_in1 === 1'b1 &amp;&amp; v_in         v_out &lt;= 'b1; end else begin         v out &lt;= 1'b0;</pre>                                            | vdd_upf<br>vdd_src<br>vzs vdd_out                                                                                                                                                                                                                                                                                                                                                         |

|                                                                    | end<br>end<br>enddule                                                                                                                                           | vss_upr active<br>pwr_on                                                                                                                                                                                                                                                                                                                                                                  |

|      | Signal Name                                                     | Values C1      | 0          | 50          | 100      |             | 150           |              | 200   | 25                  |

|------|-----------------------------------------------------------------|----------------|------------|-------------|----------|-------------|---------------|--------------|-------|---------------------|

| Ð    | test.u_top.vss_upf                                              | FULL_ON, OV    | OFF (      |             |          | FULL_C      | DN, 6V        |              |       | ( OFF               |

|      | test.u_top.vsrc1                                                | 0              |            |             |          |             |               |              |       |                     |

| -    | test.u_top.vsrc2                                                | z              |            |             |          |             |               |              |       |                     |

|      | test.u_top.vsrc3                                                | z              |            | $\frown$    |          | $\frown$    |               |              |       |                     |

| Đ    | test.u_top.vact_par F                                           | PARTIAL_ON, OV | OFF        |             |          |             | ARTIAL_ON, OV | /\           |       |                     |

| Ð    | test.u_top.vact_cus                                             | OFF            | UNDETERMI* | OFF FULL *I | OFF      | (FULL *)    | OFF           | (FULL*       | OFF   | TFULL Y OFF UNDET * |

| Ð    | <pre>f test.u_top.act[2:0]</pre>                                | 4              | ×          |             | 4        |             | X             |              |       |                     |

| Đ    | <pre>f test.u_top.sw[2:0]</pre>                                 | 0              | ×          | 0 X 4 X 0   | (1)3)2)0 | Х7Х         | 0 (4) 0 )     | 1 <u>(</u> 3 | 2 X 0 | <u> </u>            |

|      |                                                                 |                |            |             |          | test.u_top. | .u_binding    |              |       |                     |

|      | <pre>test.u_top.u_binding.v_inM</pre>                           | 0              |            |             |          |             |               |              |       |                     |

|      | <pre>test.u_top.u_binding.v_in1</pre>                           | z              |            |             |          |             |               |              |       |                     |

|      | 🚽 test.u_top.u_binding.v_in2                                    | z              |            |             |          |             |               |              |       |                     |

|      | <pre>test.u_top.u_binding.v_out</pre>                           | 0              |            |             |          |             |               |              |       |                     |

|      |                                                                 |                |            |             |          | test.ut     | op.sw_M       |              |       |                     |

|      | test.u_top.sw_M.src_valid                                       | 1              |            |             |          |             |               |              |       |                     |

|      | <pre>test.u_top.sw_M.active</pre>                               | 1              |            |             |          |             |               |              |       |                     |

|      | <pre>test.u_top.sw_M.pwr_on</pre>                               | 0              |            |             |          |             |               |              |       |                     |

|      | 🕒 test.u_top.sw_M.vdd_out1                                      | 0              |            |             |          |             |               |              |       |                     |

|      | <pre>test.u_top.sw_M.vdd_out2</pre>                             | Θ              |            |             |          |             |               |              |       |                     |

|      |                                                                 |                |            |             |          | test.u_t    | op.sw_0       |              |       |                     |

| - 11 | test.u_top.sw_0.src_valid                                       | 1              |            | $\sim$      |          | $\sim$      |               |              |       |                     |

| - 10 | <pre>test.u_top.sw_0.active</pre>                               | 0              |            |             |          |             |               |              |       |                     |

|      | <pre>test.u_top.sw_0.pwr_on</pre>                               | o              |            |             |          |             |               |              |       |                     |

|      | <pre>test.u_top.sw_0.vdd_out1</pre>                             | z              |            |             |          |             |               |              |       |                     |

|      | ➡ test.u_top.sw_0.vdd_out2                                      | z              |            |             |          |             |               |              |       |                     |

|      | test.u_top.sw_1<br>test.u_top.sw_1.src_valid                    | 4              |            |             |          | test.u_t    | op.sw_1       |              |       |                     |

| -    | <pre>test.u_top.sw_1.src_valid     test.u_top.sw_1.active</pre> | 1              |            |             |          |             |               |              |       |                     |

|      |                                                                 | 0              |            |             |          |             |               | \            |       |                     |

| -    | <pre>d test.u_top.sw_1.pwr_on</pre>                             | 0              |            |             |          |             |               | /            |       |                     |

|      | <pre>best.u_top.sw_1.vdd_out1</pre>                             | z              |            |             |          |             |               |              |       |                     |

|      | <pre>test.u_top.sw_1.vdd_out2</pre>                             | z              |            |             |          |             |               |              |       |                     |

|      |                                                                 |                | •          |             |          |             |               |              |       |                     |

| 0    | 50                                                              |                |            | 100         | 15       | 50          |               | 200          |       |                     |

# Test Setup & Results

#### Test Setup

- Default Behavior Tests:

- Scenario 1A: Test UPF to HDL bi-directional connections (used as inputs)

- Scenario 1B: Test UPF to HDL bi-directional connections (used as outputs)

- Scenario 2A: Test hierarchical supply connections within UPF (HDL ports declared as bi-directional)

- Scenario 2B: Test hierarchical supply connections within UPF (HDL ports declared with functional direction)

- Support for Modeling Approaches

- Modeling 1: Test support for using compiler directives

- Modeling 2: Test support for UPF custom resolution functions

- Modeling 3: Test support for HDL resolution functions

### Results: Scenario 1A

Test data showed that for the common scenario – where a bidirectional HDL port on a macro model was intended to be used as an input (sink) to the model, all three simulators resolved the port behavior as expected

### Results: Scenario 1B

The reverse scenario – where the bi-directional HDL signal was coming from a switch model and intended to be a source – showed mixed results.

| Simulator A                                                                                                      | Simulator B                                                                                        | Simulator C                                                                                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -Note that bi-di port is being<br>treated as an output<br>-Bi-di supply ports resolved<br>correctly to 'output'. | -HDL bi-di ports were treated as<br>inputs; UPF supply net connections<br>were treated as sources. | <ul> <li>-Warning that bi-di HDL port was<br/>being treated as an input.</li> <li>-HDL bi-di ports were treated as<br/>inputs; UPF supply net connections<br/>were treated as sources.</li> </ul> |

|                                                                                                                  |                                                                                                    |                                                                                                                                                                                                   |

|                                                                                                                  |                                                                                                    |                                                                                                                                                                                                   |

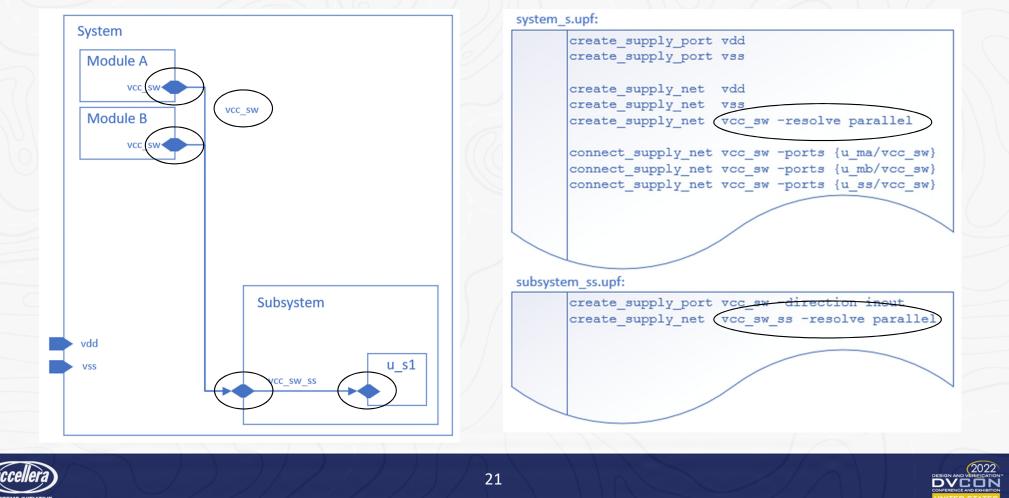

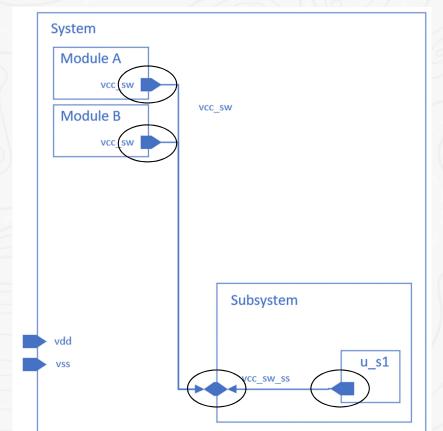

#### Scenario 2A: Hierarchical Supply Net

#### Results: Scenario 2A – Hier UPF, bi-di HDL ports

- Could only test Simulator A (B & C treated as inputs)

- For Simulator A, the results were as expected; the behavior for HDL 'inout' ports matched expectations

- Warning that 'inout' for UPF port direction is not supported...?

- Top-level supply net resolved as expected—only FULL\_ON when all hierarchical supplies were on.

- Submodule supply net showed PARTIAL\_ON as expected when only top-level supplies were on.

## Scenario 2A: Hierarchical Supply Net

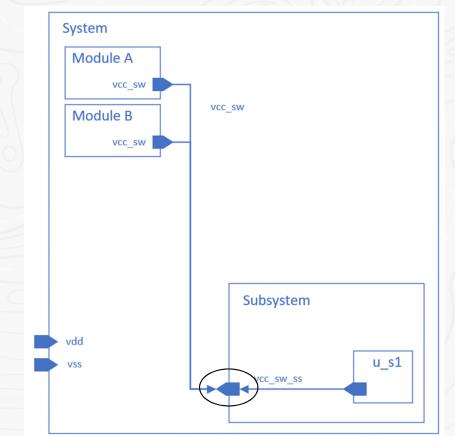

#### Scenario 2B: Hierarchical Supply Net

- System-level supply net (vcc\_sw) has three drivers; it should be PARTIAL\_ON when any one is on and only FULL\_ON when all three are FULL\_ON.

- Subsystem-level supply net (vcc\_sw\_ss) should exactly mimic this behavior.

#### Scenario 2B: Hier Supply Net, 'out' UPF port

- System-level net (vcc\_sw) still retains three drivers and 'parallel' resolution expectations...

- Subsystem-level net (vcc\_sw\_ss) now has only one driver (u\_s1), so it should not be influenced by system-level drivers...

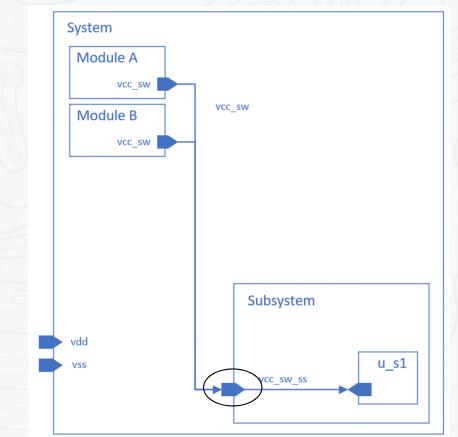

#### Scenario 2B: Hier Supply Net, 'in' UPF port

- System-level supply net (vcc\_sw) should not depend on subsystem net state for resolution.

- Subsystem-level supply net (vcc\_sw\_ss) should see two drivers (same as Scenario 2A)

#### Results: Scenario 2B – Hier UPF, uni-di HDL ports

- The results showed that all three simulators modelled the proper behavior of the system supply net when it was declared 'inout' showing FULL\_ON only when all contributing supplies were on.

- However, all three simulators exhibited slightly different behavior when dealing with UPF supply port connections that are hierarchically connected, and all three exhibited slightly errant behavior based on an expectation from the LRM.

## Results: Scenario 2B

|   | Simulator A                          | Simulator B                        | Simulator C                         |

|---|--------------------------------------|------------------------------------|-------------------------------------|

|   | Same results as Scenario 2A:         | -Top-level supply net resolved as  | -Top-level supply net resolved as   |

| 9 | -Top-level supply net resolved as    | expected—only FULL_ON when all     | expected—only FULL_ON when all      |

|   | expected—only FULL_ON when all       | hierarchical supplies were on.     | hierarchical supplies were on.      |

|   | hierarchical supplies were on.       | -Submodule supply net showed       | -Submodule supply net showed        |

| ) | -Submodule supply net showed         | PARTIAL_ON when only top-level     | PARTIAL_ON when only top-level      |

|   | PARTIAL_ON when only top-level       | supplies were on.                  | supplies were on.                   |

| _ | supplies were on.                    | -Unusual results were seen when    | -Unusual results were seen when     |

| - | -Unusual results were seen when      | hierarchical UPF port was declared | hierarchical UPF port was declared  |

| 2 | hierarchical UPF port was declared   | as 'out': subsystem goes           | as 'out' or 'in': results match the |

|   | as 'out': subsystem goes             | PARTIAL_ON when system supplies    | 'inout' port declaration case.      |

|   | PARTIAL_ON when system supplies      | are active.                        |                                     |

|   | are active.                          | -Unusual results were seen when    |                                     |

|   | -Unusual results were seen when      | hierarchical UPF port was declared |                                     |

|   | hierarchical port was declared 'in': | as 'in': subsystem and system nets |                                     |

| - | subsystem supply never goes          | go PARTIAL_ON as soon as parent    |                                     |

|   | FULL_ON                              | domain is valid.                   |                                     |

### Results: Modeling 1 – Compiler directives

Compiler directives are well supported by all three simulators under consideration, and there were no issues using these to get the expected behavior.

## Results: Modeling 2 – UPF resolution

- Support for user-defined resolution functions was somewhat uneven, with all three simulators exhibiting slightly different behavior.

- Simulator A was the only one to accept the example from the IEEE-1801 specification as written.

| Simulator A                                      | Simulator B                                                                 | Simulator C                                                                                                          |

|--------------------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| Supported IEEE-1801 example resolution function. | Only allows resolution between<br>two supply nets – task (not<br>function). | Allows function definition only via<br>vendor-provided IEEE-1801 custom<br>extension, limited resolution<br>options. |

|                                                  |                                                                             |                                                                                                                      |

|                                                  |                                                                             |                                                                                                                      |

## Results: Modeling 3 – HDL Resolution

- When using HDL resolution functions, the results were mostly positive; all three simulators supported the basic functions of binding a resolution module via a testbench and resolved HDL conflicts as expected.

- However, only Simulator A supported doing this on HDL nets defined and connected within the UPF with 'create\_logic\_net' and 'connect\_logic\_net' commands.

- Simulators B and C required the nets to be defined within the HDL.

- This limitation in Simulators B and C seems arbitrary and out of sync with the expectations of the UPF LRM to allow the creation of new logic nets when needed.

## Analysis & Conclusions

### Analysis

- The UPF/HDL resolution vectors 'vct' do not seem to be used for resolving supply net drive direction—in spite of the fact that they are written and applied with a source/destination direction in mind.

- Simulator A was the only simulator to allow bi-directional HDL ports to be connected and used as outputs; the other two defaulted the ports to 'inputs' in spite of the context of what they were being connected to. It was also the only simulator to fully support the example IEEE1801 custom resolution function as written, and it was the only simulator to allow binding connections with UPF-provided logic nets.

### Analysis

- UPF custom resolution functions are difficult to apply because supply nets do not contain a 'name' or 'id' that would allow a user to distinguish between a set of supplies to resolve.

- The resulting supply sources of 'supply\_net\_type' appear only with state and voltage information, and the UPF LRM does not provide an explicit definition about the order that supply net connections are maintained in when multiple 'connect\_supply\_net' commands could each make multiple supply net connections each.

#### Conclusions

- The default treatment of inout HDL ports and UPF hierarchical port connections vary across EDA vendors...

- Basic support of common bi-directional port modeling function is uneven across the three major EDA simulators...

- Future UPF revisions should seek to take advantage of 'vct' drive direction information when provided to determine which side of a supply net is the source.

- Future UPF revisions should make this ordering of resolution function supplies explicit, or future supply\_net\_type definitions should include a name field that is populated when nets are declared.

# Questions?

Thank you for your attention!