# Problematic Bi-Directional Port Connections: How Well Is Your Simulator Filling the UPF LRM Void?

Brandon Skaggs Cypress Semiconductor, An Infineon Technologies Company 201. E. Main Street, Suite 500A Lexington, KY 40508 brandon.skaggs@infineon.com

Abstract—The UPF LRM does not describe in detail the handling of bi-directional (inout) HDL port connections, and this leaves the handling of commonly-used connections open to the interpretation of EDA vendors. In this paper we present two common bi-directional supply port connections that are often the source of unexpected corruption before discussing three possible methods for working around them. We then examine how well each of the three main EDA simulators support the initial scenario and the proposed workarounds. Finally, possible future enhancements to the UPF LRM to ensure well-defined behavior across all tools is discussed.

# I. INTRODUCTION

The IEEE1801 Standard for Design and Verification of Low-Power, Energy-Aware Electronic Systems commonly known as the Unified Power Format (UPF) standard—provides a framework for describing the power intent and supply distribution for both implementation and power-aware verification tools. Power domains, supply connectivity, and expected (or invalid) power states can be defined in a way to direct synthesis tools to select cell libraries (typically provided in *Liberty* format) appropriate for the design, LINTing tools to verify that implementation is achievable, and layout tools to properly implement the intent. Functional power-aware simulation (which often inserts or substitutes functional, power-aware behavioral models for *Liberty* cells/macros) can also use the UPF power intent specification to verify correct functional behavior along with power state transitions and correct isolation and retention during power-down.

However, the behavior of bi-directional HDL ports commonly used to model supplies within power-aware behavioral models are not well defined by even the most recent UPF LRM specifications. This leaves the behavior of these ports (and their interaction with connected supply ports) up to the implementation chosen by the EDA vendor.

This paper presents two common 'problematic' bi-directional port modeling issues found within power-aware simulations, describes possible methods for modeling these connections, and tests the support for each of these methods within the most widely-used power-aware simulators in the market. Finally, enhancements to future UPF LRM revisions are discussed—enhancements that would align expectations to a common, well-defined behavior.

## A. Motivation & Contributions of this Paper

How tools interpret proper behavior of bi-directional port semantics can have an impact on best practices for designing hierarchical power intent and writing effective models for simulation. This paper presents a systematic survey of the behavior of contemporary EDA functional, digital simulators—in an area where the IEEE specification is not explicit—in order to inform these best practices and suggest improvements in future IEEE 1801 revisions.

## B. Organization of this Paper

We begin our discussion by describing some common areas where bi-directional ports are used within poweraware simulations, followed by a presentation of several common methods for modeling bi-directional ports and their proper resolution. Data is then presented on the default behavior of the three major EDA simulators within these common scenarios and modeling approaches—discussing the results and any issues encountered. Finally, the paper concludes by discussing items for future study.

### **II. KEY TERMS**

| Unified Power Format (UPF) | IEEE standard format for describing intended design power intent abstractly      |

|----------------------------|----------------------------------------------------------------------------------|

| Power Management           | Pertaining to the modulation of supply for the purpose of reducing circuit power |

| Power-aware Simulation     | Digital simulation where power-related behavior is modelled.                     |

| Supply Net type            | Object type representing a supply with a state and voltage component             |

| Source                     | Object providing power to a sink                                                 |

| Sink                       | Object being driven by a source                                                  |

## III. COMMON BI-DIRECTIONAL PORT MODELING SCENARIOS

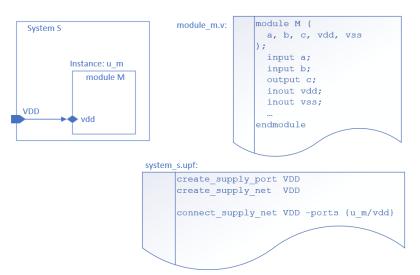

Consider the common scenario where a connection is made between a power-aware simulation model and a UPF supply net, as presented in Figure 1. Since supply voltages are often treated within Verilog as logic ports with 'inout' port direction, this creates a classic 'supply net to HDL inout' connection within the simulation.

Figure 1. Typical Bi-Directional HDL to Supply Net Connections (Scenario 1)

From the connection itself, it is not clear within the system S whether the behavioral model of module M is meant to be a source or sink for the connected supply net VDD. If the 'vdd' HDL port on module M is meant to model an input supply, it wouldn't be expected to drive the connected supply net; however, if module M were modeling a power switch, and the HDL port was representing a switched output, then it would be a source and not a sink on the supply net. Per the UPF LRM, the existence of an 'inout' port implies the latter (a source driving the supply net), but the common scenario is the former (a simple sink being driven by the supply). This often creates a 'multiple driver' error and corruption on the supply net—when corruption on the supply net is not what would actually happen within the system.

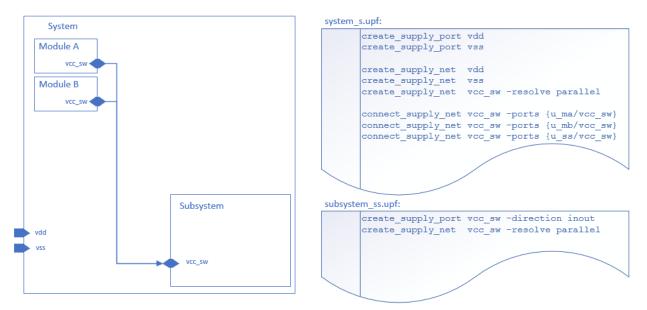

This scenario can be extended to examine a similar resolution concern when 'inout' UPF supply ports are used to describe connections within a hierarchical power intent definition. Consider the scenario in Figure 2 where a supply net is driven by several power switches – distributed among submodules whose power intent is described independently and referenced hierarchically.

Figure 2. Example of a Hierarchical Supply Connection Requiring 'inout' Supply Ports (Scenario 2)

In this example, the resolution of the  $vcc\_sw$  supply net can only be obtained if the state of the submodule's power switch can be reflected onto the net through the 'inout' supply port; however, some simulators do not fully support 'inout' supply ports, and instead model them as the default 'input' direction. This can create challenges when hierarchical abstraction and re-use are leveraged within the chosen verification methodology. Other methods for resolving the state of these parallel networks is required, and they are the topic of the next section.

#### IV. METHODS FOR MODELING BI-DIRECTIONAL PORTS

There are several commonly-used methods for handing problematic bi-directional supply ports within simulation; this paper will discuss three methods, discuss the advantages and disadvantages of each, and test compatibility among the three most commonly-used simulators.

## A. Using Compiler Directives to Modify HDL Port Direction

This method involves defining the behavioral model port directions based on compiler directives in order to select the most appropriate unidirectional port direction when the model is compiled for power-aware simulation. Since it uses well-supported pre-compiler syntax and directives to completely avoid the bi-directional situations discussed in Section III, this approach is often the most straightforward and widely-supported approach. However, it requires modification of IP-provided models—which may not be an option for cases where third-party IP are used. An example of a macro written with compiler directives to manage port direction is given in Figure 3.

#### B. Defining Supply Net Custom Resolution Functions (UPF 3.x)

IEEE1801-2015 (commonly referred to as UPF 3.0) revised the UPF LRM to add the ability to create custom supply net resolution function where the pre-defined resolution functions (*unresolved*, *one\_hot*, *parallel*, and *parallel\_one\_hot*) were not sufficient to resolve more complex supply connections. By creating the capability to define resolution rules that could be unique for any given supply net, conflicts caused by bi-directionally-driven supply nets could potentially be resolved by examining the states of all drivers and assigning an appropriate value for the resolved net based on the context.

```

module my_macro ( a, b, c

`ifdef USE MACRO PG PINS

, vdd_macro

, vss macro

`endif

);

input a;

input b;

output c;

`ifdef USE MACRO PG PINS

`ifdef USE_MACRO_IO_PINS

inout vdd macro;

inout vss macro;

else

input vdd_macro;

input vss_macro;

endif

else

supply1 vdd macro;

supply0 vss_macro;

endif

. . .

```

Figure 3. Example of Using Compiler Directives to Resolve Bi-Directional Ports

An example of a custom resolution function from the IEEE1801-2015 specification is presented in Figure 4. Figure 5 shows how this custom function could be referenced within the UPF supply net declaration.

```

function automatic supply_net_type MultiSourceResolution (input supply_net_type sources[]);

supply_net_type ResolvedValue;

int FullOnVolts = 0;

int PartOnVolts = 0:

int FullOnCount = 0;

int PartOnCount = 0;

int UndetCount = 0;

foreach (sources[i]) begin

if (sources[i].state==UNDETERMINED) begin

UndetCount++;

end

else if (sources[i].state==FULL_ON) begin

FullOnVolts += sources[i].voltage;

FullOnCount++:

end

else if (sources[i].state==PARTIAL_ON) begin

PartOnVolts += sources[i].voltage;

PartOnCount++;

end

end

if (UndetCount > 0) begin

ResolvedValue.state = UNDETERMINED;

ResolvedValue.voltage = 0; // representing ¿unknown¿

end

else if (FullOnCount > 0) begin

ResolvedValue.state = FULL ON;

ResolvedValue.voltage = FullOnVolts / FullOnCount; // average value

end

else if (PartOnCount > 0) begin

ResolvedValue.state = PARTIAL ON;

ResolvedValue.voltage = PartOnVolts / PartOnCount; // average value

end

else begin

ResolvedValue.state = OFF;

ResolvedValue.voltage = 0; // representing irrelevant

end

return (ResolvedValue);

endfunction

```

Figure 4. Custom Resolution Function from IEEE 1801-2015, Section 6.24.3

create supply net vact cus -resolve resolve::MultiSourceResolution

Figure 5. Referencing a Custom Resolution Function from a User-Defined Package

## C. Resolving Supply Net Using HDL Resolution Functions

This approach involves intentionally removing UPF connections for supply nets that have problematic HDL bidirectional connections—replacing them with testbench code that monitors changes in the source supplies and then reflects the desired resolution on the HDL model nets and supply nets as appropriate. Since the testbench-provided code intercepts the possible drivers, the built-in HDL resolution function of the testbench language (Verilog, SystemVerilog, or VHDL) can be leveraged to resolve the supply net state before it is driven onto the supply net by the testbench – which is now its only source.

One key advantage to this approach (over using the UPF native supply net resolution functions or writing a custom resolution function) is the larger number of net values that can be used. Whereas UPF has only UNDETERMINED, OFF, PARTIAL\_ON, and FULL\_ON states for supply net resolution, HDL signals (in addition to 'X', '0', and '1' states) add signal values for high-impedance ('Z') and various signal strengths ('W', 'L', 'H', 'strong', 'weak', 'pull', etc.) – all with well-defined resolution functions that can be used to model priority or combinations of acceptable values. By giving different contributors to the supply net resolution different HDL strengths, a higher granularity of control is available.

Another key component of this approach is that it can be achieved by 'binding' resolution functions from within testbench code – without requiring changes within the design under test to accommodate this modeling.

Let's look at an example of how HDL resolution could be performed. In this example, a system where the active supply net (vact\_cus) can be driven by a single external supply (sw\_M), or—if the supply is absent (driven 'Z' by sw\_M)—it can be switched on internally by a series of internal switches (sw\_1 and sw\_2) and resolved as a parallel net. Note that in this scenario, there is no pre-defined resolution function for 'vact\_cus' that is appropriate.

Rather than connect the outputs of all three switches to 'vact\_cus' and provide a resolution function, the outputs of the switches are connected to a module that is added via a 'bind' statement from the testbench. This module contains the resolution function that allows the switch output to follow 'sw\_M' if it is driven, but to follow the state of both 'sw\_1' and 'sw\_2' if it isn't. A supply net connection within the UPF file makes the final translation and assignment from HDL to supply\_net\_type. Figure 6 shows the relevant HDL and UPF statements, and Figure 7 shows the resulting waveform.

| <pre>module test();<br/>reg [2:0] active;<br/>reg [2:0] sw_on;<br/>int s;<br/>top u_top(<br/>.act(active),<br/>.sw(sw_on)<br/>);<br/>bind top bind_res u_binding(<br/>.v_in1(vsrc1),<br/>.v_in2(vsrc2),<br/>.v_in4(vsrcM)<br/>};</pre> | <pre>module bind_res (     v_inM,v_in1,v_in2,     v_out );     input v_inM;     input v_in1;     input v_in2;     output reg v_out;     initial     \$monitor("t:%10d - b:%b,%b,o=%b",\$time,v_inM,v_in1,v_in2,v_out);     always @(v_inM,v_in1,v_in2)     begin     if (v_inM !== 1'b2) begin     v_out &lt;= v_inM;     end     else bedin </pre> |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre># Switched voltage busses create logic net vsrc1;</pre>                                                                                                                                                                           | <pre>if (v_inl === 1'bx    v_in2 === 1'bx) begin v out &lt;= 'bx;</pre>                                                                                                                                                                                                                                                                             |

| create logic net vsrc2;                                                                                                                                                                                                                | end                                                                                                                                                                                                                                                                                                                                                 |

| create logic net vsrc3;                                                                                                                                                                                                                | else if (v_in1 === 1'b1 && v_in2 === 1'b1) begin                                                                                                                                                                                                                                                                                                    |

| create_supply_net vact_cus                                                                                                                                                                                                             | v_out <= 'b1;                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                        | end                                                                                                                                                                                                                                                                                                                                                 |

| # Connect input supplies to the bound module                                                                                                                                                                                           | else begin                                                                                                                                                                                                                                                                                                                                          |

| <pre>connect_logic_net vsrcl -ports { sw 1/vdd_out1 }</pre>                                                                                                                                                                            | v_out <= 1'b0;<br>end                                                                                                                                                                                                                                                                                                                               |

| <pre>connect_logic_net vsrc2 -ports { sw 2/vdd_out1 } connect logic_net vsrcM -ports { sw M/vdd_out1 }</pre>                                                                                                                           | end                                                                                                                                                                                                                                                                                                                                                 |

| connect_togic_net vsich -points { sw_h/vdu_outi }                                                                                                                                                                                      | end                                                                                                                                                                                                                                                                                                                                                 |

| <pre># Connect resolved supply net to bound module connect_supply_net vact_cus -ports {u_binding/v_out } -vct SV_LOGIC2UPF</pre>                                                                                                       | endmodule                                                                                                                                                                                                                                                                                                                                           |

Figure 6. Resolving UPF Supply Net Drivers using HDL Resolution Functions

|   | Signal Name                                          | Values C1      | 0          | 50          | 100      | )               | 150       | 200              | 250                 |

|---|------------------------------------------------------|----------------|------------|-------------|----------|-----------------|-----------|------------------|---------------------|

| • | test.u_top.vss_upf                                   | FULL_ON, OV    | OFF X      |             |          | FULL_ON, OV     |           |                  | ( OFF               |

|   | test.u_top.vsrc1                                     | Θ              |            |             |          |                 |           |                  |                     |

|   | test.u_top.vsrc2                                     | z              |            |             |          |                 |           |                  |                     |

|   | test.u_top.vsrc3                                     | z              |            |             |          |                 |           |                  |                     |

|   | test.u_top.vact_par                                  | PARTIAL_ON, 0V | OFF        |             |          | PARTI           | AL_ON, OV |                  |                     |

|   | test.u_top.vact_cus                                  | OFF            | UNDETERMI* | OFF (FULL*) | OFF      | )FULL*)         | OFF       | )FULL*) OFF      | (FULL*) OFF (UNDET* |

|   | <pre>d test.u_top.act[2:0]</pre>                     | 4              | x          |             | 4        | X               |           | 3                |                     |

| • | test.u_top.sw[2:0]                                   | 0              | x          | 0 (4 ) 0    | (1)3(2)0 | χ7χο            | (4) 0     | <u>1 1 3 2 0</u> | <u>(7)</u> 0        |

|   | test.u_top.u_binding                                 |                |            |             |          | test.u_top.u_bi | .nding    |                  |                     |

|   | 📲 test.u_top.u_binding.v_inM                         | 0              |            |             |          |                 |           |                  |                     |

|   | test.u_top.u_binding.v_in1                           | z              |            |             |          |                 |           |                  |                     |

|   | test.u_top.u_binding.v_in2                           | z              |            |             |          |                 |           |                  |                     |

|   | test.u_top.u_binding.v_out                           | 0              |            |             |          |                 |           |                  |                     |

|   | test.u_top.sw_M<br>test.u_top.sw_M.src_valid         |                |            |             |          | test.u_top.s    | #_M       |                  |                     |

|   | d test.u_top.sw_M.src_valid d test.u_top.sw_M.active | 1              |            |             |          |                 |           |                  |                     |

|   |                                                      | 1              |            |             |          |                 |           |                  |                     |

|   | <pre>test.u_top.sw_M.pwr_on</pre>                    | 0              |            |             |          |                 |           |                  |                     |

|   | 🕒 test.u_top.sw_M.vdd_out1                           | 0              |            |             |          |                 |           |                  |                     |

| E | <pre>test.u_top.sw_M.vdd_out2 test.u_top.sw_0</pre>  | •              |            |             |          | test.u_top.s    |           |                  |                     |

|   | test.u_top.sw_0<br>test.u_top.sw 0.src valid         | 1              |            |             |          | Lest.u_top.s    | w_0       |                  |                     |

|   | <pre>test.u_top.sw_0.active</pre>                    |                |            |             |          |                 |           |                  |                     |

|   | test.u_top.sw_0.pwr_on                               | 0              |            |             |          |                 |           |                  |                     |

|   | B test.u_top.sw_0.vdd_out1                           | 7              |            |             |          |                 |           |                  |                     |

|   | test.u_top.sw_0.vdd_out2                             | 7              |            |             |          |                 |           |                  |                     |

|   | test.u_top.sw_1                                      |                |            |             |          | test.u_top.s    | d 1       |                  |                     |

|   | test.u_top.sw_1.src_valid                            | 1              |            |             |          |                 | -         |                  |                     |

|   | <pre>test.u_top.sw_1.active</pre>                    | 0              |            |             |          |                 |           |                  |                     |

|   | <pre>test.u_top.sw_1.pwr_on</pre>                    | 0              |            |             |          |                 |           |                  |                     |

|   | test.u_top.sw_1.vdd_out1                             | z              |            |             |          |                 |           |                  |                     |

|   | <pre>best.u_top.sw_1.vdd_out2</pre>                  | z              |            |             |          |                 |           |                  |                     |

|   |                                                      |                |            |             |          |                 |           |                  | í.                  |

| 0 |                                                      | [1]            | [•]        | 100         |          | 450             |           | 000              | 1                   |

| 0 | 50                                                   |                |            | 100         |          | 150             |           | 200              | . 25                |

Figure 7. Resolved Supply Nets with Priority

From the waveform, you can see how 'vact\_cus' is FULL\_ON whenever sw\_M is on; or, if sw\_M is disconnected (Hi-Z), 'vact\_cus' is FULL\_ON when both sw\_1 and sw\_2 are on...

# V. TEST SCENARIOS

In order to provide a picture of EDA tool support for bi-directional ports, the behavior of the three most commonly-used power-aware simulators in the industry were tested for default behavior within the scenarios in Section III—for default behavior and for support of the as well as for the modeling methods described in Section IV.

Default Behavior:

Scenario 1A: Test UPF to HDL bi-directional connections (used as inputs)

Scenario 1B: Test UPF to HDL bi-directional connections (used as outputs)

Scenario 2A: Test hierarchical supply connections within UPF (HDL ports declared as bi-directional)

Scenario 2B: Test hierarchical supply connections within UPF (HDL ports declared with functional direction)

Support for Modeling Approaches:

Modeling 1: Test support for using compiler directives

Modeling 2: Test support for UPF custom resolution functions

Modeling 3: Test support for HDL resolution functions

Each simulator was randomly assigned a designator A, B, or C, and the results of testing with each are described in Section VI.

## VI. TEST RESULTS

Scenario 1A: Test UPF to HDL bi-directional connections (used as inputs)

Test data showed that for the common scenario – where a bi-directional HDL port on a macro model was intended to be used as an input (sink) to the model, all three simulators resolved the port behavior as expected.

| Simulator A                       | Simulator B                  | Simulator C                      |

|-----------------------------------|------------------------------|----------------------------------|

| -Warning that resolution (vct)    | -Bi-di supply ports resolved | -Warning that the bi-directional |

| functions could not be applied to | correctly to 'input'.        | HDL ports would be treated as    |

| HDL bi-di ports.                  |                              | inputs.                          |

| -Bi-di supply ports resolved      |                              | -Bi-di supply ports resolved     |

| correctly to 'input'.             |                              | correctly to 'input'.            |

Scenario 1B: Test UPF to HDL bi-directional connections (used as outputs)

The reverse scenario – where the bi-directional HDL signal was coming from a switch model and intended to be a source – showed mixed results. Simulators B and C treated the connected supply nets the same as in Scenario 1A and the connected bi-directional HDL ports as sinks. Only Simulator A was able to determine that the bi-directional port was being driven by the HDL and modeled the appropriate behavior.

| Simulator A                            | Simulator B                        | Simulator C                        |

|----------------------------------------|------------------------------------|------------------------------------|

| -Note that bi-di port is being treated | -HDL bi-di ports were treated as   | -Warning that bi-di HDL port was   |

| as an output                           | inputs; UPF supply net connections | being treated as an input.         |

| -Bi-di supply ports resolved           | were treated as sources.           | -HDL bi-di ports were treated as   |

| correctly to 'output'.                 |                                    | inputs; UPF supply net connections |

|                                        |                                    | were treated as sources.           |

Scenario 2A: Test hierarchical supply connections within UPF (HDL ports declared as bi-directional)

Because of the findings in Scenario 1B—that HDL bi-directional ports were always treated as inputs by two of the three simulators—it was not possible to model Scenario 2A with Simulators B and C and see any reasonable behavior for the system model where a submodule with an 'inout' UPF port drove onto a system supply net.

For Simulator A, the results were mixed; the behavior for 'inout' ports matched expectations; however, unusual results were seen when the submodule / hierarchical UPF port was declared as 'in' or 'out' mode.

| Simulator A                        | Simulator B                 | Simulator C                 |

|------------------------------------|-----------------------------|-----------------------------|

| -Warning that 'inout' for UPF port | Test scenario not supported | Test scenario not supported |

| direction is not supported.        | (See Scenario 1B above)     | (See Scenario 1B above)     |

| -Top-level supply net resolved as  |                             |                             |

| expected—only FULL_ON when all     |                             |                             |

| hierarchical supplies were on.     |                             |                             |

| -Submodule supply net showed       |                             |                             |

| PARTIAL_ON as expected when        |                             |                             |

| top-level supplies were on.        |                             |                             |

| -Unusual results were seen when    |                             |                             |

| hierarchical UPF port was declared |                             |                             |

| as 'out': subsystem goes           |                             |                             |

| PARTIAL_ON when top-level          |                             |                             |

| supplies are enabled.              |                             |                             |

| -Unusual results were seen when    |                             |                             |

| hierarchical UPF port was declared |                             |                             |

| as 'in': subsystem never goes      |                             |                             |

| FULL_ON.                           |                             |                             |

Scenario 2B: Test hierarchical supply connections within UPF (HDL ports declared with functional direction)

This scenario was created to test the hierarchical UPF port connections after addressing the HDL port issues seen in Scenario 2A. The results showed that all three simulators modelled the proper behavior of the system supply net - showing FULL ON only when all contributing supplies were on.

However, all three simulators exhibited slightly different behavior when dealing with UPF supply port connections that are hierarchically connected, and **all three exhibited slightly errant behavior based on an expectation from the LRM**.

| Simulator A                  | Simulator B                         | Simulator C                         |

|------------------------------|-------------------------------------|-------------------------------------|

| Same results as Scenario 2A. | -Top-level supply net resolved as   | -Top-level supply net resolved as   |

|                              | expected—only FULL_ON when all      | expected—only FULL_ON when all      |

|                              | hierarchical supplies were on.      | hierarchical supplies were on.      |

|                              | -Submodule supply net showed        | -Submodule supply net showed        |

|                              | PARTIAL_ON when top-level           | PARTIAL_ON when top-level           |

|                              | supplies were on.                   | supplies were on.                   |

|                              | -Unusual results were seen when     | -Unusual results were seen when     |

|                              | hierarchical UPF port was declared  | hierarchical UPF port was declared  |

|                              | as 'out': net behaves as if it were | as 'out' or 'in': results match the |

|                              | 'inout' and goes PARTIAL_ON         | 'inout' port declaration case.      |

|                              | when system supplies are enabled.   | _                                   |

|                              | -Unusual results were seen when     |                                     |

|                              | hierarchical UPF port was declared  |                                     |

|                              | as 'in': subsystem and system nets  |                                     |

|                              | go PARTIAL_ON as soon as parent     |                                     |

|                              | domain is valid.                    |                                     |

Modeling 1: Test support for using compiler directives

As described in Section 4A above, compiler directives are well supported by all three simulators under consideration, and there were no issues using these to get the expected behavior.

| Simulator A                          | Simulator B                          | Simulator C                          |

|--------------------------------------|--------------------------------------|--------------------------------------|

| Full support for compiler directives | Full support for compiler directives | Full support for compiler directives |

# <u>Modeling 2</u>: Test support for UPF custom resolution functions

Support for user-defined resolution functions was somewhat uneven, with all three simulators exhibiting slightly different behavior. Simulator A was the only one to accept the example from the IEEE-1801 specification as written.

Simulator B would only allow custom resolution sequences written as tasks—and documentation confirmed that **resolution was limited to only two input supply nets**. This restriction seems arbitrary and likely to make this vendor's implementation unreasonable for real applications.

Simulator C supported some modifications to the standard supply net resolution functions via tool-specific extensions to the UPF commands, and only a very limited scope of changes. There was no capability to define a generic resolution function within an HDL package.

| Simulator A                 | Simulator B                        | Simulator C                            |

|-----------------------------|------------------------------------|----------------------------------------|

| Supported IEEE-1801 example | Only allows resolution between two | Allows function definition only via    |

| resolution function.        | supply nets – task (not function). | vendor-provided IEEE-1801 custom       |

|                             |                                    | extension, limited resolution options. |

Modeling 3: Test support for HDL resolution functions

When using HDL resolution functions, the results were mostly positive; all three simulators supported the basic functions of binding a resolution module via a testbench and resolved HDL conflicts as expected. However, only Simulator A supported doing this on HDL nets defined and connected within the UPF with 'create\_logic\_net' and 'connect\_logic\_net' commands; Simulators B and C required the nets to be defined within the HDL.

Since this approach attempts to replace supply net connections normally made via UPF with logic net connections, the preferred location for creating these connections would be within UPF – rather than forcing a change to the HDL under test. This limitation in Simulators B and C seems arbitrary and out of sync with the expectations of the UPF LRM to allow the creation of new logic nets when needed.

| Simulator A                       | Simulator B                         | Simulator C                         |

|-----------------------------------|-------------------------------------|-------------------------------------|

| Binding worked as expected; logic | Binding won't work on UPF-created   | Binding won't work on UPF-created   |

| nets created and connected within | logic nets. If HDL nets are created | logic nets. If HDL nets are created |

| UPF.                              | in original RTL, binding works as   | in original RTL, binding works as   |

|                                   | expected.                           | expected.                           |

## VII. ANALYSIS & CONCLUSIONS

Some other general observations can be made from the above results:

- The UPF/HDL resolution vectors 'vct' do not seem to be used for resolving drive direction—in spite of the fact that they are written and applied with a source/destination direction in mind. Future UPF revisions should seek to take advantage of this information when provided to determine which side of a supply net is the source.

- Simulator A was the only simulator to allow bi-directional HDL ports to be connected and used as outputs; the other two defaulted the ports to 'inputs' in spite of the context of what they were being connected to. It was also the only simulator to fully support the example IEEE1801 custom resolution function as written, and it was the only simulator to allow binding connections with UPF-provided logic nets.

- UPF custom resolution functions are difficult to apply because supply nets do not contain a 'name' or 'id' that would allow a user to distinguish between a set of supplies to resolve. The resulting supply sources of 'supply\_net\_type' appear only with state and voltage information, and the UPF LRM does not provide an explicit definition about the order that supply net connections are maintained in when multiple 'connect\_supply\_net' commands could each make multiple supply net connections each. Future UPF revisions should make this ordering explicit, or future supply\_net\_type definitions should include a name field that is populated when nets are declared.

## VIII. FUTURE STUDY

This survey was performed with the most contemporary versions of tools available to the author; however, in some cases the results could be different in newer releases. The results should be reviewed with each tool vendor to confirm that the behavior seen is consistent with newer releases or if newer versions have a different behavior – either by default or with available options.

## REFERENCES

- Design Automation Standards Committee of the IEEE Computer Society, "IEEE Standard for Design and Verification of Low-Power, Energy-Aware Electronic Systems", IEEE Std. 1801-2013, 29 May 2013.

- [2] Design Automation Standards Committee of the IEEE Computer Society, "IEEE Standard for Design and Verification of Low-Power, Energy-Aware Electronic Systems", IEEE Std. 1801-2015, 5 December 2015.

- [3] Design Automation Standards Committee of the IEEE Computer Society, "IEEE Standard for Design and Verification of Low-Power, Energy-Aware Electronic Systems", IEEE Std. 1801-2018, 27 September 2018.