# **Debug Automation with Al**

Craig Yang, Jaw Lee, Sherwin Lai Verdi R&D, Synopsys Taiwan

SYNOPSYS®

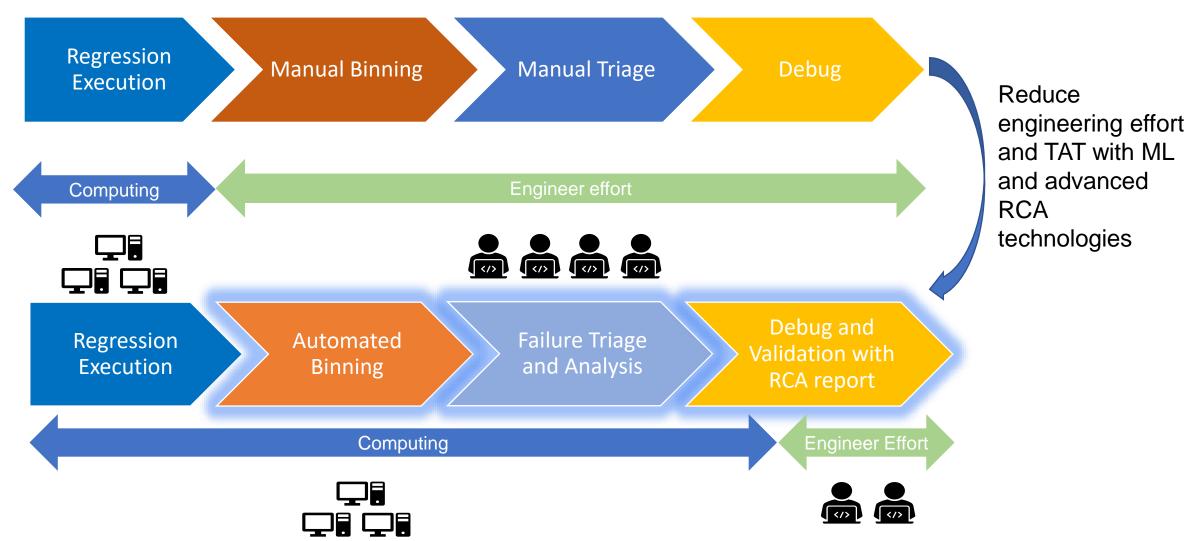

# Motivation and Debug Flow

# Regression Debug Automation Motivation

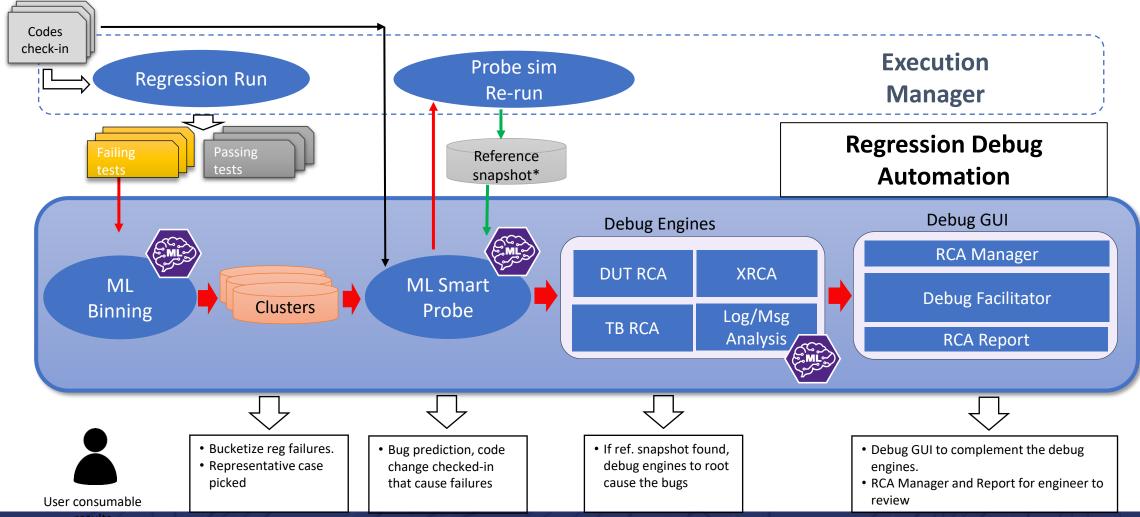

## Regression Debug Flow with ML

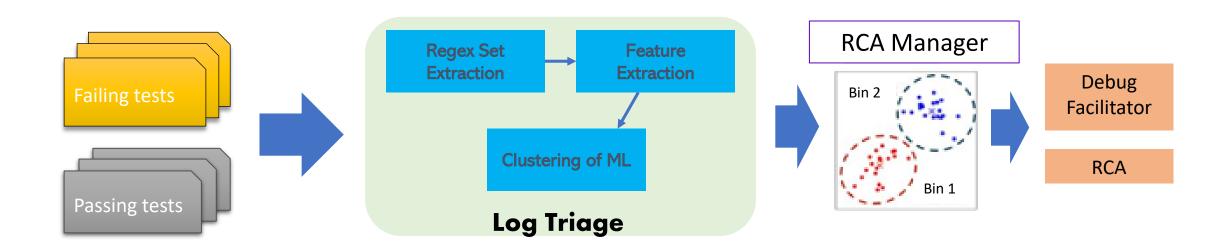

# Regression Binning

#### Regression Binning with ML

- Apply machine learning technology for regression binning

- Perform failure clustering based on the similarity of simulation logs

#### **Regression Binning Engine**

### Useful Regression Binning Features

- Predefined Errors

- UVM Errors, OVM Errors, SVA Failures, etc.

- User Defined Errors

- Control the Message Chosen Mechanism

- Filter Rules

- Waive Rules

- Rule Priority

- Adjust the Binning Result

- Replace Rule

- Pass Rule

- Multiple-Error Binning

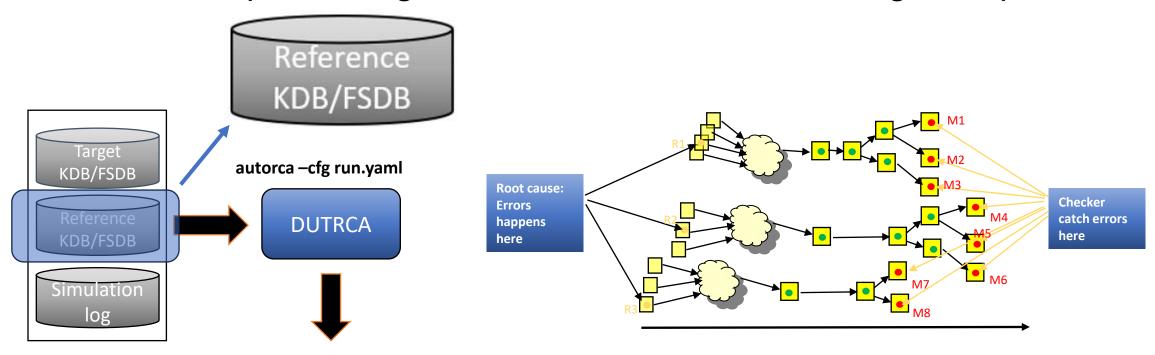

# **Bug Prediction**

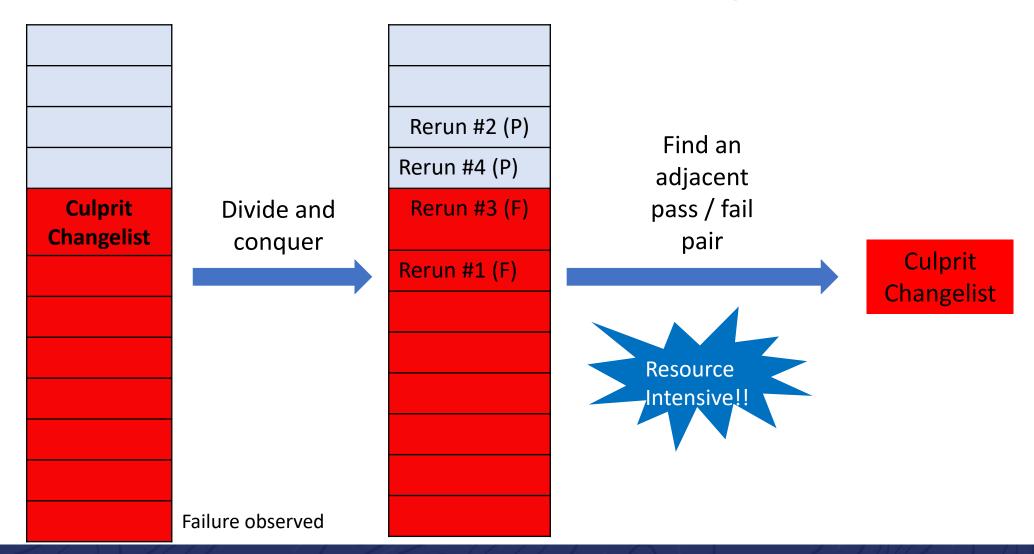

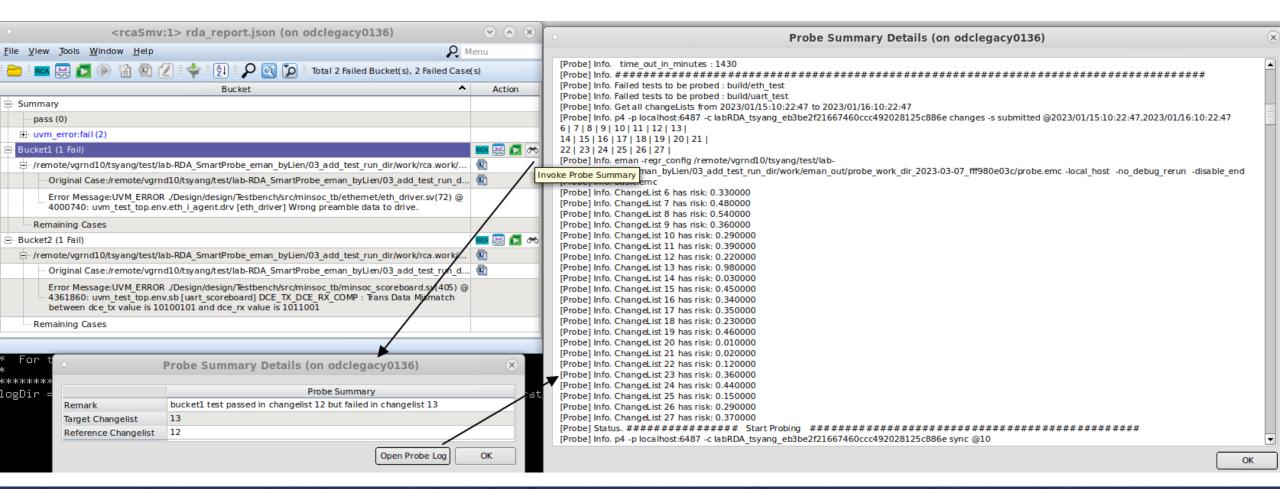

### Probe Engine

- Some debug engines need a reference design snapshot

- We need a probe engine to find the reference design snapshot

# Traditional Probe without Bug Prediction

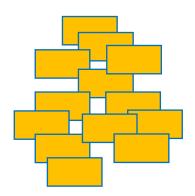

### **Bug Prediction**

CL: Changelist of Perforce

**Failed CLs**

Collect metrics for failed and passed CLs

Predict

suspicious CLs

Rerun to

validate prediction

**Passed CLs**

1. Passed CL observed last time

Bug

Prediction Model

Culprit CL

Suspicious CL

2. Failed CL observed this time

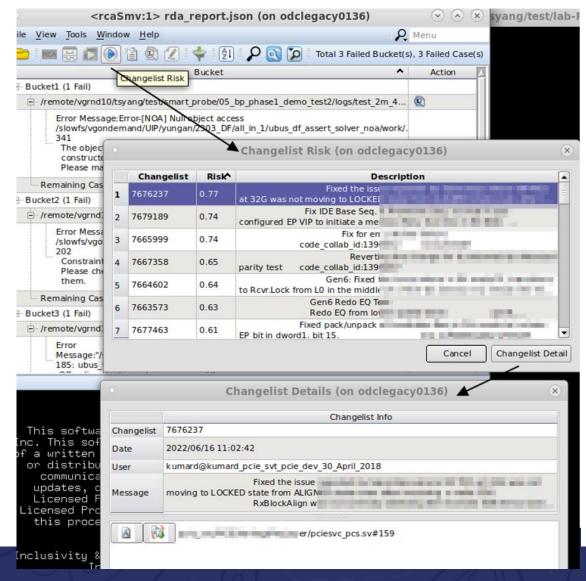

#### **Bug Prediction for Smart Probe**

Prioritize the probe efforts to high-risk changelists

#### Bug Prediction for Risk Assessment

Help the users assess high-risk changelists without running probe

# Message Analysis

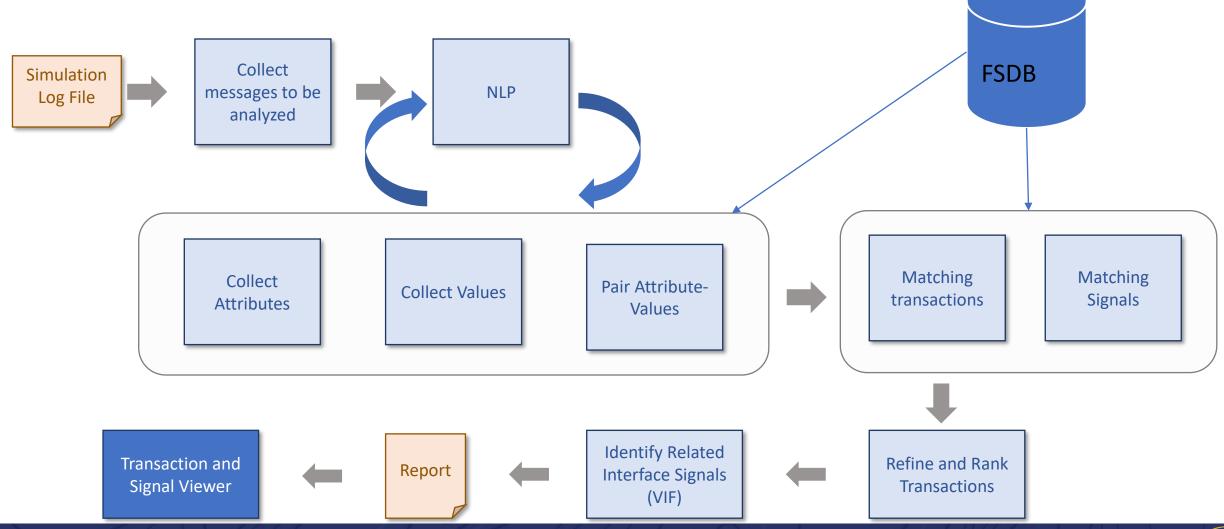

# Message Analysis – High Level Flow

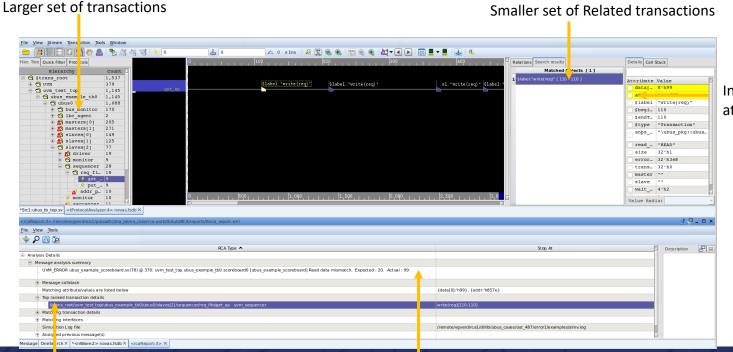

#### Message Analysis – Example

```

TBAR INFO: Started analyzing debug message(s) from simulation log file {/remote/vgsource12/ikshvaku/TD.VERDI REG/unit VERDI/unittest/evProds/tbAutoRCA/testData/swayCases/TB ERRROR/out 230/examples/simv.log}

TBAR INFO: Simulation log file contains ERRORS(14) debug messages.

TBAR INFO: Analyzing the first ERROR log message.

TBAR INFO: Analyzing the below log message.

[UVM ERROR ubus example master seq lib.sv(206) @ 80: uvm test top.ubus example tb0.ubus0.masters[1].sequencer@@loop read modify write seq.rmw seq [read modify write seq]

loop read modify write seq.rmw seq Read Modify Write Read error!}

TBAR INFO: Completed analyzing debug message(s) from simulation log file.

TBAR INFO: Matching attribute/values are listed below.

TBAR INFO: {addr:020a}, {data[0]:e9}

TBAR INFO: Matching transactions after analyzing actual, next and previous messages are listed below

TBAR INFO: Stream: {\$trans root/uvm test top/ubus example tb0/ubus0/masters[1]/driver/seq item port} Matching transactions: {2}

TBAR INFO: Stream: {$trans root/uvm test top/ubus example tb0/ubus0/masters[1]/sequencer} Matching transactions: {1}

TBAR INFO: Total matching transactions {3}

TBAR INFO: Matching virtual interface paths are listed below

TBAR INFO: /ubus tb top/vif Signals: {sig read, sig write, sig addr}

TBAR INFO: Top ranked transaction details are listed below

TBAR INFO: Transaction {get next item(req)[80-80]} Stream {$trans root/uvm test top/ubus example tb0/ubus0/masters[1]/driver/seq item port} Component type {uvm driver} Port type {uvm seq item pull port}

TBAR INFO: Connected to {uvm test top.ubus example tb0.ubus0.masters[1].sequencer.seq item export} Component type {uvm sequencer} Port type {uvm seq item pull imp}

TBAR INFO: Please run the {/slowfs/vgvips19/prasadtc/verdiLog/tbAutoRCA/reports//simvErrorAnalysisLog/run verdi} script to view the simv log file analysis results in Verdi.

```

Interested transaction attributes

#### Summary

- Manual regression debug is tedious, but we can automate it with AI and advanced RCA technologies

- Regression binning classifies many failed tests into a few bins of different errors

- Bug prediction reduces the time on locating reference snapshots for debug engines

- Message analysis identifies transactions and VIFs that are related to the error message

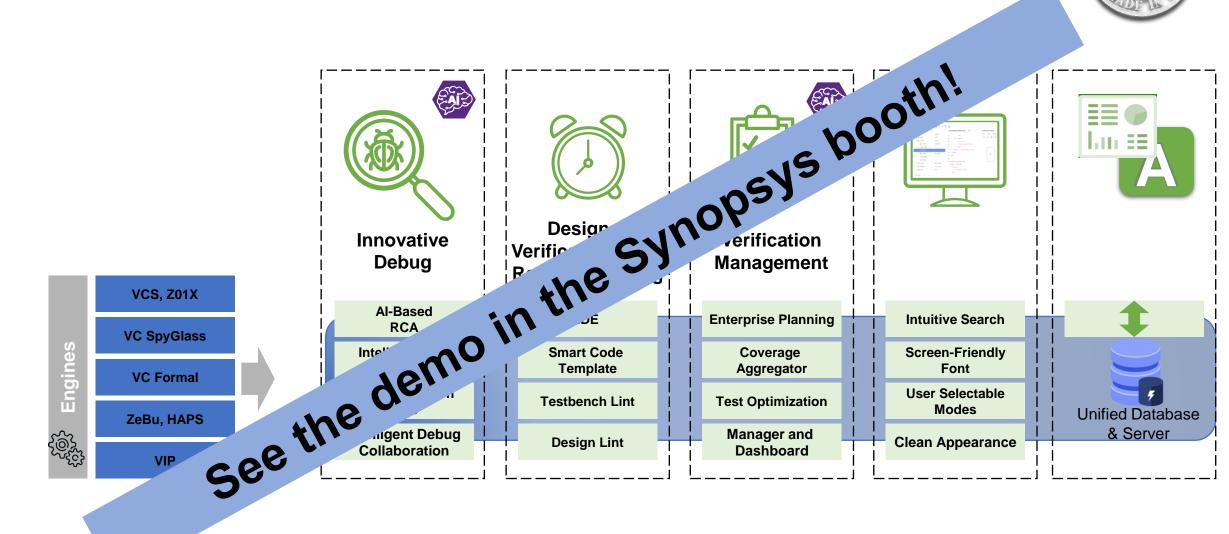

#### Introducing Next-Generation Verdi Platform

#### Questions