**SYNOPSYS**°

# Conquering UCle 1.1 Multi-die System Verification Challenges

# Interface Verification Critical for Chiplet and UCIe Adoption

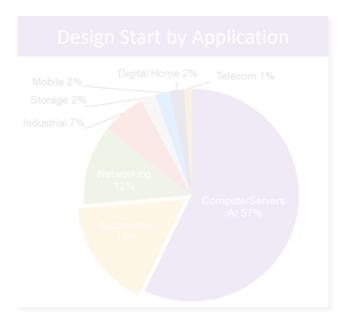

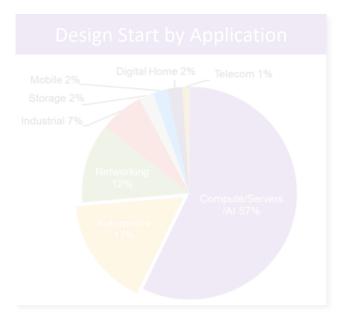

Die-to-Die IP design starts to grow 5X in 5 years\*\*\*

" \$50B in Chiplet revenue forecasted by 2024"

"Led by HPC & Automotive"

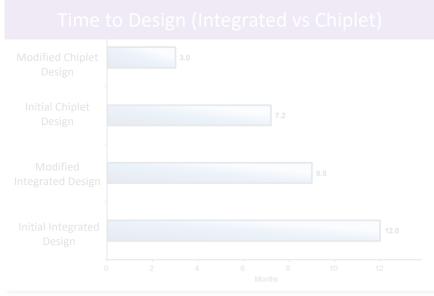

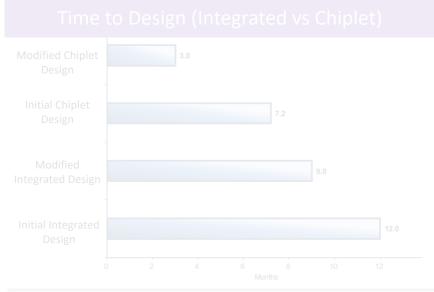

"The time-to-market may be 60% faster for initial chiplet designs compared to integrated designs"

\*Source: Gartner 2021 \*\*Source: IBS 2023 \*\*\*Source: IP Nest 2022

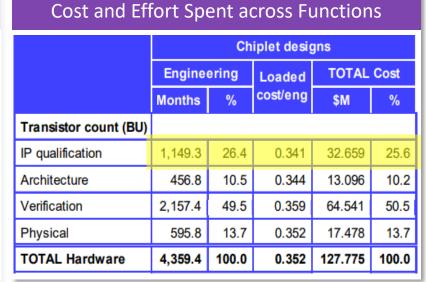

"The highest-cost design step is functional verification, and emulation capabilities are very important"

### Multi-Die System Examples

Enabled by More Cost-Effective Multi-Die Packaging Technologies!

#### INTEL - Ponte-Vechio Xe-HPC GPU

100B+ Tr's, 47 Active Tiles, 5 Process Nodes, EMIB/Foveros

#### APPLE - M1 UltraMax CPU

2x Dies, 114B Transistors, 2.5TB D2D BW, Silicon Connected

#### AMD - EPIC Server CPU

100B+ Tr's, 47 Active Tiles, 5 Process Nodes, EMIB/Foveros

#### TESLA - 9 Peta Flops AI-Training

25x 50B Transistors, Reconstructed fanout wafer

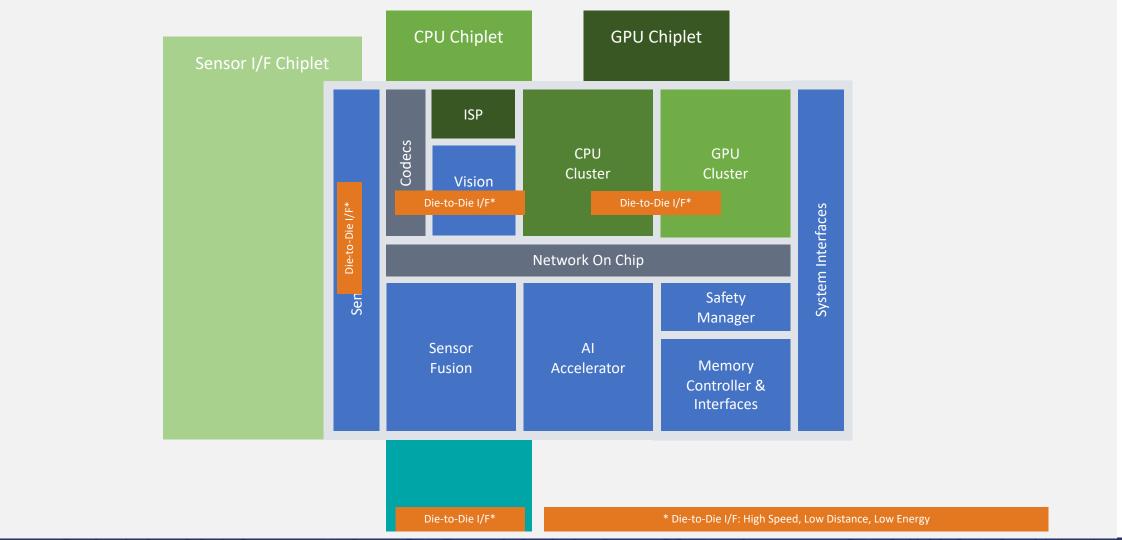

### Optimizing Architectural Functions into Chiplets

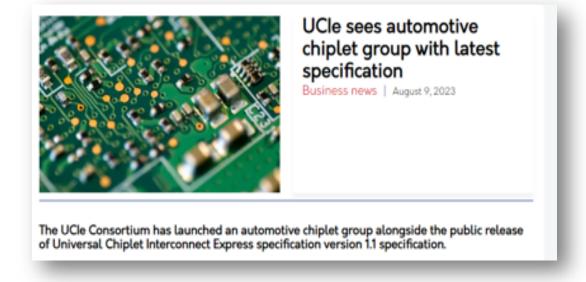

# UCIe 1.1 Focuses on Key Automotive Customer Asks!

Safety, Security, Reliability and Ecosystem Adoptions

- Preventive Monitoring

- On-field Repairability

- Ecosystem fit through multiple existing protocols

- More ...

### UCIe 1.1 Verification Requirements

1 Preventive Monitoring

On-field Repairability

3 Ecosystem Adoption

4 Cost Optimization

Compliance Testing

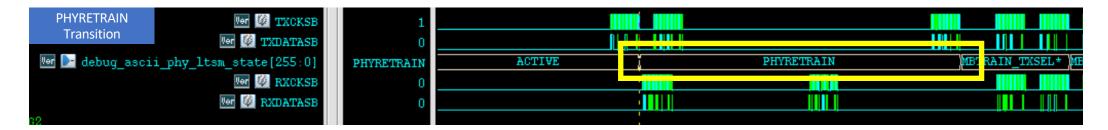

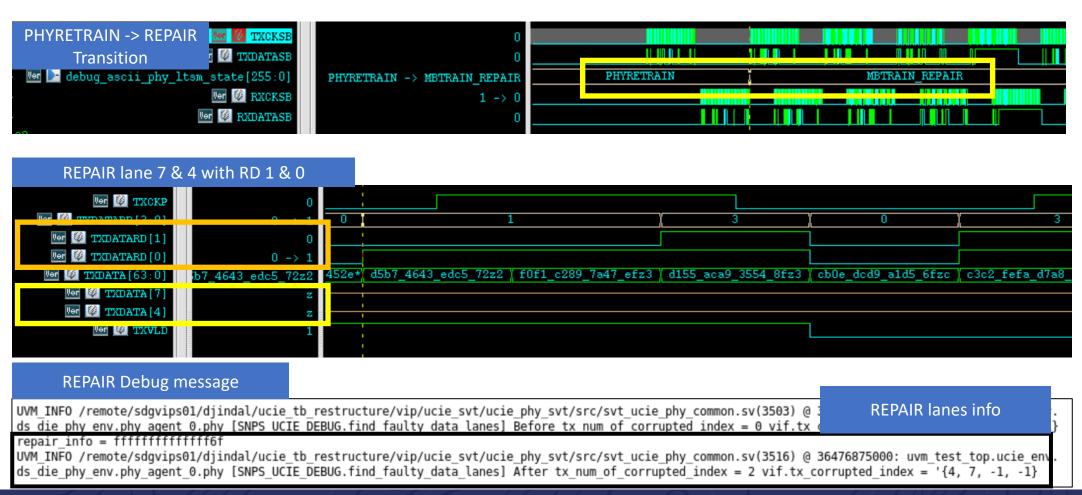

### **Preventive Monitoring**

#### Link Health Monitoring Considerations

- Continuous Monitoring: Per-lane eye-margin measurement and control to shift eye-margin

- Failure rate of link: Periodic insertion of parity bytes

- PHYRETRAIN: Retraining of link during runtime to ensure link safety

#### Failure Detection Considerations

- Reporting of failure: Standard UHM registers to log error along with timestamp

- Interrupt: Indication to the system about link failure

### Preventive Monitoring – Synopsys UCIe VIP

| Design and Verification considerations | VIP features                                                                                                                                                                                                            |

|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Continuous monitoring & reporting      | <ul> <li>API</li> <li>Control eye margins during LTSM states</li> <li>Read/write UHM registers</li> </ul>                                                                                                               |

| Failure rate of link                   | <ul><li>Parity computation and correction</li><li>Callback to inject parity error</li></ul>                                                                                                                             |

| PHYRETRAIN                             | <ul> <li>Local and remote Adapter and PHY initiated retrain</li> <li>API         <ul> <li>Control retrain pattern count</li> <li>Corrupt retrain results</li> <li>Forcibly move to retrain state</li> </ul> </li> </ul> |

| Interrupt                              | API to enable/disable interrupts                                                                                                                                                                                        |

Protocol checks to catch unexpected DUT behaviours

### Preventive Monitoring – Synopsys UCIe VIP

API to initiate RETRAIN from Adapter layer

//API to drive RETRAIN

ds\_seq.direct\_ssm\_state(svt\_ucie\_types::RETRAIN);

#### PHYRETRAIN entry Debug message

UVM\_INFO /remote/sdgvips01/djindal/ucie\_tb\_restructure/vip/ucie\_svt/ucie\_phy\_svt/src/svt\_ucie\_phy\_ltsm.sv(116) @ 410850000000: uvm\_test\_top.ucie\_env. ds die phy env.phy agent 0.phy [init] Phy LTSM transitioned to phy ltsm[phyretrain] state.

```

Field Description:

START TIME

Begin time of the transaction in ns.

PHY SB transfer log

END TIME

End time of the transaction in ns.

- Transaction Direction(Tx/Rx)from VIP perspective.

DIR(Tx/Rx)

SRC ID

- Indicates the source.

- Indicates the destination, where L stands for Local Die and R stands for Remote die

DST ID

OPCODE

- Indicates about the packet type as well either it carries 32b or 64b of data.

TAG

- Indicates the completion tag associated with the corresponding request.

MSGCODE

Indicates the type of Message.

- Indicates address of the request.

ADDR

MSGINFO

- Indicates the Message information.

- Indicates payload which can be 32 bits or 64 bits wide depending on the opcode ({Phase 2, Phase 3}).

DATA

COMP STATUS

- Indicates the completion status of the request.

- Indicates byte enable for the request.

MSGSUBCD

Indicates the sub type of Message.

PHYRETRAIN start request

START TIME

END TIME

SRC ID

DST ID

OPCODE

TAG /

ADDR /

(in ns)

MSGCODE

MSGINFO

41097.000000

41176.0000

PHY(R)

MSG NO DATA

0001

: {}

'h01

'hc5

41557.000000

41636.0000

RX

PHY

PHY(R)

MSG NO DATA

'hca

0001

'h01

41895.000000

41975.0000

MSG NO DATA

'h01

```

UCle 1.1 Verification Requirements 1 Preventive Monitoring

2 On-field Repairability

3 Ecosystem Adoption

4 Cost Optimization

Compliance Testing

### On-field Repairability

#### Repairability Considerations

- Redundancy mapping: Clock and valid lane mapping, single lane and two-lane data mapping

- REPAIR: Usage of Redundant pins to repair clock, valid and data lanes

- TRAINERROR: Repair of lanes is not feasible

### On-field Repairability – Synopsys UCIe VIP

UCIe 1.1 Verification Requirements 1 Preventive Monitoring

2 On-field Repairability

3 Ecosystem Adoption

4 Cost Optimization

Compliance Testing

- Streaming Protocol usage considerations

- *Flit formats*: Usage of existing PCIe/CXL flit formats for various streaming protocol chiplets e.g. AXI, CHI, vendor defined etc.

- Features: Use D2D features like CRC, Retry, parity, etc.

| Flit Format   Flit Format Name | PCle                                                | CXL 68B                 | CXL 256B  | Streaming               |           |           |

|--------------------------------|-----------------------------------------------------|-------------------------|-----------|-------------------------|-----------|-----------|

| Number                         | Filt Format Name                                    | Flit Mode               | Flit Mode | Flit Mode               | UCle 1.0  | UCle 1.1  |

| 1                              | Raw                                                 | Optional                | Optional  | Optional                | Mandatory | Mandatory |

| 2                              | 68B                                                 | N/A                     | Mandatory | N/A                     | N/A       | Supported |

| 3                              | Standard 256B End<br>Header                         | Mandatory               | N/A       | N/A                     | N/A       | Supported |

| 4                              | Standard 256B Start<br>Header                       | Optional                | N/A       | Mandatory               | N/A       | Supported |

| 5                              | Latency Optimized<br>256B without optional<br>Bvtes | N/A                     | N/A       | Optional                | N/A       | Supported |

| 6                              | Latency Optimized<br>256B with optional Bytes       | Strongly<br>Recommended | N/A       | Strongly<br>Recommended | N/A       | Supported |

- Streaming Protocol usage considerations

- *Flit formats*: Usage of existing PCIe/CXL flit formats for various streaming protocol chiplets e.g. AXI, CHI, vendor defined etc.

- Features: Use D2D features like CRC, Retry, parity, etc.

| Flit Format Nov | Flit Format Name                                    | PCle                    | CXL 68B   | CXL 68B CXL 256B        | Streaming |           |

|-----------------|-----------------------------------------------------|-------------------------|-----------|-------------------------|-----------|-----------|

| Number          | Filt Format Name                                    | Flit Mode               | Flit Mode | Flit Mode               | UCle 1.0  | UCle 1.1  |

| 1               | Raw                                                 | Optional                | Optional  | Optional                | Mandatory | Mandatory |

| 2               | 68B                                                 | N/A                     | Mandatory | N/A                     | N/A       | Supported |

| 3               | Standard 2568 End<br>Header                         | Mandatory               | N/A       | N/A                     | N/A       | Supported |

| 4               | Standard 256B Start<br>Header                       | Optional                | N/A       | Mandatory               | N/A       | Supported |

| 5               | Latency Optimized<br>256B without optional<br>Bytes | N/A                     | N/A       | Optional                | N/A       | Supported |

| 6               | Latency Optimized<br>256B with optional Bytes       | Strongly<br>Recommended | N/A       | Strongly<br>Recommended | N/A       | Supported |

- Streaming Protocol usage considerations

- Flit formats: Usage of existing PCIe/CXL flit formats for various streaming protocol chiplets e.g. AXI, CHI, vendor defined etc.

- Features: Use D2D features like CRC, Retry, parity, etc.

| Flit Format Flit Format Name | PCle                                                | CXL 68B                 | CXL 256B  | Streaming               |           |           |

|------------------------------|-----------------------------------------------------|-------------------------|-----------|-------------------------|-----------|-----------|

| Number                       | Filt Format Name                                    | Flit Mode               | Flit Mode | Flit Mode               | UCle 1.0  | UCle 1.1  |

| 1                            | Raw                                                 | Optional                | Optional  | Optional                | Mandatory | Mandatory |

| 2                            | 68B                                                 | N/A                     | Mandatory | N/A                     | N/A       | Supported |

| 3                            | Standard 256B End<br>Header                         | Mandatory               | N/A       | N/A                     | N/A       | Supported |

| 4                            | Standard 256B Start<br>Header                       | Optional                | N/A       | Mandatory               | N/A       | Supported |

| 5                            | Latency Optimized<br>256B without optional<br>Bytes | N/A                     | N/A       | Optional                | N/A       | Supported |

| 6                            | Latency Optimized<br>256B with optional Bytes       | Strongly<br>Recommended | N/A       | Strongly<br>Recommended | N/A       | Supported |

- Streaming Protocol usage considerations

- Flit formats: Usage of existing PCIe/CXL flit formats for various streaming protocol chiplets e.g. AXI, CHI, vendor defined etc.

- Features: Use D2D features like CRC, Retry, parity, etc.

| Flit Format   Flit Format Name | PCle                                                | CXL 68B CXL 256E        | CXL 256B  | Streaming               |           |           |

|--------------------------------|-----------------------------------------------------|-------------------------|-----------|-------------------------|-----------|-----------|

| Number                         | riit roilliat Naille                                | Flit Mode               | Flit Mode | Flit Mode               | UCle 1.0  | UCle 1.1  |

| 1                              | Raw                                                 | Optional                | Optional  | Optional                | Mandatory | Mandatory |

| 2                              | 68B                                                 | N/A                     | Mandatory | N/A                     | N/A       | Supported |

| 3                              | Standard 256B End<br>Header                         | Mandatory               | N/A       | N/A                     | N/A       | Supported |

| 4                              | Standard 256B Start<br>Header                       | Optional                | N/A       | Mandatory               | N/A       | Supported |

| 5                              | Latency Optimized<br>256B without optional<br>Bytes | N/A                     | N/A       | Optional                | N/A       | Supported |

| 6                              | Latency Optimized<br>256B with optional Bytes       | Strongly<br>Recommended | N/A       | Strongly<br>Recommended | N/A       | Supported |

#### Enhanced Protocol considerations

- Stack mux: Muxing of different protocol and utilizing the bandwidth efficiently

- Arbitration: Per flit arbitration to utilize 100% bandwidth and didn't violate maximum percentage

#### Link initialization considerations

- Initialization & Negotiation: Negotiate and finalize multi-protocol mode, stack 0/1 enable, flitformat and stack bandwidth with remote link partner

- State Machine: Independent link state management for state machine for individual FDI interface in Multi-protocol mode

#### Data flow considerations

- Multiplexing: Muxing of data coming from independent data source

- Error Detection: CRC/parity error detection in D2D Adapter for all flit formats

| Design and Verification considerations | VIP features                                                                                                                                                                                                                                           |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Link initialization                    | <ul> <li>Parameter exchange advertisement</li> <li>Clock gate handshake for independent FDI interface</li> <li>API to move to specific state</li> </ul>                                                                                                |

| Data Flow                              | <ul> <li>Independent interfaces to transport data using multiple instances</li> <li>API         <ul> <li>Configure flit format</li> <li>Configure protocol for both stacks</li> </ul> </li> <li>Data integrity check using CRC, parity etc.</li> </ul> |

| Throughput                             | Per flit arbitration with 50% bandwidth                                                                                                                                                                                                                |

| Error injection                        | <ul> <li>Callback</li> <li>To inject error in flit</li> <li>To corrupt sideband messages</li> </ul>                                                                                                                                                    |

### Ecosystem Adoption – Synopsys UCIe VIP

#### API to configure multi-protocol

```

foreach(env_cfg.ds_protocol_cfg.fdi_cfg[i,j])begin

if(i==0 || j==1)begin

env_cfg.ds_protocol_cfg.fdi_cfg[i][j].configure_protocol(svt_ucie_types::CXL_3, svt_ucie_types::CXL_LATENCY_OPTIMIZED_WITH_OB_MODE, svt_ucie_types::STACK_0_CXL_CACHEMEM);

end

else begin

env_cfg.ds_protocol_cfg.fdi_cfg[i][j].configure_protocol(svt_ucie_types::STREAMING, svt_ucie_types::CXL_LATENCY_OPTIMIZED_WITH_OB_MODE, svt_ucie_types::STACK_1_STREAMING_PROTOCOL);

end

end

```

#### Configure Protocol debug message

```

UVM_INFO /remote/sdgvips01/vsheth/ucie_svt_vip_pou_client_19_12/vip/ucie_svt/src/svt_ucie_fdi_configuration.sv(773) @ 0.00000 ns: reporter [configure_protocol] FDI is configured with supported_protocol(CXL_3), supported_protocol_flit_fmt(CXL_LATENCY_OPTIMIZED_WITH_OB_MODE) and stream_id(STACK_0_CXL_CACHEMEM) with API call

UVM_INFO /remote/sdgvips01/vsheth/ucie_svt_vip_pou_client_19_12/vip/ucie_svt/src/svt_ucie_fdi_configuration.sv(773) @ 0.00000 ns: reporter [configure_protocol] FDI is configured with supported_protocol(STREAMING), supported_protocol_flit_fmt(CXL_LATENCY_OPTIMIZED_WITH_OB_MODE) and stream_id(STACK_1_STREAMING_PROTOCOL) with API call

```

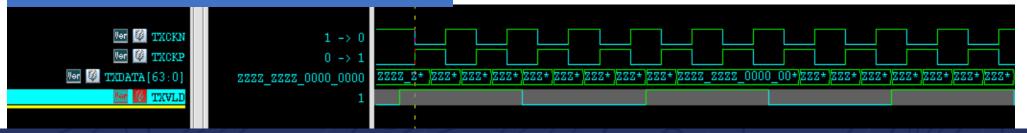

#### Data Transfer on individual FDI lp data and lp valid

UCIe 1.1 Verification Requirements 1 Preventive Monitoring

On-field Repairability

3 Ecosystem Adoption

4 Cost Optimization

Compliance Testing

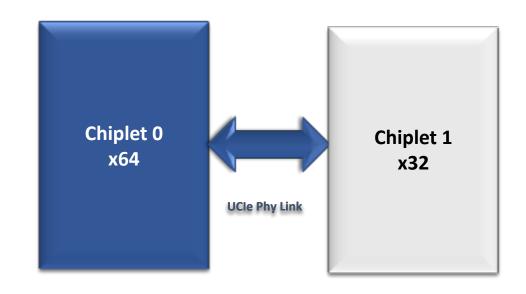

### **Cost Optimization**

- Advance package considerations

- Reusability: x64 link can operate as a x32 when supported and negotiated in MBINIT.PARAM

- Optimization: Lesser fan-out and reduced die cost by reducing pins

- Enable x32 support using below two methods:

- Link capability DVSEC register APMW

- Physical Layer control register Force x32 width mode

### **Cost Optimization**

| Design and Verification considerations | VIP features                                                                                                                                                |

|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter Exchange                     | <ul> <li>UCle-A x32 parameter exchange</li> <li>API</li> <li>Enable x32 support</li> <li>Bypass link states</li> <li>Move to specific link state</li> </ul> |

| MB Repair                              | <ul> <li>API</li> <li>Control repair pattern count</li> <li>Corrupt repair result</li> </ul>                                                                |

| MB Reversal                            | <ul> <li>API</li> <li>Control reversal pattern count</li> <li>Corrupt reversal result</li> </ul>                                                            |

| Data Flow                              | <ul> <li>API</li> <li>Control inter packet delay</li> <li>Inject back pressure</li> </ul>                                                                   |

### Cost Optimization – Synopsys UCIe VIP

API to configure x32

```

//Configuring link width

env_cfg.ds_phy_cfg.configure_link_width(svt_ucie_types::X32_WIDTH, svt_ucie_types::X32_WIDTH);

```

### Configure link width debug message

UVM\_INFO /remote/sdgvips01/djindal/ucie\_tb\_restructure/vip/ucie\_svt/src/svt\_ucie\_phy\_env\_configuration.sv(843) @ 0: reporter [configure\_link\_width] PHY modules are configured with supported\_link\_width(X32\_WIDTH) and target\_link\_width(X32\_WIDTH) with API call

####

#### B2B Data Transfer utilizing optimal link bandwidth

UCle 1.1 Verification Requirements 1 Preventive Monitoring

2 On-field Repairability

3 Ecosystem Adoption

4 Cost Optimization

Compliance Testing

### **Compliance Testing**

PHY Compliance

Adapter Compliance

Protocol Layer Compliance

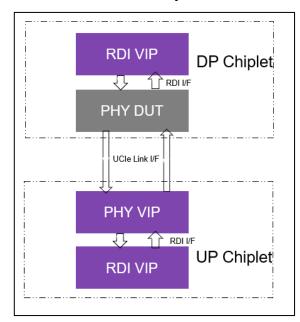

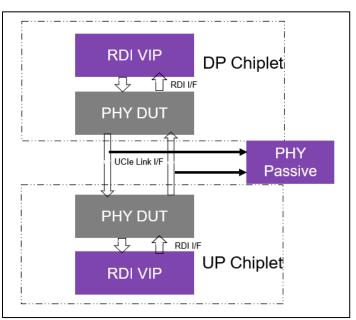

### PHY Compliance

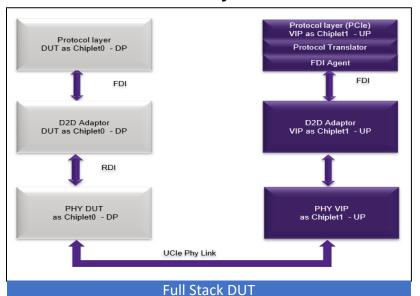

| Test criteria            | VIP features                                                                                                                                                                               | VIP topology                |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| Link Initialization      | <ul> <li>API</li> <li>Trigger link initialization</li> <li>Control training pattern counts</li> </ul>                                                                                      |                             |

| Timing/Voltage margining | <ul> <li>API to control eye margins during LTSM states</li> </ul>                                                                                                                          | VIP as<br>Chiplet0- DP      |

| BER measurement          | <ul> <li>Callback</li> <li>To inject CRC, parity errors</li> <li>To timeout sideband request</li> </ul>                                                                                    | PHY DUT as<br>Chiplet0 - DP |

| Error injection          | <ul> <li>API</li> <li>Control timeout of state</li> <li>Timeout sideband request</li> <li>Corrupt training pattern results</li> <li>Callback to block sideband response message</li> </ul> | VIP as<br>Chiplet1 - UP     |

Golden Die: All above and ability to inject errors that cause timeouts on sideband messages as well as states

### **Adapter Compliance**

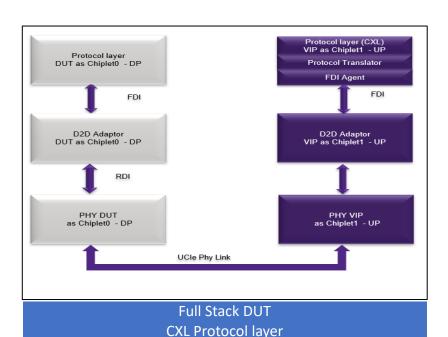

| Test criteria              | VIP features                                                                                                                                    | VIP topology                     |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Injection of NOP/Test flit | <ul><li>API to enable flit injection</li><li>Callback to inject flits</li></ul>                                                                 |                                  |

| State Request              | <ul> <li>API</li> <li>Enable state request injection</li> <li>Move to a specific state</li> </ul>                                               | VIP as<br>Chiplet0 - DP          |

| Response sideband messages | <ul> <li>API to enable sideband response message injection</li> <li>Callback to block sideband response</li> </ul>                              | D2D Adaptor DUT as Chiplet0 - DP |

| Retry                      | <ul> <li>API</li> <li>Enable retry injection</li> <li>Enable/disable retry rules groups</li> <li>ACK/NAK indication of received flit</li> </ul> | VIP as<br>Chiplet1 - UP          |

Golden Die: Support all formats, ability to inject above errors

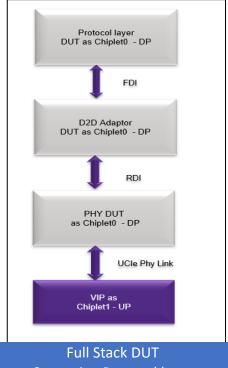

### **Protocol Compliance**

- Leverage PCIe and CXL Protocol compliances defined by those specifications

- Streaming protocols: use their respective compliance

- VIP features:

- Ability to generate PCIe, CXL and streaming protocol scenarios

- Callback to inject errors

PCIe Protocol layer

### Compliance testing

#### Testing Phases

| Phases                            | Phase1                                                                                                                | Phase2                                                                                                                                                                                                 | Phase 3                                                                                                                                                                                                                            |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Goal                              | Bring Up                                                                                                              | Data Flow                                                                                                                                                                                              | Error injection                                                                                                                                                                                                                    |

| Design Verification Consideration | <ul><li>Link up</li><li>RDI bring up</li><li>FDI bring up</li></ul>                                                   | <ul><li>Flit formats</li><li>CRC, parity, retry etc.</li><li>Data integrity</li></ul>                                                                                                                  | <ul> <li>Error injection at each layer</li> </ul>                                                                                                                                                                                  |

| VIP feature                       | <ul> <li>API</li> <li>Trigger link         initialization</li> <li>Control training         pattern counts</li> </ul> | <ul> <li>API</li> <li>Drive sideband and main-band traffic.</li> <li>Control parity and retry features</li> <li>Analysis port at each interface for scoreboarding</li> <li>All flit formats</li> </ul> | <ul> <li>Callback         <ul> <li>To inject errors</li> <li>To block sideband response message</li> </ul> </li> <li>API         <ul> <li>Control timeout of state</li> <li>Delay sideband response message</li> </ul> </li> </ul> |

# Interface Verification Critical for Chiplet and UCle Adoption

Die-to-Die IP design starts to grow 5X in 5 years\*\*\*

" **\$50B in Chiplet revenue** forecasted by 2024"

"Led by HPC & Automotive"

"The time-to-market may be 60% faster for initial chiplet designs compared to integrated designs"

\*Source: Gartner 2021 \*\*Source: IBS 2023 \*\*\*Source: IP Nest 2022

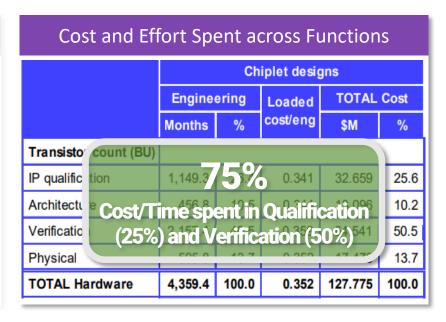

75%

Cost/Time spent in Qualification (25%) and Verification (50%)

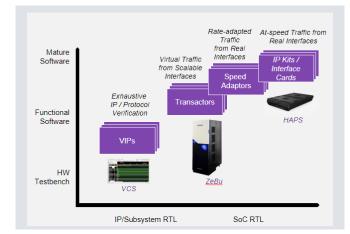

### Reducing Inter-logic SoCs Tape-out Risks

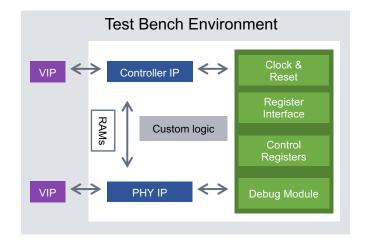

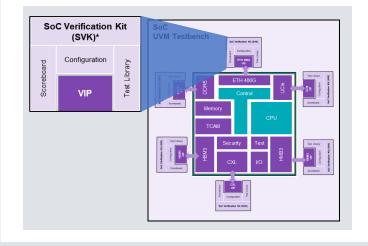

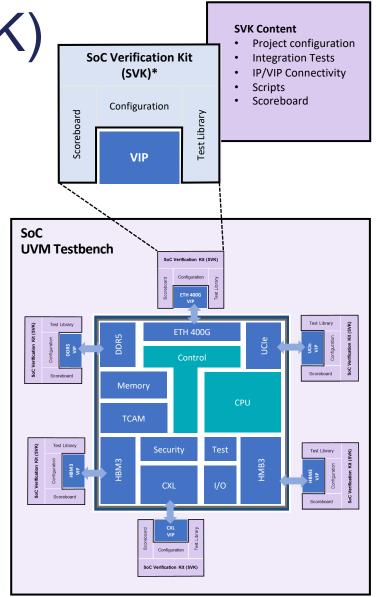

Pre-validated IP-VIP SoC Verification Kits Reduce Design Risk & Accelerate Time-to-Market

#### **IP/Vendor Selection**

- Broadest IP VIP portfolio

- Pre-tested, silicon-proven IP Subsystems for your SoC

- IP & SoC experts configure and customize to your requirements

#### **IP Qualification**

- Active engagement with spec bodies and eco-system partners

- Ready-to-go Compliance test suites for IP qualification

- Frees your team to work on your product differentiation

#### **IP Integration**

- Reference flows and services for IP integration and convergence between project teams

- First-time-right SoC integration speeds TTM

### Synopsys SoC Verification Kit (SVK)

Accelerating SoC Verification with Synopsys IP, VIP and VCS

- Challenges

- Expertise for UVM-based, scalable testbenches

- Verification resource limitations

- SVK Benefits

- Out-of-the-box verification solution for complex protocols

- Tailor made for project-specific IP configuration

- Accelerates the SoC testbench development

- Enables testing of Synopsys IPs in Subsystem/SoC environment

- Lowers integration risk through proven verification methodologies

- Available for HPC/Automotive protocols: UCle, PCle, CXL, DDR, HBM, Ethernet

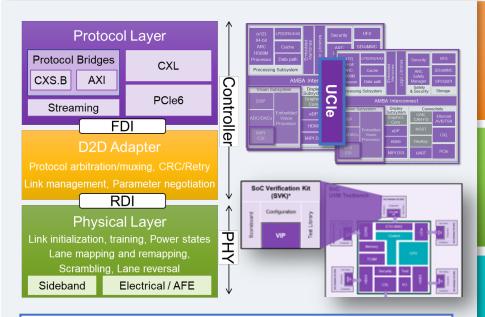

### Verify and Validate Your Multi-Die Interfaces

Synopsys UCIe IP-VIP Validated Together to Reduce Project Risk

#### Latest UCIe Specifications and Topologies

Synopsys UCIe VIP supports entire UCIe standard from PHY to Protocol layer covering all IP to System Level topologies

#### Co-validated with Synopsys IPs

Synopsys UCIe VIP used to validate UCIe IP from Synopsys and leading partners ensuring

#### **Debug Productivity**

Native VCS and Verdi integration provides high simulation and debug productivity for UCIe

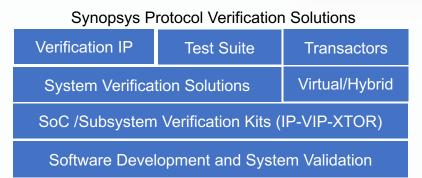

#### Protocol Verification Solutions for all Use-cases

IP to SoC Level RTL Verification

Software development and system validation

Integrated IP-VIP setups for quick bring-up and verification

## **SYNOPSYS®**