Institute for Communication Technologies and Embedded Systems

#### LO YEAR ANNIVERSARY

### Open-Source Virtual Platforms for Industry and Research Nils Bosbach, RWTH Aachen University Lukas Jünger, MachineWare GmbH Rainer Leupers, RWTH Aachen University

### About Us

#### Nils Bosbach

PhD student at *Chair for Software for Systems on Silicon (SSS)*, RWTH Aachen University

#### Lukas Jünger

- Co-founder of *MachineWare GmbH*

- Chair of the SystemC Configuration, Control and Inspection (CCI) Working Group

**Open-Source** Virtual Platforms for Industry and Research

**Open-Source** Virtual Platforms for Industry and Research

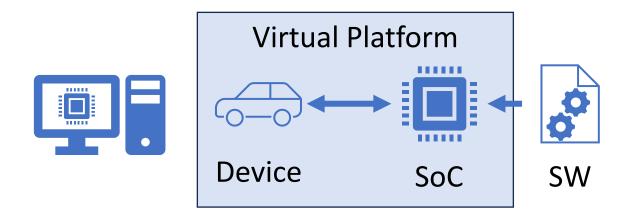

"A virtual platform is a functional representation of a digital system written entirely in software." - Cadence

### **Open-Source** Virtual Platforms for Industry and Research

- Prototyping

- Develop & test models

- Embedded SW development

- Prototyping of new architectures

- Architecture exploration

- Improve simulation performance

### **Open-Source** Virtual Platforms for Industry and Research

# Many commercial solutions available

$\mathbf{O}$

Solution we will talk about today:

#### Available on GitHub

✓ Clone

✓ Play around

✓ Extend

### Free and/or Open-Source Software

- Disclaimer: I am not a lawyer!

- "Free of charge" or "free as in freedom"?

- Licenses

|                   | Apache 2.0                                 | GPLv2       |

|-------------------|--------------------------------------------|-------------|

| Closed-source     | Allowed                                    | Not-allowed |

| Commercialization | Easy (no submarine patents)                | Difficult   |

| IP Protection     | Easy (derived works under another license) | Difficult   |

• Are Apache 2.0 and GPLv2 compatible? Maybe

# Virtual Platforms

A brief introduction

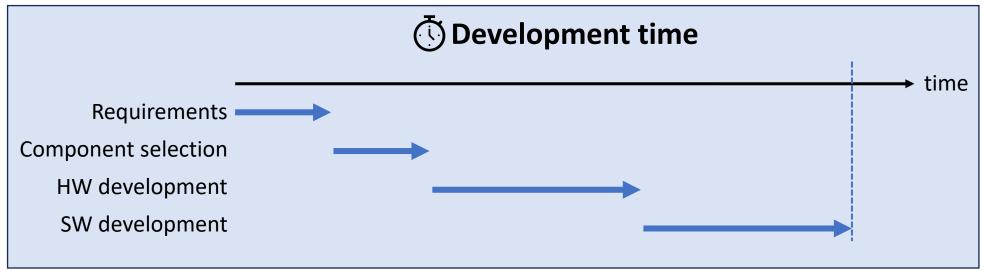

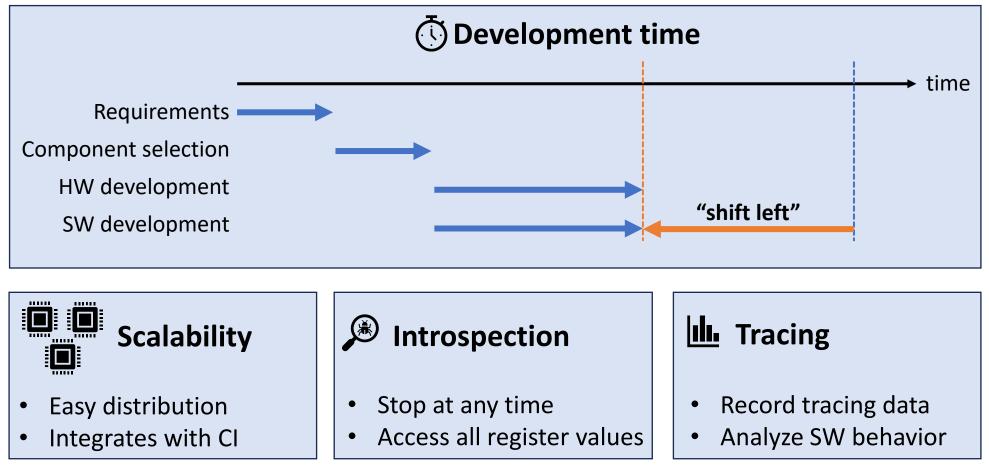

## Why Do We Need Virtual Platforms?

### Why Should You Use Virtual Platforms?

### Why Should You Use Virtual Platforms?

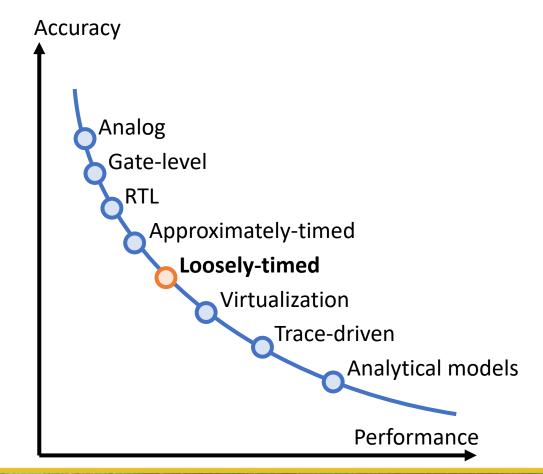

### Abstraction Level

- Many different abstraction levels

- Tradeoff between performance and accuracy

### Choose the level that fits your needs

# Virtual Platform Design

Let's get started!

### How to Start?

|  | Specification |

|--|---------------|

|--|---------------|

- List of components

- Interface description

- Functional behavior

- Simulates the behavior

- Can execute target SW

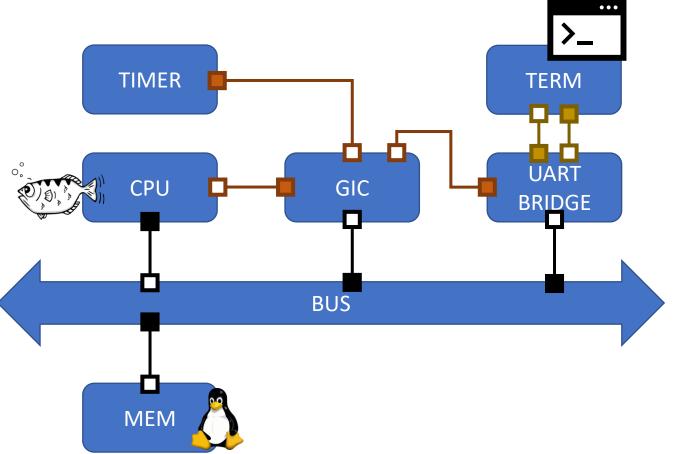

VCML-based models to mimic the behavior of the SoC

Virtual Components Modeling Library – adds modeling primitives

Standardized "design and verification language" (IEEE Std. 1666™-2011)

## Why Do We Need a Modeling Library?

Concept of time

Simulated parallelism

Standardized interfaces (ports, TLM sockets)

Hierarchy (modules)

Models (e.g., buses)

Frequently-needed parts (e.g., register model)

Often-used communication-protocol implementations (SPI, CAN, I<sup>2</sup>C, ...)

TLM logging/tracing, (parametrization, configuration)

## Virtual Components Modeling Library (VCML)

- Loosely-timed simulation framework based on SystemC TLM-2.0

- Apache-2.0 license

- Windows, Linux, MacOS

- x86, arm64 CI builds

- Provides

- Commonly used features (registers, peripherals, etc.)

- Abstract protocols based on TLM-2.0 (interrupt, SPI, I<sup>2</sup>C, etc.)

- Models (memory, memory-mapped buses, UARTs, etc.)

- Extensive unit test suite

https://github.com/machineware-gmbh/vcml

### Why Should You Use VCML?

- Completely standard SystemC TLM-2.0 compatible

- Saves your time when construction a new VP

- Reuse VCML features and models

- Supports all major Systems: Windows, Linux, MacOS, x86 and arm64

- Easy commercialization through Apache 2.0 license

- Example VPs available open-source (ARM and OpenRISC)

- Commercial support available through MachineWare

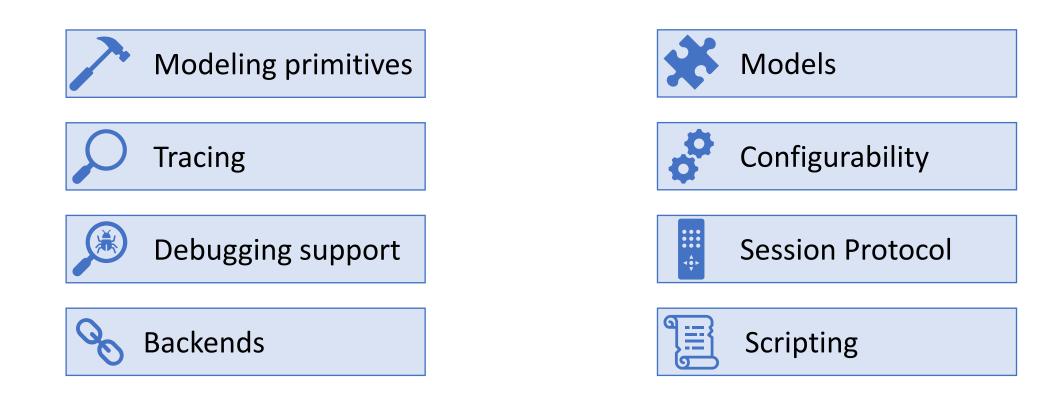

### VCML-Highlights

## Implementation of the CPU Model

SYSTEMS INITIATIVE

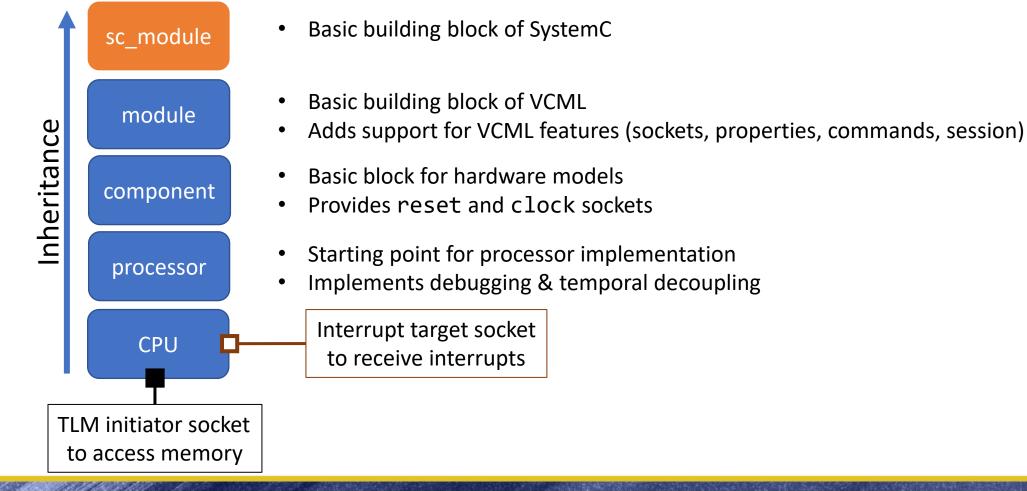

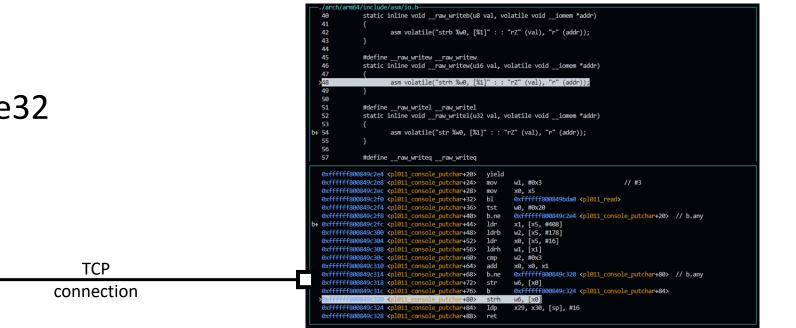

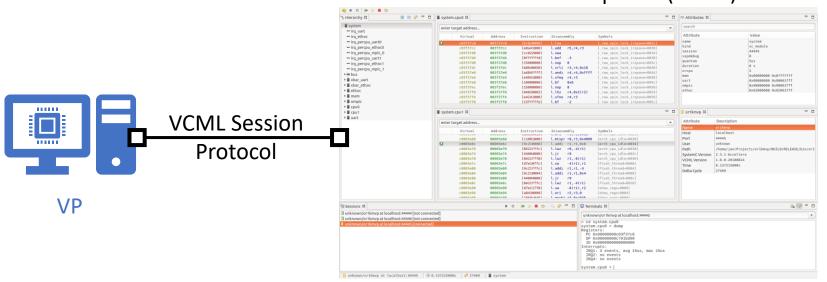

## Target Software Debugging

- Full debugging support

- Including OS

vcml::processor 🗗

• GDB/Lauterbach's Trace32

#### Remote GDB

### Lauterbach's Trace32

......

VP

CE32 PowerView for RISC-V

- Multicore debugging

- OS awareness

- User-space debugging

#### Watch our Trace32 demo:

https://youtu.be/B6zys6\_M-k4

|          |                                     | E          | 3::Register          |               | - 🗆      | X        |                  |        |       |          |             |         |            |             |           |         |

|----------|-------------------------------------|------------|----------------------|---------------|----------|----------|------------------|--------|-------|----------|-------------|---------|------------|-------------|-----------|---------|

| XO       | 0                                   | X16        |                      | S Stack       |          | <b>A</b> |                  |        |       |          |             |         |            |             |           |         |

| X1       | FFFFFFF80031F1A                     | X17        | 54494D45             |               |          |          |                  |        |       |          |             |         |            |             |           |         |

| X2       | FFFFFFF80E03F00                     | X18        | 1                    |               |          |          |                  |        | [ B   | 8::List] |             |         |            |             |           | - 🗆     |

| X3       | FFFFFFF80ED5558                     | X19        | 7                    | Ster          | <b>N</b> | ver      | Diverge          | Return | 🕈 Un  | ► Go     | Break       | Nº Mode | <i>₩</i> + | <b></b>     | Find:     | proc    |

| X4       | FFFFFFF80E0BF80                     | X20        | FFFFFFF80ED636C      | <b>N</b> Step |          |          | - 0              |        |       |          |             | Piode   | - 10       |             |           | P       |

| X5       | FFFFFFE0012D3180                    | X21        | 0                    |               |          |          | addr/line        |        | label |          | nemonic     |         |            | comme       |           |         |

| X6       | 8                                   | X22        | FFFFFFFF80ED6018     |               |          |          | FF800032C4       |        |       |          | ddi         |         | 0,-0x27    |             | ×10,×10,  | , - 632 |

| X7       | FFFFFFFF80C00418                    | X23        | FFFFFFF80800008      |               |          |          | FF800032C8       |        |       |          | uipc        | x1,0x5  |            | ; x1,       |           |         |

| X8<br>X9 | FFFFFFFF80E03F10<br>FFFFFFF80ED61C0 | X24<br>X25 | 80016038<br>80037E94 | SP:FI         | FFF::F   | FFFFF    | FF800032CC       |        |       |          | alr         | x1,-0x  | CA(X1)     | ; X1        | L,-202(x1 |         |

| X10      | PFFFFFFF00ED01C0                    | X25<br>X26 | 00037E94             | CD 51         |          |          | 50<br>FF800032D0 |        |       |          |             |         |            |             |           |         |

| X11      | 0000000200000000                    | X27        | 0                    |               |          |          | FF800032D0       |        |       |          | .ld         | x11,0x  |            |             | L,8(x9)   |         |

| X12      | 1                                   | X28        | 01E5                 |               |          |          | FF800032D2       |        |       |          | uipc<br>ddi | x10,0x  |            | ; ×10       |           | 624     |

| X13      | 1293                                | X29        | 01E5                 |               |          |          | FF800032DA       |        |       |          | uipc        | x10,x10 |            | а;<br>: x1. | x10,x10,  | ,-034   |

| X14      | 1293                                | X30        | 1                    |               |          |          | FF800032DF       |        |       |          | alr         | x1, -0x |            |             | ,-220(x1  | 1)      |

| X15      | FFFFFFE03EFD9320                    | X31        | FFFFFFD00406BC08     |               |          |          | FF800032E2       |        |       |          | .mv         | x10,x9  |            | , ^1        | ,-220(X1  | -/      |

|          |                                     |            |                      |               |          |          | FF800032E4       |        |       |          | uipc        | x1,0x5  |            | ; x1,       | 1511      |         |

| PC       | FFFFFFF8000328E                     | PRIV       | HS                   |               |          |          | FF800032E8       |        |       |          | alr         | x1,0x3  |            |             | ,984(x1)  |         |

| •        |                                     |            |                      |               |          |          | FF800032E0       |        |       |          | .ldsp       | x1,0x1  |            |             | 24(x2)    |         |

|          |                                     |            |                      | SP:FI         | FFF::FF  | FFFFF    | FF800032EE       | 6442   |       | С        | .ldsp       | x8,0x1  |            |             | 16(x2)    |         |

|          |                                     |            |                      |               |          |          |                  |        |       |          |             |         |            |             |           |         |

|          |                                     |            |                      |               |          |          |                  | •      |       |          |             |         |            |             |           | •       |

|          |                                     |            |                      |               |          |          |                  |        |       |          |             |         |            |             |           |         |

|          |                                     |            |                      |               |          |          |                  |        |       |          |             |         |            |             |           |         |

|          |                                     |            |                      |               |          |          |                  |        |       |          |             |         |            |             |           |         |

|          |                                     |            |                      |               |          |          |                  |        |       |          |             |         |            |             |           |         |

|          |                                     |            |                      |               |          |          |                  |        |       |          |             |         |            |             |           |         |

|          |                                     |            |                      |               |          |          |                  |        |       |          |             |         |            |             |           |         |

|          |                                     |            |                      |               |          |          |                  |        |       |          |             |         |            |             |           |         |

**Open-Source Virtual Platforms for Industry and Research**

2023 DESIGN AND VERIFICATION CONFERENCE AND EXHIBITION EUROPEE LD YEAR ANNIVERSARY

## SIM-V and Lauterbach Trace32 Like real hardware, just better

### How to Implement Peripherals?

sc\_module module component peripheral

- Basic building block of SystemC

- Basic building block of VCML

- Adds support for VCML features (sockets, properties, commands, ...)

- Basic block for hardware models

- Provides reset and clock sockets

- Starting point for custom I/O peripheral models

- Adds support for registers

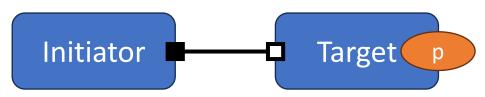

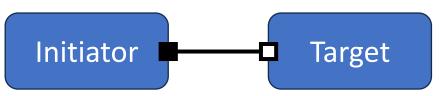

### Interfaces

- Memory accesses

- Interrupt

- Communication/data transfer (e.g., SPI, I<sup>2</sup>C, ...)

### **Based on TLM blocking transports**

#### Payload

- Operation (R/W)

- Data pointer

- Attributes

### Interfaces

- Memory accesses

- Interrupt

- Communication/data transfer (e.g., SPI, I<sup>2</sup>C, ...)

#### **Based on TLM blocking transports**

#### **Process payload**

• Execute operation (R/W)

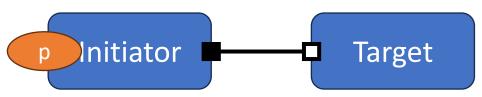

### Interfaces

- Memory accesses

- Interrupt

- Communication/data transfer (e.g., SPI, I<sup>2</sup>C, ...)

### **Based on TLM blocking transports**

#### Send payload back

• Analyze returned payload

### Interfaces

- Memory accesses

- Interrupt

- Communication/data transfer (e.g., SPI, I<sup>2</sup>C, ...)

### **Based on TLM blocking transports**

#### **Implemented protocols**

- CAN PCI

- Clock

SD

- Ethernet Serial

- GPIO SPI

- I<sup>2</sup>C VirtlO

## Predefined Peripherals in VCML

- Memory

- Interrupt controllers (ARM, RISC-V)

- Ethernet, SPI, I<sup>2</sup>C controller

- SD controller

- UARTs (e.g., PL011)

- Sensors (SPI/I<sup>2</sup>C-based)

- VirtIO (controller, console, RNG, block, ...)

- CAN (bridge & bus)

## Configurability

- VCML provides properties to configure modules

- CCI-compatible

- LUA scripting

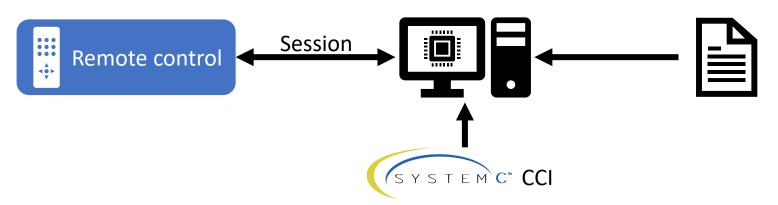

- Session protocol

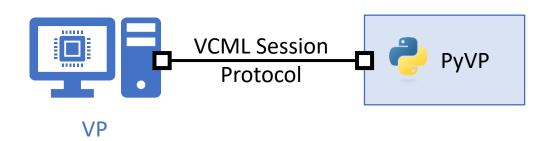

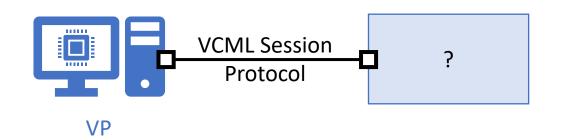

### Session

#### Virtual Platform Explorer (ViPER)

- Control the simulation

- Access/inspect models

- Open, TCP-based protocol

### Session

### Virtual Platform Explorer (ViPER) R R 📌 = D 🛢 outen.

- Python-based implementation of a Session client

- Use Python to script the simulation •

### Session

#### Virtual Platform Explorer (ViPER)

- Infinite number of use cases

- Very powerful interface

- Simple usage

### Free Implementations

- OpenRISC 1000 Multicore Virtual Platform (OR1KMVP)

- Embeds the open-source OR1KISS into vcml::processor

- Simple interpreter-based instruction-set simulator (ISS)

- https://github.com/janweinstock/or1kmvp

- An ARMv8 Virtual Platform (AVP64)

- Embeds the ARMv8 unicorn implementation (QEMU-based) into vcml::processor

- Dynamic-binary-translation (DBT)-based ISS

- https://github.com/aut0/avp64

## **Commercial Implementations**

#### • SIM-V

- Ultra-fast RISC-V simulator

- Supports state-of-the-art extensions

- Custom-instruction API

- SIM-A

- Ultra-fast ARM Cortex-M simulator

- QBox

- QEMU in SystemC TLM-2.0 through VCML

### Full-System Integration

- \* Instantiate models

- **Bind** sockets

- $\succeq$  Start simulation

### SW Development

#### Demo - Find the tutorial on the AVP64 GitHub page

https://github.com/aut0/avp64/tree/master/vscode

# Summary

From spec to chip

#### Slides: https://mwa.re/vcml-tutorial

### Summary

| VP Be              | SW Stack      |                 |

|--------------------|---------------|-----------------|

| 🕚 Development Time | Introspection | (Custom) Models |

| Scalability        | III. Tracing  | VCML            |