# Metadata Based Testbench Generation Automation

Daeseo Cha<sup>1</sup>, Soonoh Kwon<sup>2</sup>, Ahhyung Shin<sup>3</sup>, Youngnam Youn<sup>4</sup>, Youngsik Kim<sup>5</sup>, Seonil Brian Choi<sup>6</sup> Samsung Electronics Co., Ltd., Seoul, Korea (<sup>1</sup>dscha; <sup>2</sup>soonoh1.kwon; <sup>3</sup>ah0403.shin; <sup>4</sup>yyn612; <sup>5</sup>ys31.kim; <sup>6</sup>seonilb.choi@samsung.com)

Abstract: This paper introduces the concept of automated testbench generation techniques using metadata of design spec. It focuses on full chip level structural testbench for register and interconnect verification. We demonstrate what contents need to be captured in metadata and how to automate UVM (Universal Verification Methodology) testbench generation with metadata.

## I. Introduction

Generally, the functional verification environment has been developed by referencing functional specification and RTL design implementation specification together. As the size and complexity of SOC design continues to increase and the development time spent for SOC (System on a Chip) design is required to be shortened, it is very important to follow the variation of functional spec and implement them into RTL design properly. Moreover, the functional spec of design is changed frequently during development cycle. If these changes are not managed systematically, it makes the discrepancy between functional spec and RTL implementation spec.

Register and interconnect verification are the basic features of SOC verification, and they need to be done in early stage of verification with the highest priority. Register verification checks whether all IPs are controlled correctly through register access transaction. Interconnect verification checks whether all masters and slaves are accessed correctly on backbone bus through random data access transaction. Usually, register verification environment consists of register model and address map (uvm\_reg) for each IP, a VIP agent replacing CPU. Interconnect verification environment consisted of VIP agents replacing all masters and slaves. They are highly dependent on the design implementation spec coming from design team. The problem is that verification engineers collect this information by referring to design specification documents and it is likely to insert human-errors when making verification environment, hence the inconsistency between design and documents happens. If there is this kinds of error, it takes long time for debugging because it is running on full-chip. In order to remove this problem, this paper proposes metadata based testbench generation automation approach which is aligned with metadata based SOC design integration automation.

#### II. PROPOSED APPROACH

IP-XACT is the IEEE standard metadata format (IEEE1685) which includes an information for full chip RTL integration(<u>https://www.accellera.org/downloads/standards/ip-xact</u>). Mainly it consists of two parts, one is IP package that includes port list, Interface, and SFR spec, and the other is design architecture that includes IP instance, connection between IPs. However, it is not enough for automating testbench generation (such as security, parameters required for VIP configuration, etc.) so we improved this by extending the contents of metadata. Newly defined metadata contains data for design automation of system IPs such as backbone interconnect, clock and power management unit and so on. In addition, we added more information for testbench automation such as controlling sequences, into the extended metadata. With this extended metadata, we are able to automate RTL design and testbench generation.

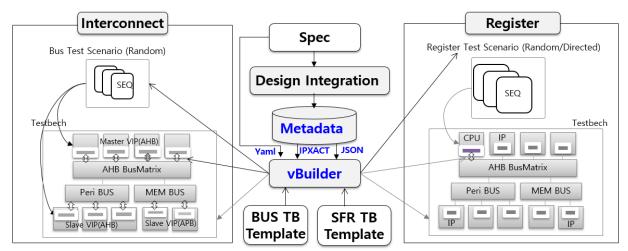

Figure 1 shows the proposed full chip register and interconnect testbench generation flow using metadata. vBuilder(Verification Builder) parses metadata to populate required information for testbench generation, such as IP address map, registers, location where masters and slaves are located, interface protocols and signal for masters/slaves, from metadata (IP-XACT), and then it renders target project testbench with existing register testbench template (SFR TB Template) and interconnect testbench templates(BUS TB Template), which are reusable for all projects. Generated testbench by vBuilder consists of 1) instantiating VIP (Verification IP), 2) connecting VIP ports to RTL signals, 3) generating complete test scenarios.

Figure 1. Metadata based Testbench Generation Flow.

## A. Metadata

IP-XACT provides an IP connectivity standard for full chip RTL integration. Fig 2 shows the content which is described by JSON (JavaScript Object Notation), extracted from IP-XACT. It contains useful information for generating verification environment such as hierarchical instance name, interface name for masters and slaves, interface parameters and so on. They are used to integrate VIP which generates random bus transaction and checker to monitor DUT response through the interface in verification environment.

| "/BLK_CPU/AHB2APB_CPU_0": {         | "PRDATAS0": {                            |

|-------------------------------------|------------------------------------------|

| "interfaces": {                     | "width": "32",                           |

| "AHB00_S": {                        | "direction": "in",                       |

| "mode": "slave",                    | "slices": {                              |

| "connection":                       | "31,16": {                               |

| "/BLK_CPU/AHB_BRIDGE_CPU,AHB02_MS", | "connection": [                          |

| "portmap": {                        | "/BLK_CPU/AHB2APB_CPU_0,PRDATAS0,15,0",  |

| "HADDR": "HADDR",                   | "/BLK_CPU/AHB2APB_CPU_0,PRDATAS0,31,16", |

| "HCLK": "HCLK",                     | "/BLK_CPU/AHB2APB_CPU_0,PRDATAS1,15,0",  |

| "HRDATA": "HRDATA",                 | "/BLK_CPU/AHB2APB_CPU_0,PRDATAS1,31,16", |

| "HREADY": "HREADY",                 | "/BLK_CPU/TAP,p_rdata,15,0"              |

| "HREADYOUT": "HREADYOUT",           | ]                                        |

| "HRESETn": "HRESETn",               | },                                       |

| "HRESP": "HRESP",                   | "15,0": {                                |

| "HSELx": "HSEL",                    | "connec                                  |

| "HSIZE": "HSIZE",                   | "connection": [                          |

| "HTRANS": "HTRANS",                 | "/BLK_CPU/AHB2APB_CPU_0,PRDATAS0,15,0",  |

| "HWDATA": "HWDATA",                 | "/BLK_CPU/AHB2APB_CPU_0,PRDATAS0,31,16", |

| "HWRITE": "HWRITE"                  | "/BLK_CPU/AHB2APB_CPU_0,PRDATAS1,15,0",  |

| }                                   | "/BLK_CPU/AHB2APB_CPU_0,PRDATAS1,31,16", |

| },                                  | "/BLK_CPU/TAP,p_rdata,15,0"              |

|                                     |                                          |

Figure 2. Metadata for Interfaces.

Fig 3 shows the contents for **advanced** information which describes where masters and slaves are located, how connections are made between masters and slaves, what address spaces are used for slaves, what interface protocol is used for a slave and so on. It is necessary information to generate full chip interconnection testbench.

| <pre>{     "Master_list": [         "/BLK_CPU/bbio_ahb_32_bit_filter, AHBLite_M",         "/BLK_CPU/cortex_m4, AHBLite_M_Code",         "/BLK_CPU/cortex_m4, AHBLite_M_Data",         "/BLK_CPU/cortex_m4, AHBLite_M_System",         "/BLK_CPU/udma_top, AHBLite_M"     ],     "Slave_list": [         {             {</pre> | <pre>"AHB_BUSMATRIX": {     "Instance_hierarchy": "/BLK_CPU/AHB_BUSMATRIX_MAIN_GNX",     "Sparse_connection": {         "s00_ahb_32": [             "m01_ahb_32",             "m02_ahb_32",             "m03_ahb_32",             "m04_ahb_32",             "m05_ahb_32",             "m06_ahb_32",             "m06_ahb_32",             "m06_ahb_32",             "m01_ahb_32",             "m01_ahb_32",             "m01_ahb_32",             "m01_ahb_32",             "m01_ahb_32",             "m01_ahb_32",             "m01_ahb_32",             "m06_ahb_32",             "m06_ahb_32",</pre> |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "Base_addr": "0x40006600",<br>"Interface_info": "/BLK_CPU/SYS_ALIVE/ccd_top,<br>APB_S_CCD_TOP",<br>"vlnv": {<br>"vendor": "samsung.com",                                                                                                                                                                                      | "m06_ahb_32"<br>],<br>"s01_ahb_32": [<br>"m00_ahb_32",<br>"m01_ahb_32",<br>"m02_ahb_32",                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| "version": "1.0. META"<br>},<br>"AMBA_type": "APB"<br>},                                                                                                                                                                                                                                                                      | "m05_ahb_32",<br>"m06_ahb_32"<br>],                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

Figure 3. Metadata for Interconnect Topology.

Fig 4 shows the contents for **project specific information** which needs to be considered separately. It is a code snippet of address map for a project, which is used by interconnect verification environment that generates random transactions to backbone bus. Line 2~11 describes unmapped logic and line 13~28 describes read-only region. This information is used for the policy of stimulus and checker. Since it is extended metadata for automating verification environment, it is hard to describe them with existing IP-XACT only. So we chose **yaml** to model this contents because it is simple to describe, has existing interface with Jinja for rendering.

| 1 i | wb special addr m           | nap : "'{     |                |                |               |          |              |                                    |

|-----|-----------------------------|---------------|----------------|----------------|---------------|----------|--------------|------------------------------------|

| 2   | 2 //USER CUSTOMIZATION+head |               |                |                |               |          |              |                                    |

| 3   | //MST NAME                  | E   SLV NAME  | ST ADDR        | END ADDR       | GRANULARIT    | Y   WR M | SK   PATTERN | USER DEFINE                        |

| 4   | '{,                         | , –           | 32'h200C 0000, | 32'h200C 0FFF, | 32'h1000,     | 0,       | NO ACCESS,   | <pre>}, // for unmapped test</pre> |

| 5   | ١{,                         | ,             | 32'h200C 1000, | 32'h200F FFFF, | 32'h10 0000,  | Θ,       | NO ACCESS,   | <pre>}, // for unmapped test</pre> |

| 6   | '{,                         | ,             | 32'h4000 8100, | 32'h4000 89FF, | 32'h10 0000,  | Θ,       | NO ACCESS,   | <pre>}, // for unmapped test</pre> |

| 7   | ١{,                         | ,             | 32'h4000 8A00, | 32'h4000 8BFF, | 32'h10 0000,  | Θ,       | NO ACCESS,   | <pre>}, // for unmapped test</pre> |

| 8   | '{,                         | ,             | 32'h4000 8E00, | 32'h4000_9FFF, | 32'h10_0000,  | Θ,       | NO ACCESS,   | <pre>}, // for unmapped test</pre> |

| 9   | '{,                         | ,             | 32'h4000 A300, | 32'h4000 FFFF, | 32'h10 0000,  | Θ,       | NO ACCESS,   | <pre>}, // for unmapped test</pre> |

| 10  | ١{,                         | ,             |                | 32'h4001_0FFF, | 32'h10_0000,  | Θ,       | NO_ACCESS,   | <pre>}, // for unmapped test</pre> |

| 11  | ١{,                         | ,             | 32'h4001_1900, | 32'hFFFF_FFFF, | 32'h1000_0000 | , 0,     | N0_ACCESS    | 5, }, // for unmapped test         |

| 12  |                             |               |                |                |               |          |              |                                    |

| 13  |                             | MSPI,         | Θ,             | 0,             | 32'h1000,     | 0,       |              | },                                 |

| 14  | '{,                         | BBIO_RSGN,    | Θ,             | 0,             | 32'h1000,     | Θ,       | READ_ONLY,   | },                                 |

| 15  |                             | CNT_CPU_GPIO, | Θ,             | Θ,             | 32'h1000,     | Θ,       | READ_ONLY,   | },                                 |

| 16  | '{,                         | AON_ALIVE0,   | Θ,             | 0,             | 32'h1000,     | 0,       | READ_ONLY,   | },                                 |

| 17  |                             | AON_ALIVE1,   | Θ,             | Θ,             | 32'h1000,     | Θ,       | READ_ONLY,   | },                                 |

| 18  | '{,                         | CNT_ISPEND,   | Θ,             | 0,             | 32'h1000,     | 0,       | READ_ONLY,   | },                                 |

| 19  |                             | CMU_ISPEND,   | Θ,             | 0,             | 32'h1000,     | Θ,       | READ_ONLY,   | },                                 |

| 20  | '{,                         | CNT_SENSOR,   | Θ,             | Θ,             | 32'h1000,     | Θ,       | READ_ONLY,   | },                                 |

| 21  |                             | CMU_SENSOR,   | Θ,             | 0,             | 32'h1000,     | 0,       | READ_ONLY,   | },                                 |

| 22  | ١{,                         | CNT_FE,       | Θ,             | Θ,             | 32'h1000,     | Θ,       | READ_ONLY,   | },                                 |

| 23  |                             | CNT_ISP,      | Θ,             | 0,             | 32'h1000,     | 0,       | READ_ONLY,   | },                                 |

| 24  | ۲{,                         | CMU_ISP1,     | Θ,             | 0,             | 32'h1000,     | Θ,       | READ_ONLY,   | },                                 |

| 25  |                             | CLKGEN,       | Θ,             | Θ,             | 32'h1000,     | Θ,       | READ_ONLY,   | },                                 |

| 26  | '{,                         | MEM_SENSOR,   | Θ,             | 0,             | 32'h1000,     | 0,       | READ_ONLY,   | },                                 |

| 27  |                             |               |                |                |               |          |              |                                    |

| 28  | '{,                         | ROM,          | Θ,             | 0,             | 32'h1000,     | 0,       | READ_ONLY,   | },                                 |

| 29  | ۲{,                         | ,             |                | 32'h2010_09FF, | 32'h0400,     | 1,       | READ_WRITE,  | },                                 |

| 30  | '{,                         | 1             | 32'h2010_B000, | 32'h2010_B7FF, | 32'h0400,     | 2,       | READ_WRITE,  | },                                 |

Figure 4. Metadata for project specific information

## B. Testbench Generation

The previous approach to create full-chip interconnect testbench was a manual process:

- Step 1: Extract required information for testbench from design specification documents

- Step 2: Generate testbench initial version

- Step 3: Modify testbench code according to RTL implementation spec

- Step 4: Clean-up testbench (build & compile)

- Step 5: Start verification

Current approach is able to automate from step 1 to step 4 using metadata. vBuilder (In-house verification builder to generate various target testbench such as generic IP, full-chip testbench or application specific testbench generation for register, interconnect) parses metadata of either json or IP-XACT, and generates UVM testbench

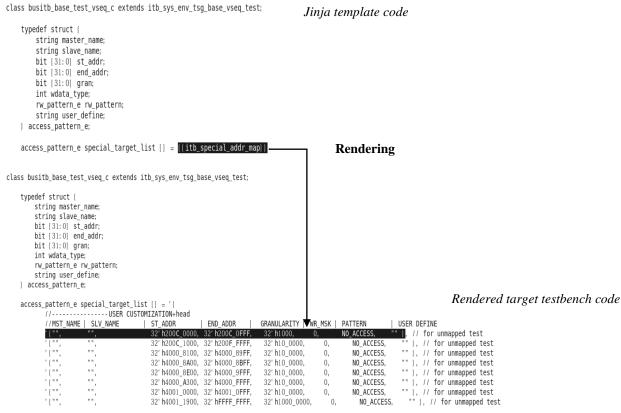

vBuilder uses **Jinja** to handle project specific metadata when generating testbench like Fig 5. It renders target testbench code by combining jinja template code with yaml data file.

Figure 5. Rendering testbench code using Jinja

#### C. Configurable Testbench Generation

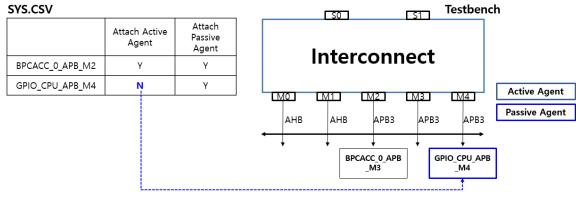

By default testbench configuration, all masters and slaves are replaced with active VIP (Verification IP) components in interconnect testbench. Active VIP master generates bus transaction to backbone bus and active VIP slave responds to backbone bus. This configuration can be used from early verification stage. However, once real IP RTLs are available later, they need to be included in interconnect testbench for performance verification or stress tests. To do that, our new approach can support this configuration update easily by changing parameters from SYS.CSV file. Fig 6. shows how to configure SYS.CSV. If "attach active agent" will be set to "N", RTL IP will be used from interconnect testbench.

Figure 6. Configurable Interconnect Testbench Generation

## D. Sign-off for Register Sanity Test using Metadata

IP-XACT and RTL are mandatory deliverables on IP hand-off and it needs to be guaranteed that IP-XACT and RTL are functionally equivalent. To reinforce this, this check requirement is added to IP sign-off system and this check can be done automatically by leveraging register testbench automation using metadata above.

IP-XACT provides the way of describing register with various attributes and they can be modeled using uvm\_reg library in UVM testbench. In order to increase the quality of register checking in IP sign-off system, the functional behaviors in UVM testbench for IP-XACT tags for **testable**, **constraint and coverage** related tags in Table 1, was customized.

| Metadata (IP-XACT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Testbench (UVM_REG)                                                                                                                                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <spirit:field><br/><spirit:name>PA_TxHsG1SyncLength_MSB</spirit:name><br/><spirit:<b>writeValueConstraint&gt;<br/><spirit:minimum>0</spirit:minimum><br/><spirit:maximum>1</spirit:maximum><br/><br/></spirit:<b></spirit:field>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <pre>class hsi_unipro16_pa_std_region_pa_txhsg2synclength_pa_txhsg2synclen_msb_c extends uvm_reg_field; constraint valid { value inside { ['h0:'h1] }; } endclass : hsi_unipro16_pa_std_region_pa_txhsg2synclength_pa_txhsg2synclen_msb_c </pre>                                                                                              |

| <pre><spirit:register> <spirit:name>COMP_OPTION_SUITE</spirit:name> <spirit:addressoffset>0x20</spirit:addressoffset> <spirit:size spirit:resolve="immediate">32</spirit:size> <spirit:field> <spirit:bitoffset>2</spirit:bitoffset> <spirit:bitwidth spirit:resolve="immediate">30</spirit:bitwidth> </spirit:field> <spirit:field> <spirit:field> <spirit:field> <spirit:field> <spirit:field> <spirit:bitoffset>1</spirit:bitoffset> <spirit:bitwidth spirit:resolve="immediate">1 <spirit:field> <spirit:field> <spirit:field> <spirit:field> <spirit:field> <spirit:field> <spirit:bitwidth spirit:resolve="immediate">1 <spirit:field> <spirit:field> <spirit:field> <spirit:bitwidth spirit:resolve="immediate">1</spirit:bitwidth> </spirit:field> <spirit:hitwidth spirit:resolve="immediate">1</spirit:hitwidth></spirit:field></spirit:field></spirit:bitwidth> </spirit:field> <spirit:field> <spirit:bitwidth spirit:resolve="immediate">1</spirit:bitwidth> 1</spirit:field></spirit:field></spirit:field></spirit:field></spirit:field></spirit:field></spirit:bitwidth> </spirit:field> </spirit:field> </spirit:field> </spirit:field> </spirit:field> 1 1 1 111     <td><pre>class hsi_unipro16_component_region_comp_option_suite_c extends uvm_reg;<br/>rand uvm_reg_field reserved_ff0;<br/>rand uvm_reg_field rx_symbol_clk1_reset_type;<br/>rand uvm_reg_field rx_symbol_clk0_reset_type;<br/>covergroup cg_vals;<br/>option.per_instance = 1;<br/>reserved_ff0: coverpoint reserved_ff0.value[29:0]<br/>{</pre></td></spirit:register></pre> | <pre>class hsi_unipro16_component_region_comp_option_suite_c extends uvm_reg;<br/>rand uvm_reg_field reserved_ff0;<br/>rand uvm_reg_field rx_symbol_clk1_reset_type;<br/>rand uvm_reg_field rx_symbol_clk0_reset_type;<br/>covergroup cg_vals;<br/>option.per_instance = 1;<br/>reserved_ff0: coverpoint reserved_ff0.value[29:0]<br/>{</pre> |

| spirit:resolve="immediate">1<br><br>                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <spirit:register><br/><spirit:name>PA_AvailTxDataLanes</spirit:name><br/><spirit:field><br/><spirit:name>PA_AvailTxDataLanes</spirit:name><br/>&lt;<b>spirit:testable&gt;false</b><br/></spirit:field></spirit:register>                             | <pre>class hsi_unipro16_pa_std_region_pa_availtxdatalanes_c extends uvm_reg;<br/>uvm_resource_db#(bit)::set(("REG::",get_full_name()},<br/>"NO_REG_HW_RESET_TESTS", 1, this);<br/>uvm_resource_db#(bit)::set(("REG::",get_full_name()},<br/>"NO_REG_ACCESS_TESTS", 1, this);</pre> |

| <spirit:register><br/><spirit:name>COMP_RESET</spirit:name><br/><spirit:field><br/><spirit:name>comp_reset</spirit:name><br/><spirit:testable<br>spirit:testConstraint="readOnly"&gt;true<br/></spirit:testable<br></spirit:field></spirit:register> | class hsi_unipro16_component_region_comp_reset_c extends uvm_reg;<br>uvm_resource_db#(bit)::set({"REG::",get_full_name()},<br>"NO_REG_ACCESS_TESTS", 1, this);                                                                                                                     |

Table 1. Metadata for Register Sanity

# III. CASE STUDY

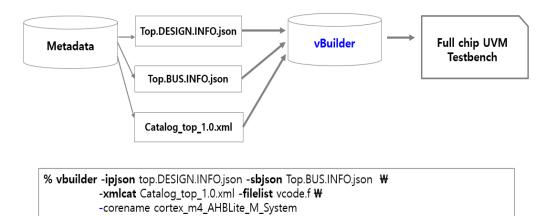

- A. Full chip Register Verification

- ✓ DUT Info

- Image Sensor (50Mp)

- ✓ Inputs

- Top.DESIGN.INFO.json: AMBA bus interface details for all masters and slaves •

- Top.BUS.INFO.json: Back-bone bus details •

- Catalog\_top\_1.0.xml: All IP-XACT information for IP/TOP (Registers, Fileset, Clock, Reset)

Figure 7. Full-chip Register Testbench Generation Flow

- Output: UVM Testbench  $\checkmark$

- Add AHB master VIP to Cortex M4 System Bus .

- Generate uvm\_reg model for all IPs •

- Generate test scenario on top of boot sequence which user provides •

- Build and run script •

✓ Generated testbench code:

| <pre>'uvm_object_utils(ccd_top_ccd_top_apb_s_ccd_top_reg_blk_c) function new(string name = "ccd_top_ccd_top_apb_s_ccd_top_reg_blk_c) endfunction: new virtual function void buil if (\$test\$plusargs("BIO_ENDIAN")) begin // If you want to set endfanness as BIO, please check th     default_map = create_map("default_map", 'UVM_REG_ADDR_W end else begin     default_map = create_map("default_map", 'UVM_REG_ADDR_W end</pre> | <pre>set cmu_sensor_cortex_m4_reg_bik.inii1dC ;<br/>set anb0_cortex_m4_abbi_ten_m_system_map, add_submap(this.cmu_sensor_cortex_m4_reg_bik.default_map);<br/>set anb1 ; Suu_cMU_SENSOR_cMU_SENSOR_APE_S_RET_FAX:<br/>set anb1 ; Suu_cMU_SENSOR_cMU_SENSOR_cMU_SENSOR_APE_S_RET_FAX:<br/>set anb1 ; Suu_cMU_SENSOR_cMU_SENSOR_cMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENSOR_CMU_SENS</pre> |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>this.ccd_en = new("ccd_en");<br/>this.ccd_en.configure(this, null);<br/>this.ccd_en.bwild();<br/>default_map.adu_reg(ccd_en, 'h80);</pre>                                                                                                                                                                                                                                                                                       | <pre>uvm_info(get_full_name(), \$psprintf("%Od_clocks_rose", 'WAIT_CLOCK_CYCLE_AFTER_RESET_ENDED), UVM_LOW) reg_access_seq = reg_access_seq_C::type_id::create("reg_access_seq"); // other rote rote rote rote rote rote rote ro</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| <pre>this.ccd_state = new("ccd_state");<br/>this.ccd_state.configure(this, null);<br/>this.ccd_state.buil(d);<br/>default_map.add_reg(ccd_state, 'h02);</pre>                                                                                                                                                                                                                                                                        | //with reset value<br>reg_access_seq.kind _ REG_HW_RESET;<br>reg_access_seq.model _ p_sequencer.p_reg_blk;<br>reg_access_seq.start(mull);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| <pre>this.ccd_jdg = new("ccd_jdg");<br/>this.ccd_jdg.configure(this, null);<br/>this.ccd_jdg.build();<br/>default_map.add_reg(ccd_jdg, 'h94);</pre>                                                                                                                                                                                                                                                                                  | // with 0 value<br>reg_access_seq.kind <mark>= REC_ACCESS_</mark> 0;<br>reg_access_seq.start( <b>null</b> );                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| <pre>this.ccd_jdg_top_chip = new("ccd_jdg_top_chip");<br/>this.ccd_jdg_top_chip.configure(this, null);<br/>this.ccd_jdg_top_chip.build();</pre>                                                                                                                                                                                                                                                                                      | // with 1's value of all bits<br>reg_access_seq.kindREG_ACCESS_1;<br>reg_access_seq.start(mull);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

Figure 9. Example code for full-chip Register Verification Testbench

# ✓ Result:

Register testbench generation is fully automated using metadata and it successfully runs as one-shot and found a few IP-XACT/RTL issues quickly. Table 2 shows total runtime for register verification in this design.

| Step                          | Time     | Iteration | Total Time |

|-------------------------------|----------|-----------|------------|

| 1. Testebench Generation Time | 00:02:49 | 1         |            |

| 2. RTL compile                | 00:00:30 | 1         | 00:38:26   |

| 3. Compile (multi-snapshot)   | 00:00:30 | 49 (IP)   |            |

| 4. Run Tests                  | 00:00:13 | 49 (IP)   |            |

Table 2. Full-chip Register Testbench Runtime

# B. Full chip Interconnect Verification

- ✓ DUT Înfo

- Image Sensor (50Mp)

- Bus Master: 5 with AHB interfaces

- Bus Slave: 12 AHB slaves, 105 APB slaves

% vbuilder -ipjson top.DESIGN.INFO.json -sbjson vbuilder\_input.json -bus

Figure 8. Full-chip Interconnect Testbench Generation Flow

- ✓ Output: UVM Testbench

- Add AHB master VIP to Cortex M4 System Bus

- Generate uvm\_reg model for all IPs

- Generate test scenarios on top of boot sequence which user provides

base\_test, one\_to\_all\_test, all\_to\_one\_test, all\_to\_all\_test, unmapped\_test

- Build and run script

#### ✓ Generated testbench code:

| //master0                                                                    | class busiwb all to all test vseq c extends busiwb base test vseq c;           |

|------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| <pre>force top.BLK CPU.bbio ahb 32 bit filter.HADDRM = HIN 00 haddr;</pre>   |                                                                                |

| <pre>force top.BLK CPU.bbio ahb 32 bit filter.HBURSTM = HIN 00 hburst;</pre> | virtual task do stimulus ();                                                   |

| force top.BLK CPU.bbio ahb 32 bit filter.HLOCKM = HIN 00 hmastlock           |                                                                                |

| <pre>force top.BLK_CPU.bbio_ahb_32_bit_filter.HPROTM = HIN_00 hprot;</pre>   | <pre>foreach(tgt_slave_list[s_idx]) begin</pre>                                |

| filter HSTZEM - HTN 00 brize:                                                | int ss = s_idx;                                                                |

| Connect VIP to DUT                                                           | <pre>access_pattern_e tmp_access_route_list[\$];</pre>                         |

| cdn ahb active master sv #(                                                  | <pre>access_pattern_e tmp_route_consider_except[];</pre>                       |

| .interface soma(interface soma),                                             |                                                                                |

| . ADDR WIDTH(ADDR WIDTH),                                                    | H Make Route List                                                              |

| .DATA WIDTH(DATA WIDTH),                                                     | <pre>foreach(src_master_lis)[ss][m_idx]) begin</pre>                           |

| RESP WIDTH (RESP WIDTH)                                                      | int mm = m idx                                                                 |

| ) i shell cis tb top top BLK CPU bbio ahb 32 bit filter AHBLite M(           | access_pattern_e access_region;                                                |

| .AHB HCLK(aclk0 clk),                                                        | access_region.master_name = src_master_list[ss][mm];                           |

| .AHB HRESET(nReset0 resetN),                                                 | access_region.st_addr = 0;                                                     |

| AHB HADDR out (AHB HADDR out HIN 00 haddr),                                  | access_region.end_addr = 0;                                                    |

| AHB HBURST out (AHB HBURST out HIN 00 hburst).                               | access_region.gran = 32'h1000;                                                 |

| AHB HLOCK (AHB HLOCK HIN 00 hmastlock).                                      | access_region.wdata_type = 0;                                                  |

| AHB HPROT out (AHB HPROT out HIN 00 hprot),                                  | access_region.rw_pattern = READ_WRITE;                                         |

| AHB HSIZE out (AHB HSIZE out HIN 00 hsize),                                  | access_region.user_define = "";                                                |

| AHB HTRANS out (AHB HTRANS out HIN 00 htrans),                               | access_region.slave_name = tgt_slave_list[ss];                                 |

| AHB HWDATA out (AHB HWDATA out HIN 00 hwdata)                                | <pre>tmp_access_route_list.push_back(access_region);</pre>                     |

| AHB HWRITE out (AHB HWRITE out HIN 00 hwrite).                               | end                                                                            |

| AHB HRDATA(HIN 00 hrdata AHB HRDATA),                                        | make pattern list with exception ( and list (the passes much list)             |

| .AHB HREADY(out1 AHB HREADY),                                                | <pre>make_pattern_list_with_exception( .ref_list(tmp_access_route_list),</pre> |

| .AHB HRESP(HIN 00 hresp AHB HRESP),                                          | .result list(tmp route consider except) );                                     |

| .AHB HGRANT(tie i shell cis to top top BLK_CPU bbio ahb 32 bit fi            |                                                                                |

| .AHB HMASTLOCK(tie i shell cis to top top BLK CPU bbio ahb 32 bit            | <pre>foreach(tmp_route_consider_except[t_idx]) begin</pre>                     |

| .AHB HSEL(sink i shell cis tb top top BLK CPU bbio ahb 32 bit fil            | int ii = t idx                                                                 |

| b_top_top_BLK_CPU_bbio_ahb_32_bit                                            | ham = tat slave list(ss)                                                       |

| Instantiate VIP b_top_top_BLK_CPU_bbio_ahb_32_bit                            | all masters to all slaves test                                                 |

|                                                                              |                                                                                |

Figure 10. Example code for full-chip Interconnect Verification Testbench

#### ✓ Result

Table 3 shows total runtime for sanity test scenario of interconnect testbench generated by vBuilder. This sanity tests consisted of one master to one slave access test, one master to all slave access test, all masters to one slave access test.

| Step                                             | Time     | Iteration | Total Time |  |

|--------------------------------------------------|----------|-----------|------------|--|

| 1. Testebench Generation Time                    | 00:04:39 | 1         |            |  |

| 2. Build simulation snapshot                     | 00:03:18 | 1         | 02:07:57   |  |

| 4. Run Sanity Test                               | 00:10:00 | 12        |            |  |

| Table 3 Full chin Interconnect Testbench Puntime |          |           |            |  |

Table 3. Full-chip Interconnect Testbench Runtime

#### IV. RESULT

The setup time for interconnect testbench of SOC design used to take two weeks with previous approach at the flagship mobile AP SOC project because it requires many iterations due to mismatches between RTL and testbench. However, the proposed metadata based testbench generation approach reduces this setup time in a day by removing manual process and human-errors. In addition, since interconnect testbench automation can generate target testbench having different configuration of VIP/RTL agents automatically, the scope of verification is easily extended to performance verification, power estimation. The accuracy for performance and power analysis is increased by including key RTL agents like DRAM.

As IP and full chip sign-off for register access test can be performed easily using vBuilder(metadata), the quality of RTL was improved from early stage of design cycle. Thus, verification engineers can focus on functional verification from the beginning. Prior to vBuilder, it requires many iterations due to the mismatch between RTL and specification documents.

### V. CONCLUSION

In this paper, we present new methodology regarding how to automate register and interconnect testbench generation using design spec metadata. It contributes to reduce testbench setup time for SOC design from two weeks to one day as well as removing debug efforts due to the discrepancy between RTL design and testbench. Moreover, we can significantly improve the verification quality of register and interconnect verification with this automated approach and it helps us extend verification coverage, start complex function test quickly.

# REFERENCES

- IEEE Standard for Universal Verification Methodology Language Reference Manual, " in IEEE Std 1800.2-2017, 26 May 2017

- [2] IEEE Standard for SystemVerilog--Unified Hardware Design, Specification, and Verification Language, " in IEEE Std 1800-2017 (Revision of IEEE Std 1800-2012), 22 Feb. 2018

- [3] IP-XACT, <u>https://en.wikipedia.org/wiki/IP-XACT</u>

- [4] Accellera, <u>https://www.accellera.org</u>

- [5] Introducing JSON, <u>https://www.json.org</u>