# Low Power Extension in UVM Power Management

Silicon Interfaces<sup>®</sup> www.siliconinterfaces.com

Priyanka Gharat (<u>priyanka@siliconinterfaces.com</u>), Avnita Pal (<u>avnita@siliconinterfaces.com</u>), Shikhadevi Katheriya (<u>shikha@siliconinterfaces.com</u>)

Abstract- Incorporating Power Architecture either is in conjunction with or in sequence to functional verification using different languages, many times with different team members using different tools, and divergent approaches leading to potential errors, almost a fourth dimension to our strategy leveraging the test bench architecture. Industry seems to be following a parallel path with respect to Methodologies based test bench Power Architecture, including Unified Power Formats (UPF Both are fundamental requirements to IP and ASIC verification especially in the power saving mobile world. It would be more efficient to do Methodologies based Functional Verification and Coverage interleaved with Low Power Implementation. We have noted previous works in power libraries for VMM and have corrected shortfalls and failings and have modified suitably to work within UVM, which is a much-enhanced Methodology.

# I. INTRODUCTION

This Poster demonstrates Power Libraries classes built in System Verilog (UVM\_Power) expanding UVM Package Library with Power Domains, Supply Sets, Switches, States and Low Power Strategies as Base Class which may be used within UVM Environment. These Power Base Classes are further built for multi-Cores, Bus Interface, Memory, Etc.

This proposal is to interleave Functional Verification Methodology and Power Architecture in a single existing and widely deployed methodologies-based platform, like UVM.

- With low power strategies, based on UPF and multi-core extensions, a low power or power aware designer or verification engineers would now be able to have a strategy/plan whilst the design/verification is being undertaken.

- As the needs for smaller and Low Power Aware designs needs increase doing the Power Architecture Strategy, especially the Verification as an afterthought post Functional Verification may lead to unwanted re-spins detrimental to costs as well as time to market guidelines.

- Bringing in Power Verification at an earlier stage will bring down the total time for incorporating power strategies resulting in far shorter design cycles.

# **II. DESIGN AND IMPLEMENTATION**

An overall UPF structure is created using UVM classes which include different tasks such as creating power domains, different scopes then supply nodes for each of the domains which are created. These classes are used as library and can be extended for creating structures based on DUT/SOC architecture.

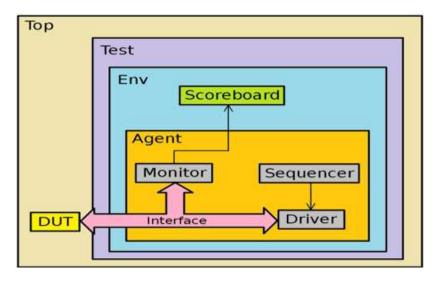

Fig 1. Hierarchical Structure of UVM

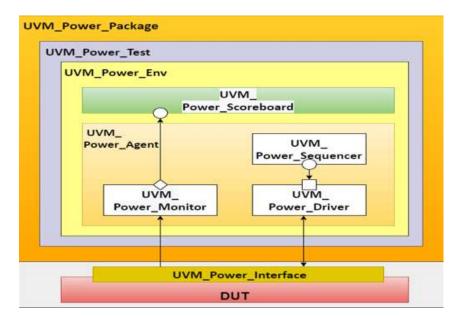

Fig 2. Hierarchical Structure of UVM Power Domain

# III. UVM POWER PACKAGE ARCHITECTURE

System Verilog Package declared for Low Power UVM\_LP (similarly to power formats used in UPF) and have either a single base class for LP with tasks and functions defined for create\_power\_domains, create\_supply\_ports for domains and logic ports for switches, create supply\_nets (VDD, VSS for each power-domains) and logic\_nets for switches, connect\_supply\_nets to ports, associate supply\_nets, create port & power states & tables, and then for strategies, like level shifters, isolations & retention – logic ports/nets and set the library cells for isolation and retention

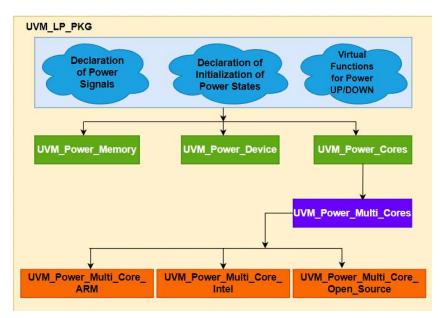

Top level consists of base class (UVM\_power) and various extended packages for- UVM\_power\_device, UVM\_power\_memory, UVM\_power\_core and further class extend for UVM\_power\_multicore, UVM\_power\_ARM, UVM\_power\_Intel, UVM\_power\_OPEN\_SOURCE extending UVM\_power\_core.

The base class has several predefined methods (functions and tasks) in the design-

- Power Domains

- Supply sets/nets

- Connect Supply sets to Power Domains.

- Switches With signals, like Wait\_For\_Interrupt; Wait\_For\_Event; Delay time for power down; Enable wakeup timer interrupt before power down.

- States normal, standby, connect\_standby, retention, sleep, dormant, deepsleep, hibernate, power\_down\_state; {c0,c1,c2,c3,c4,c5,c6,c7,c8} power\_up\_state.

- Assign States to Supply sets.

- Strategies for Level Shifters, Retention and Isolation.

- Mapping Strategies to Libraries.

- Virtual functions, tasks & sub-routines for power up and power down, state transitions, etc

The template UVM has UVM\_power\_test top, UVM\_power\_Agent, UVM\_power\_Sequence, UVM\_power\_Driver, Monitor, Score board, etc..

Fig 3. Flowchart of UVM Low Power Package

# IV. ARCHITECTURE OF UVM\_POWER PACKAGE FOR MULTI-CORE

Here we are framing an example which is an ARM processor or cluster with single core or it can be formed with multi core processor needed to create a System Verilog encapsulated class with inbuilt task and functions defined in it for Low Power UVM package.

The top level consists of base class (ARM\_Muli\_cluster\_UVM\_LP\_TEST) and various extended packages for-UVM\_Power\_Agent, UVM\_power\_multi\_cluster\_transaction, UVM\_power\_sequencer, UVM\_power\_driver. Also there will be several agents for multiple protocols and interfaces like UVM\_Power\_Agent\_PCIe, UVM\_Power\_Agent\_AXI, UVM\_Power\_Agent\_ARM\_CHI etc. for large SoC design.

| 20.000 | UVM Power Agent<br>Willi cluster UVM Low Power class Environment<br>UVM Power Agent<br>UVM Low Power<br>Muhi cluster Transation<br>Muhi cluster Transation<br>Field Dower seman<br>PCle power seman<br>UVM Power Sequencer<br>UVM Power Sequencer |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -      | ARM LOW Power AMBA CHI- 5 ACP AXI BUS                                                                                                                                                                                                             |

Fig 4. Hierarchical view of UVM Low Power Package for multi core

### V. EVIDENCE: INCORPORATING UVM\_POWER PACKAGE TO UVM

We are providing the sample code for the UVM Power Package as defined and which may be incorporated in UVM Libraries package uvm power pkg; import uvm pkg::\*; class uvm\_low\_power; //'uvm component utils(uvm low power); - Factory Registration //function new (string name, uvm component uvm low power); //endfunction : new – Construction class low power; function string create power domain(input string domain name, input string states, input int index); string power domain[]; power domain=new[index]; for(int i=0;i<index;i++) begin power domain[i] = {"PD ",domain name}; // domain created here return power domain[i]; end endfunction function string create\_supply\_port (input string in\_port, input string type\_of\_signal);

if(type\_of\_signal=="power\_high")

return {in\_port,"\_VDDH"}; ...

else if(type\_of\_signal=="power\_low")

return {in\_port,"\_VDDL"};

else if(type\_of\_signal=="ground")

return [in\_port,"\_VDDL"]; return {in port," VSS"}; else return "NULL"; endfunction function string create supply net(input string in signal, input string type of signal); if(type\_of\_signal=="power") return {in signal," Pwr"}; else if(type of signal=="ground") return {in signal," Gnd"}; else return {in signal," net"}; endfunction function string connect\_supply\_net(input string in\_port, input string in\_net); return {in\_port,"\_",in\_net}; endfunction function bit isolation cell(input in signal); isolation cell = in signal;endfunction function bit retention cell(input in signal, restore); reg memory; memory = in signal; if(restore == 1) // when restore is enabled then the signal is available at the o/p side. retention cell = memory; endfunction

function bit power\_switch(input in\_signal,switch\_control);

if(switch\_control == 1)

power\_switch = in\_signal;

else

power switch = 1'bx;

endfunction endclass endpackage

# V. EVIDENCE: INCORPORATING UVM\_POWER PACKAGE TO UVM

As you can see invoking the Low Power Package is as simply as "A" "B" "C" and the good part is that the "A" will come as part of the Low Power Package. In step B, we have included the library package and the header files as well as writing the test bench with instantiating the necessary classes, etc. The Low Power Class can be extended and run the necessary build, connect and run phases.

In Step C here we are passing a dynamic array of the top level modules present in the DUT which would need to have Power Domains. These are typically already instantiated in the test bench top module and can be extracted using an external python script. The calls to the functions will return the value as required in our Low Power domain.

## A. Defining Low Power Macros

`define uvm\_object\_utils(T) `define uvm\_field\_string(ARG,FLAG) `define uvm\_field\_object(ARG,FLAG) `define uvm\_field\_int(ARG,FLAG) //`define uvm\_field\_queue\_int(ARG,FLAG)

//`uvm\_object\_utils\_begin(TYPE) //`uvm\_field\_\* macro invocations here //`uvm\_object\_utils\_end

class lp\_uvm\_macros extends uvm\_object; string str; lp\_uvm\_macros subdata; int field; lnt queue{\$]; `uvm\_object\_utils\_begin(lp\_uvm\_macros) `uvm\_field\_string(str, UVM\_DEFAULT) `uvm\_field\_object(subdata, UVM\_DEFAULT) `uvm\_field\_object(subdata, UVM\_DEFAULT) `uvm\_field\_queue\_int(queue, UVM\_DEFAULT) `uvm\_object\_utils\_end endclass

#### B. Importing UVM Low Power in TB

`include "pkg\_lp.sv"

`include "uvm\_macros.svh"

//`include "lp\_uvm\_macros.svh"

import uvm\_pkg::\*;

import uvm\_power\_pkg::\*;

#### module tb;

reg clock, reset; string domains[]; string states[]; int i; mymod mm(clock,reset);

class lp extends low\_power;

//build phase

function void build\_phase(uvm\_phase phase);

endfunction

//connect phase

function void connect\_phase(uvm\_phase phase);

endfunction

//run phase

task run\_phase(uvm\_phase phase);

phase.raise\_objection(this);

begin

uvm\_top\_sequence seq;

seq=uvm\_top\_sequence::type\_id::create("seq");

#5;

seq.start(sequencer);

end

phase.drop\_objection(this);

endtask

endclass

C. Instantiating Power Classes

lp lp1;

initial begin clock = 0; lp1 = new(); i=3; // index domains=new[i]; domains='("USB", "DMA", "CPU", "WISHBONE"}; #40 Sfinish; end always

begin #5 clock = ~clock; end

always @(posedge clock)

begin

port=lp1.create\_supply\_port(domains[j],"power\_medium");

net=lp1.create\_supply\_net(domains[j],"power");

j++;

end

// instances of the low-power module

// isolation\_celliso();

// retention\_cell ret();

endmodule

# VI. EVIDENCE: EXTENDING UVM\_POWER PACKAGE FOR MULTI-CORE

As given in IV, this is code incorporating the UVM Power Libraries and extending the same to multi-core, particularly for powerup and powerdown.

#### class my\_power extends uvm\_power;

//`uvm\_component\_utils(my\_power) Factory Registeration

//Constructor function new(string name = "", uvm\_component parent); super.new(name,parent); endfunction uvm\_power power;

initial begin

power = new();

// down\_state =

uvm\_power\_pkg::uvm\_power::c1;

power.powerup(2);

power.powerdown(3);

power.sequential\_power\_down\_up\_multi\_core\_f(); power.power\_up\_another\_core\_f();

end

package uvm\_power\_pkg; class uvm\_power; //signals rand bit Wait For\_interrupt; rand bit Walt\_For\_Event; rand bit Delay\_time\_for\_power\_down; rand bit Enable\_wakeup\_timer\_interrupt\_before\_power\_down; **Hatates** typedefenum (modern\_standby,connect\_standby,sleep,hibemate,time\_o ff\_brake}power\_down\_state; typedefenum (c0,c1,c2,c3,c4,c6,c7,c8) power\_up\_state; power\_down\_state down\_state; power\_up\_stateup\_state; virtual function int powerup (input [2:0] up\_state); begin case(up\_state) c0: begin Sdisplay("it is in active mode"); and c1: Sdisplay("Auto halt"); c2: Sdisplay("Temporary state"); c3: \$display(" i1 and i2 caches will be flush"); c4: Sdisplay("CPU is in deep sleep"); c6: Sdisplay("Saves the core state before shutting"); c7: \$display("c6+LLCmay be flush"); c8: Sdisplay("c7+LLC may be flush"); endcase end endfunction

//build phase

function void build\_phase(uvm\_phase phase);

endfunction

//connect phase

function void connect\_phase(uvm\_phase phase);

endfunction

//run phase

task run\_phase(uvm\_phase phase);

phase.raise\_objection(this);

begin

uvm\_top\_sequence seq;

seq =

uvm\_top\_sequence::type\_id::create("seq");

#5;

seq.start(sequencer);

end

phase.drop\_objection(this);

endtask

endclass

virtual function int powerdown (input [2:0]power\_down); begin case(down\_state) modem standby; begin \$display("It is in modern standby mode"); and sleepbegin Sdisplay("It is in sleep mode"); end hibemate: begin Sdisplay("It is inside hibemate state and data is moved from RAM TO ROM"); end. connect standby begin Sdisplay["It is connect\_standby"]; end time\_off\_brake: begin Sdisplay("no operation is performed"); end endcase end endfunction endclass //Memory class class uvm power, memory extends uvm power; //Code needs to be written function new(); super.new(); \$display("It is inside uvm\_power\_memory"); //Device

class uvm\_power\_device extends uvm\_power;

//Code needs to be written

function new();

super.new(); \$display("It is inside uvm\_power\_device"); endfunction endclass //core class uvm power core extends uvm power: //Code needs to be written function new(); super.new(); Sdisplay("It is inside uvm\_power\_core"); endfunction virtual function power\_down\_another\_core\_f(); Sdisplay("It is inside power down another core"); endfunction virtual function power\_up\_another\_core\_f(); //needs to be written Sdisplay("It is inside power up another core"); endfunction endclass class uvm\_power\_multi\_core extends uvm\_power\_com: typedefstruct [ bit [3:0]NO\_OF\_CORES; bit [3:0]NO\_OF\_CORES\_W\_PROC bit [3:0]NO\_OF\_PROC\_IN\_CLUSTER; bit [3:0]NO\_OF\_CLUSTER; multi\_core; virtual function power\_up(); // needs to be written Sdisplay (it is inside power up multi core endfunction endclass

RESULT Temporary state It is in modern standby mode it is inside sequential\_power\_down\_up\_multi\_core\_f It is inside power up another core VCS Simulation Report

# CONCLUSION

Incorporating Power Management architecture within UVM methodologies alleviates challenges of functional verification engineer and power management divide. We proposed in-built Power Domain Classes as extension to UVM Package as the Library may be extended to Devices, multi-Cores, Memories, Bus Interface, etc. giving one package for implementation ease. Consolidation of Functional Verification and Power Management will lead to reduced verification time and better chance to meet the time to market deadlines.

# References

[1] UVM Community (accellera.org) https://accellera.org/community/uvm

[2] Guide to changes in IEEE 1801-2013 (UPF 2.1) (techdesignforums.com)

[3] Verification Methodology Manual for Low Power https://www.synopsys.com/company/resources/synopsys-press/vmm-low-power.html