Simon Davidmann and Lee Moore, Imperas Software simond@imperas.com, moore@imperas.com

© Imperas Software

## imperas

#### Focus of this tutorial

- RISC-V is changing the options that SoC designers have in their tool kits

- RISC-V means many teams are designing new processors, or modifying source of processors

- For RISC-V anybody can be 'an architecture licensee'

- And every CPU needs verifying... in detail... (its not like buying in pre-verified IP)

- Many people are new to CPU DV for the first time

- Traditionally done behind closed doors in commercial/proprietary companies

- This presentation aims to introduce the main approaches of RISC-V CPU DV

- And discusses pros and cons of the different approaches

- Also it introduces the main components needed in any RISC-V processor DV environment

## RISC-V processor verification tutorial Items to be covered, main takeaways

- Introduction to RISC-V

- Overview of the issues when verifying the design of a RISC-V CPU

- Different approaches to verifying a RISC-V CPU

- Main components of a verification testbench

- Introduction to simulators for RISC-V CPUs

- Use of various virtual platform components in verification

- Discussion of different reference model requirements

- Introduction to instruction stream generators

- Status of RISC-V compliance and its relationship to verification

- Pointers to some useful architectural validation test suites

- Understanding a complete SystemVerilog testbench via a detailed walk through demonstration

## Introduction to Imperas Involvement with RISC-V

- Imperas develops simulators, tools, debuggers, modeling technology, and models to help embedded systems developers get their software running...

- ...and hardware developers get their designs correct

- 14+ years, self funded, profitable, UK based, team with much EDA (simulators, verification), processors, and embedded experience

- Staff worked in Arm, MIPS, Tensilica, Cadence, Synopsys

- and in verification in EDA on development of Verilog, VCS, SystemVerilog, Verisity and their methodologies

- Started work with customers on RISC-V in 2017

- Contributed to RISC-V compliance since 2018, RISC-V DV since 2019

- Our RISC-V focus is CPU verification

- We provide configurable reference models, the fastest highest quality simulators, advanced development tools and the absolute best solution for RISC-V hardware design verification

- 20+ of the leading RISC-V CPU developers use and rely on Imperas solutions

www.imperas.com

www.OVPworld.org

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- Components of RISC-V CPU DV environment

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- Components of RISC-V CPU DV environment

For each topic and item we will try to introduce, explain, even demo technologies and products that are available – to give you a feeling of current state-of-the-art

We will also introduce and walk through some open source solutions

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- Components of RISC-V CPU DV environment

### **RISC-V History**

- RISC-V (pronounced "risk-five") is an open standard instruction set architecture (ISA) that began in 2010 and is based on established reduced instruction set computer (RISC) principles

- Unlike most other ISA designs, RISC-V is provided under open source licenses that do not require fees to use

- The project began in 2010 at the University of California, Berkeley, but now many current contributors are volunteers not affiliated with the university

- Unlike other academic designs which are typically optimized only for simplicity of exposition, the designers intended that the RISC-V instruction set be usable for practical computers

#### RISC-V == Freedom...

Freedoms enabled by RISC-V are a huge opportunity

Freedoms enabled by RISC-V are a huge opportunity

Freedoms enabled by RISC-V are a huge challenge for verification

the largest change in the industry since? ...

#### Challenges in RISC-V CPU DV

- Feature selection and choices require serious consideration due to implications of every choice

- Experienced architecture teams know the costs associated with every feature

- Every addition dramatically increases (doubles?) verification & compounds verification complexity

- Costs of simple added feature can be huge and unknown to inexperienced teams

- Adds schedule, resources, quality costs == big risks...

- As of 2021, No off-the-shelf toolkit/products available for DV of processors

- No EDA vendor has 'RISC-V CPU DV kit' product

- There are in-house proprietary solutions in CPU developers... Intel, AMD, Arm, ...

- Building your own adds schedule, resources, quality costs and risks

- Current SoC cost is 50% for HW DV (with CPUs bought in as proven IP)

- Developing own CPU adds huge DV incremental schedule, resources, quality challenges

- Brief Introduction to RISC-V

- Processor DV project timeline

- RISC-V CPU HW DV approaches

- Components of RISC-V CPU DV environment

## A CPU HW DV project timeline

- Source/build/hire/allocate the expert team to do the work...

- Focus on what needs to be verified develop measurement metrics

- Develop Verification Plan (and measurement metrics)

- Determine EDA tools and models and methods to be used

- Simulation choices: open source, commercial, bespoke, SystemVerilog, UVM, FPGA, Emulation, ...

- Formal...

- Get tools, verification IP (VIP), testbenches, models in place

- Obtain tests, create tests

- Generate huge number of (constrained random) tests

- Verify, triage and fix issues, continue...

- ... continue while measuring until functional and code coverage metrics reached

- Benchmark, soak and integration testing

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- Components of RISC-V CPU DV environment

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- Components of RISC-V CPU DV environment

During this section, several components will be mentioned... like ISS, and ISG – these may be introduced as we go, or may be discussed in more detail in later sections of this tutorial

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- #0 "hello world" test

- #1 self checking tests (e.g. Berkeley torture tests pre2018)

- #2 Post simulation trace log file compare (e.g. Google riscv-dv 2019)

- #3 sync-lock-step-compare (e.g. CV32E40P in OpenHW 1H 2020)

- #4 async-lock-step-compare (e.g. CV32E40P in OpenHW 2H H2020)

- #5 test bench use of standards (RVVI) (e.g. CV32E40X/S in OpenHW 2021)

- Components of RISC-V CPU DV environment

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- #0 "hello world" test

- #1 self checking tests (e.g. Berkeley torture tests pre2018)

- #2 Post simulation trace log file compare (e.g. Google riscv-dv 2019)

- #3 sync-lock-step-compare (e.g. CV32E40P in OpenHW 1H 2020)

- #4 async-lock-step-compare (e.g. CV32E40P in OpenHW 2H H2020)

- #5 test bench use of standards (RVVI) (e.g. CV32E40X/S in OpenHW 2021)

- Components of RISC-V CPU DV environment

Note that not all projects have the same requirements, schedule or verification needs – so each project's DV needs may / will differ

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- #0 "hello world" test

- #1 self checking tests (e.g. Berkeley torture tests pre2018)

- #2 Post simulation trace log file compare (e.g. Google riscv-dv 2019)

- #3 sync-lock-step-compare (e.g. CV32E40P in OpenHW 1H 2020)

- #4 async-lock-step-compare (e.g. CV32E40P in OpenHW 2H H2020)

- #5 test bench use of standards (RVVI) (e.g. CV32E40X/S in OpenHW 2021)

- Components of RISC-V CPU DV environment

#### #0: 'Hello World' DV

- "if I can get a program to run then my DV is done... right?"

- "my DV challenge is sorted if I can get Linux to boot on my design..."

- Basically this level of DV is where developer feels if they can get their current compilation of their current program to run (through one path) - then their silicon design job is done

- This may be fine for test chips, research, academic, hobbyists, but NOT for products

- This approach is often due to lack of knowledge or interest in quality, ...

#### 'Hello World' DV

• This requires either an HDL simulator, or an FPGA, or some silicon, and a test harness of some form to allow it to run programs...

This is not DV!

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- #0 "hello world" test

- #1 self checking tests (e.g. Berkeley torture tests pre2018)

- #2 Post simulation trace log file compare (e.g. Google riscv-dv 2019)

- #3 sync-lock-step-compare (e.g. CV32E40P in OpenHW 1H 2020)

- #4 async-lock-step-compare (e.g. CV32E40P in OpenHW 2H H2020)

- #5 test bench use of standards (RVVI) (e.g. CV32E40X/S in OpenHW 2021)

- Components of RISC-V CPU DV environment

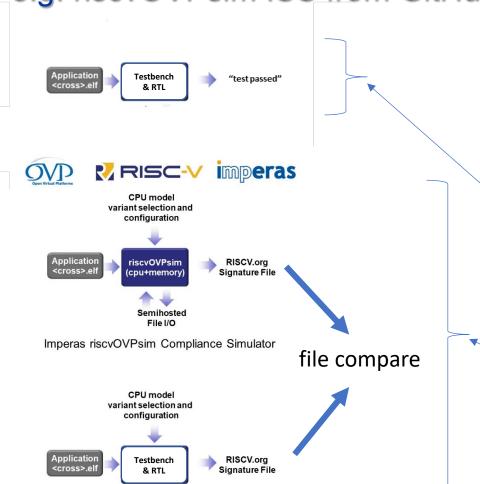

#### #1: Simple (results) check (1a)

Run RTL DUT in testbench

- (no real testbench)

- Just loads & runs the test program

- Each test program checks its results = go/no go test

- Prints message to log

- or writes bit to memory

#### #1: Simple (results) check (1b)

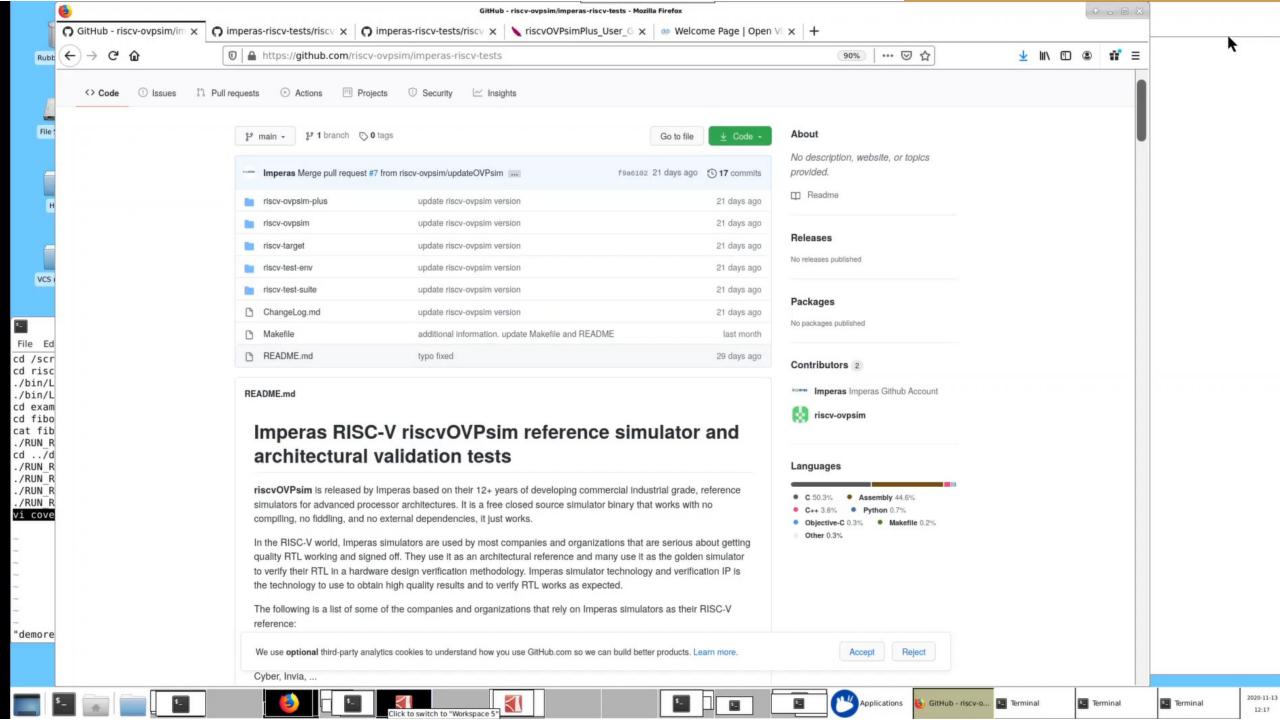

(use e.g. riscvOVPsim ISS from GitHub)

- Run RTL DUT in testbench

- (no real testbench)

- Just loads & runs the test program

- Either

- Each test program checks its results = go/no go test

- Prints message to log

- or writes bit to memory

- Or, then run ISS, write log or signature file

- Compare/diff file results (afterwards)

- This is the approach taken by RISCV International for their architectural validation ("compliance tests")

#### #1: Simple check

(use e.g. riscvOVPsim ISS from GitHub)

- Summary

- Very simple, needs basic ISS, and tool chains

- Free ISS: <a href="https://github.com/riscv-ovpsim">https://github.com/riscv-ovpsim</a>

- Free compiler: <a href="https://github.com/lmperas/riscv-toolchains">https://github.com/lmperas/riscv-toolchains</a>

- Basic bring up

- Good for simple test runs

- Basic functionality testing

- Still need accurate, configurable, version selectable, complete, reference model

- Not a robust DV solution

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- #0 "hello world" test

- #1 self checking tests (e.g. Berkeley torture tests pre2018)

- #2 Post simulation trace log file compare (e.g. Google riscv-dv 2019)

- #3 sync-lock-step-compare (e.g. CV32E40P in OpenHW 1H 2020)

- #4 async-lock-step-compare (e.g. CV32E40P in OpenHW 2H H2020)

- #5 test bench use of standards (RVVI) (e.g. CV32E40X/S in OpenHW 2021)

- Components of RISC-V CPU DV environment

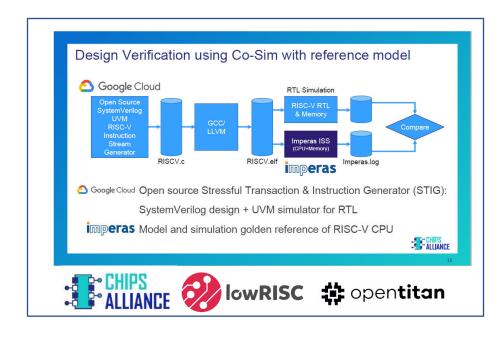

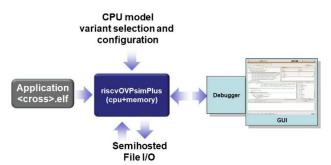

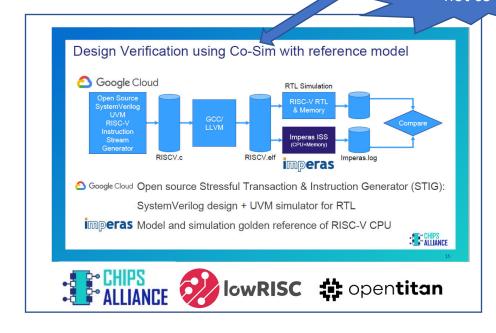

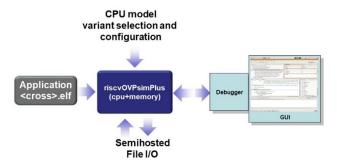

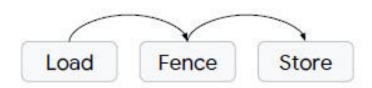

## #2: Entry Level DV: post-sim trace-compare (use e.g. riscvOVPsimPlus ISS from OVPworld)

Imperas riscvOVPsimPlus Reference Simulator

Page 31

- Process

- use random generator (ISG) to create tests

- during simulation of ISS write trace log file

- during simulation of RTL write trace log file

- at the end of both runs, run logs through compare program to see differences / failures

- ISS: riscvOVPsimPlus includes Trace and GDB interface

- Free ISS: https://www.ovpworld.org/riscvOVPsimPlus

- ISG: riscv-dv from Google Cloud / Chips Alliance

- Free ISG: https://github.com/google/riscv-dv

# #2: Entry Level DV: post-sim trace-compare (use e.g. riscvOVPsimPlus ISS for Note: This is not co-sim...

Imperas riscvOVPsimPlus Reference Simulator

- Process

- use random generator (ISG) to create tests

- during simulation of ISS write trace log file

- during simulation of RTL write trace log file

- at the end of both runs, run logs through compare program to see differences / failures

- ISS: riscvOVPsimPlus Includes Trace and GDB interface

- Free ISS: https://www.ovpworld.org/riscvOVPsimPlus

- ISG: riscv-dv from Google Cloud / Chips Alliance

- Free ISG: https://github.com/google/riscv-dv

## #2: Entry Level DV: post-sim trace-compare (use e.g. riscvOVPsimPlus ISS from OVPworld)

#### Summary

- Compares files created after test runs

- Can be signature, logging, or instruction trace

- Can use random ISG as no need to know expected results...

- Usually the easiest method to implement (dependent on tracing formats)

- Capture of program flow (monitor the PC)

- Capture of program data (monitor the Registers)

- Potentially very large data files

- Potential for wasteful execution (if early failure)

- Will not work for on async events, control flow, or hardware real time effects, MP, OoO, multi-issue, ...

- Not a robust DV solution for commercial cores

- Can engage with Imperas for licenses of reference models and optional development to add customer own instructions, CSR, behaviors

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- #0 "hello world" test

- #1 self checking tests (e.g. Berkeley torture tests pre2018)

- #2 Post simulation trace log file compare (e.g. Google riscv-dv 2019)

- #3 sync-lock-step-compare (e.g. CV32E40P in OpenHW 1H 2020)

- #4 async-lock-step-compare (e.g. CV32E40P in OpenHW 2H H2020)

- #5 test bench use of standards (RVVI) (e.g. CV32E40X/S in OpenHW 2021)

- Components of RISC-V CPU DV environment

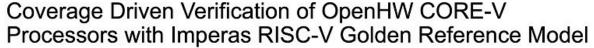

# #3: Industrial Quality Sync DV (sync-lock-step-compare)

Example flow:

- Tandem lockstep run both reference and DUT run together in lock step

- Not very complex to obtain, set up

- Compare PC, CSRs, GPRs, other internal state instruction by instruction

- No requirement on data saving

- No requirement on known good results in test

- Will not work for async events and control flow,

... it is all about the data flow

- [OpenHW evolved into using async see later slides]

Page 35

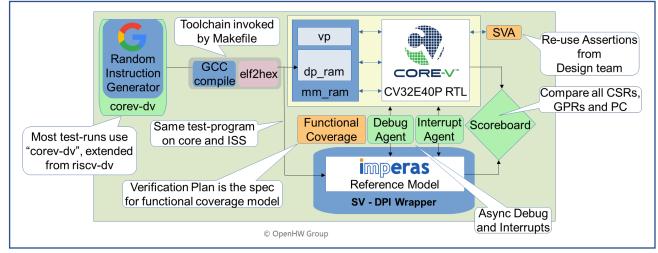

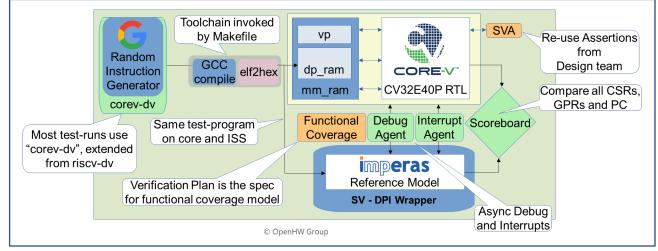

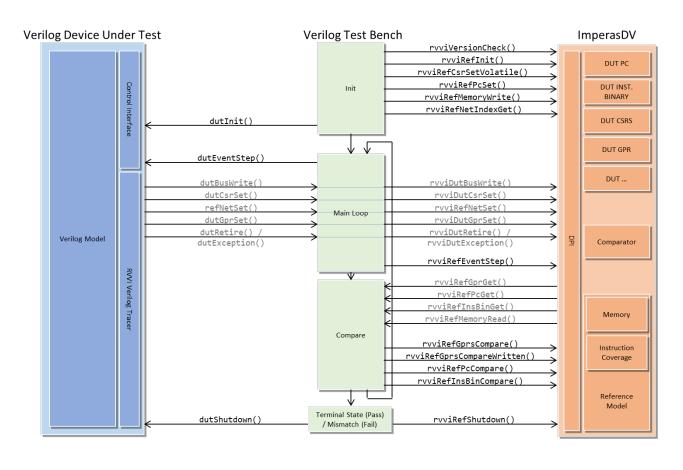

- SystemVerilog UVM Step and Compare flow using Imperas Reference Model

- Imperas OVP model is encapsulated into SystemVerilog testbench module

- Control block steps both CPUs, extracting data and comparing results

1st Generation OpenHW flow (1H2020)

# #3: Industrial Quality Sync DV (sync-lock-step-compare)

#### Summary

- Instruction by instruction lockstep comparison (excludes async events)

- Comparison of execution flow

- Comparison of program data

- Comparison of programmers and internal state

- Immediate comparison

- Allows for debug introspection at point of failure very powerful

- Does not waste execution cycles after failure

- Will not work for async events, control flow, or hardware real time effects, ...

- Not too hard to develop & set up (depends on RTL DUT tracer features)

- Lock-Step / Compare is by far the best and most efficient approach

- But does not address async events (see level #4)

- Need to engage with vendors such as Imperas for licenses of reference models and optional development to add customer own instructions, CSR, behaviors

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- #0 "hello world" test

- #1 self checking tests (e.g. Berkeley torture tests pre2018)

- #2 Post simulation trace log file compare (e.g. Google riscv-dv 2019)

- #3 sync-lock-step-compare (e.g. CV32E40P in OpenHW 1H 2020)

- #4 async-lock-step-compare (e.g. CV32E40P in OpenHW 2H H2020)

- #5 test bench use of standards (RVVI) (e.g. CV32E40X/S in OpenHW 2021)

- Components of RISC-V CPU DV environment

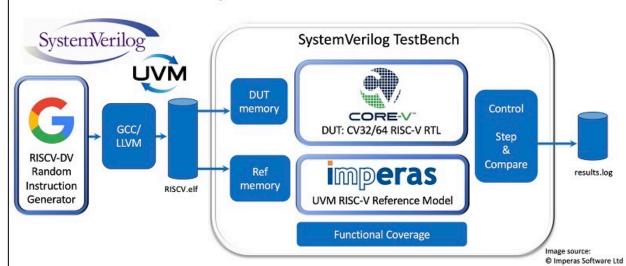

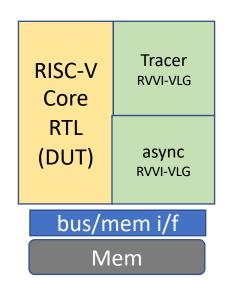

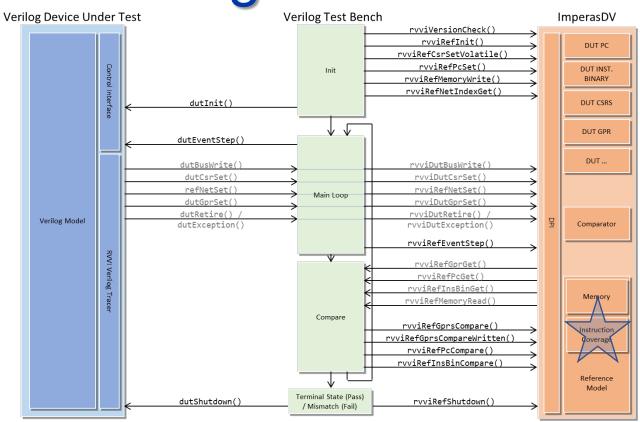

## #4: Industrial Highest Quality Async DV (async-lock-step-compare)

imperas

- Builds on & extends Industrial Quality sync-lock-step-compare DV

- Adds focus on async capabilities

- Depending on design this can include: OoO, MP, debug mode, interrupts, multi-issue, ...

- Example SystemVerilog Components

- tracer: Reports instructions for checking and register writebacks

- step\_and\_compare: Manages the reference model and checks functionality

- interrupt\_assert: Properties for interrupt coverage/checking

- debug\_assert: Properties for debug coverage/checking

- Typically hard, complex, and expensive to get working

- Challenge is extracting async info from microarchitecture RTL pipeline

- See latest developments with RVVI and ImperasDV

2<sup>nd</sup> generation CV32E40P OpenHW flow (2H2020) (Imperas model encapsulated in SystemVerilog)

## #4: Industrial Highest Quality Async DV (async-lock-step-compare)

#### Summary

- Instruction by instruction lockstep comparison (includes async events)

- Comparison of execution flow, of program data, of programmers and internal state

- Immediate comparison

- Allows for debug introspection at point of failure very powerful

- Does not waste execution cycles after failure

- Includes focus on async events, control flow, and hardware real time effects

- Can be hard to develop & set up (depends on RTL DUT tracer features and pipeline understanding)

- See latest development for RVVI and ImperasDV

- Can be expensive in terms of time, resources, licenses and costs a lot per bug found

- But the bugs are even more expensive if not found early enough...

- Lockstep / Compare is by far the best and most efficient approach (industry 'gold standard')

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- #0 "hello world" test

- #1 self checking tests (e.g. Berkeley torture tests pre2018)

- #2 Post simulation trace log file compare (e.g. Google riscv-dv 2019)

- #3 sync-lock-step-compare (e.g. CV32E40P in OpenHW 1H 2020)

- #4 async-lock-step-compare (e.g. CV32E40P in OpenHW 2H H2020)

- #5 test bench use of standards (RVVI) (e.g. CV32E40X/S in OpenHW 2021)

- Components of RISC-V CPU DV environment

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- #0 "hello world" test

- #1 self checking tests (e.g. Berkeley torture tests pre2018)

- #2 Post simulation trace log file compare (e.g. Google riscv-dv 2019)

- #3 sync-lock-step-compare (e.g. CV32E40P in OpenHW 1H 2020)

- #4 async-lock-step-compare (e.g. CV32E40P in OpenHW 2H H2020)

- #5 test bench use of standards (RVVI) (e.g. CV32E40X/S in OpenHW 2021)

- Digression into why we need standards...

- Components of RISC-V CPU DV environment

### Challenges moving forward – the need for standards

imperas

- There are many different components needed:

- DUT & its encapsulation

- 'tracer' information

- Control

- Reference model & its encapsulation

- Configuration

- Comparisons

- Synchronization

- Asynchronous operations

- Control

- Functional coverage measurement & assertions

- Test bench

- Configuration

- Overall control

- Scoreboarding

- Reporting / Logging

- Tests (directed or generated)

- Program linker scripts and binary file reader

- And each component has different interfaces and requirements on the interfaces

2<sup>nd</sup> generation CV32E40P OpenHW flow (2H2020)

### Challenges moving forward – the need for standards

imperas

- There are many different components needed:

- DUT & its encapsulation

- 'tracer' information

- Control

- Reference model & its encapsulation

- Configuration

- Comparisons

- Synchronization

- Asynchronous operations

- Control

- Functional coverage measurement & assertions

- Test bench

- Configuration

- Overall control

- Scoreboarding

- Reporting / Logging

- Tests (directed or generated)

Page 43

- Program linker scripts and binary file reader

- And each component has different interfaces and requirements on the interfaces

2<sup>nd</sup> generation CV32E40P OpenHW flow (2H2020)

It would be a disaster for RISC-V if every design team had to re-invent everything...

#### Why need standard interfaces?

- There are many blocks required in DV solutions

- They all have different interfaces and these interfaces need defining

- They may come from different developers / suppliers

- They may be used in different projects and processor configurations / generations

- If standards exist, then verification IP can be created and licensed

- Goals when developing standard interfaces:

- block re-use

- common ways to do things

- quick start-up

- efficiency

#### Why adopt a standard?

- You have to use some interfaces

- No need to re-invent on your own they do not need to be proprietary

- RVVI is an open standard available on GitHub

- RVVI (and its predecessor) have already been flushed out and are in use

- There is no downside to adoption

- Upside to adoption: potentially make use of other tools / code

- What tools / technologies can potentially be (re)used

- Encapsulation of reference models

- Test benches & test bench components (including onward connection to reference models)

- Functional coverage & assertions

- Log file writer

- Signature file writer (for RISC-V compliance testing)

### RVVI: RISC-V Verification Interface History

- This RVVI work has evolved from over 2 years experience

- Imperas, EM Micro, and SiLabs, ..., working with several RISC-V verification projects

- Collaboration with OpenHW Group (<a href="https://github.com/openhwgroup/core-v-verif">https://github.com/openhwgroup/core-v-verif</a>)

- Re-usable test bench for Core-V range of open-source RISC-V cores

- Also... there was previously the RISC-V Formal Interface (RVFI) targeting formal tools

- https://github.com/SymbioticEDA/riscv-formal

- Interface for providing observation into a running core by streaming what is executing on the core (i.e. the basic trace data / functionality)

- For quality RISC-V processor DV more is needed (than RVFI)

- And each user needs to extend it with proprietary extensions (which is not the right approach...)

- The RVVI-VLG interface has some parts very similar to the RVFI

- RVVI-VLG can be thought of as an updated superset of RVFI

#### Agenda

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- #0 "hello world" test

- #1 self checking tests (e.g. Berkeley torture tests pre2018)

- #2 Post simulation trace log file compare (e.g. Google riscv-dv 2019)

- #3 sync-lock-step-compare (e.g. CV32E40P in OpenHW 1H 2020)

- #4 async-lock-step-compare (e.g. CV32E40P in OpenHW 2H H2020)

- #5 test bench use of standards (RVVI) (e.g. CV32E40X/S in OpenHW 2021)

- Components of RISC-V CPU DV environment

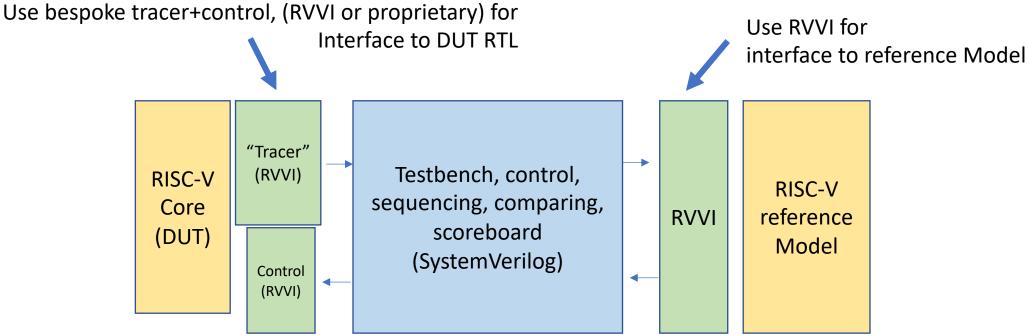

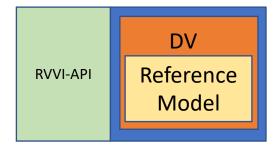

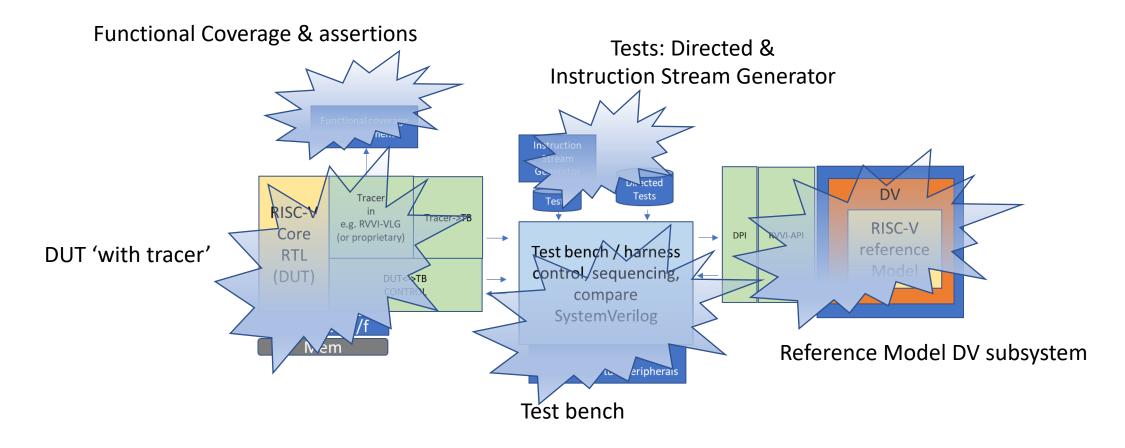

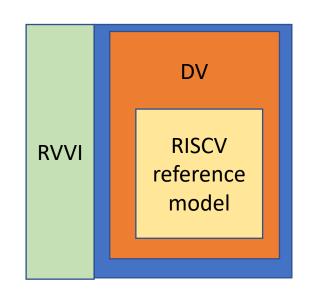

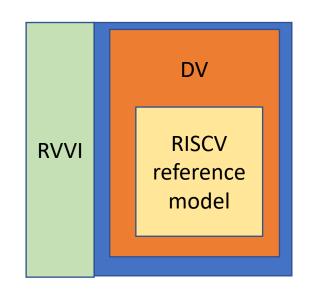

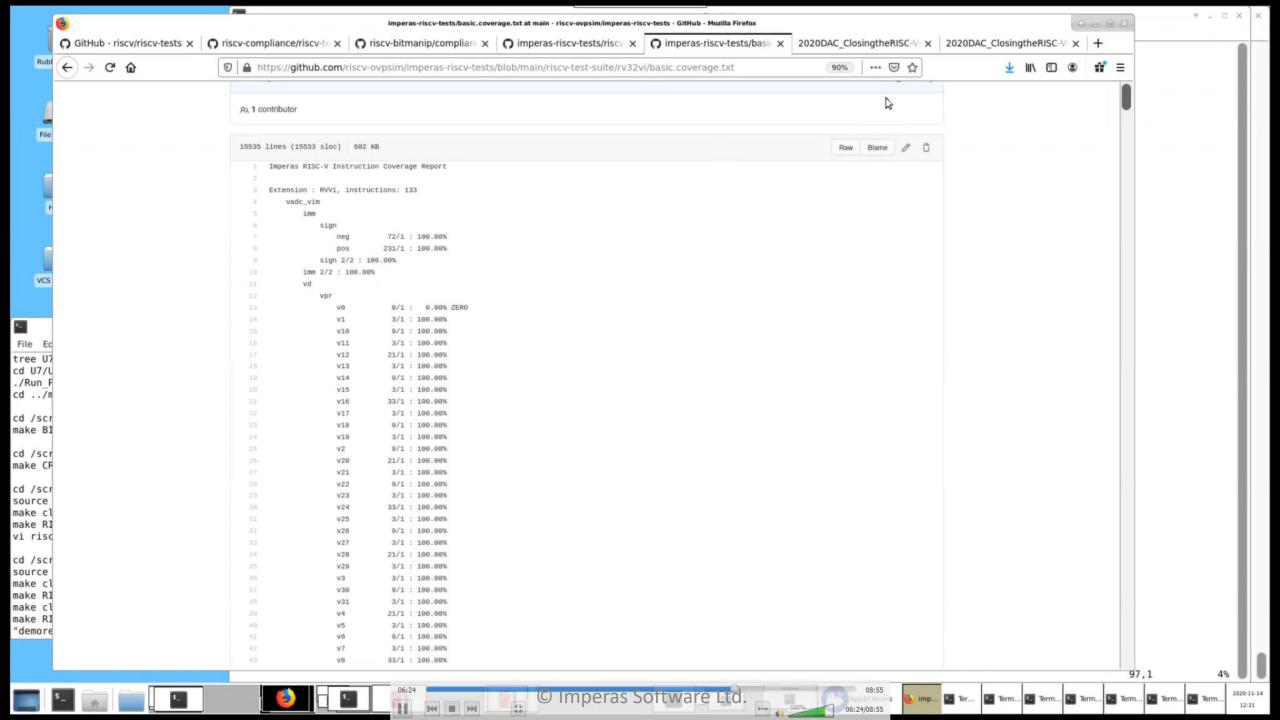

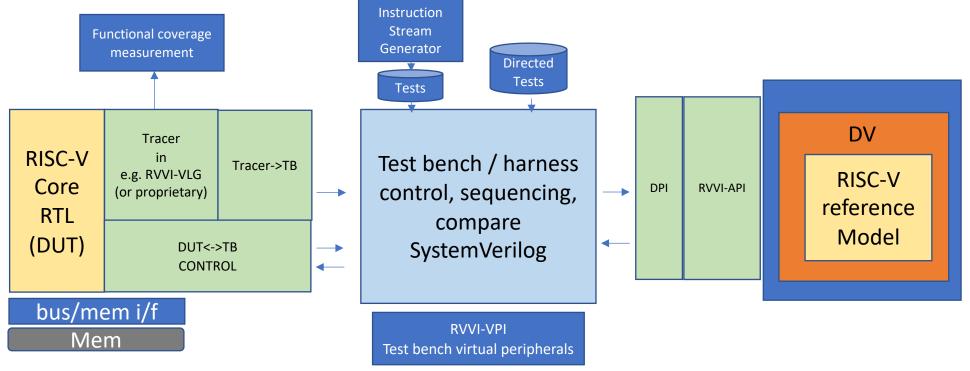

## #5 Evolving to use developing standards (RVVI)

- Focus is on developing standard interfaces between components

- Allows reuse

- Allows development of independent VIP

- Two main components to consider

- DUT

- Reference model

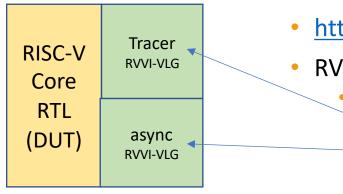

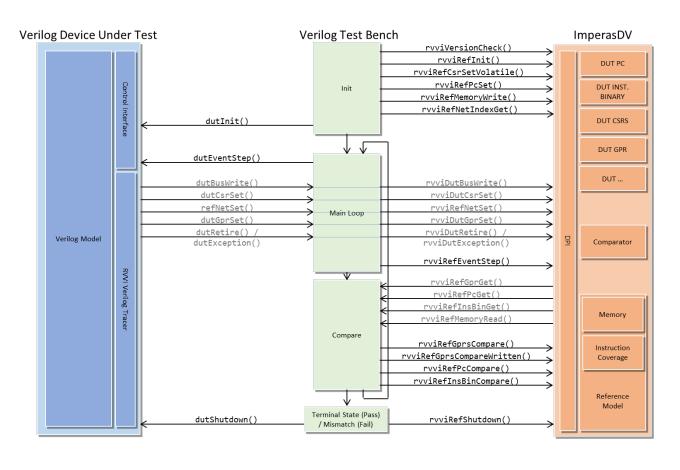

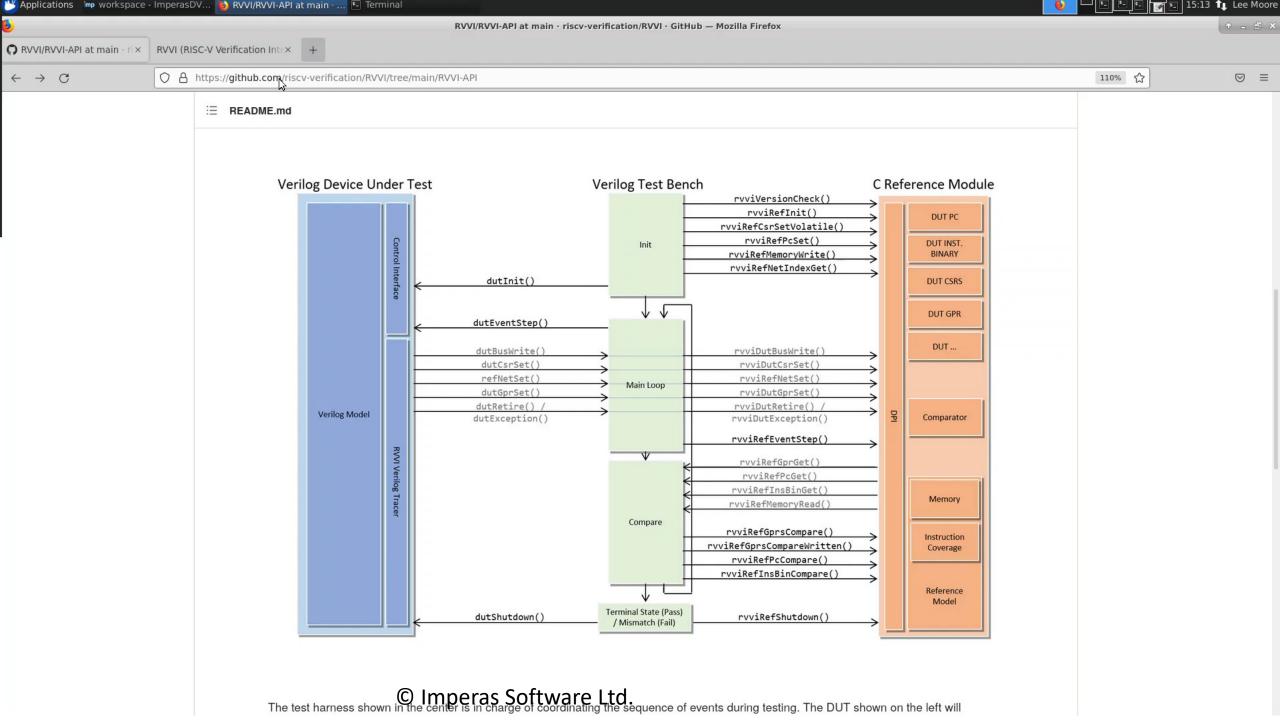

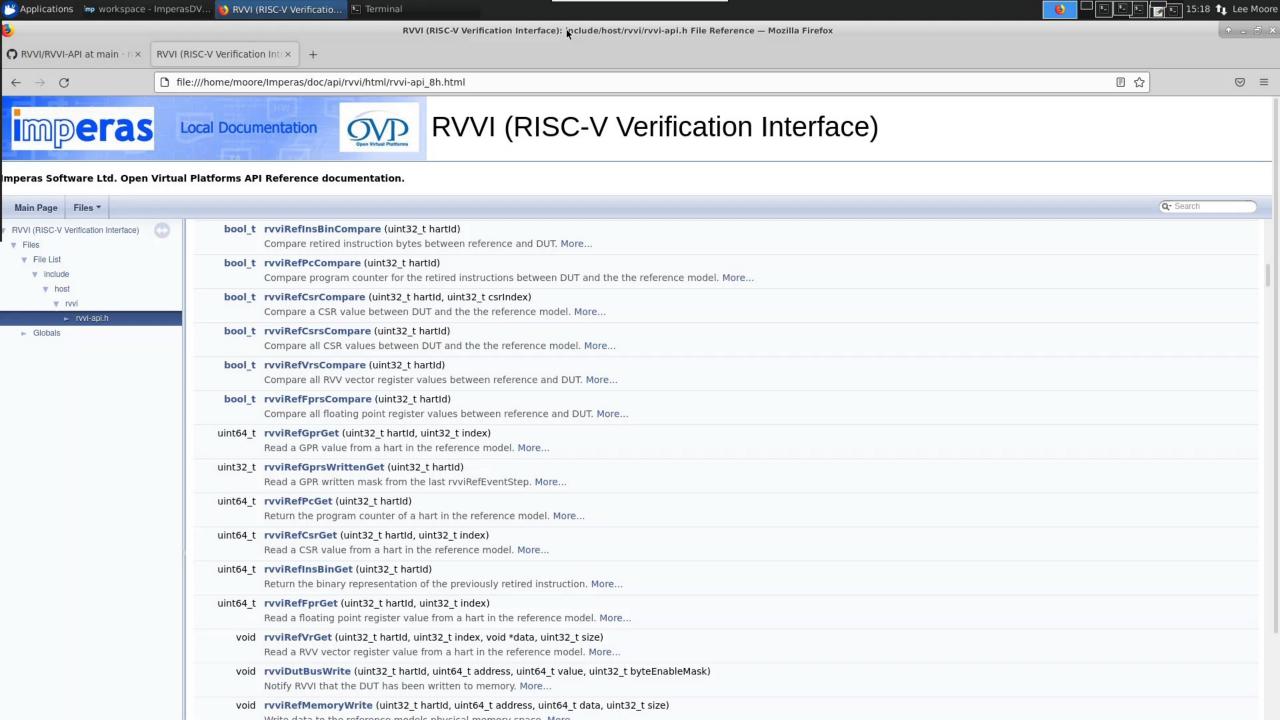

### RVVI: RISC-V Verification Interface (driven by RISC-V DV usage)

- https://github.com/riscv-verification/RVVI (Public Open Standard)

- RVVI-VLG

- Verilog DUT interfaces

- RVVI-VLG state streaming 'tracer' data

- RVVI-VLG nets implementation dependent (Interrupts, Debug)

- Handles multi-hart, multi-issue, Out-of-Order

- RVVI-API

- Controls DV subsystem and reference model

- C/C++

- SystemVerilog

Test bench virtual peripherals

RVVI-VPI

- RVVI-VPI (work-in-progress (Feb. 2022))

- Virtual Peripheral Interfaces

- timers, interrupts, debug, random, printer/uart, ...

- Verilog and C macros & examples

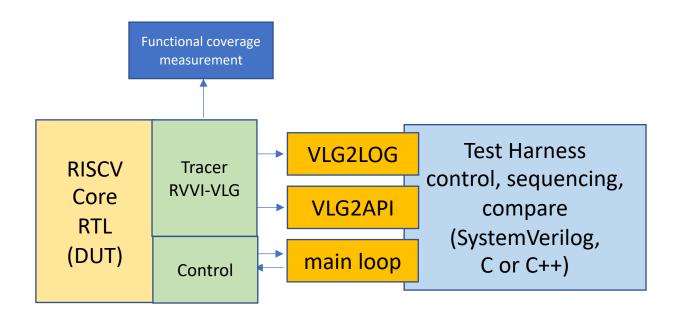

## SystemVerilog test bench using RVVI and components

SystemVerilog

Binary object

### 5 main CPU DV components

#### RTL DUT with 'tracer' interface

- The key component the DUT being tested

- Includes memory model and bus interfaces

- Requires a 'tracer' to provide appropriate data to the test bench

- Requires control interface so test bench can step through events

- Quality of the 'tracer' determines the potential capabilities of the DV

- Can be RVVI, bespoke, or bespoke + extensions + control

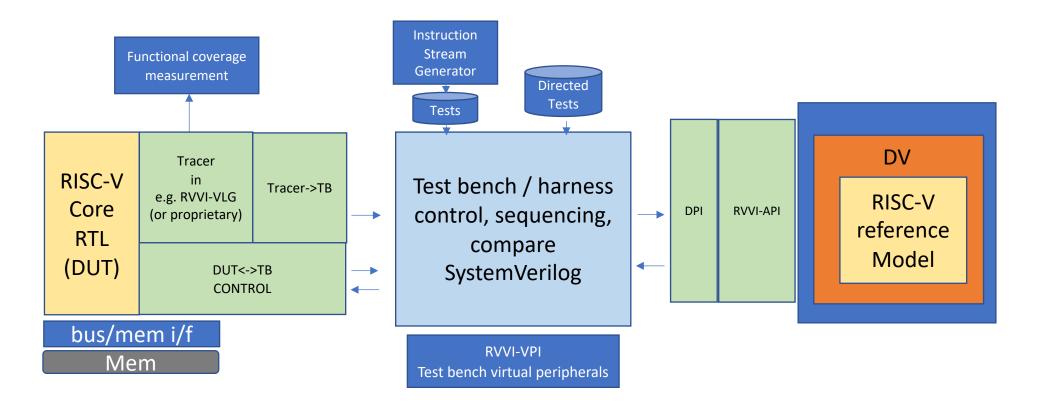

### Tests: Directed & Instruction Stream Generator

(random)

Instruction

Stream Test

Generator

Directed Tests

- Generates test programs

- Usually using constrained random approach

- Most often obtain one:

- Commercial such as Valtrix STING

- Open source e.g. Google riscv-dv (written in SystemVerilog)

- Acquire suites of tests

- Imperas make some available

- May require toolchains like GCC, LLVM for assemblers, linkers

#### Imperas Test Suites

- When verifying a CPU design you can never have enough tests...

- Imperas have developed a directed RISC-V test generator, instruction coverage measuring VIP, and a test qualifying mutating fault simulator to provide high quality test suites

- The generated tests suites are targeting architectural compatibility as defined in the RVIA architectural test working group coverage requirements

- There are currently over 50 free test suites, including

- I,M,C,F,D,B,K,V,P

- The provided vector test suite is one specific vector engine configuration

- The test suites are provided under an OVP open source license and are available free from: <a href="https://github.com/riscv-ovpsim/imperas-riscv-tests">https://github.com/riscv-ovpsim/imperas-riscv-tests</a>

### Functional Coverage & assertions

Functional coverage measurement

- Normally written in SystemVerilog using covergroups, coverpoints, and assertions

- Targets specific measurements as required in verification plan

- Connects to RVVI-VLG from 'tracer'

- Typically includes

- Standard ISA instruction extension measurement

- Sequential instruction monitoring for e.g. hazards, etc.

- Privilege model items such as interrupts, exceptions, debug mode

- User specifics related to pipeline and micro-architecture

- Requires SystemVerilog simulator

Test bench / harness control, sequencing, compare (SystemVerilog, C or C++)

#### Test Bench / Harness

Test bench / harness control, sequencing, compare

SystemVerilog

RVVI-VPI

Test bench virtual peripherals

- Instances and connects all the subsystems

- Controls the stepping of events and instructions

- Connects the data & signals between the DUT and reference subsystem synchronizers and comparators

- Can have virtual peripherals such as uart for logging, or timers for asynchronous event / interrupt generation

- Can be in SystemVerilog for DUT in RTL

- Can be in C/C++ for DUT in C based compiled simulator

- Imperas provides templates in C/C++ and SystemVerilog

# Reference model DV Subsystem

- Three main components

- RISC-V reference model

- DV infrastructure to control model, etc.

- RVVI interface into test bench / harness

- Responsible for

- Configuration of model

- Comparisons between DUT and reference state

- Synchronization due to pipeline affects

- Asynchronous operations

- Control of model

# Reference model DV Subsystem

- Three main components

- RISC-V reference model

- DV infrastructure to control model, etc.

- RVVI interface into test bench / harness

- Responsible for

- Configuration of model

- Comparisons between DUT and reference state

- Synchronization due to pipeline affects

- Asynchronous operations

- Control of model

#### Key component is Reference Model

- RISC-V is highly configurable & extendable

- 200... Questions ?

So it can get a little .... complicated

#### Example reference model: Imperas

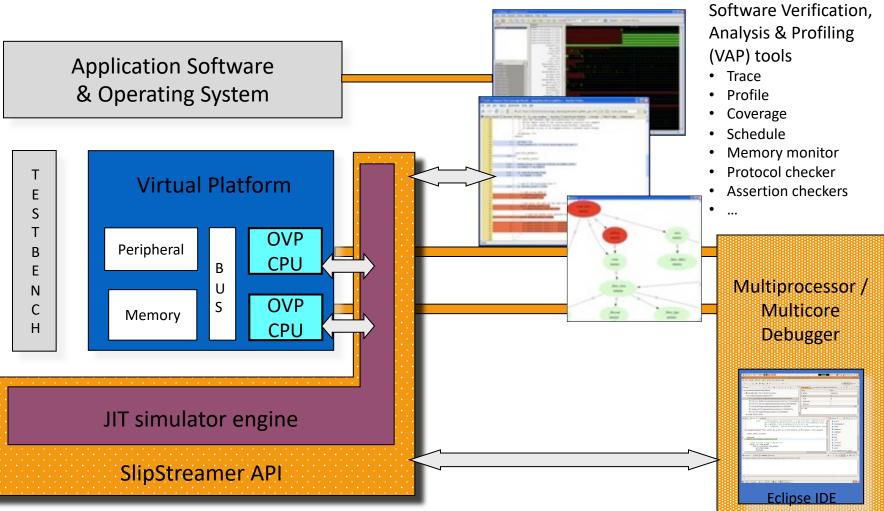

RISC-V Reference Model & Simulator

http://www.imperas.com/riscv

- Imperas provides full RISC-V Specification envelope model

- Industrial quality model /simulator of RISC-V processors for use in compliance, verification and test development

- Complete, fully functional, configurable model / simulator

- All 32bit and 64bit features of ratified User and Privilege RISC-V specs

- Unprivileged versions 2.2, 20191213

- Privilege versions 1.10, 1.11, 1.12

- Vector extension, versions 0.7.1, 0.8, 0.9, 1.0

- Bit Manipulation extension, versions 0.91, 0.92. 0.93, 1.0.0

- Hypervisor version 0.6.1, 1.0.0

- K-Crypto Scalar version 0.7.1, 1.0.0

- Debug versions 0.13.2, 0.14, 1.0.0

- P DSP/SIMD versions 0.5.2, 0.9.6

- Zicbom, Zicbop, Zicboz, Zmmul, Zfh, Zfinx, Zce

- Svnapot, Svpbmt, Svinval, Smstaten, Smepmp, ...

- Model source included under Apache 2.0 open source license

- Used as reference by :

- Mellanox/Nvidia, Seagate, NSITEXE/Denso, Google Cloud, Chips Alliance, lowRISC, OpenHW Group, Andes, Valtrix, SiFive, Codasip, MIPS, Nagra/Kudelski, Silicon Labs, RISC-V Compliance Working Group,

Imperas is used as RISC-V Golden Reference Model

#### Imperas Model extensibility

RISC-V Base Model User Extension:

custom

instructions

&

CSRs

- Separate source files and no duplication to ensure easy maintenance

- Imperas or user can develop the extension

- User extension source can be proprietary

Imperas develops and maintains base model

- Base model implements RISC-V specification in full

- Fully configurable to select which ISA extensions

- Fully configurable to select which version of each ISA extension

- Updated very regularly as ISA extension specification versions change

- Fully configurable for all RISC-V specification options

- e.g. implemented optional CSRs, read only or read/write bits etc...

Imperas provides methodology to easily extend base model

- Templates to add new instructions

- Code fragments for adding functionality

- 100+ page user guide/reference manual with many examples

- Includes example extended processor model

#### User feedback of Imperas as a reference

- "Andes is pleased to <u>certify the Imperas model and simulator</u> as a reference for the new Vector processor NX27V, and is already actively used by our mutual customers."

- Charlie Hong-Men Su, CTO / EVP at Andes Technology Corp

- "We have <u>selected Imperas simulation tools and RISC-V models</u> for our design verification flow because of the <u>quality of the models and</u>

<u>the ease of use</u> of the Imperas environment. Imperas reference model of the complete RISC-V specification, the ability to add our custom instructions to the model and their experience with processor RTL DV flows were also important to our decision."

- Shlomit Weiss, Senior Vice President of Silicon Engineering at Mellanox / Nvidia

- "The OpenHW Group charter is to deliver high quality processor IP cores for our leading commercial members and open source community adoption. Central to this goal, the OpenHW Verification Task Group developed and published a DV test plan and implemented an open engineering-in-progress approach as we complete the verification tasks using the <u>Imperas golden RISC-V reference model</u>."

- Rick O'Connor, Founder and CEO at OpenHW Group

- "Imperas are the pioneers in simulation technology and processor verification for RISC-V. Codasip is very proud of our rigorous approach to verification <u>using Imperas as an important part of our quality process</u> furthers extend our differentiation. The Imperas independence, reputation and technical strength provides our customers with further reassurance in our 'best in class' RISC-V processors."

- Philippe Luc, Verification Director Codasip

- "With this Imperas collaboration, our <u>mutual customers will benefit from the availability of SiFive qualified models</u> that are compatible with the mainstream EDA tool flows."

- Phil Dworsky, Director, Strategic Alliances, SiFive

#### Agenda

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- #0 "hello world" test

- #1 self checking tests (e.g. Berkeley torture tests pre2018)

- #2 Post simulation trace log file compare (e.g. Google riscv-dv 2019)

- #3 sync-lock-step-compare (e.g. CV32E40P in OpenHW 1H 2020)

- #4 async-lock-step-compare (e.g. CV32E40P in OpenHW 2H H2020)

- #5 test bench use of standards (RVVI) (e.g. CV32E40X/S in OpenHW 2021)

- #6 using standards based DV products and VIP

- Drill down into an available commercial RISC-V HW DV verification solution

- Demonstration of ImperasDV in action on open source RISC-V cores

- Components of RISC-V CPU DV environment

#### A dedicated RISC-V CPU DV solution: ImperasDV from Imperas

#### CPU DV test bench components

#### CPU DV test bench components

#### Focus on:

- DUT + 'tracer'

- Test bench

- DV subsystem

#### **ImperasDV**

- Encapsulates the reference model

- Select model, use variant, configure,

- Includes DUT reference state storage

- Includes synchronization technology

- Can run sync, async, interrupts, debug, multi-hart

- Includes comparison technology

- Includes Imperas instruction coverage

- Is configurable and traceable

- Can be used in C/C++ or SystemVerilog test bench / harness

- Uses RVVI-API

- Very simple to use the 'smarts' are built-in

Test bench / harness control, sequencing, compare (SystemVerilog, C or C++)

#### Test Bench / Harness

- Instances and connects all the subsystems

- Controls the stepping of events and instructions

- Connects the data & signals between the DUT and reference subsystem synchronizers and comparators

- Can be in SystemVerilog for DUT in RTL

- Can be in C/C++ for DUT in C based compiled simulators

- Imperas provides templates in C/C++ and SystemVerilog

- Expect users to extend and customize

### ImperasDV setup

Page 69

- Reference model setup

- Configuration of register and memory initialization

- Selection of what to compare (depends on DUT 'tracer' capabilities):

- PC, GPR, CSR, FPR, VR, decode, net, hart...

- Select capabilities:

- sync-lock-step-compare or async-lock-step-compare

- Trace and logging set up

- Selection of built-in Imperas instruction coverage

- Choice of DV control options

### Agenda

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- Drill down into an available commercial RISC-V HW DV verification solution

- Demonstration of ImperasDV in action on open source RISC-V cores

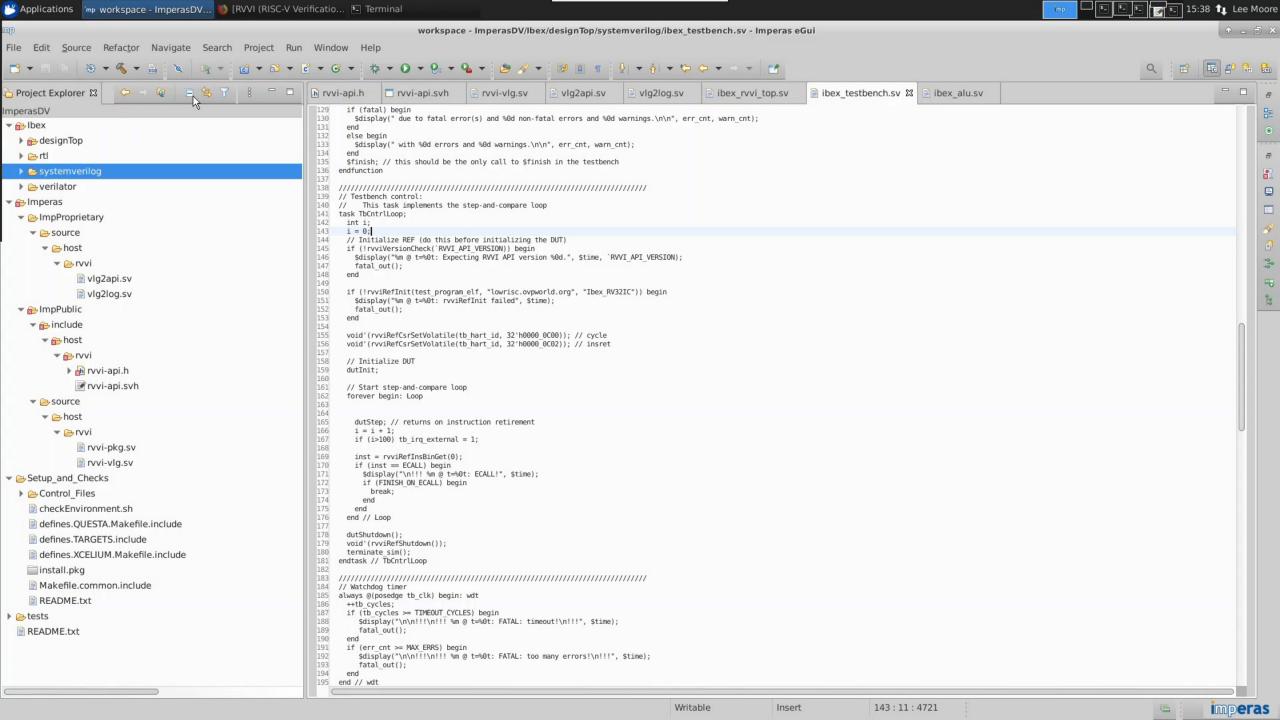

- SystemVerilog test bench

- Components of RISC-V CPU DV environment

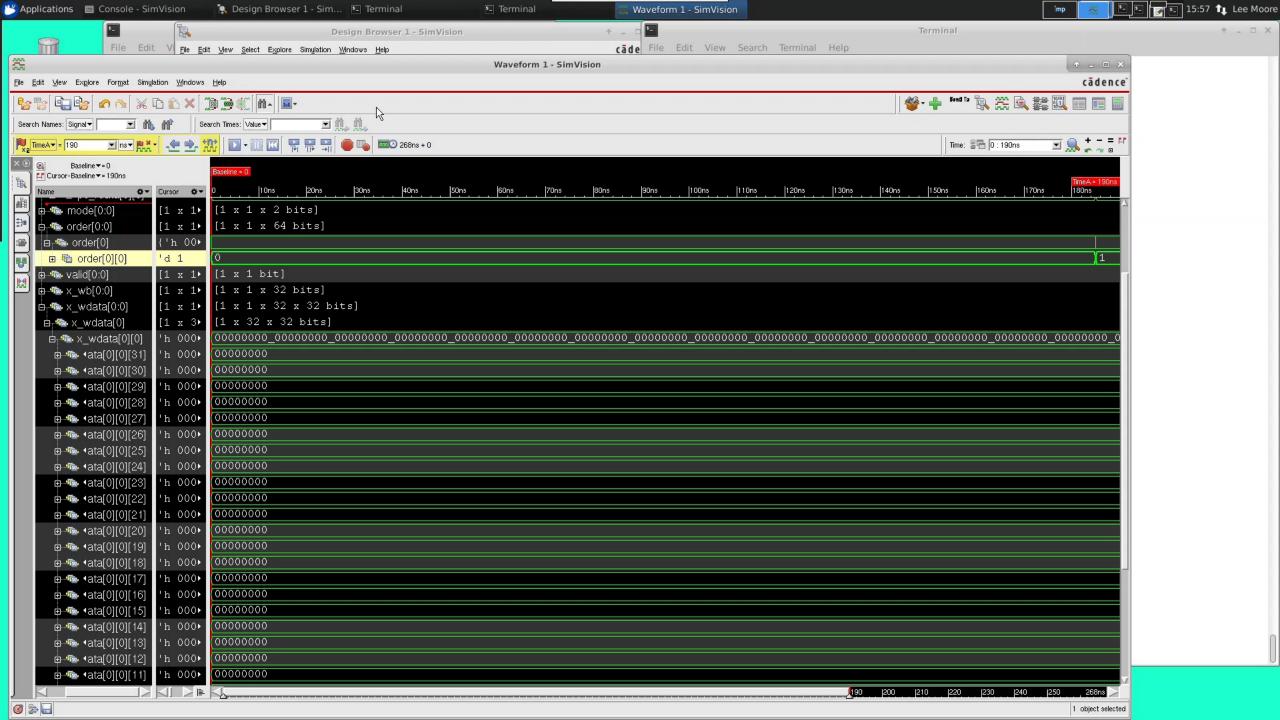

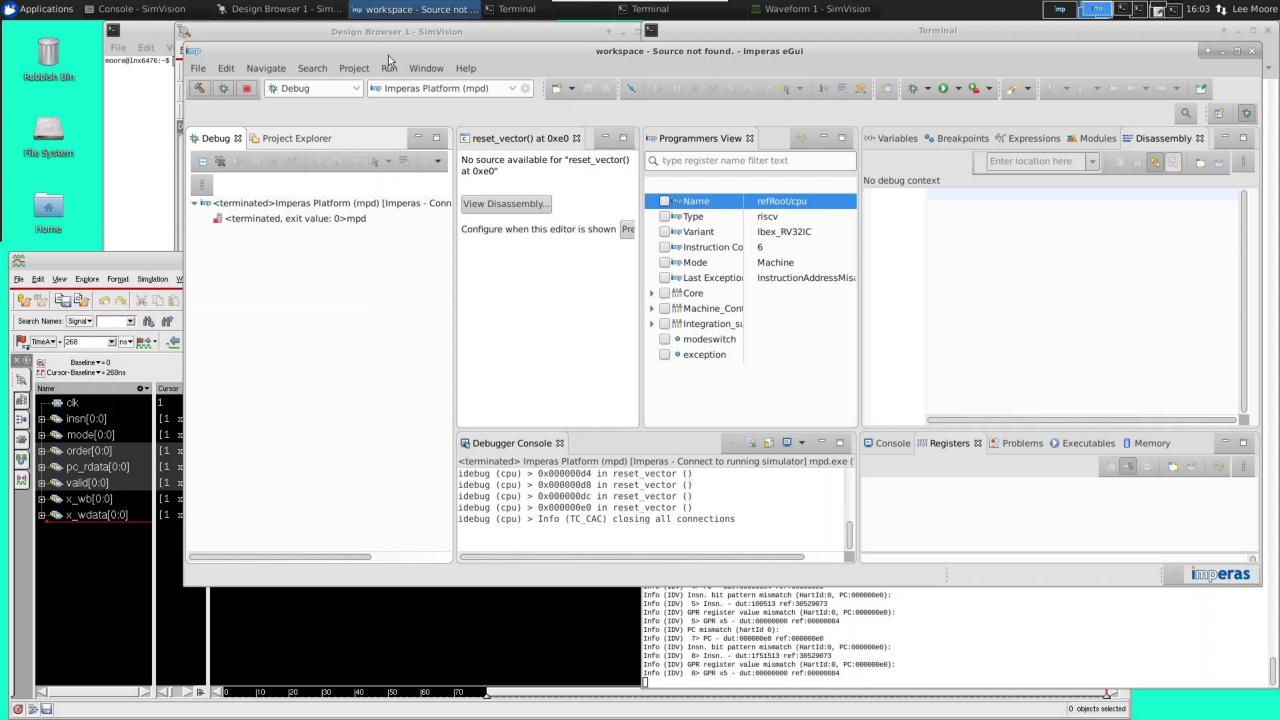

Demo: ImperasDV

Core: lowRISC lbex

Simulator: SystemVerilog

DV mode: sync-lock-step-compare

- Walk through C/C++ rvvi.h and in doxygen introduce APIs: RVVI-VLG

- Walk through tracer code where it converts RVVI-VLG nets to -> RVVI-API

- Walk through SystemVerilog harness

- Show init, config, main step loop

- Run example passes

- Run example fails, show trace, show in eGuiMPD and waveforms

- Show arch test suites

- Show instruction coverage

Page 71

01 2022

## Demonstration / Walkthrough of ImperasDV Commercial RISC-V CPU DV solution Lee Moore

### Agenda

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- Drill down into an available commercial RISC-V HW DV verification solution

- Demonstration of ImperasDV in action on open source RISC-V cores

- SystemVerilog test bench

- Components of RISC-V CPU DV environment

Home

256 MB

Volume

Volume

```

Terminal

File Edit View Search Terminal Help

Info x5 00001234 -> 000023cc

RET, 0, 186, 000003d0, "c3428293 addi x5, x5, -972 ", x5=00002000, , , ,

Info x5 000023cc -> 00002000

RET, 0, 187, 000003d4, "00020337 lui x6, 0x20

",x6=00020000,,,,

x6,0x20

Info x6 ffffffff -> 00020000

RET, 0, 188, 000003d8, "00430313 addi x6, x6, 4

",x6=00020004,,,,

Info 188: 'refRoot/cpu', 0x000000000000000000018(begin_testcode+294): Machine 00430313 addi x6,x6,4

Info x6 00020000 -> 00020004

RET, 0, 189, 000003dc, "00532023 sw

x5,0(x6)

Info 189: 'refRoot/cpu', 0x000000000000003dc(begin_testcode+298): Machine 00532023 sw

x5,0(x6)

RET, 0, 190, 000003e0, "00002297 auipc x5, 0x2

",x5=000023e0,,,,

Info 190: 'refRoot/cpu', 0x000000000000000000000000000000000+1 (machine 00002297 auipc x5,0x2

Info x5 00002000 -> 000023e0

RET, 0, 191, 000003e4, "cb028293 addi x5, x5, -848 ", x5=00002090, , , ,

Info 191: 'refRoot/cpu', 0x0000000000000000004(begin_testcode+2a0): Machine cb028293 addi x5,x5,-848

Info x5 000023e0 -> 00002090

",x6=00020000,,,,

RET, 0, 192, 000003e8, "00020337 lui

x6,0x20

Info 192: 'refRoot/cpu', 0x00000000000000088(begin_testcode+2a4): Machine 00020337 lui

x6,0x20

Info x6 00020004 -> 00020000

RET, 0, 193, 000003ec, "00830313 addi x6, x6, 8

",x6=00020008,,,,

Info 193: 'refRoot/cpu', 0x0000000000000000c(begin_testcode+2a8): Machine 00830313 addi x6,x6,8

Info x6 00020000 -> 00020008

RET, 0, 194, 000003f0, "00532023 sw

x5,0(x6)

",,,,,

Info 194: 'refRoot/cpu', 0x0000000000000000016(begin_testcode+2ac): Machine 00532023 sw

x5,0(x6)

RET,0,195,000003f4,"00100293 addi x5,x0,1 ",x5=00000001,,,,

Info 195: 'refRoot/cpu', 0x0000000000003f4(begin_testcode+2b0): Machine 00100293 addi

x5, x0, 1

Info x5 00002090 -> 00000001

RET, 0, 196, 000003f8, "00020337 lui

x6,0x20

",x6=00020000,,,,

Info 196: 'refRoot/cpu', 0x00000000000003f8(begin_testcode+2b4): Machine 00020337 lui

x6,0x20

Info x6 00020008 -> 00020000

RET, 0, 197, 000003fc, "00532023 sw

x5,0(x6)

Info 197: 'refRoot/cpu', 0x00000000000003fc(begin_testcode+2b8): Machine 00532023 sw

x5,0(x6)

RET, 0, 198, 00000400, "Off0000f fence

",x3=00000001,,,,

RET, 0, 199, 00000404, "00100193 addi x3, x0, 1

Info 199: 'refRoot/cpu', 0x00000000000000404(begin_testcode+2c0): Machine 00100193 addi x3,x0,1

Info x3 ffffedcc -> 00000001

EXC, 0, 200, 00000408, "00000073 ecall

Info 200: 'refRoot/cpu', 0x0000000000000000000(begin_testcode+2c4): Machine 000000073 ecall

Info mstatus 00001880 -> 00001800

Info mepc 00000144 -> 00000408

Info mcause 00000000 -> 0000000b

!!! ibex_testbench.TbCntrlLoop.Loop @ t=2630ns: ECALL!

Info -----

Info ImperasDV VERIFICATION REPORT:

Info Instruction retires :

199

Info Exceptions

1

Info

Mismatches

Info

Sets / Compares

200 / 200

Info

PC

Info

Instruction

200 / 200

Info

GPR

200 / 6400

Info

CSR

0 / 0

Info

FPR

0 / 0

Info

VR

0 / 0

Info

Total compares :

6800

Info -----

Test PASSED with 0 errors and 0 warnings.

Simulation complete via $finish(1) at time 2630 NS + 0

../designTop/systemverilog/ibex_testbench.sv:135    $finish; // this should be the only call to $finish in the testbench

xcelium> exit

20.03-s010: Exiting on Feb 04, 2022 at 15:51:16 GMT (total: 00:00:04)

moore@lnx6476:-/Demo/ImperasDV/Ibex/systemverilog$

```

15:52 👠 Lee Moore

256 MB

Volume

Volume

File Edit View Search Terminal Help Info x5 00001234 -> 000023cc RET, 0, 186, 000003d0, "c3428293 addi x5, x5, -972 ", x5=00002000, , , , Info x5 000023cc -> 00002000 RET, 0, 187, 000003d4, "00020337 lui x6, 0x20 ",x6=00020000,,,, x6,0x20 Info x6 ffffffff -> 00020000 RET, 0, 188, 000003d8, "00430313 addi x6, x6, 4 ",x6=00020004,,,, Info 188: 'refRoot/cpu', 0x0000000000000000000d8(begin\_testcode+294): Machine 00430313 addi x6,x6,4 Info x6 00020000 -> 00020004 RET, 0, 189, 000003dc, "00532023 sw x5,0(x6) Info 189: 'refRoot/cpu', 0x000000000000003dc(begin\_testcode+298): Machine 00532023 sw RET, 0, 190, 000003e0, "00002297 auipc x5, 0x2 ",x5=000023e0,,,, Info 190: 'refRoot/cpu', 0x00000000000000000000000000000000+29c): Machine 00002297 auipc x5,0x2 Info x5 00002000 -> 000023e0 RET, 0, 191, 000003e4, "cb028293 addi x5, x5, -848 ", x5=00002090,,,, Info 191: 'refRoot/cpu', 0x000000000000003e4(begin\_testcode+2a0): Machine cb028293 addi x5,x5,-848 Info x5 000023e0 -> 00002090 ",x6=00020000,,,, RET, 0, 192, 000003e8, "00020337 lui x6.0x20 Info 192: 'refRoot/cpu', 0x0000000000000088(begin\_testcode+2a4): Machine 00020337 lui Info x6 00020004 -> 00020000 RET, 0, 193, 000003ec, "00830313 addi x6, x6, 8 ",x6=00020008,,,, Info 193: 'refRoot/cpu', 0x0000000000000000c(begin\_testcode+2a8): Machine 00830313 addi x6,x6,8 Info x6 00020000 -> 00020008 RET, 0, 194, 000003f0, "00532023 sw x5,0(x6) ",,,,, x5,0(x6) ",x5=00000001,,,, RET, 0, 195, 000003f4, "00100293 addi x5, x0, 1 Info 195: 'refRoot/cpu', 0x000000000000001f4(begin\_testcode+2b0): Machine 00100293 addi x5, x0, 1 Info x5 00002090 -> 00000001 RET, 0, 196, 000003f8, "00020337 lui x6,0x20 ",x6=00020000,,,, Info 196: 'refRoot/cpu', 0x00000000000003f8(begin\_testcode+2b4): Machine 00020337 lui x6,0x20 Info x6 00020008 -> 00020000 RET, 0, 197, 000003fc, "00532023 sw x5,0(x6) Info 197: 'refRoot/cpu', 0x00000000000003fc(begin\_testcode+2b8): Machine 00532023 sw x5,0(x6) RET, 0, 198, 00000400, "Off0000f fence Info 198: 'refRoot/cpu', 0x0000000000000000(begin\_testcode+2bc): Machine Off0000f fence ",x3=00000001,,,, RET, 0, 199, 00000404, "00100193 addi x3, x0, 1 Info 199: 'refRoot/cpu', 0x00000000000000404(begin\_testcode+2c0): Machine 00100193 addi x3,x0,1 Info x3 ffffedcc -> 00000001 EXC. 0. 200, 00000408, "00000073 ecall Info mstatus 00001880 -> 00001800 Info mepc 00000144 -> 00000408 Info mcause 00000000 -> 0000000b !!! ibex\_testbench.TbCntrlLoop.Loop @ t=2630ns: ECALL! Info -----Info ImperasDV VERIFICATION REPORT: Info Instruction retires : 199 Info Exceptions 1 Info Mismatches Info Sets / Compares Info PC 200 / 200 Info Instruction 200 / 200 Info GPR 200 / 6400 Info CSR 0 / 0 Info FPR 0 / 0 Info VR 0 / 0 Info Total compares : 6800 Info -----Test PASSED with 0 errors and 0 warnings. Simulation complete via \$finish(1) at time 2630 NS + 0 ../designTop/systemverilog/ibex\_testbench.sv:135 \$finish; // this should be the only call to \$finish in the testbench xcelium> exit TOOL: xrun(64) 20.03-s010: Exiting on Feb 04, 2022 at 17:23:34 GMT (total: 00:00:04) moore@lnx6476:-/Demo/ImperasDV/Ibex/systemverilog\$

Terminal

■ 17:25 👠 Lee Moore

256 MB

Volume

Volume

Terminal File Edit View Search Terminal Help Loading snapshot worklib.ibex testbench:sv .................. Done xmsim: \*W, XCLGNOPTM: The SystemVerilog constraint solver Xceligen options 'seed\_only\_rand and process\_alternate\_rng and ignore\_worklib\_name' are now enabled b y default.. SVSEED default: 1 xmsim: \*W,RNDNOXCEL: A newer version of the SystemVerilog constraint solver is available. It is recommended to enable it using "xrun/xmsim -xceligen on=1903 . xmsim: \*W,DSEM2009: This SystemVerilog design is simulated as per IEEE 1800-2009 SystemVerilog simulation semantics. Use -disable\_sem2009 option for turning o ff SV 2009 simulation semantics. xcelium> source /home/nda/cadence/installs/XCELIUM2003/tools/xcelium/files/xmsimrc xcelium> run ibex\_testbench.tb\_cntrl @ t=0ns; loading test\_program /home/moore/Demo/ImperasDV/Ibex/systemverilog/work/I-ADD-01.hex Info (OR\_OF) Target 'refRoot/cpu' has object file read from '/home/moore/Demo/ImperasDV/Ibex/systemverilog/work/I-ADD-01.elf' Info (OR\_PH) Program Headers: Info (OR\_PH) Type Offset VirtAddr PhysAddr FileSiz MemSiz Flags Align Info (OR\_PD) LOAD 0x00001000 0x00000000 0x000000000 0x000000444 0x000000444 R-E 1000 Info (OR\_PD) LOAD 0x00002000 0x00001000 0x00001000 0x00001204 0x00001204 RW- 1000 Info (ICV\_PVSN) parameter 'user\_version' is '20190305' Info (ICV\_ALI) Pseudo instructions will be translated Info (OP\_NOS) Simulator finishing because 'nosimulation' was specified Info (OP\_NOS) Simulator finishing because 'nosimulation' was specified ImperasDV Initialised: - program: /home/moore/Demo/ImperasDV/Ibex/systemverilog/work/I-ADD-01.elf vendor: lowrisc.ovpworld.org variant: Ibex RV32IC !!! ibex\_testbench.TbCntrlLoop.Loop @ t=2630ns: ECALL! Info ----Info ImperasDV VERIFICATION REPORT: Info Instruction retires : 199 Info Exceptions Info Mismatches Info Sets / Compares Info PC 200 / 200 Info Instruction 200 / 200 Info GPR 200 / 6400 Info CSR 0 / 0 Info FPR 0 / 0 Info VR 0 / 0 Info 6800 Total compares : Info -----Info (ICV\_RD) Reading file /home/moore/Demo/ImperasDV/Ibex/systemverilog/I-ADD-01.basic.coverage.yaml Info (ICV\_RD) Reading file /home/moore/Demo/ImperasDV/Ibex/systemverilog/I-AND-01.basic.coverage.yaml Info (ICV\_RD) Reading file /home/moore/Demo/ImperasDV/Ibex/systemverilog/I-BLT-01.basic.coverage.yaml Info (ICV\_RD) Reading file /home/moore/Demo/ImperasDV/Ibex/systemverilog/I-LW-01.basic.coverage.yaml Info (ICV\_RD) Reading file /home/moore/Demo/ImperasDV/Ibex/systemverilog/I-SW-01.basic.coverage.yaml Info (ICV\_WCR) Writing coverage report collate.basic.coverage.txt Info -----Info TOTAL INSTRUCTION COVERAGE : RV32I Info Threshold : 1 Info Instructions counted : 192 Info Unique instructions : 13/39 : 33.33% Info Coverage points hit : 503/2540 : 19.80% Info -----Test PASSED with 0 errors and 0 warnings. Simulation complete via \$finish(1) at time 2630 NS + 0 ../designTop/systemverilog/ibex\_testbench.sv:135 \$finish; // this should be the only call to \$finish in the testbench xcelium> exit 20.03-s010: Exiting on Feb 04, 2022 at 17:27:26 GMT (total: 00:00:02) TOOL: xrun(64) moore@lnx6476:-/Demo/ImperasDV/Ibex/systemverilog\$ grep -n "Coverage points hit" \*.txt collate.basic.coverage.txt:3182:Info Coverage points hit : 503/2540 : 19.80% I-ADD-01.basic.coverage.txt:3182:Info Coverage points hit : 253/2540 : 9.96% I-AND-01.basic.coverage.txt:3182:Info Coverage points hit : 253/2540 : 9.96% I-BLT-01.basic.coverage.txt:3182:Info Coverage points hit : 189/2540 : 7.44% I-LW-01.basic.coverage.txt:3182:Info Coverage points hit : 195/2540 : 7.68% I-SW-01.basic.coverage.txt:3182:Info Coverage points hit : 154/2540 : 6.06% moore@lnx6476:-/Demo/ImperasDV/Ibex/systemverilog\$

17:29 1 Lee Moore

Demo: ImperasDV

Core: lowRISC lbex

Simulator: SystemVerilog

DV mode: sync-lock-step-compare

- Walk through C/C++ rvvi.h and in doxygen introduce APIs: RVVI-VLG

- Walk through tracer code where it converts RVVI-VLG nets to -> RVVI-API

- Walk through SystemVerilog harness

- Show init, config, main step loop

- Run example passes

- Run example fails, show trace, show in eGuiMPD and waveforms

- Show arch test suites

- Show instruction coverage

Page 83

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- Components of RISC-V CPU DV environment

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- Components of RISC-V CPU DV environment

- Compliance Tests and other Test Suites

- Instruction Stream Generators

- Functional Coverage

- Instruction Set Simulators

### RISC-V International's compliance tests

- RISC-V International has been working on compliance testing since 2018

- Status (Feb 2022):

- Test suites for basic un-priv older ratified extensions I, M, C, etc

- Simple framework for running DUT and provides signatures for comparison

- Working on new framework to run in a post simulation signature compare mode

- Encapsulates sail model, uses yaml configuration, does not provide build in reference signatures

- Process is self-certification

- You run the tests on your DUT and declare it is RISC-V compliant

#### RISC-V International Compliance Special Interest Group - Charter (aka compliance working group)

#### SIG Charter

The Architectural Compatibility Test SIG is an umbrella group that will provide guidance, strategy and oversight for the development of tests used to help find incompatibilities with the RISC-V Architecture as a step in the Architectural Compatibility self-certification process

The group will:

- Guide Development of:

- Architectural tests for RISC-V implementations covering ratified and in-flight specifications for

Architectural versions, standard extensions, and implementation options.

- · Tools and infrastructure to help identify architectural incompatibilities in implementations

- Work with LSM and Chairs for resources to get the above work done.

- Mentor or arrange for mentoring for the resources to get the above work done

#### RISC-V International Compliance Special Interest Group (2) (aka compliance working group)

#### RISC-V attendance

#### Only RISC-V Members May Attend

- Non-members are asked to please leave.

- Members share IP protection by virtue of their common membership agreement. Non-members being present jeopardizes that protection

- It is easy to become a member. Check out riscv.org/membership

- If you need work done between non-members or or other orgs and RISC-V, please use a joint working group (JWG).

- used to allow non-members in SIGs but the SIGs purpose has changed.

- Please put your name and company (in parens after your name) as your zoom name. If you are an

individual member just use the word "individual" instead of company name.

- Non-member guests may present to the group but should only stay for the presentation. Guests should leave for any follow on discussions.

#### RISC-V International Compliance Special Interest Group (3) – Mailing List (aka compliance working group)

Tech: Architecture Test SIG sig-arch-test@lists.riscv.org

#### Architecture Test SIG

Define coverage requirements for RV32I compliance tests, release compliance test format spec, release compliance suite for RV32I

For bugs & ongoing tasks in Jira, please see the Jira project for Compliance

#### **Group Information**

- 2 138 Members

- 202 Topics, Last Post: Feb 5

- Started on 2019-12-17

#### Group Email Addresses

Post: sig-arch-test@lists.riscv.org

Subscribe: sig-arch-test+subscribe@lists.riscv.org

Unsubscribe: sig-arch-test+unsubscribe@lists.riscv.org

Group Owner: sig-arch-test+owner@lists.riscv.org

Help: sig-arch-test+help@lists.riscv.org

Top Hashtags [See All]

#### **Group Settings**

- This is a subgroup of main.

- All members can post to the group.

- Posts to this group do not require approval from the moderators.

- Messages are set to reply to sender.

- Subscriptions to this group do not require approval from the moderators.

- Archive is visible to anyone.

- Members can edit their messages.

- Members can set their subscriptions to no email.

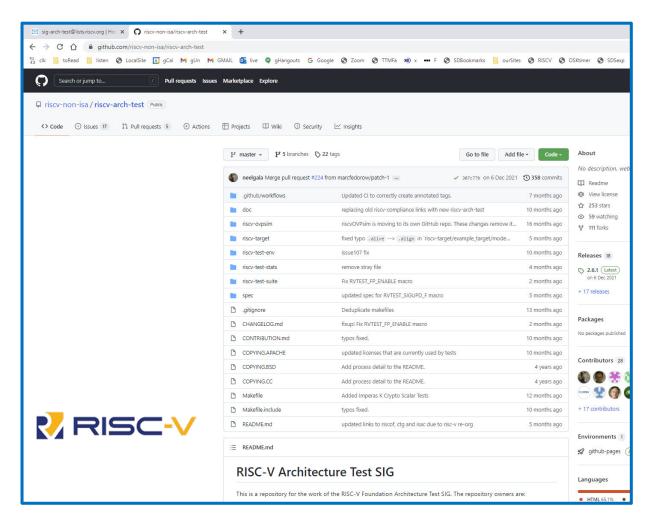

#### RISC-V International Compliance Special Interest Group (4) - GitHub (aka compliance working group)

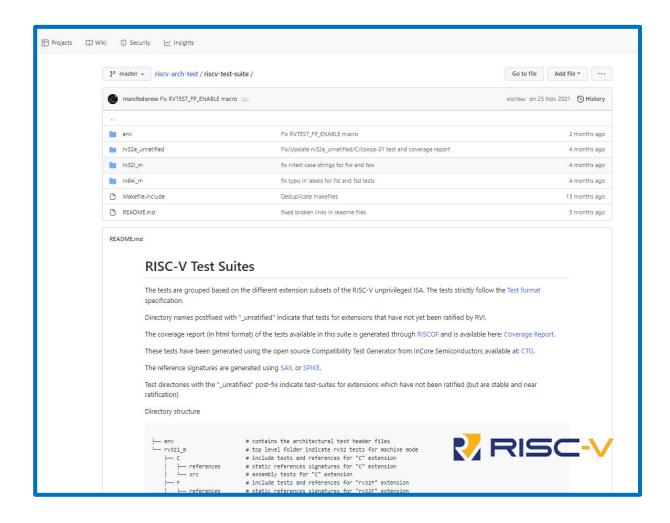

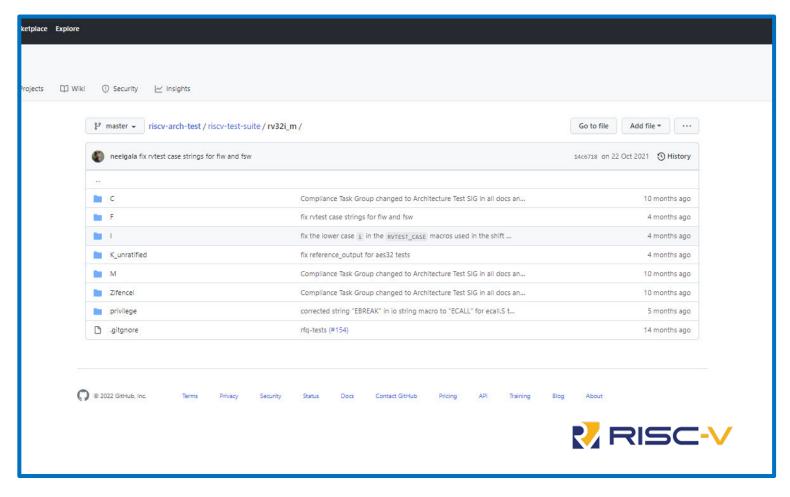

#### RISC-V International Compliance Special Interest Group (5) – GitHub – test suites (aka compliance working group)

#### RISC-V International Compliance Special Interest Group (6) – GitHub – test suites (aka compliance working group)

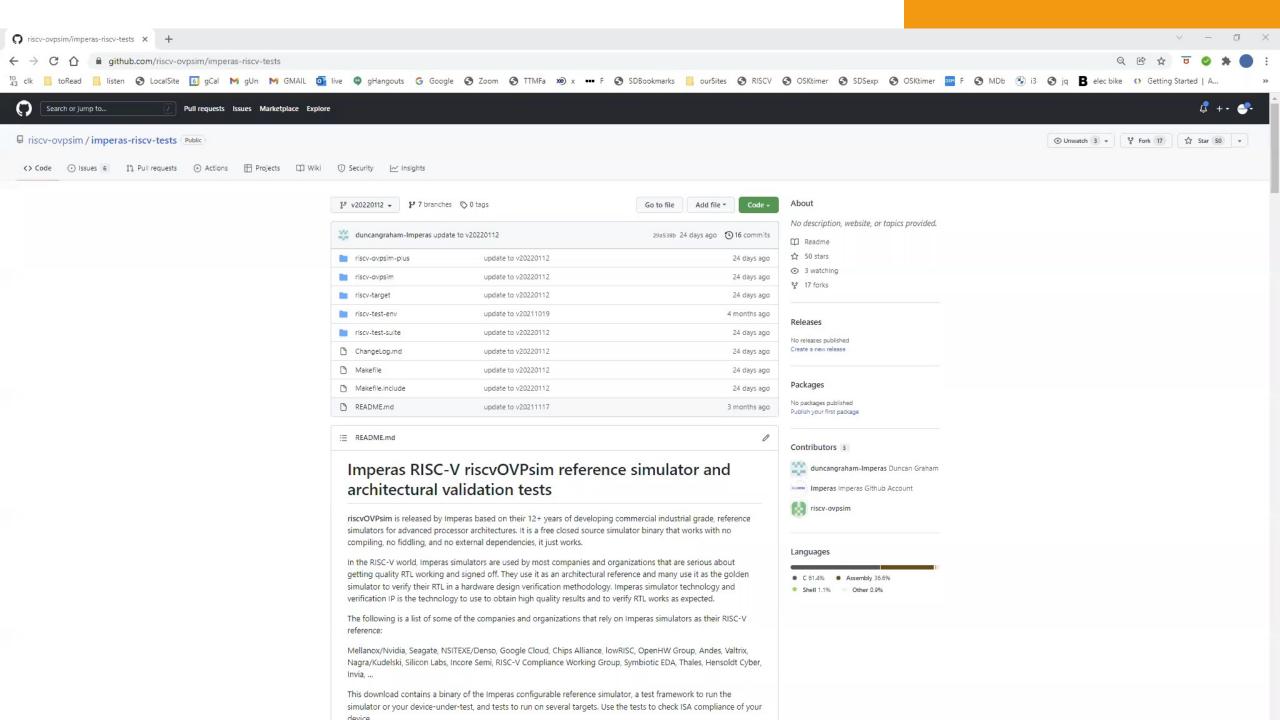

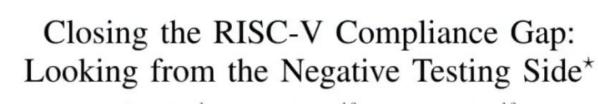

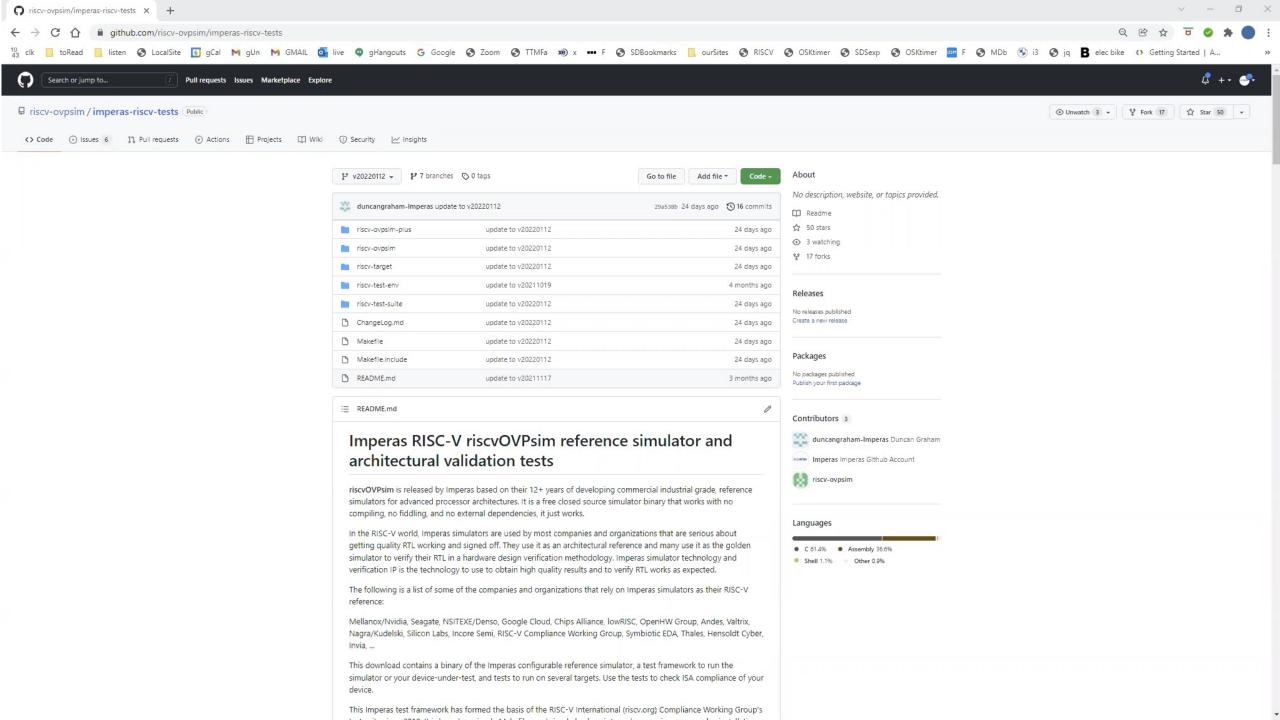

### Imperas Test Suites

- When verifying a CPU design you can never have enough tests...

- Imperas have developed a directed RISC-V test generator, instruction coverage measuring VIP, and a test qualifying mutating fault simulator to provide high quality test suites

- The generated tests suites are targeting architectural compatibility as defined in the RVIA architectural test working group coverage requirements

- There are currently over 50 free test suites, including

- I,M,C,F,D,B,K,V,P

- The provided vector test suite is one specific vector engine configuration

- The test suites are provided under an OVP open source license and are available free from: <a href="https://github.com/riscv-ovpsim/imperas-riscv-tests">https://github.com/riscv-ovpsim/imperas-riscv-tests</a>

### Bremen Univ. 'Fuzz' tests

- + 160%

Vladimir Herdt<sup>1</sup> Daniel Große<sup>1,2</sup> Rolf Drechsler<sup>1,2</sup>

<sup>1</sup>Cyber-Physical Systems, DFKI GmbH, 28359 Bremen, Germany

<sup>2</sup>Institute of Computer Science, University of Bremen, 28359 Bremen, Germany {vherdt,grosse,drechsle}@informatik.uni-bremen.de

Abstract—Compliance testing for RISC-V is very important. Therefore, an official hand-written compliance test-suite is being actively developed. However, besides requiring significant manual effort, it focuses on positive testing (the implemented instructions work as expected) only and neglects negative testing (consider illegal instructions to also ensure that no additional/unexpected behavior is accidentally added). This leaves a large gap in compliance testing.

In this paper we propose a fuzzing-based test-suite generation approach to close this gap. We found new bugs in several RISC-V simulators including *riscvOVPsim* from Imperas which is the official reference simulator for compliance testing.

#### I. INTRODUCTION

An Instruction Set Architecture (ISA) defines the interface between the Hardware (HW) of a processor and the Software (SW).

While as a consequence, the format of a SW binary running on

that represents the output of the test result and is dumped at the end of the test execution. For compliance testing, these signatures are compared against golden reference signatures (obtained by running the test-suite on a reference simulator). A separate sub test-suite is developed for the RISC-V base ISA as well as for each standard ISA extension. Besides the significant manual effort for the maintenance, the compliance test-suite focuses on positive testing only, i.e. to show that the implemented instructions work as expected. However, it neglects negative testing, i.e. to consider illegal instructions to also ensure that no additional/unexpected behavior is accidentally added. This leaves open a large gap in compliance testing.

Contribution: In this paper we propose a fuzzing-based test-suite generation approach to close this gap. We leverage state-of-the-art fuzzing techniques (based on LLVM libFuzzer) to iteratively generate test-cases which are executed on a RISC-V simulator and

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- Other components of RISC-V CPU DV environments

- Compliance Tests and other Test Suites

- Instruction Stream Generators

- Functional Coverage

- Instruction Set Simulators

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- Other components of RISC-V CPU DV environments

- Compliance Tests and other Test Suites

- Instruction Stream Generators

- Google Cloud riscv-dv (SystemVerilog open source)

- OpenHW Group force-riscv (C++ open source)

- Valtrix STING (commercial)

- Functional Coverage

- Instruction Set Simulators

## CPU DV test bench components

# Constrained Random Instruction Stream Test Generators (ISG)

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- Other components of RISC-V CPU DV environments

- Compliance Tests and other Test Suites

- Instruction Stream Generators

- Google Cloud riscv-dv (SystemVerilog open source)

- OpenHW Group force-riscv (C++ open source)

- Valtrix STING (commercial)

- Functional Coverage

- Instruction Set Simulators

# **Key Features**

01

Randomness

Randomize everything: instruction, ordering, program structure, privileged mode setting, exceptions.. 02

**Architecture Aware**

The generated program should be able to hit the corner cases of the processor architectural features.

03

Performance

The instruction generator should be scalable to generate a large program in a short period of time.

04

Extendability

Easy to add new instruction sequences, custom instruction extension, custom CSR etc.

From Google Cloud presentation 2019 RISC-V Summit

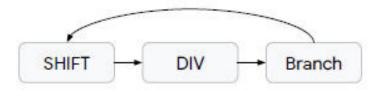

#### Randomness

#### Instruction level randomization

Cover all possible operands and immediate values of each instruction Example: Arithmetic overflow, divide by zero, long branch, exceptions etc.

#### Sequence level randomization

Maximize the possibility of instruction orders and dependencies

#### Program level randomization

Random privileged mode setting, page table organization, program calls

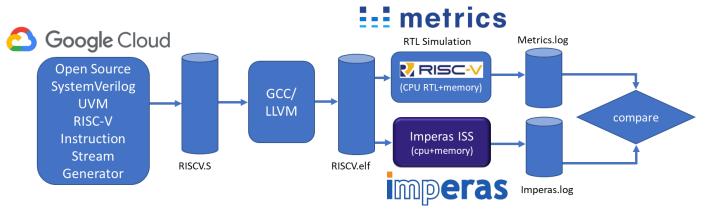

# Google RISC-V Instruction Stream Generation

imperas

- High quality SystemVerilog UVM DV infrastructure

- Open source

- Drives a RISC-V core through corner cases and pushes it to the limit

https://github.com/google/riscv-dv

- Imperas worked on this with Google Cloud & Metrics through 2019-2020

- Uses a post-sim trace-compare methodology

- Uses Imperas riscvOVPsim as the reference

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- Other components of RISC-V CPU DV environments

- Compliance Tests and other Test Suites

- Instruction Stream Generators

- Google Cloud riscv-dv (SystemVerilog open source)

- OpenHW Group force-riscv (C++ open source)

- Valtrix STING (commercial)

- Functional Coverage

- Instruction Set Simulators

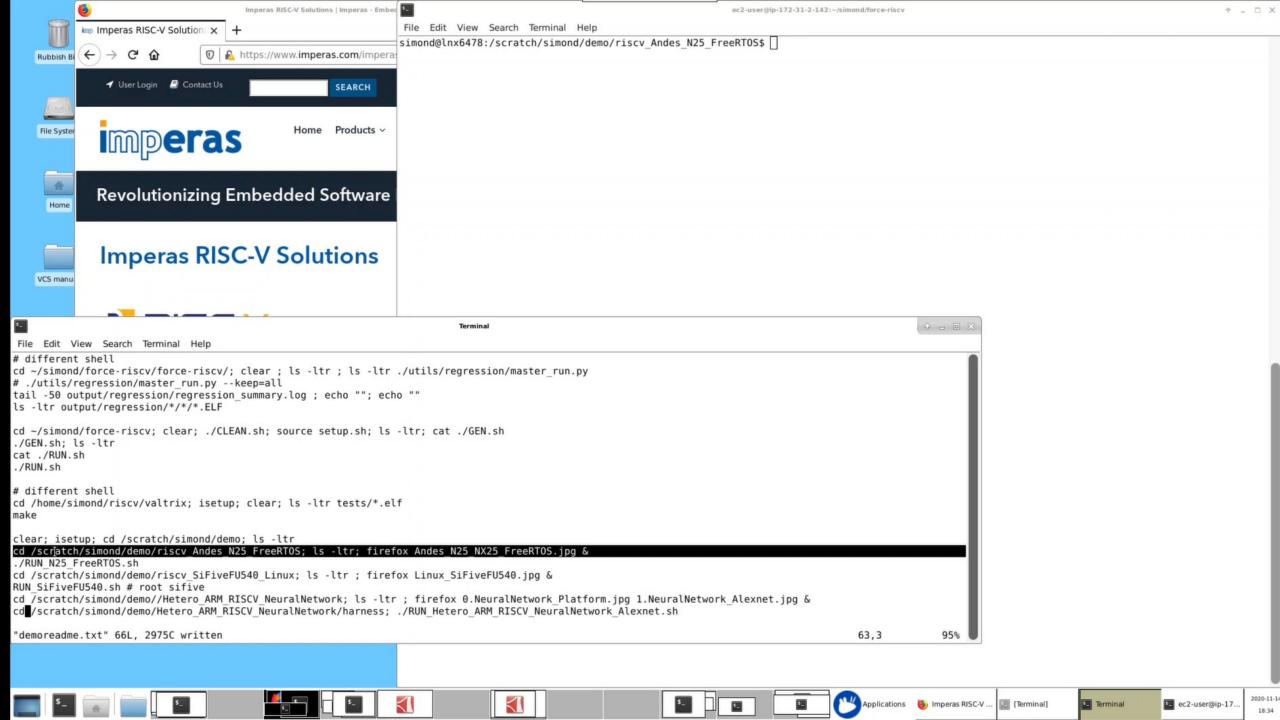

# OpenHW Group force-riscv

- Developed initially by Futurewei

- Open source C++

- https://github.com/openhwgroup/force-riscv

- Initial focus on RV64, recently working on RV32

- Not yet key part of OpenHW flows for core-v cores

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- Other components of RISC-V CPU DV environments

- Compliance Tests and other Test Suites

- Instruction Stream Generators

- Google Cloud riscv-dv (SystemVerilog open source)

- OpenHW Group force-riscv (C++ open source)

- Valtrix STING (commercial)

- Functional Coverage

- Instruction Set Simulators

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- Other components of RISC-V CPU DV environments

- Compliance Tests and other Test Suites

- Instruction Stream Generators

- Functional Coverage

- Instruction Set Simulators

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- Other components of RISC-V CPU DV environments

- Compliance Tests and other Test Suites

- Instruction Stream Generators

- Functional Coverage

- Imperas Built-in Instruction Coverage

- SystemVerilog Covergroups, Coverpoints, Assertions

- Instruction Set Simulators

### Imperas Instruction Coverage

- Built-in as 'extension library' to Imperas models

- Works with all Imperas simulators and RISC-V models

- Focus is for measuring 'architectural validation tests'

- i.e. measurement of basic architectural operations

- Not intended for measuring HW DV testing (use SystemVerilog for that)

- Controlled from command line tailor options for each run

- Outputs .txt file, and .yaml file of data

- After individual runs, collates data into 'suite measured coverage'

- Shows what has, and has not, been covered

- Selectable coverage focus

- --extensions, --instructions

- --mnemonic, --basic, --extended

### ImperasDV Instruction Coverage

- Reference model setup

- Configuration of register and memory initialization

- Selection of what to compare (depends on DUT 'tracer' capabilities):

- PC, GPR, CSR, FPR, VR, decode, net, hart...

- Select capabilities:

- sync-lock-step-compare or async-lock-step-compare

- Trace and logging set up

- Selection of built-in Imperas instruction coverage

- Choice of DV control options

# ImperasDV Instruction Coverage

- Reference model setup

- Configuration of register and memory initialization

- Selection of what to compare (depends on DUT 'tracer' capabilities):

- PC, GPR, CSR, FPR, VR, decode, net, hart...

- Select capabilities:

- sync-lock-step-compare or async-lock-step-compare

- Trace and logging set up

- Selection of built-in Imperas instruction coverage

- Choice of DV control options

ImperasDV includes built-in Imperas Instruction Coverage

### Agenda

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- Other components of RISC-V CPU DV environments

- Compliance Tests and other Test Suites

- Instruction Stream Generators

- Functional Coverage

- Imperas Built-in Instruction Coverage

- SystemVerilog Covergroups, Coverpoints, Assertions

- Instruction Set Simulators

### CPU DV test bench components

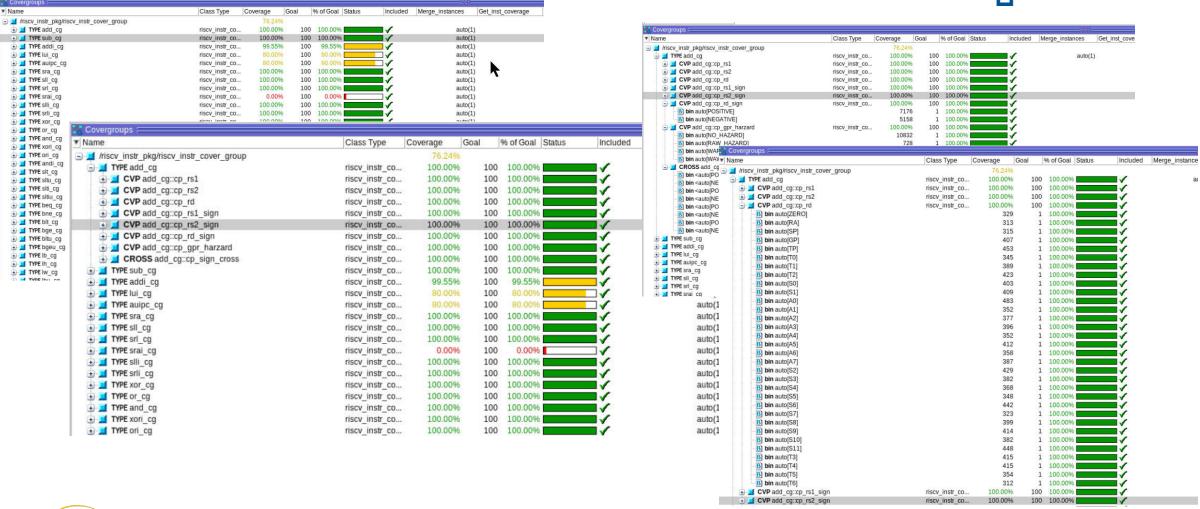

#### SystemVerilog Functional Coverage

- Recall there needs to functional coverage connected to the 'tracer'

- To measure what the architecture and micro-architecture is doing...

Page 119

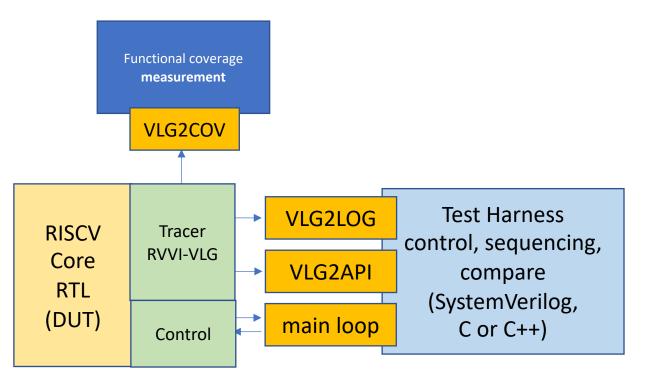

# CPU DV test bench components SystemVerilog Functional Coverage (2)

- And we saw earlier in the detailed ImperasDV walkthrough the connections from the 'tracer' via the RVVI

- From the standard RVVI-VLG there are reusable source 'clients' that connect the 'tracer' to other components

## CPU DV test bench components

SystemVerilog Functional Coverage (3)

We can connect a functional coverage subsystem in the same way

### Connecting RVVI to Covergroups

imperas

- VLG2COV connects to 'tracer' and is informed when events like an instruction retires or interrupt is taken

- On these events VLG2COV

- calls 'sample' in coverage class

- Which then calls the appropriate covergroup sample functions

```

covergroup ins cg with function sample(string ins str);

option.per instance = 1;

102

cp_asm : coverpoint get_asm_enum(ins_str);

103

endgroup

104

105

function new();

ins cg = new();

107

endfunction

108

109

function void sample(input string decode);

110

string ins str, op[4], key, val;

int num = $sscanf (decode, "%s %s %s %s %s", ins str, op[0], op[1], op[2], op[3]);

111

112

ins cq.sample(ins str);

endfunction

114

115 endclass

116

```

```

covergroup sub cg with function sample(ins t ins);

option.per instance = 1;

797

: coverpoint get gpr_name(ins.ops[0].val, ins.ops[0].key, "sub");

798

: coverpoint get gpr name(ins.ops[1].val, ins.ops[1].kev, "sub");

799

: coverpoint get gpr name(ins.ops[2].val, ins.ops[2].key, "sub");

800

801

covergroup sw cg with function sample(ins t ins);

option.per instance = 1:

804

cp_rs2 : coverpoint get_gpr_name(ins.ops[0].val, ins.ops[0].key, "sw");

805

: coverpoint get gpr name(ins.ops[1].val, ins.ops[1].key, "sw");

806

: coverpoint get imm(ins.ops[2].key, "sw") {

807

bins neg = \{[\$:-1]\};

808

bins zero = {0};

809

bins pos = \{[1:\$]\};

810

811

endgroup

812

813

covergroup wfi_cg with function sample(ins_t ins);

814

option.per instance = 1:

815

cp asm : coverpoint ins.asm == WFI {

816

ignore bins zero = \{0\};

817

818

endgroup

819

820

covergroup xor cg with function sample(ins t ins);

821

option.per instance = 1;

822

cp_rd : coverpoint get_gpr_name(ins.ops[0].val, ins.ops[0].key, "xor");

cp rs1 : coverpoint get gpr name(ins.ops[1].val, ins.ops[1].key, "xor");

: coverpoint get gpr name(ins.ops[2].val, ins.ops[2].key, "xor");

endgroup

```

### **RVVI Functional Coverage**

- So the use of a standard interface from DUT 'tracer' to testbench means reusable standard components can be developed

- A key one is a SystemVerilog Functional Coverage sub system

- And for RISC-V standard extensions they can be provided as SystemVerilog source

- And then extended for DV specifics of the specific micro-architecture

- Such as pipeline issues, hazards, assertions design specific items

- Imperas has an example available (Feb2022) and will shortly release others

- (contact Imperas for more information)

# SystemVerilog simulators provide Coverage reports

Coverage reports from Siemens/Mentor Questa

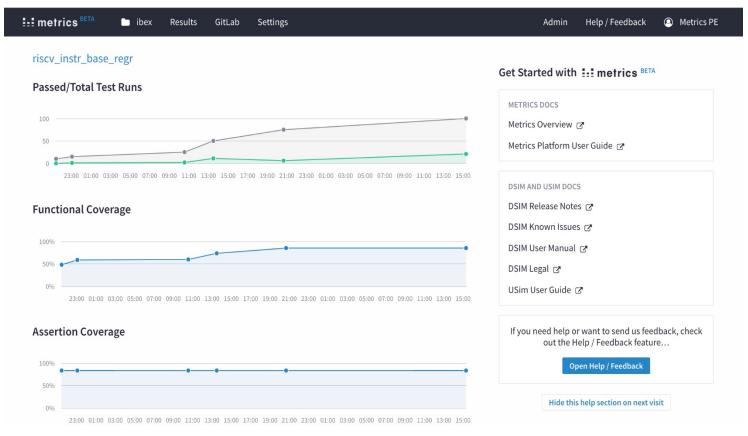

# Metrics: includes top level overview dashboard

Allows management overview of status of verification

### Agenda

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- Other components of RISC-V CPU DV environments

- Compliance Tests and other Test Suites

- Instruction Stream Generators

- Functional Coverage

- Instruction Set Simulators

## Agenda

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- Other components of RISC-V CPU DV environments

- Compliance Tests and other Test Suites

- Instruction Stream Generators

- Functional Coverage

- Instruction Set Simulators

- Free riscvOVPsim (github)

- Free riscvOVPsimPlus (ovpworld.org)

- Commercial M\*SIM (imperas.com)

- Commercial M\*SDK (imperas.com)

- Commercial ImperasDV (imperas.com)

# Imperas Tools for Embedded Software Development, Debug & Test

Page 129

### **ISS: Summary**

- Only mentioned Imperas simulators (as we use daily, our customers rely on them, and we understand their quality)

- There are others...

- There are many open source grad. student project simulators... go search github...

- RISC-V has a formal model under development 'sail'

- There is also spike from Berkeley for architectural exploration

- And there are full system software emulators like qemu

- Free: github: riscvOVPsim.exe

- Model selection configuration

- Signature, logs, coverage

- Includes rv32I tests

- Useful for compliance tests

- Free: ovpworld.org (needs registration): riscvOVPsimPlus.exe

- As riscvOVPsimPlus

- trace, debug

- Useful for post-sim-trace-compare, e.g. in Google riscv-dv

- Commercial from Imperas the industry leader in processor based simulation solutions

- Full range of ISS, virtual platforms, full system emulation, fixed & extendable platforms

- 50 reference platforms, 250+ peripheral components, 300+ processor models

### Agenda

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- Other components of RISC-V CPU DV environments

- Summary

Congratulations... on getting to the end of this tutorial

- if you got this far and still have some energy...

- send us an email (<u>info@imperas.com</u>) with

- Subject: imperasdv at dvcon22 tutorial

- With: comments on this tutorial

- and we will send the first 50 of you one of our ImperasDV drinking mugs.

### We covered...

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- Components of RISC-V CPU DV environment

## We covered (2)

- Brief Introduction to RISC-V

- RISC-V CPU HW DV approaches

- #0 "hello world" test

- #1 self checking tests (e.g. Berkeley torture tests pre2018)

- #2 Post simulation trace log file compare (e.g. Google riscv-dv 2019)

- #3 sync-lock-step-compare (e.g. CV32E40P in OpenHW 1H 2020)

- #4 async-lock-step-compare (e.g. CV32E40P in OpenHW 2H H2020)

- #5 test bench use of standards (RVVI) (e.g. CV32E40X/S in OpenHW 2021)

- #6 using standards based DV products and VIP (ImperasDV)

- And had a 35 minute walk through

# We covered (3)

imperas

- Components of RISC-V CPU DV environment

- Compliance Tests and other Test Suites

- RISC-V architectural test suites

- Imperas architectural test suites

- Bremen fuzz testing

- Instruction Stream Generators

- Google riscv-v

- OpenHW force-riscv

- Valtrix STING

- Functional Coverage

- Imperas build-in instruction coverage

- SystemVerilog covergroups and coverpoints

- Instruction Set Simulators & tools

- Free riscvOVPsim (github)

- Free riscvOVPsimPlus (ovpworld.org)

- Commercial M\*SIM (imperas.com)

- Commercial M\*SDK (imperas.com)

- Commercial ImperasDV (imperas.com)

### What we did not talk about...

- SystemVerilog encapsulation of Imperas models (yes we do that)

- Using ISS with RTL emulators

- Including hybrid simulation (yes we do that)

- Formal tools

- (no we don't do these...)

### Summary

- The open standard ISA of RISC-V offers many design freedoms

- Many standard extensions and configuration options plus custom instructions

- The key verification requirements are to detect discrepancies with efficient debug

- The open standard RVVI offers a framework for verification reuse with support for both open-source and commercial tools

- RISC-V Verification Interface

- https://github.com/riscv-verification/RVVI

- Lockstep / Compare is by far the best and most efficient approach (industry 'gold standard')

- https://www.imperas.com/imperasdv

### Thank You!

info@imperas.com

www.imperas.com

www.imperas.com/ImperasDV

www.OVPworld.org

# Questions?