# How to leverage the power of MATLAB from Functional Verification Test Benches

Tom Richter - MathWorks

#### Agenda

- Verification Challenges

- Why MATLAB?

- Verification options

- Co-simulation with MATLAB® on top

- Co-simulation with HDL Simulator on top

- SystemVerilog DPI component generation

- UVM testbenches and components

- Questions

# Verification Challenges

- The complex nature of the design

- Time and resource limitation

- Stimulus generation

- Golden reference model creation

- Verify that the deployed algorithm works the same as the reference

- Are all requirements implemented and tested?

- Used in many domains such as signal processing, image processing and communications

- There, it is de facto standard language to explore, evaluate, and design architectures and algorithms

- MATLAB environment and its add-on products:

- Intuitively learnable high-level programming language

- Huge library of Functions, Classes, and System Objects

- Diverse visualization options

- Many apps, functions and objects for signal generation

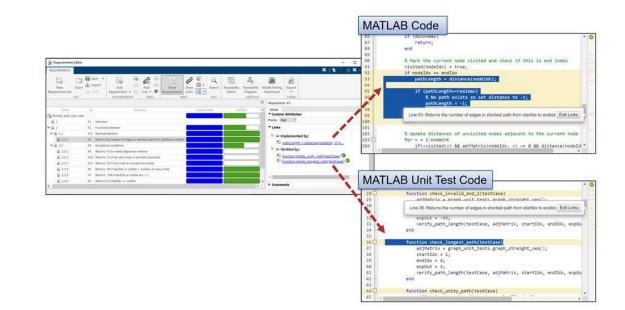

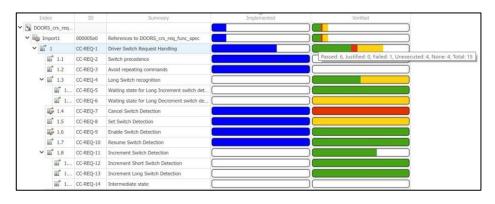

#### Requirement Implementation and Testing

- MathWorks offers also tools to

- associate requirements with MATLAB code and

- plain-text external code, such as C code,

- This is achieved by

- creating selection-based links with the Requirements Editor or

- creating links programmatically at the MATLAB command line.

- Verify requirements with MATLAB code by creating links to MATLAB unit tests and running the tests

- View and edit links to code

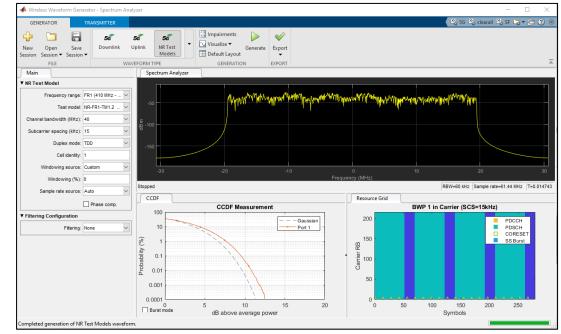

#### Stimulus - Wireless Waveform Generator App

Certain MATLAB add-on come with rich features for waveform generation, full system simulation, and visualization.

- Waveform Generator App from 5G Toolbox offers:

- Off-the-shelf waveforms : NR-TMs/FRCs

- Custom downlink & uplink waveforms

- CCDF measurement

- Export waveform or generate code

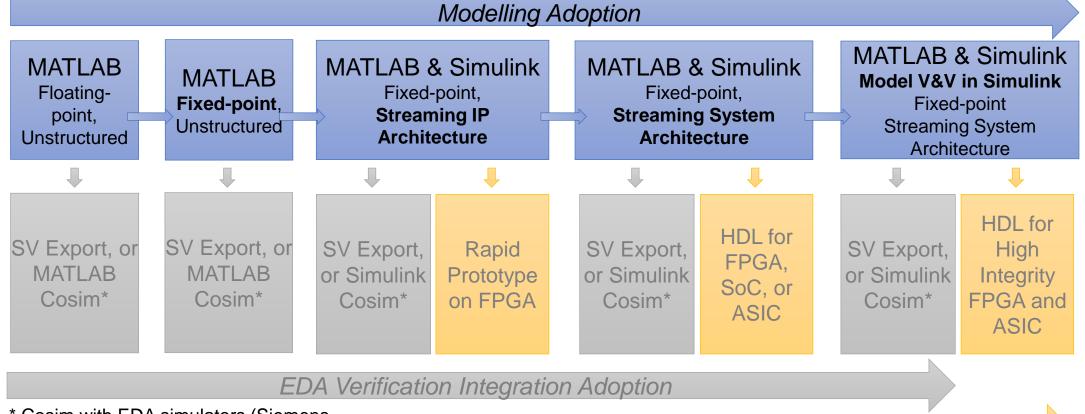

### Verification with MATLAB and Simulink

- Early verification and prototyping capabilities

- FPGA-in-the-loop on FPGA and SoC boards

- Automated insertion of probes into FPGA netlists for viewing and analysis

- Hardware-based testing through read/write access to AXI registers and DDR

- Capabilities for functional verification

- Co-simulation with HDL simulators from Siemens<sup>®</sup> EDA, Cadence<sup>®</sup>, and AMD<sup>®</sup>

- SystemVerilog DPI components and testbenches from MATLAB and Simulink

- Universal Verification Methodology (UVM) testbenches and components

#### Three ways to do Co-Simulation in MATLAB

There are three options to achieve co-simulation with MATLAB by using a MATLAB:

- System Object hdlverifier.HDLCosimulation or hdlcosim

- Callback function in combination with the instance **matlabtb**

- Callback function in combination with the instance **matlabcp**

#### MATLAB on Top - Workflow

Using a Co-Simulation System Object is considered to be a "MATLAB on top – workflow":

- MATLAB will be the manager

- Creates stimuli for the device under test (e.g.: manually written RTL)

- Controls the compilation of the HDL files

- Launches the HDL simulator tool (GUI or batch mode)

- Sends stimuli to the HDL simulator continually (sample or frame based)

- Receives simulated data from the HDL simulator

- Compares, visualizes, or postprocesses the received data

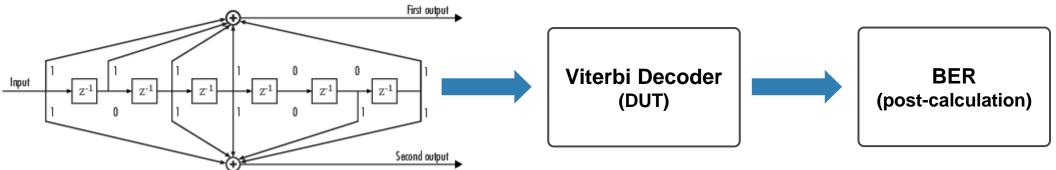

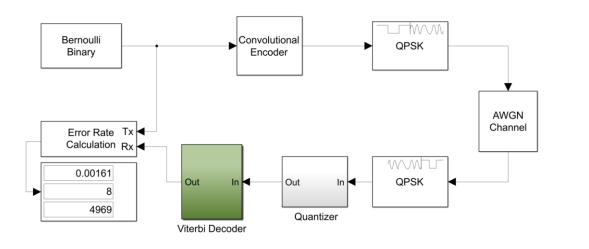

### Example – Verify a Viterbi Decoder (VVD)

The Viterbi decoding algorithm is still used in space communications, voice recognition, ..., and DNA sequencing. Assume:

- The algorithm was developed and tested in MATLAB

- VHDL code was manually written following the same specs

- You think about reusing the MATLAB code for verification

### Example VVD – Reference Algorithm

- System design

- Write code (unstructured, floating point)

- Test algorithms

| 2                                                                                                     | EsNo = 3; % Energy per symbol to noise power spectrum density ratio in dB<br>FrameSize = 1024; % Number of bits in each frame                                                                                                                                                                                                     |

|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                       | Convolution Encoder                                                                                                                                                                                                                                                                                                               |

| L                                                                                                     | hConEnc = comm.ConvolutionalEncoder; % TrellisStructure = poly2trellis(7, [171 133]) - default                                                                                                                                                                                                                                    |

|                                                                                                       | QPSK Modulator                                                                                                                                                                                                                                                                                                                    |

| 5                                                                                                     | hMod = comm.QPSKModulator('BitInput',true);                                                                                                                                                                                                                                                                                       |

|                                                                                                       | AWGN channel                                                                                                                                                                                                                                                                                                                      |

| 5<br>7<br>3<br>9                                                                                      | <pre>hChan = comm.AWGNChannel('NoiseMethod',<br/>'Signal to noise ratio (Es/No)',<br/>'SamplesPerSymbol',1,<br/>'EsNo',EsNo);</pre>                                                                                                                                                                                               |

|                                                                                                       | QPSK Demodulator                                                                                                                                                                                                                                                                                                                  |

| Ð                                                                                                     | <pre>hDemod = comm.QPSKDemodulator('DecisionMethod','Log-likelihood ratio',<br/>'Variance',0.5*10^(-EsNo/10),'BitOutput',true);</pre>                                                                                                                                                                                             |

|                                                                                                       | Viterbi Decoder (MATLAB simulation)                                                                                                                                                                                                                                                                                               |

| 2                                                                                                     | <pre>hDecSim = comm.ViterbiDecoder('TracebackDepth',32, % TrellisStructure = poly2trellis(7, [171 133]) - default</pre>                                                                                                                                                                                                           |

|                                                                                                       | Error Rate Calculator                                                                                                                                                                                                                                                                                                             |

| 1                                                                                                     | <pre>receiveDelay = 32; % TracebackDepth hError = comm.ErrorRate('ComputationDelay',100,'ReceiveDelay',receiveDelay);</pre>                                                                                                                                                                                                       |

|                                                                                                       | Visualization                                                                                                                                                                                                                                                                                                                     |

| 5<br>7<br>3<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9 | <pre>hScope = timescope("NumInputPorts",2,"LayoutDimensions",[2,1],"ChannelNames", {'Input', 'Received'},<br/>"SampleRate",100e6,"TimeUnits","seconds","TimeSpan",10e-7,"PlotType","stairs");<br/>hScope.ActiveDisplay = 1;<br/>hScope.YLimits = [0 1];<br/>hScope.YLimits = [0 1];<br/>hScope.Position = [27 225 800 500];</pre> |

| 1<br>5<br>5                                                                                           | <pre>hConstDiag = comm.ConstellationDiagram("NumInputPorts",2,"ChannelNames", {'Modulated','Received'}, "XLimits",[-3 3],"YLimits",[-3 3],"ShowReferenceConstellation",false,'ShowLegend',true,'ColorFading',true); hConstDiag.Position = [833 175 600 600];</pre>                                                                |

|                                                                                                       | 4                                                                                                                                                                                                                                                                                                                                 |

# Example VVD – Refine Reference Algorithm

- Research on algorithm implementation

- Write code (unstructured, fixed-point)

- Test algorithm against reference

|      | <u> </u>                                                                  |     |

|------|---------------------------------------------------------------------------|-----|

| 10   | <pre>function y = TBU(dec, index)</pre>                                   | ^ @ |

| 2    |                                                                           |     |

| 3    | % traceback storage register                                              |     |

| 4    | persistent tb_reg;                                                        |     |

| 5    | <pre>if isempty(tb_reg)</pre>                                             |     |

| 6    | <pre>tb_reg = getfi(zeros(1,64), 0, 32, 0);</pre>                         |     |

| 7    | end                                                                       |     |

| 8    |                                                                           |     |

| 9 🗄  | %                                                                         |     |

| 10   | % TBU (Trace Back Unit)                                                   |     |

| 11   | %                                                                         |     |

| 12   |                                                                           |     |

| 13   | % stores path metric decision inforamtion from PMU unit                   |     |

| 14   | <pre>tb_reg = bitconcat(bitsliceget(tb_reg, 31, 1), dec);</pre>           |     |

| 15   |                                                                           |     |

| 16   | % trace back unit                                                         |     |

| 17   | for i=1:32                                                                |     |

| 18   | <pre>index = tbunit(index, tb_reg, i);</pre>                              |     |

| 19   | end                                                                       |     |

| 20   |                                                                           |     |

| 21   | % the 6th bit of the 32th trace back step is the decoder output           |     |

| 22   | <pre>tband = bitget(index, 6);</pre>                                      |     |

| 23   | <pre>y = logical(tband);</pre>                                            |     |

| 24   |                                                                           |     |

| 25   | end                                                                       |     |

| 26   |                                                                           |     |

| 27 🗐 | <pre>function new_idx = tbunit (current_idx, tb_reg, stage)</pre>         |     |

| 28   |                                                                           |     |

| 29   | <pre>idx = int32(current_idx) + int32(1);</pre>                           |     |

| 30   | <pre>tbread = bitget(tb_reg(idx), stage);</pre>                           |     |

| 31   |                                                                           |     |

| 32   | <pre>shift_idx = bitconcat(bitsliceget(current_idx, 5, 1), tbread);</pre> |     |

| 33   | <pre>new_idx = bitconcat(getfi(0, 0, 2, 0), shift_idx);</pre>             |     |

| 34   |                                                                           |     |

| 35   | end                                                                       |     |

| 36   |                                                                           | -   |

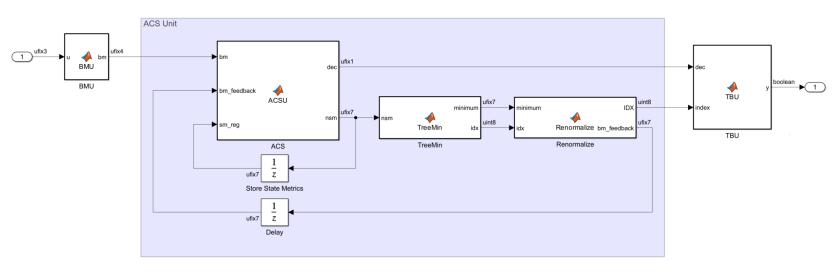

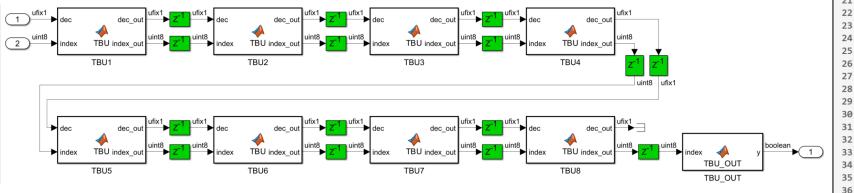

### Example VVD – Streaming Algorithm

- Research on IP requirements

- Refine code (streaming, fixed-point)

- Test algorithm against unstructured fixed-point reference

function [dec\_out, index\_out] = TBU(dec, index) 2 % TBU (Trace Back Unit) 3 4 % initialize 4-stage trace back storage shift register 5 persistent tb\_reg1 tb\_reg2 tb\_reg3 tb\_reg4 6 if isempty(tb reg1) 7 tb reg1 = getfi(zeros(1, 64), 0, 1, 0); 8 end 9 if isempty(tb reg2) 10 tb\_reg2 = getfi(zeros(1, 64), 0, 1, 0); 11 end 12 if isempty(tb reg3) 13 tb\_reg3 = getfi(zeros(1, 64), 0, 1, 0); 14 end 15 if isempty(tb reg4) 16 tb\_reg4 = getfi(zeros(1, 64), 0, 1, 0); 17 end 18 19 % 4-stage trace back storage shift register 20 dec out = tb reg4; 21 tb reg4 = tb reg3; tb\_reg3 = tb\_reg2; tb\_reg2 = tb\_reg1; tb reg1 = dec; 25 26 % stage one idx = int32(index) + int32(1); tbread = tb\_reg1(idx); shift\_idx = bitconcat(bitsliceget(index, 5, 1), tbread); index = bitconcat(getfi(0, 0, 2, 0), shift idx); 32 % stage two 33 idx = int32(index) + int32(1);34 tbread = tb reg2(idx); shift\_idx = bitconcat(bitsliceget(index, 5, 1), tbread);

index = bitconcat(getfi(0, 0, 2, 0), shift\_idx);

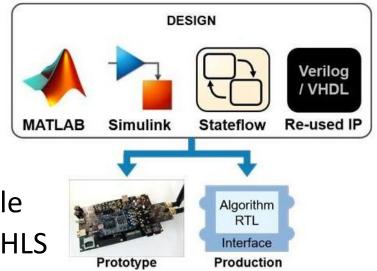

# Example VVD – Integration Decision

Depending on your final target (FPGA/ASIC/SoC) and preferences you may now decide how to resume in the integration process.

- Manually writing RTL code

- High-level synthesis

- Automatic code generation, e.g.: <u>HDL Coder™</u>:

- Synthesizable VHDL, Verilog, and SystemVerilog code

- Fully generic, target independent, readable, and traceable

- Synthesizable SystemC code and testbench for Stratus<sup>™</sup> HLS

- Support for vertical products for AI, DSP, Comms, and Vision

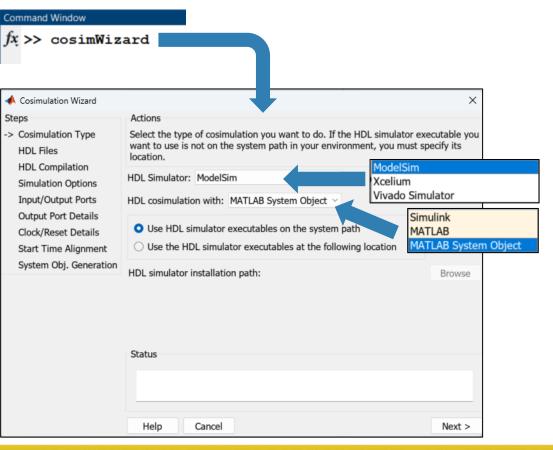

### Example VVD – Prepare Co-Simulation

The Cosimulation Wizard helps you with:

- Creating a MATLAB System Object or callback function from a template

- Preparing the tcl-commands for the HDL simulator

Function

compile\_hdl\_design\_viterbi\_block.m

hdlcosim\_viterbi\_block.m

Script

launch hdl simulator viterbi block.m

Adapt the generated files for your needs

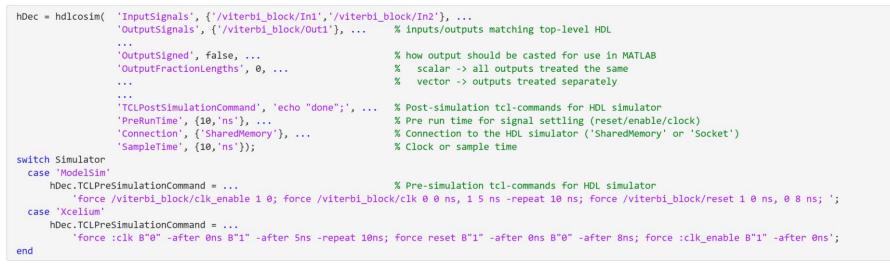

#### Example VVD – Launch HDL Simulator

• Modify the System Object code if necessary

• Launch the HDL Simulator (that compiles the code and sets up the tool)

```

switch Simulator

case 'ModelSim'

vsim('tclstart',viterbi_cosimulation_tclcmds('vsimmatlabsysobj'),"runmode","Batch");

case 'Xcelium'

nclaunch('tclstart',viterbi_cosimulation_tclcmds('hdlsimmatlabsysobj'));

end

```

Δ

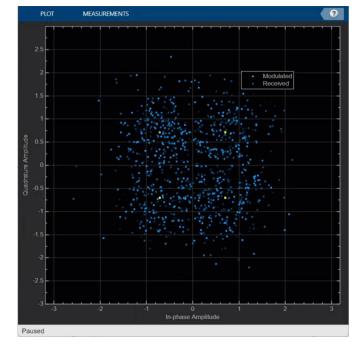

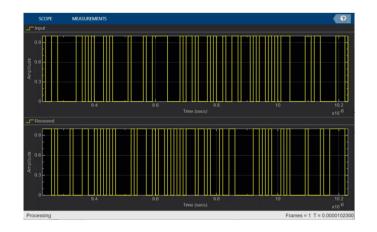

#### Example VVD – Run Co-Simulation

#### • Create a loop to run the whole transceiver chain

```

receiveDelay = 58;

% TracebackDepth + Pipeline Delay

hError = comm.ErrorRate('ComputationDelay',100, 'ReceiveDelay', receiveDelay);

hScope.reset;

rng(1)

for counter = 1:20480/FrameSize

% Run 20480 samples with frame-processing 1024 samples/frame

= randi([0 1],FrameSize,1);

% Generate a pseudo-random bit sequence initialized (seed 1)

data

% Convolution Encoder

encodedData

= hConEnc(data);

modSignal

= hMod(encodedData);

% OPSK Modulator

receivedSignal = hChan(modSignal);

% AWGN Channel

demodSignalSD = hDemod(receivedSignal);

% OPSK Demodulator

quantizedValue = fi(4-demodSignalSD,0,3,0);

% Quantization

input1

= quantizedValue(1:2:2*FrameSize); % Input Preparation

input2

= quantizedValue(2:2:2*FrameSize);

receivedBits

= hDec(input1, input2);

% Run Viterbi Decoder on HDL Simulator

= hError(data, double(receivedBits)); % Calculate Bit Error Rate

errors

hScope(data, receivedBits)

% Show transmitted and received random sequence in a Scope

hConstDiag(modSignal, receivedSignal)

% Show constellation of modulated transmitted and received signal

```

• Compare the results with the simulation reference

fprintf('Bit Error Rate is %d\n',errors(1))

Bit Error Rate is 3.493751e-03

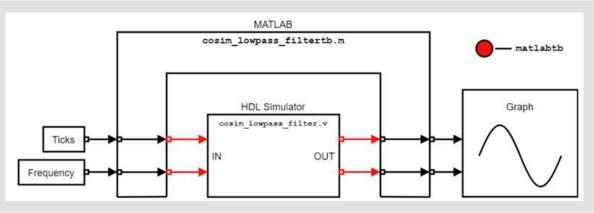

#### HDL Simulator on Top - Workflow

Using callback functions in MATLAB and instances like **matlabtb** or **matlabcp** made known to the HDL Simulator we call the workflow "HDL Simulator on top ":

- MATLAB just works in the background

- It needs to run the HDL Link MATLAB server using shared memory interprocess communication

- HDL Simulator controls the whole simulation

- Triggers the callback function in MATLAB

- Sends/requests data to/from MATLAB

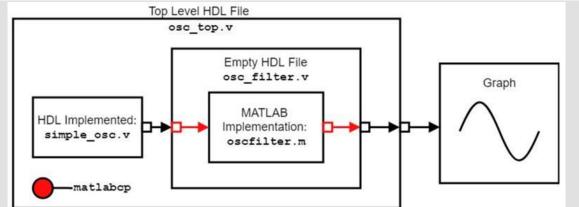

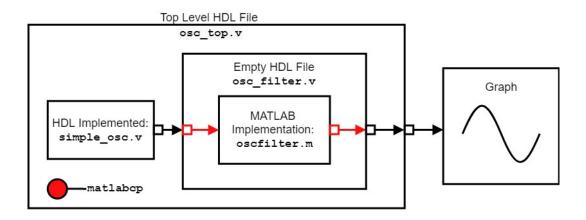

#### Component vs. Testbench

# matlabcpmatlabtbTest your HDL code in an HDL Simulator but a certain<br/>component which does not yet exists in HDL will be<br/>simulated through MATLAB. Testbench exists in EDA tool.Drive stimuli from MATLAB to an HDL component and send<br/>the output back to MATLAB. Testbench exists in MATLAB<br/>but is controlled (called) from the HDL Simulator.It sends output from HDL Simulator to MATLAB and receives<br/>input to HDL from Simulator MATLABAcquire input to HDL Simulator from MATLAB and send<br/>back output from HDL Simulator to MATLAB

Implement Filter Component of Oscillator in MATLAB

Cosimulation for Testing Filter Component Using MATLAB Test Bench

# Example – MATLAB Filter Component (MFC)

The following steps are required to create and test a MATLAB component that can be used from an HDL Simulator:

- Generate a Callback Template

- Integrate your MATLAB function into the template files

- Modify the generated tcl-file

- Start the HDL Link MATLAB server

- Run existing testbench in HDL Simulator

# Example (MFC) – Cosimulation Wizard

The Cosimulation Wizard helps again with:

- Creating a callback function from a template

- Preparing the tcl-commands

|                         |                                            |                                                                                                                                                                                            |   | HDL Compilation      | Callback type: matlabcp · Callback function name: ofdmTxResourceGridCB                                |

|-------------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------------|-------------------------------------------------------------------------------------------------------|

|                         | Cosimulation Wizard                        |                                                                                                                                                                                            |   | HDL Modules          | HDL component: /OFDM_Tx_Resource_Grid Browse                                                          |

|                         | Steps<br>-> Cosimulation Type<br>HDL Files | Actions<br>Select the type of cosimulation you want to do. If the HDL simulator executable you want to us<br>is not on the system path in your environment, you must specify its location. | 2 | -> Callback Schedule | Trigger mode:     Repeat     Sample time (ns):     320                                                |

|                         | HDL Compilation                            | HDL Simulator: ModelSim                                                                                                                                                                    |   | Script Generation    | Add Remove<br>MATLAB Callback Functions                                                               |

| Command Window          | HDL Modules<br>Callback Schedule           | HDL cosimulation with: MATLAB<br>• Use HDL simulator executables on the system path                                                                                                        |   |                      | matlabcp /OFDM_Tx_Resource_Grid 320 ns -repeat 320 ns -mfunc ofdmTxResourceGridCB.m -use_instance_obj |

| $f_{x} >> $ cosimWizard | Script Generation                          | O Use the HDL simulator executables at the following location HDL simulator installation path: Browsee                                                                                     |   |                      |                                                                                                       |

|                         |                                            |                                                                                                                                                                                            |   |                      |                                                                                                       |

|                         |                                            |                                                                                                                                                                                            |   |                      | Status                                                                                                |

|                         |                                            | Status                                                                                                                                                                                     |   |                      |                                                                                                       |

|                         |                                            |                                                                                                                                                                                            |   |                      |                                                                                                       |

|                         |                                            | Help Cancel Next >                                                                                                                                                                         |   |                      | Help Cancel < Back Next >                                                                             |

Notice to the test of test of

Cosimulation Type

HDL Files

generated commands

Steps

Enter the required parameters for scheduling MATLAB callback function. When finished, use the 'Add' button to generate matlabtb or

matlabcp commands that associates MATLAB function with an instantiated HDL design. If necessary, use the 'Remove' button to remove

# Example (MFC) – Callback Template

Two options for MATLAB component function writing:

- Using the HDL Instance Object (used for the template)

- MATLAB function prototype: function matlabFuncName(obj)

- Object field examples:

- obj.portvalues, obj.tnow, obj.userdata, obj.simstatus, obj.argument, obj.portinfo

```

function oscfilter(obj)

%

% MATLAB Callback function template

% OSCFILTER HDL simulator example "Osc"

```

- TCL command: matlabcp hdlInstanceName -mfunc matlabFuncName -use instance obj

- Using Port Information

• MATLAB function prototype:

- function [oport,tnext] = oscfilter(iport, tnow, portinfo)

%

% MATLAB Callback function template

% OSCFILTER HDL simulator example "Osc"

- function [oport, tnext] = matlabFuncName(iport, tnow, portinfo)

- TCL command: matlabcp hdlInstanceName -mfunc matlabFuncName

# Example (MFC) – Run Co-Simulation

Run the HDL Link MATLAB server for communication between the HDL simulator and MATLAB:

In an open MATLAB session run:

> hdldaemon

- You can also open a MATLAB session in batch mode:

- Windows cmd: matlab -nodesktop -r "hdldaemon"

- Linux shell: xterm -e "matlab -nodesktop -r "hdldaemon"" &

- Start the cosimulation

- Windows cmd: vsim -do qcommands\_osc\_w.tcl

- Linux shell: vsim -do qcommands\_osc\_1.tcl

(here ModelSim was used)

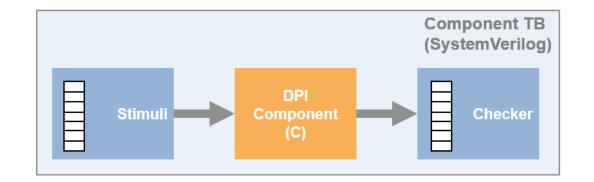

# SystemVerilog – DPI Component Generation

- Export a MATLAB function as a component with a direct programming interface (DPI) for use in a SystemVerilog simulation

- MATLAB Coder is used for generating C code with a DPI wrapper

- The DPI wrapper communicates with a SystemVerilog interface function

- The SystemVerilog component can be used within a SystemVerilog testbench

- Get DPI component shared library for:

- Linux (.so) or Windows (.dll)

- Templates to influence component

- Sequential sequential design, with registers

- Combinational with no registers

- Different choices for port data types

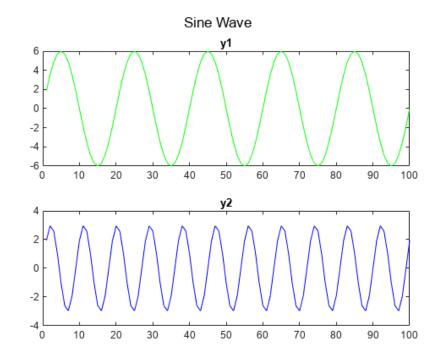

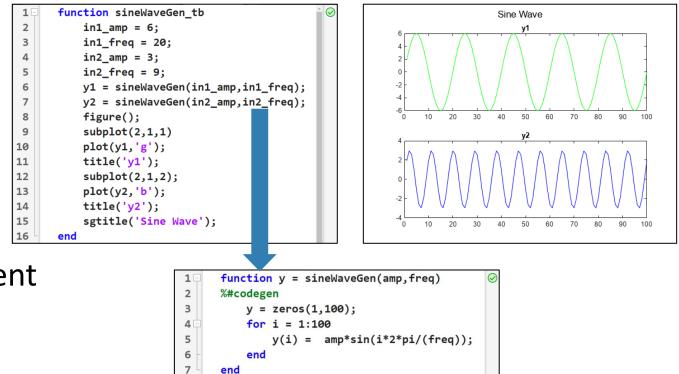

### Example – Sine Wave Generator (SWG)

The following steps are required to generate a SystemVerilog DPI component:

- Prepare a MATLAB function for code generation

- Create a MATLAB testbench file (optional)

- Define and set a configuration object (optional)

- Generate the component using dpigen

- Verify your component with a generated testbench (optional)

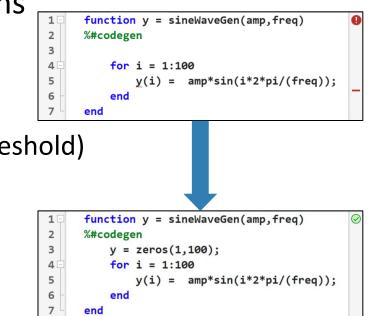

# Example (SWG) – Prepare Function

Before generating the component from MATLAB code ensure to:

- Initialize variables and define them on all execution paths

- Define static variables as persistent (states, registers)

- Avoid dynamic memory allocation for efficiency

- Rather use fixed-size arrays and variable-size arrays (size < threshold)

- To identify issues:

- Use %#codegen pragma to instruct the MATLAB Code Analyzer to help with finding and fixing violations

- Run the Code Screener

# Example (SWG) – MATLAB Testbench

A MATLAB testbench is an optional file. However, it helps with:

- Defining port

- data types,

- sizes, and

- complexity

- Testing and debugging the MATLAB function

- Verifying the generated component

# Example (SWG) – Configuration

#### • Create a **svdpiConfiguration** object

- The default configuration points to the templates for a sequential module (component and testbench template)

- clk, clk\_en, reset inputs

- Change component and testbench name, and SystemVerilog port types

```

svcfg=svdpiConfiguration

svcfg =

svdpiConfiguration with properties:

ComponentKind: 'sequential-module'

CoderConfiguration: [1x1 coder.EmbeddedCodeConfig]

ComponentTypeName: ''

TestBenchTypeName: ''

TestBenchTypeName: ''

TemplateDictionary: []

PortGroups: []

ComponentTemplateFiles: {'/mathworks/devel/bat/Bdoc23a/build/matlab/toolbox/hdlverifier/dpigenerator/rtw/SequentialTestBenchML.svt'}

```

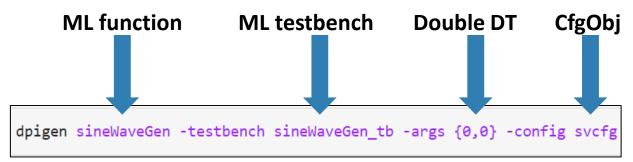

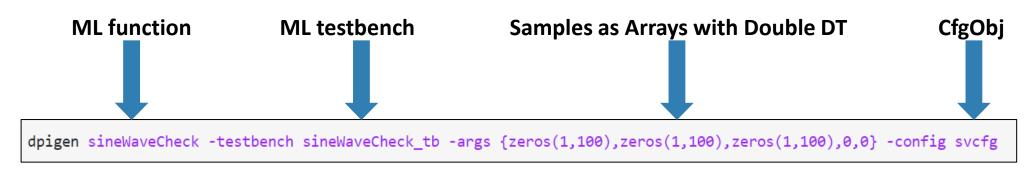

# Example (SWG) – Component Generation

Use the **dpigen** function to generate the component artefacts. You can:

- Define the MATLAB function and optionally the MATLAB testbench

- Provide sample data for input arguments

- Set a configuration object or separately:

- Custom include files

- Compiler options

- SystemVerilog Port data types

- Component templates

• Generate and launch a code generation report

# Example (SWG) – Package Required Files

With the **packNGo** function you can zip all the required Files.

• Easily share the generated artefacts

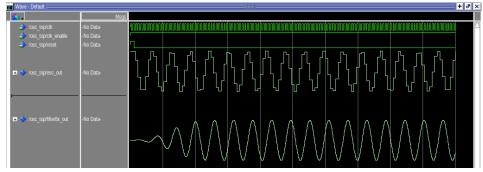

# Example (SWG) – Verify Component

When generating the component including testbench you can directly verify it with an HDL simulator

- A \*\_tb.sv file is generated together with data files for stimuli and expected output

- tcl-scripts provided for compiling and running the testbench in:

- ModelSim<sup>™</sup>/QuestaSim<sup>™</sup>

- Cadence<sup>®</sup> Xcelium<sup>™</sup>

- Synopsys<sup>®</sup> VCS<sup>TM</sup>

- AMD<sup>®</sup> Vivado<sup>TM</sup>

sineWaveGen

dpi\_tb

dpig\_in1.dat

dpig\_in2.dat

dpig\_out1.dat

run\_tb\_mq.do

run\_tb\_vcs.sh

run\_tb\_vivado.bat

run\_tb\_vivado.sh

run\_tb\_xcelium.sh

sineWaveGen\_tb.sv

| C:\WINDOWS\SYSTEM32\cmc × + ~                                                                  | -     | × |

|------------------------------------------------------------------------------------------------|-------|---|

| Microsoft Windows [Version 10.0.22621.2134]<br>(c) Microsoft Corporation. All rights reserved. |       |   |

| C:\codegen\dll\sineWaveGen\dpi_tb>vsim < run_tb_                                               | mq.do |   |

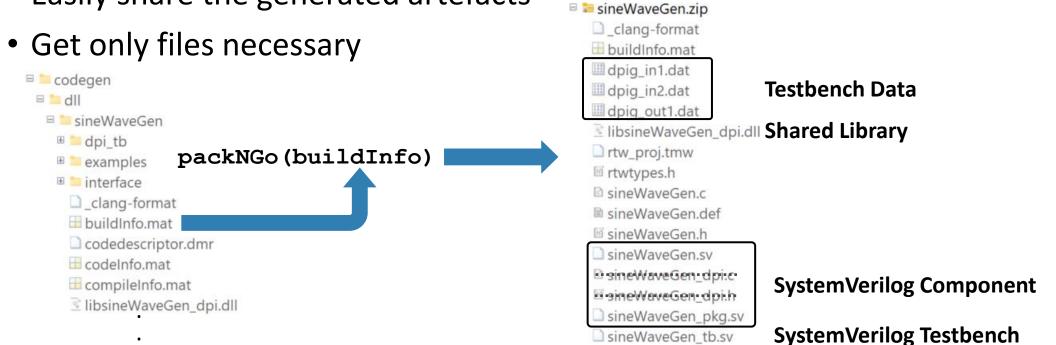

#### UVM Component Generation from MATLAB

In addition of generating a general SystemVerilog DPI component, further template files enable also the generation of UVM components.

- Can integrate into a full UVM testbench

- Templates for component and testbench:

- Predictor

- Sequence

- Scoreboard

| S | SVT File                                                                                                                                                                                                                |  |  |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|   | CombinationalModuleML.svt                                                                                                                                                                                               |  |  |

|   | CombinationalTestBenchML.svt                                                                                                                                                                                            |  |  |

|   | PredictorComponentML.svt                                                                                                                                                                                                |  |  |

|   | PredictorTestBenchML.svt                                                                                                                                                                                                |  |  |

|   | ScoreboardComponentML.svt                                                                                                                                                                                               |  |  |

|   | ScoreboardTestBenchML.svt                                                                                                                                                                                               |  |  |

|   | SequenceComponentML.svt                                                                                                                                                                                                 |  |  |

|   |                                                                                                                                                                                                                         |  |  |

|   | SequenceTestBenchML.svt                                                                                                                                                                                                 |  |  |

|   | SequenceTestBenchML.svt SequentialModuleML.svt                                                                                                                                                                          |  |  |

|   |                                                                                                                                                                                                                         |  |  |

|   | SequentialModuleML.svt                                                                                                                                                                                                  |  |  |

|   | SequentialModuleML.svt<br>SequentialModuleVarSizeInterfaceML.svt                                                                                                                                                        |  |  |

|   | <ul> <li>Sequential Module ML.svt</li> <li>Sequential Module Var Size Interface ML.svt</li> <li>Sequential Module Var Size ML.svt</li> </ul>                                                                            |  |  |

|   | <ul> <li>SequentialModuleML.svt</li> <li>SequentialModuleVarSizeInterfaceML.svt</li> <li>SequentialModuleVarSizeML.svt</li> <li>SequentialTestBenchML.svt</li> </ul>                                                    |  |  |

|   | <ul> <li>SequentialModuleML.svt</li> <li>SequentialModuleVarSizeInterfaceML.svt</li> <li>SequentialModuleVarSizeML.svt</li> <li>SequentialTestBenchML.svt</li> <li>SequentialTestBenchVarSizeInterfaceML.svt</li> </ul> |  |  |

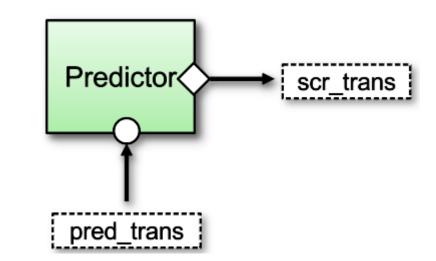

#### UVM – Predictor component

The predictor template generates a UVM predictor module that has:

- an export that inputs a predictor transaction, and

- an analysis port that outputs a scoreboard transaction.

- The predictor template includes these variables:

- ComponentTypeName

- TestBenchTypeName

- ComponentPackageTypeName

- InputTransTypeName

- OutputTransTypeName

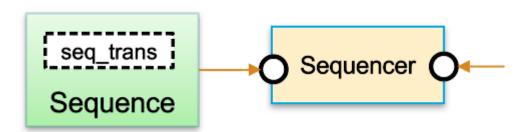

#### UVM – Sequence component

The sequence template generates a UVM sequence module.

- It includes these variables:

- ComponentTypeName

- TestBenchTypeName

- ComponentPackageTypeName

- SequenceTransTypeName

- SequencerTypeName

- SequenceCount

- SequenceFlushCount

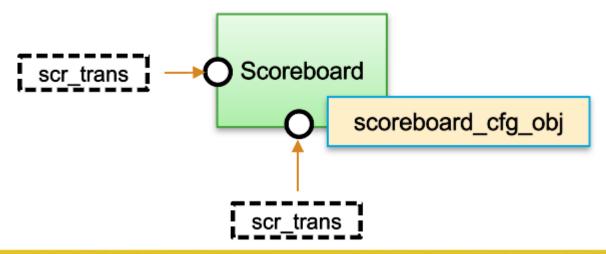

#### UVM – Scoreboard component

The scoreboard template generates a UVM scoreboard module that has two exports that input a scoreboard transaction.

- The scoreboard template includes these variables:

- ComponentTypeName

- TestBenchTypeName

- ComponentPackageTypeName

- InputTransTypeName

- OutputTransTypeName

- ConfigObjTypeName

- Map ports to port groups by using the addPortGroup object function.

# Example – Sine Wave Check (SWC)

The following steps are required to generate a UVM component:

- Prepare a MATLAB scoreboard function

- Create a MATLAB testbench file (optional)

- Define a configuration object (required)

- Provide UVM settings to the cfgobj

- Specify which port belongs to which port group

- Generate the component using dpigen

- Verify your component with a generated testbench (optional)

Scoreboard

scr trans

scoreboard cfg obj

scr\_trans

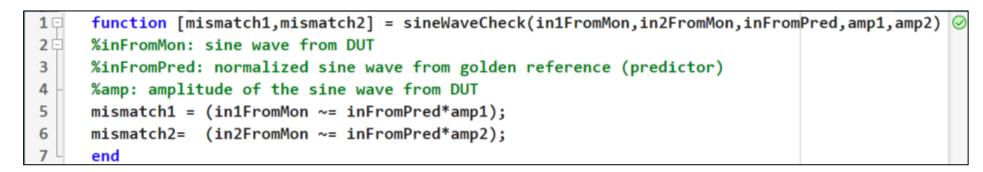

# Example (SWC) – Scoreboard Function

Before generating the component from MATLAB code do the preparation steps necessary for SystemVerilog DPI components.

- Write a scoreboard function that compares

- output of the DUT with

- output of a golden reference

- Inputs are from Monitor and Predictor. Configurations are inputs, too.

# Example (SWC) – Configuration for UVM

#### • Create a **svdpiConfiguration** object and then change:

- Change the kind of the component, and

- Optionally the component name

- Check and optionally change through the Template Dictionary

- Name of component package file

- Name of input/output transition

- Name of configuration object

- Specify which port belongs to which port group

clear svcfg;

svcfg=svdpiConfiguration; svcfg.ComponentKind = 'uvm-scoreboard

| 1 | % * This template requires the following vars and MUST be defined in the svdpiConfiguration.TemplateDictionary</th   |

|---|----------------------------------------------------------------------------------------------------------------------|

| 2 | PortGroups: PREDICTOR_INPUTS, MONITOR_INPUTS, CONFIG_OBJECT_INPUTS                                                   |

| 3 | */>                                                                                                                  |

| 4 | % * This template requires the following vars. They can be overriden in the svdpiConfiguration.TemplateDictionary */ |

| 5 | % <begin_local_dictionary></begin_local_dictionary>                                                                  |

| 6 | ComponentPackageTypeName=% <componenttypename>_pkg</componenttypename>                                               |

| 7 | InputTransTypeName=scoreboard_input_trans                                                                            |

| 8 | OutputTransTypeName=scoreboard_output_trans                                                                          |

| 9 | ConfigObjectTypeName=scoreboard_cfgobj                                                                               |

| 0 | % <end_local_dictionary></end_local_dictionary>                                                                      |

svcfg.TemplateDictionary = {'InputTransTypeName','sineWaveTrans'};

| <pre>addPortGroup(svcfg,'MONITOR_INPUTS',{'in1FromMon','in2FromMon'});</pre> |

|------------------------------------------------------------------------------|

| addPortGroup(svcfg,'PREDICTOR_INPUTS',{'inFromPred'});                       |

| addPortGroup(svcfg,'CONFIG_OBJECT_INPUTS',{'amp1','amp2'});                  |

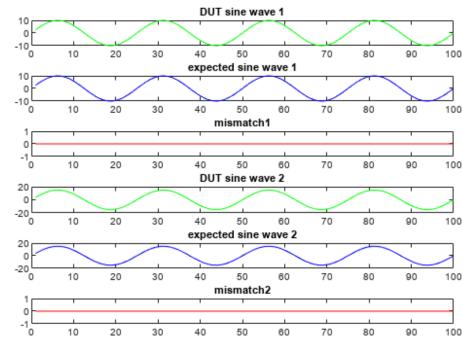

### Example (SWC) – Generate and Verify

Use the **dpigen** function to generate the component artefacts.

Test the UVM component using the generated SystemVerilog testbench and tcl-file.

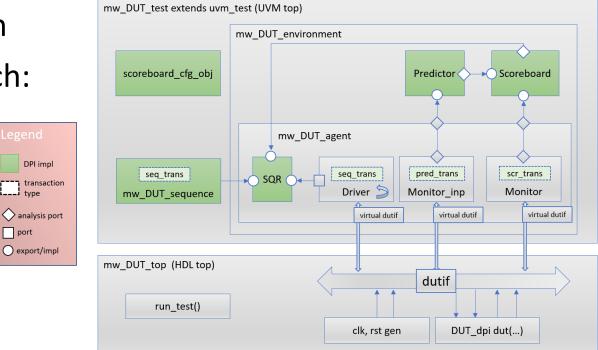

### FPGA/ASIC/SoC Workflow Adoption

\* Cosim with EDA simulators (Siemens, Cadence) or FPGA-in-the-Loop (FIL)

Code Generation Adoption

#### Questions