# How to Avoid the Pitfalls of Mixing Formal and Simulation Coverage

Mark Eslinger, Siemens Joseph V Hupcey III, Siemens Nicolae Tusinschi, Siemens

# Sound Familiar?

# "I want to see coverage data from all sources combined into a single report, so we can see our progress at-a-glance."

### Introduction

- The goal: Use multiple verification strategies to ensure the Device Under Test (DUT) behaves as specified

- The challenge: comparing and combining the results from each verification strategy to the verification plan

- The most common request: merging simulation and formal coverage

- The most common problem(s): understanding what formal coverage is, proper merging of formal and simulation coverage data

# **Re-Cap: Simulation Coverage**

- Code coverage

- The % of RTL code that have been executed by test(s)

- "Dead" / "Unreachable" code could imply a bug

- Says nothing about DUT conformance to the specification

- Functional coverage

- Metric of how much design functionality has been exercised

- Spec./functional feature mapped to a "cover point"

- Goal is 100% coverage conformance to specification

# Brief Digression: Formal Results Are Valid for All Inputs & All Time

### **Analogy**

### Finding solutions to $ax^2 + bx + c = 0$

- <u>Constrained-random simulation approach</u>: Randomly plug-in numbers in the hope you eventually satisfy the equation

- Formal approach:  $x=rac{-b\pm\sqrt{b^2-4ac}}{2a}$  for all values of t

It is exhaustive

# Formal Coverage

### Reachability

• A sequence of input signals which can reach the coverage element

### Observability

• All possible state space paths from a selected node to signals in an assertion

### **Structural Cone of Influence (COI)**

• All logic from a specified node back to the primary inputs

### **Mutation**

• Automatically inserted "mutations" in the DUT cause an assertion failure

# Pitfalls of Merging Sim & Formal Coverage

- #1 Caveat: just because something is "covered" doesn't mean it's properly verified

- Simulation coverage only reflects specific forward paths the simulation has traversed from the inputs through the state space, for a specific set of stimuli

- Some types of formal coverage also reflect a "forward traversal" from the inputs, but often the amount of logic "covered" is greater than simulation

- Other types of formal coverage "works backwards" from an output

- Code coverage from simulation represents end-to-end cluster/SOC level testing, while formal is typically run at the block level

## Example 1: Basic Sim. Vs. Formal Code Coverage

| 2 | INPUTS | ( | OUTPUTS | 5 |                                 |

|---|--------|---|---------|---|---------------------------------|

|   | Sel    | А | В       | С |                                 |

|   | 00     | 0 | 0       | 0 | Focusing on output B requiremen |

|   | 01     | 1 | 0       | 0 | B output is a pulse             |

|   | 10     | 0 | 1       | 0 | Property: B => !B               |

|   | 11     | 0 | 0       | 1 |                                 |

### Example 1: Basic Sim. Vs. Formal Code Coverage

### Simulation

12 1

13 1

14 1

16 🗸

18 /

19 1

20 🗸

21 1

23 Xs

24 Xs

25 Xs

26 ✓

27 🗸

28 🗸

29 🗸

31 Xs

32 Xs

33 Xs

34 X

48 🗸

49 🗸

50 1

51 √

52 🗸

53 √

54 1

55 🗸

56

35

36

**Coverage includes**

logic not related to

satisfying the

requirement

SYSTEMS INITIATIVE

15

17

### Formal always @(posedge clk or negedge rstn) X \* \* Eu = a v = a v = a if (!rstn) rsel <= 2'b00; 12 always @(posedge clk or negedge rstn) else rsel <= sel;</pre> 13 if (!rstn) rsel <= 2'b00; × 14 × rsel <= sel;</pre> else always @(rsel) 15 case (rsel) 16 always @(rsel) 2'b00: begin 17 case (rsel) wA <= 1'b1; 18 2'b00: begin × wB <= 1'b1; wA <= 1'b1; 19 x wC <= 1'b1; end wB <= 1'b1; 20 ~ 22 X X 2'b01: begin 21 wC <= 1'b1; end × 2'b01: begin wA <= 1'b1; 22 × wB <= 1'b0; 23 WA <= 1'b1; × wC <= 1'b0; end 24 wB <= 1'b0; 1 wC <= 1'b0; end 2'b10: begin 25 × 2'b10: begin 26 wA <= 1'b0; × 27 WA <= 1'b0; wB <= 1'b1; × 28 wB <= 1'b1; wC <= 1'b0; end ~ 29 wC <= 1'b0; end 2'b11: begin × 30 XB X 30 2'b11: begin X WA <= 1'b0; 31 X wA <= 1'b0; wB <= 1'b0; 32 wB <= 1'b0; ~ wC <= 1'b1; end 33 × wC <= 1'b1; end default: begin wA <= 1'b0; wB <= 1'b0; wC <= 1'b0; end 34 XI default: begin wA <= 1'b0; wB <= 1'b0; wC <= 1'b0; end endcase 35 endcase **Coverage only** 36 always @(posedge clk or negedge rstn) 37 always @(posedge clk or negedge rstn) **if** (!rstn) pA <= 1'b0; if (!rstn) pA <= 1'b0; 38 × includes logic if (pA) pA <= 1'b0; else pA <= wA; else if (pA) pA <= 1'b0; else pA <= wA; 39 X else always @(posedge clk or negedge rstn) always @(posedge clk or negedge rstn) 40 if (!rstn) pB <= 1'b0; 41 if (!rstn) pB <= 1'b0; 4 related to else if (pB) pB <= 1'b0; else pB <= wB; if (pB) pB <= 1'b0; else pB <= wB; 42 ~ else always @(posedge clk or negedge rstn) 43 always @(posedge clk or negedge rstn) if (!rstn) pC <= 1'b0; satisfying the 44 × if (!rstn) pC <= 1'b0; else if (pC) pC <= 1'b0; else pC <= wC; if (pC) pC <= 1'b0; else pC <= wC; 45 else × 46 requirement always @\* 47 always @\* if (rsel == 2'b00) begin if (rsel == 2'b00) begin 48 × A <= 1'b0; 49 A <= 1'b0 × B <= 1'b0; B <= 1'b0; 50 ~ C <= 1'b0; 51 C <= 1'b0; × nd else begin end else begin 52 × $A \leq pA;$ 53 × $A \leq DA$ : B <= pB; 54 B <= pB; ~ 2022 C <= pC; 55 × $C \leq pC;$ DVCON end 56 end

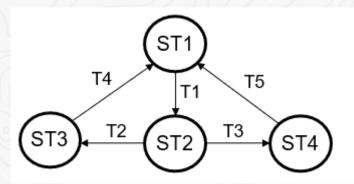

### Example 2: Sim. Vs. Formal FSM Code Coverage

T1: start = 1 T2: sel = 01 T3: sel = 10 T4: done = 1 T5: done = 1 Note: Same state transitions not shown

The following property was run in simulation and formal against a Verilog model of this state machine:

```

a_mout_mutex: assert property (@(posedge clk) $onehot0(mout) );

```

Simulation was run with one value of the select signal used which exercised the output

The property passed in simulation and was proven in formal

### Example 2: Sim. Vs. Formal FSM Code Coverage

| - |     |     |     |

|---|-----|-----|-----|

|   | min | Int | nn  |

| 3 | imu | au  | IUH |

|   |     |     | / - |

always @(posedge clk or negedge rstn) if (!rstn) cnt <= 3'b000; else  $cnt \leq cnt + 1;$

assign done = (cnt == 3'b111) ? 1'b1 : 1'b0;

always @(posedge clk or negedge rstn)

**Simulation run** with sel = 1, uses 3 states of the FSM and more

SYSTEMS INITIATIVE

| if (!rst | tn) cstate <= ST1;           |        |    |     |

|----------|------------------------------|--------|----|-----|

| else     | cstate <= nstate;            |        |    |     |

|          |                              |        |    |     |

| always ( | ¢*                           |        |    |     |

| case(cst | tate)                        |        |    |     |

| ST1: if  | (start)                      | nstate | <= | ST2 |

|          | else                         | nstate | <= | ST1 |

| ST2: if  | (sel == 2'b01)               | nstate | <= | ST3 |

|          | else if (sel == 2'b10)       | nstate | <= | ST4 |

|          | else                         | nstate | <= | ST2 |

| ST3: if  | (done)                       | nstate | <= | ST1 |

|          | else                         | nstate | <= | ST3 |

| ST4: if  | (done)                       | nstate | <= | ST1 |

|          | else                         | nstate | <= | ST4 |

| default  |                              | nstate | <= | ST1 |

| endcase  |                              |        |    |     |

|          |                              |        |    |     |

| always ( | g*                           |        |    |     |

| if (csta | ate == ST3)                  |        |    |     |

| 1        | mout <= 2'b01;               |        |    |     |

| else if  | (cstate == ST4)              |        |    |     |

|          | <pre>mout &lt;= 2'b10;</pre> |        |    |     |

| else     |                              |        |    |     |

|          | mout <= 2'b00;               |        |    |     |

|          |                              |        |    |     |

### Formal always @(posedge clk or negedge rstn) if (!rstn) cnt <= 3'b000; PISP cnt <= cnt + 1; assign done = (cnt == 3'b111) ? 1'b1 : 1'b0; always @(posedge clk or negedge rstn) if (!rstn) cstate <= ST1;</pre> 1 else cstate <= nstate; always @\* case(cstate) nstate <= ST2; ST1: if (start) 2 else nstate <= ST1; 1 ST2: if (sel == 2'b01) nstate <= ST3; 4 else if (sel == nstate <= ST4;</pre> b10) 8 else nstate <= ST2;</pre> 2 ST3: if (done) nstate <= ST1; 1 4 else nstate <= ST3; 4 if (done) nstate <= ST1; ST4: 1 else nstate <= ST4; 8 default: nstate <= ST1;</pre> 1 endcase always @\* if (cstate == ST3) 4 mout <= 2'b01; else if (cstate == ST4)

8

mout <= 2'b10;

mout <= 2'b00;

else

**Formal only** needs the final logic for the full proof, no FSM needed

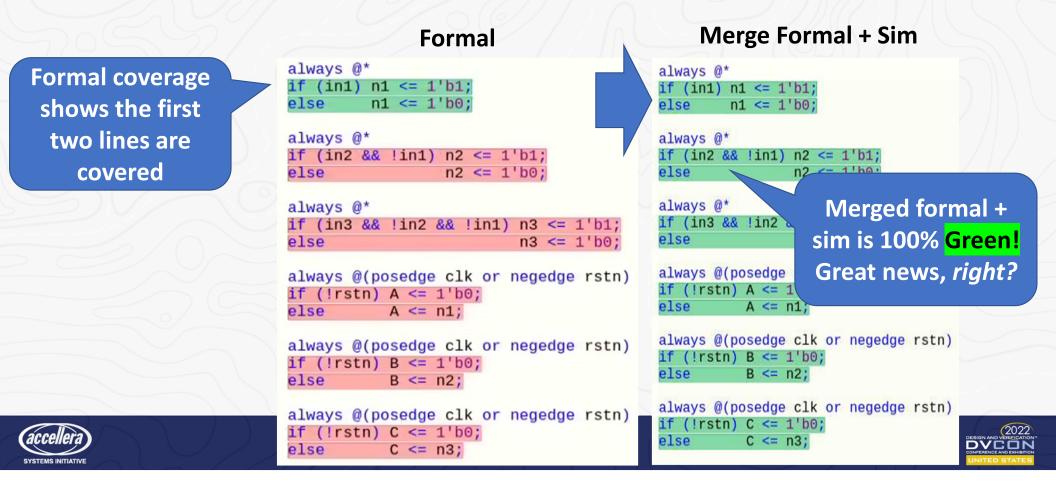

### Example 3: Closing Code Coverage Holes

Simulation

always @\* Specification: if (in1) n1 <= 1'b1;</pre> p1 <= 1'b0; else Outputs are mutex-based on an encoding of the 3 inputs alw (in2 && !in1) n2 <= 1'b1; else n2 <= 1'b0; **Good news:** always @\* if (in3 && !in2 && !in1) n3 <= 1'b1; Only one coverage else n3 <= 1'b0; hole remains after always @(posedge clk or negedge rstn) simulation if (!rstn) A <= 1'b0; A <= n1; else always @(posedge clk or negedge rstn) if (!rstn) B <= 1'b0; B <= n2; else always @(posedge clk or negedge rstn) if (!rstn) C <= 1'b0; C <= n3; else

### Example 3: Let's Quickly Close This ...

a\_bogus: assert property (@(posedge clk) in1 |-> n1 );

## Example 3: Not so fast ... Look at the Property

- a\_bogus: assert property (@(posedge clk) in1 |-> n1 );

- This property is actually useless it tests nothing

- It is not tied to a testplan, or to the verification of any design requirements

### A better approach:

The design requires the 3 outputs to be mutex, thus a more useful property which checks this requirement is:

a\_good: assert property (@(posedge clk) \$onehot0({A,B,C}) );

### Example 3: NOW the Requirement Is Proven

a\_good: assert property (@(posedge clk) \$onehot0({A,B,C}) );

Formal

This formal coverage result reflects requirements and can be merged with sim

| always @' | k  |    |       |

|-----------|----|----|-------|

| if (in1)  | n1 | <= | 1'b1; |

| else      | n1 | <= | 1'b0; |

always @\* if (in2 && !in1) n2 <= 1'b1; else n2 <= 1'b0;

always @\* if (in3 && !in2 && !in1) n3 <= 1'b1; else n3 <= 1'b0;

always @(posedge clk or negedge rstn) if (!rstn) A <= 1'b0; else A <= n1;

always @(posedge clk or negedge rstn)

if (!rstn) B <= 1'b0;

else B <= n2;</pre>

always @(posedge clk or negedge rstn)

if (!rstn) C <= 1'b0;

else C <= n3;</pre>

2022 ESIGN AND VERIFICATION DVCDN ONFERENCE AND EXHIBITION

### Example 4: 100% Coverage – But There is Still a Bug!

### a lwave

**Specification:**

• Outputs are mutex-based -check the 'out1', 'out2' signals

• The FSM to only be in state 2 for no more than 3 cycles

Both sim AND formal are 100% Green! Great news, *right?*

| always @(         | posedge | clk   | or  | negedge | rstn |

|-------------------|---------|-------|-----|---------|------|

| <b>if (!</b> rstn | ) cnt < | = 2'b | 00; |         |      |

| else              | cnt <   | = cnt | +   | 1;      |      |

Simulation

always @(posedge clk or negedge rstn) if (!rstn) cstate <= ST1; else cstate <= nstate;

### always @\*

| case(cst | case(cstate) |        |    |      |  |  |  |

|----------|--------------|--------|----|------|--|--|--|

| ST1: if  | (sel)        | nstate | <= | ST2; |  |  |  |

|          | else         | nstate | <= | ST1; |  |  |  |

| ST2: if  | (&cnt)       | nstate | <= | ST3; |  |  |  |

|          | else         | nstate | <= | ST2; |  |  |  |

| ST3:     |              | nstate | <= | ST1; |  |  |  |

| default: |              | nstate | <= | ST1; |  |  |  |

| endcase  |              |        |    |      |  |  |  |

assign out1 = (cstate == ST3);

| always @(posedge | e clk | or   | neged | je | rstn) |

|------------------|-------|------|-------|----|-------|

| if (!rstn)       |       |      | out2  | <= | 1'b0  |

| else if (out:    |       |      |       |    | 1'b0  |

| else if          | (cnt  | [1]) | out2  | <= | 1'b1  |

| else             |       |      | out2  | <= | out2  |

### Formal

| always (        |          |         |       | negedge | rstn)   |

|-----------------|----------|---------|-------|---------|---------|

| if (!rst        |          |         |       |         |         |

| else            | cnt      | <= cn1  | t + 1 | L;      |         |

|                 |          |         |       |         |         |

| always (        |          |         |       |         | rstn)   |

| if (!rst        | :n) csta | ate <=  |       | 1       |         |

| -1              |          |         | 1     |         |         |

| else            | CST      | ate <=  | nsta  | ate;    |         |

| always (        | *        |         |       |         |         |

| case(cst        |          |         |       |         |         |

| ST1: if         |          | nstate  | a <-  | ST2     |         |

| 1               | (361)    | IIState |       | 2       |         |

| +               | else     | nstate  | -> 4  |         |         |

|                 | 0200     | nocae   |       | 1       |         |

| ST2: if         | (&cnt)   | nstate  | e <=  |         |         |

| 2               |          |         |       | 4       |         |

|                 | else     | nstate  | e <=  | ST2;    |         |

|                 |          |         |       | 2       |         |

| ST3:            |          | nstate  | e <=  | ST1;    |         |

| 4               |          |         |       | 1       |         |

| default:        |          | nstate  | e <=  | ST1;    |         |

|                 |          |         |       | 1       |         |

| endcase         |          |         |       |         |         |

|                 |          |         | _     | OTO L   |         |

| assign <b>c</b> | put1 = ( | cstate  | 9 ==  |         |         |

|                 |          |         |       | 4       |         |

| alwaye (        | Inocode  |         | or r  | ogodgo  | retn)   |

| always (        |          | e cik   | 01 1  |         | = 1'b0; |

| else            |          | 2)      |       |         | 1'b0;   |

| 0100            | else if  |         | [1])  | out2 <  |         |

|                 |          |         |       |         |         |

else

# Example 4: Not So Fast ...

All the code is traversed, BUT the functional behavior is incorrect!

Recall the key requirement: "the FSM to only be in state 2 for no more than 3 cycles"

### **Solutions**

A) Have the forethought to manually write and include the following assertion

**B)** Use automated Mutation coverage

# Example 4: Using Mutation Coverage to Reveal Bugs in 100% Covered DUTs

Mutation coverage reveals the missing requirement and related test from the testplan

| Control<br>Coverage                   |     |

|---------------------------------------|-----|

| case (cstate)<br><br>ST1:<br>if (sel) |     |

| active nstate <= \$                   | ST2 |

|                                       |     |

| if (!rst | tn) cnt <= 2'l | 900 <b>;</b>       |                      |

|----------|----------------|--------------------|----------------------|

| else     | cnt <= cnt     | : + 1;             |                      |

| always ( | )(posedge clk  | or negedge rstn)   |                      |

| if (!rst | tn) cstate <=  | ST1;               |                      |

| else     | cstate <=      | nstate;            |                      |

| always ( | <u>)</u> *     |                    |                      |

| case(cst | tate)          |                    |                      |

| ST1: if  | (sel) nstate   | e <= ST2;          |                      |

|          | else nstate    | e <= ST1;          | Detection            |

| ST2: if  | (&cnt) nstate  | e <= ST3;          | Coverage             |

|          | else nstate    | e <= ST2;          |                      |

| ST3:     | nstate         | e <= ST1;          | case (cstate)        |

| default  | : nstate       | • <= ST1;          | unit (Case (Castate) |

| endcase  |                |                    | ST1: if(sel)         |

|          |                |                    | nstate <= ST2;       |

| assign d | out1 = (cstate | e == ST3);         |                      |

| Ŭ        |                |                    | modify               |

| always ( | (posedge clk   | or negedge rstn)   | nstate <=            |

| if (!rst |                | out2 <= 1'b0;      |                      |

| <u> </u> |                | out2 <= 1'b0;      |                      |

|          |                | [1]) out2 <= 1'b1; |                      |

|          | else           | out2 <= out2;      | DESIGN AND           |

### Summary of Formal vs. Sim Coverage Differences

| Formal Code Coverage                        | Simulation Code Coverage                                                 |

|---------------------------------------------|--------------------------------------------------------------------------|

| Property based                              | Vector based                                                             |

| Exact: Only logic used in proof is covered  | Generous: Whatever a vector hits, is covered                             |

| Covered logic only related to proof         | Covered logic may be unrelated to test                                   |

| Only needed statements in a block covered   | All statements in block covered by default                               |

| Calculated from synthesized netlist         | Calculated from RTL (may include testbench)                              |

| Formal uses abstractions – impacts coverage | No abstractions used                                                     |

| Qualify input constraints used in a proof   | Input constraints only impact reachability                               |

| Reachability analysis used for exclusions   | Reachability analysis used for exclusions, done with formal (CoverCheck) |

### Recommendations

- Close code coverage for each verification engine separately

- Focus on improving testbench completeness and robustness in each domain

- In the formal domain run both proof core and mutation coverage to check testbench completeness

- Use test planning to assign which verification engine verifies which parts of the design

- When mixing formal and sim coverage, try to keep it to instance boundaries

- Have peer reviews of coverage to ensure short cuts are not being taken

- Know where your code coverage comes from: Formal vs. Simulation

- Keep code coverage data from each domain separate in the main coverage database

- The reporting must also make it clear where the coverage data came from

- Avoid adding targeted tests/properties to trivially get to 100% coverage

- Coverage holes point to an incomplete testplan, and ultimately an incomplete/weak testbench

- When adding properties to close code coverage holes, testplan design requirements is your guide!

### Summary

- It is possible to combine the strengths of simulation and formal to ensure that your DUT behaves as specified

- Understanding how sim and formal coverage metrics work in isolation and how they combine – provides a holistic picture of your verification

- Mutation analysis coverage is a powerful tool to make sure 100% coverage doesn't fool you into missing bugs in your testbench

# Questions?