# Get Ready for UVM-SystemC

#### Martin Barnasconi - NXP Semiconductors

Presented by: Anupam Bakshi - Agnisys

# Outline

- A bit of history...

- Why UVM in SystemC?

- Main concepts of UVM

- Advantages of UVM-SystemC

- Work-in-Progress: Register Abstraction Layer

- Register Model examples

- Standardization in Accellera

- Next steps

- Summary and outlook

- UVM-SystemC tutorial at DVCon Europe

# A bit of history...

In the pre-UVM era, various EDA vendors offered a verification methodology in SystemC

OVM-SC (Cadence), AVM-SC (Mentor), VMM-SC (Synopsys)

- Unfortunately, consolidation towards UVM focused on a SystemVerilog standardization and implementation only

- Non-standard methods and libraries exist to bridge the UVM and SystemC world

- Cadence's UVM Multi Language library: offers a 'minimalistic' UVM-SC

- Mentor's UVM-Connect: Mainly TLM communication and configuration

- In 2011, a European consortium started building a UVM standard compliant version based on SystemC / C++

- Initiators: NXP, Infineon, Fraunhofer, Magillem, Continental, and UPMC

# Why UVM in SystemC?

- Elevate verification **beyond block-level** towards **system-level**

- System verification and Software-driven verification are executed by teams not familiar with SystemVerilog and its simulation environment

- Trend: Tests coded in C or C++. System and SW engineers use an (open source) tool-suite for embedded system design and SW dev.

- Structured ESL verification environment

- The verification environment to develop Virtual Platforms and Virtual Prototypes is currently ad-hoc and not well architected

- Beneficial if the first system-level verification environment is UVM compliant and can be reused later by the IC verification team

- Extendable, fully open source, and future proof

- Based on Accellera's Open Source SystemC simulator

- As SystemC is C++, a rich set of C++ libraries can be integrated easily

# Main concepts of UVM (1)

- Clear separation of test stimuli (sequences) and test bench

- Sequences are treated as 'transient objects' and thus independent from the test bench construction and composition

- In this way, sequences can be developed and reused independently

- Introducing test bench abstraction levels

- Communication between test bench components based on transaction level modeling (TLM)

- Register abstraction layer (RAL) using register model, adapters, and predictors

- **Reusable verification components** based on standardized interfaces and responsibilities

- Universal Verification Components (UVCs) offer sequencer, driver and monitor functionality with clearly defined (TLM) interfaces

# Main concepts of UVM (2)

- Non-intrusive test bench **configuration** and **customization**

- Hierarchy independent configuration and resource database to store and retrieve properties everywhere in the environment

- Factory design pattern introduced to easily replace UVM components or objects for specific tests

- User-defined callbacks to extend or customize UVC functionality

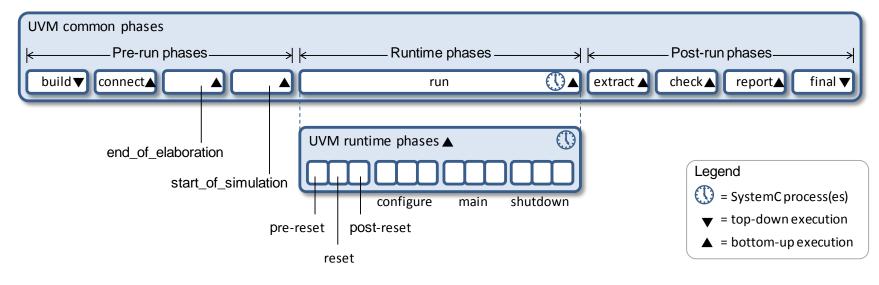

- Well defined **execution** and **synchronization** process

- Simulation based on phasing concept: build, connect, run, extract, check and report. UVM offers additional refined run-time phases

- Objection and event mechanism to manage phase transitions

- Independent result checking

- Coverage collection, signal monitoring and independent result checking in scoreboard are running autonomously

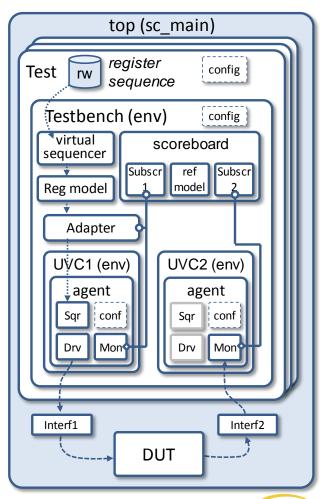

# **UVM Layered Architecture**

- The top-level (e.g. sc\_main) contains the test(s), the DUT and its interfaces

- The DUT interfaces are stored in a configuration database, so it can be used by the UVCs to connect to the DUT

- The test bench contains the UVCs, register model, adapter, scoreboard and (virtual) sequencer to execute the stimuli and check the result

- The test to be executed is either defined by the test class instantiation or by the member function run\_test

2015

DESIGN AND VERIE

# Advantages of UVM-SystemC

- UVM-SystemC library features

- UVM components are SystemC modules

- TLM communication API based on SystemC

- Phases of elaboration and simulation aligned with SystemC

- Packing / Unpacking using stream operators

- Template classes to assign RES/RSP types

- Standard C++ container classes for data storage and retrieval

- Other C++ benefits (exception handling, constness, multiple inheritance, etc.)

### UVM components are SystemC modules

- The UVM component class (uvm\_component) is derived from the SystemC module class (sc\_module)

- It inherits the execution semantics and all features from SystemC

- Parent-child relations automatically managed by uvm\_component\_name (alias of sc\_module\_name); no need to pass ugly *this*-pointers

- Enables creation of spawned SystemC processes and introduce concurrency (SC\_FORK, SC\_JOIN); beneficial to launch runtime phases

- No need for SV-like "virtual" interfaces; regular SystemC channels (derived from sc\_signal) between UVC and DUT can be applied

```

namespace uvm { LRM definition

class uvm_component : public sc_core::sc_module,

public uvm_report_object

{ ... };

} // namespace uvm

class my_uvc : public uvm_env Application

{

public:

my_uvc(uvm_component_name name): uvm_env(name)

{}

...

};

NOTE: UVM-SystemC API under review – subject to change

```

# SystemC TLM communication (1)

- TLM-1 put/get/peek interface

- put/get/peek directly mapped on SystemC methods

- UVM methods get\_next\_item and try\_next\_item mapped on SystemC

- TLM-1 primarily used for sequencer-driver communication

- TLM-1 analysis interface

- UVM analysis port, export and imp using SystemC tlm\_analysis\_if

- Used for monitor-subscriber (scoreboard) communication

- UVM method connect mapped on SystemC bind

```

namespace uvm {

LRM definition

template <typename REQ, typename RSP = REQ>

class uvm_sqr_if_base

: public virtual sc_core::sc_interface

{

public:

virtual void get_next_item( REQ& req ) = 0;

virtual bool try_next_item( REQ& req ) = 0;

virtual void item_done( const RSP& item ) = 0;

virtual void item_done() = 0;

virtual void get( REQ& req ) = 0

```

```

namespace uvm {

LRM definition

template <typename T>

class uvm_analysis_port : public tlm::tlm_analysis_port<T>

{

public:

uvm_analysis_port();

uvm_analysis_port( const std::string& name );

virtual const std::string get_type_name();

virtual void connect( tlm::tlm_analysis_if<T>& _if );

...

NOTE: UVM-SystemC API under review – subject to change

```

# SystemC TLM communication (2)

- As the UVM TLM2 definitions are inconsistent with the SystemC TLM-2.0 standard, these are *not implemented* in UVM-SystemC

- Furthermore, UVM only defines *TLM2-like* transport interfaces, and does not support the Direct Memory Interface (DMI) nor debug interface

- Therefore, a user is recommended to directly use the SystemC TLM-2.0 interface classes in UVM-SystemC

- Hopefully, the UVM SystemVerilog Standardization Working Group in IEEE (P1800.2) is willing to resolve this inconsistency and align with SystemC (IEEE Std 1666-2011)

### Phases of elaboration and simulation

- UVM-SystemC phases made consistent with SystemC phases

- UVM-SystemC supports the 9 common phases and the (optional) refined runtime phases

- Objection mechanism supported to manage phase transitions

- Multiple domains can be created to facilitate execution of different concurrent runtime phase schedules

### (Un)packing using stream operators

- Thanks to C++, stream operators (<<, >>) can be overloaded to enable elegant type-specific packing and unpacking

- Similar operator overloading technique also applied for transaction comparison (using equality operator ==)

```

class packet : public uvm sequence item

Application

class packet : public uvm sequence item

Application

{

public:

public:

int a, b;

int a, b;

UVM OBJECT UTILS(packet);

UVM OBJECT UTILS(packet);

packet( uvm_object_name name = "packet" )

packet( uvm_object_name name = "packet" )

: uvm sequence item(name), a(0), b(0) {}

: uvm sequence item(name), a(0), b(0) {}

virtual void do pack( uvm packer& p ) const

virtual void do pack( uvm packer& p ) const

p.pack_field_int(a, 64);

Disadvantage: type-

Elegant packing using

p << a << b; _

p.pack_field_int(b, 64);

specific methods

stream operators

virtual void do unpack( uvm packer& p )

virtual void do_unpack( uvm_packer& p )

p >> a >> b;

a = p.unpack field int(64);

b = p.unpack_field_int(64);

};

NOTE: UVM-SystemC API under review - subject to change

};

DESIGN AND VERIFIC

13

ONFERENCE AND EXHIBITION

```

SYSTEMS INITIATIVE

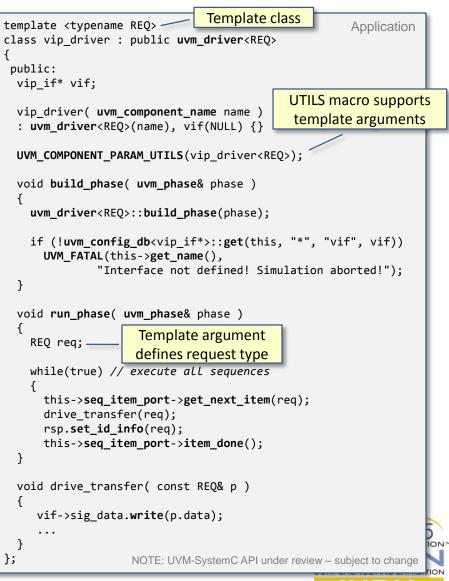

### C++ Template classes

- Template classes enable elegant way to deal with special types such as RES/RSP

- UVM-SystemC supports template classes using macros

UVM\_COMPONENT\_UTILS or UVM\_COMPONENT\_PARAM\_UTILS (no difference)

- More advanced template techniques using explicit specialization or partial specialization are possible

### Standard C++ container classes

- Standard C++ containers can be used for efficient data storage using push/pop mechanisms and retrieval using iterators and operators

- Examples: dynamic arrays (std::vector), queues (std::queue), stacks (std::stack), heaps (std::priority\_queue), linked lists (std::list), trees (std::set), associative arrays (std::map)

- Therefore UVM-SystemC will not define uvm\_queue nor uvm\_pool

SYSTEMS INITIATIVE

### Other benefits

#### • Exception handling:

The standard C++ exception handler mechanism is beneficial to catch serious runtime errors (which are not explicitly managed or found using UVM\_FATAL) and enables a graceful exit of the simulation

#### • Constness:

Ability to specify explicitly that a variable, function argument, method or class/object state cannot be altered

#### • Multiple inheritance:

Ability to derive a new class from two 'origins' or base classes.

• ...and much more C++ features...

### Work-in-Progress: Register Abstraction Layer

| Register Abstraction Layer                                   | Status      |

|--------------------------------------------------------------|-------------|

| Register model containing registers, fields, blocks, etc.    | testing     |

| Register callbacks                                           | testing     |

| Register adapter, predictor, sequences and transaction items | testing     |

| Register front-door access                                   | testing     |

| Build-in register test sequencers                            | development |

| Memory and memory allocation manager                         | development |

| Virtual registers and fields                                 | development |

| Register back-door access (hdl_path)                         | study       |

| Randomization of registers                                   | study       |

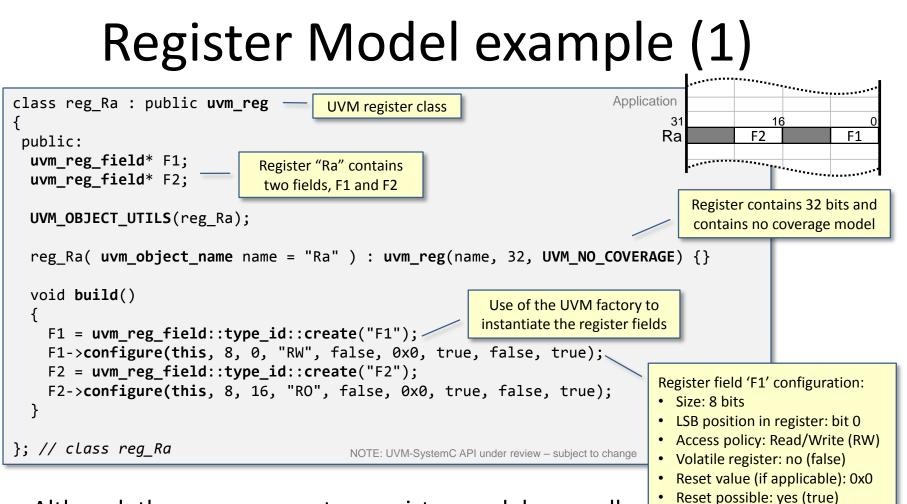

Although the user can create a register model manually, the recommended use model is to generate this register model from an IP-XACT register description

Can be randomized: no (false) Is individually accessible: yes

(true)

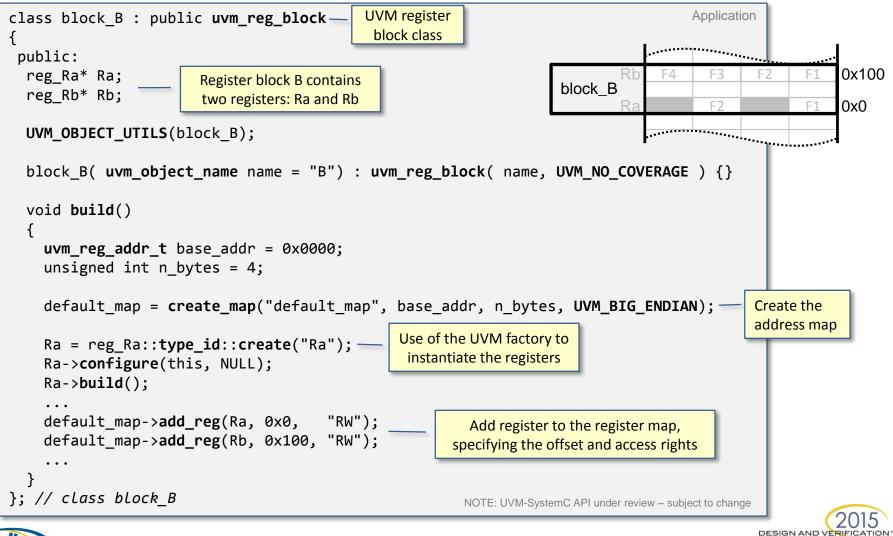

# Register Model example (2)

19

ONFERENCE AND EXHIBITION

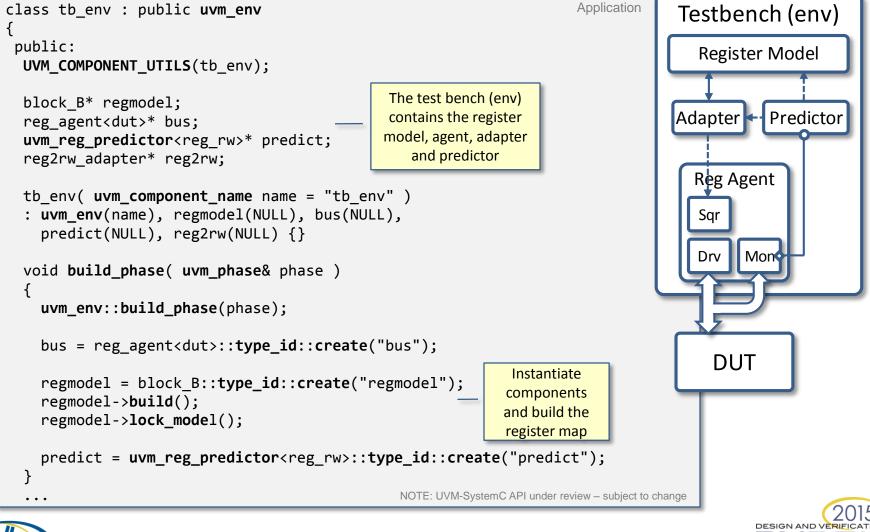

### Test Bench including Register Model (1)

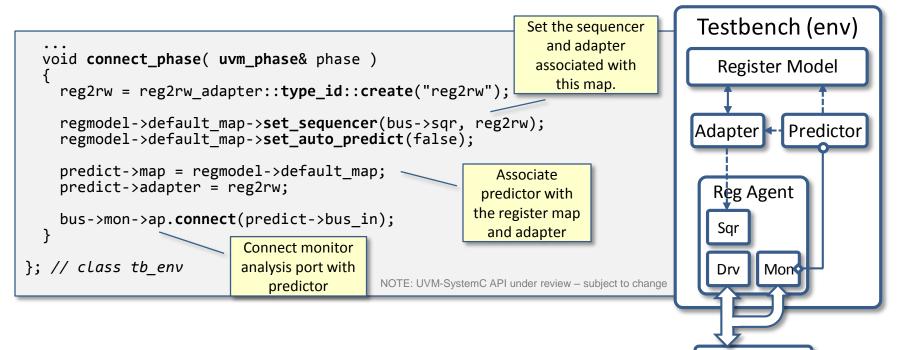

### Test Bench including Register Model (2)

DUT

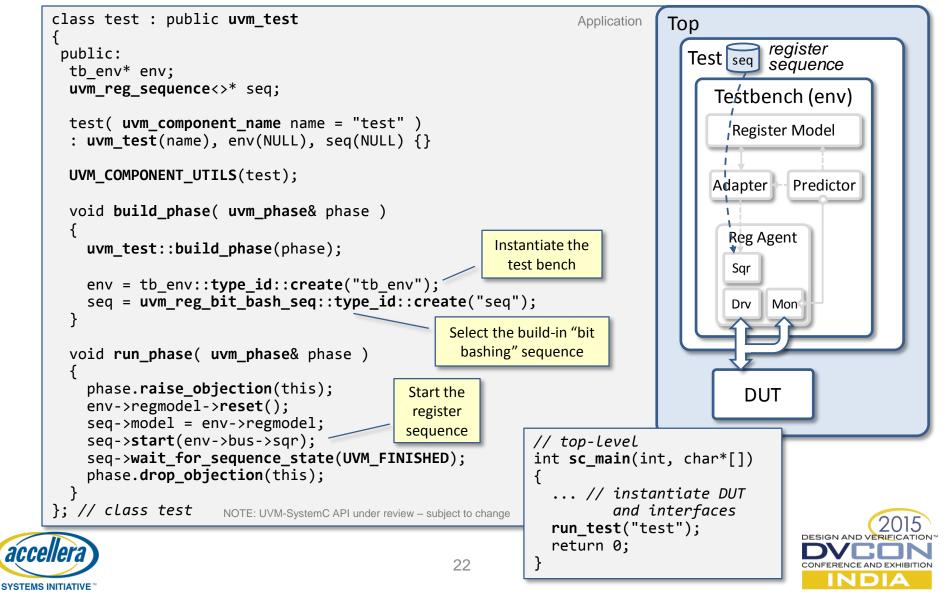

### Execute Build-in Register Test (1)

### Execute Build-in Register Test (2)

Copyright (c) 1996-2014 by all Contributors, ALL RIGHTS RESERVED Universal Verification Methodology in SystemC (UVM-SystemC) Version: 1.0-alpha1 Build: 510 Date: 2015-09-01 Copyright (c) 2006 - 2015 by all Contributors See NOTICE file for all Contributors ALL RIGHTS RESERVED http://www.verdi-fp7.eu/ Licensed under the Apache License, Version 2.0 UVM\_INFO @ 0 s: reporter [RNTST] Running test 'test'... UVM INFO @ 0 s: reporter [STARTING SEQ] UVM INFO @ 0 s: reporter [uvm reg bit bash seq] Verifying bits in register regmodel.Ra in map 'regmodel.default map'... UVM INFO @ 0 s: reporter [uvm reg bit bash seq] ... Bashing RW bit #0 UVM INFO @ 0 s: reporter [uvm reg map] Writing 0x000000000000001 at address 0x0 via map 'regmodel.default map'... UVM INFO @ 0 s: reporter [REG PREDICT] Observed WRITE transaction to register regmodel.Ra: value = 0x1 : updated value = 0x1 UVM INFO @ 0 s: reporter [uvm reg map] Wrote 0x000000000000001 at address 0x0 via map 'regmodel.default map': UVM IS OK... UVM INFO @ 0 s: reporter [RegModel] Wrote register via map regmodel.default map: regmodel.Ra = 0x1 UVM INFO @ 0 s: reporter [uvm reg map] Reading address 0x0 via map 'regmodel.default map'... UVM INFO @ 0 s: reporter [REG PREDICT] Observed READ transaction to register regmodel.Ra: value= 0x1 UVM INFO @ 0 s: reporter [uvm reg map] Read 0x00000000000001 at address 0x0 via map 'regmodel.default map': UVM IS OK... UVM INFO @ 0 s: reporter [RegModel] Read register via map regmodel.default map: regmodel.Ra = 0x1 --- UVM Report Summary ---Ouit count : 0 of 10 \*\* Report counts by severity UVM INFO : 836 UVM WARNING : 1 UVM ERROR : 0 UVM FATAL : 0 \*\* Report counts by id [RNTST] 1 [RegModel] 256 [STARTING SEQ] 1 TPRGED] 1 uvm reg bit bash seq] 66 [uvm reg map] 512 UVM INFO @ 0's: reporter [FINISH] UVM-SystemC phasing completed; simulation finished

SystemC 2.3.1-Accellera --- Dec 29 2014 13:55:54

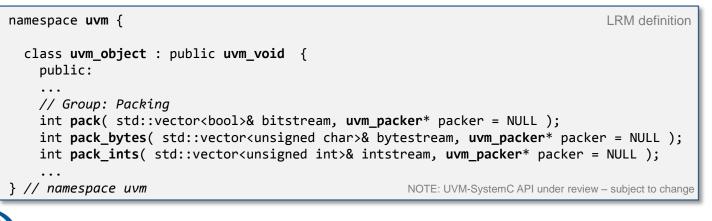

# Standardization in Accellera

- Growing industry interest for UVM in SystemC

- Standardization in SystemC Verification WG ongoing

- Writing and review of UVM-SystemC Language Reference Manual (LRM)

- Improving the UVM-SystemC Proofof-Concept (PoC) implementation

- Creation of a UVM-SystemC regression suite

- Draft release of UVM-SystemC planned for end 2015

- Both LRM and PoC made available under the Apache 2.0 license

- Exact timing dependents on progress (and issues we might find)

|         | UVM-SystemC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | - 1     |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|         | (UVM-SC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | - 1     |

|         | Language Reference Manual                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |

|         | 1.0 DRAFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |

|         | 6.4 uvm_factory                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |

|         | The class uwm_factory implements a factory pattern. A singleton factory instance is created for a given simulation<br>run. Object and component types are registered with the factory using proxies to the actual objects and component<br>being created. The classes uwm_object registry=T> and uwm_component_registry=T> are used to proxy object<br>of type uwm_object and uwm_component respectively. These registry classes both use the uwm_object_wrappen<br>as abstract base class. |         |

|         | 6.4.1 Class definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |

|         | namespace uvm (                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |

|         | class uvs_factory (                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |

| 1 Octob | public:<br>uvm_factory();                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |

|         | <pre>~uvs_factory();</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |

|         | // Group: Registering types                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |

|         | <pre>void do_register' ( uvm_object_vrapper' obj ); // is 'register' in UVM standard</pre>                                                                                                                                                                                                                                                                                                                                                                                                  |         |

|         | // Group: Type & instance overrides                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |

|         | UVM-SystemC (UVM-SC) Language Reference Manual – 1.0 DRAFT                                                                                                                                                                                                                                                                                                                                                                                                                                  | Page 52 |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |

### Next steps

- Main focus this year:

- UVM-SystemC API documented in the Language Reference Manual

- Further mature and test the proof-of-concept implementation

- Extend the regression suite with unit tests and more complex (application) examples

- Next year...

- Finalize upgrade to UVM 1.2 (upgrade to UVM 1.2 already started)

- Add constrained randomization capabilities (e.g. SCV, CRAVE)

- Introduction of assertions and functional coverage features

- Multi-language verification usage (UVM-SystemVerilog  $\leftrightarrow$  UVM-SystemC)

- ...and beyond: IEEE standardization

- Alignment with IEEE P1800.2 (UVM-SystemVerilog) necessary

# Summary and outlook

- Good progress with UVM-SystemC standardization in Accellera

- UVM-SystemC foundation elements are implemented

- Register Abstraction Layer currently under development

- Review of Language Reference Manual and Proof-of-concept implementation ongoing

- First draft release of UVM-SystemC planned for end 2015

- Next steps

- Make UVM-SystemC fully compliant with UVM 1.2

- Introduce new features: e.g. randomization, functional coverage

- How you can contribute

- Join Accellera and participate in this standardization initiative

- Development of unit tests, examples and applications

# UVM-SystemC at DVCon Europe

- DVCon Europe hosts a tutorial on UVM-SystemC:

*"UVM Goes Universal Introducing UVM in SystemC"*

- Contents

- Introduction: Basics and key mechanisms of UVM

- Verification examples: demonstrating the applications of UVM-SystemC

- Standardization perspective: Presents the ongoing development of the proof-of-concept implementation and the language reference manual

- Program and registration: www.dvcon-europe.org

Nov 11-12, 2015 Munich, Germany

### Questions