# 2022 DESIGN AND VERIFICATION<sup>™</sup> DVCDN CONFERENCE AND EXHIBITION UNITED STATES

# Finding Hidden Bugs In Deep Cycles

Advanced Debug Methodologies for Software-first System Validation

Youcef Qassid & Andy Jolley

## Tutorial Overview & Agenda

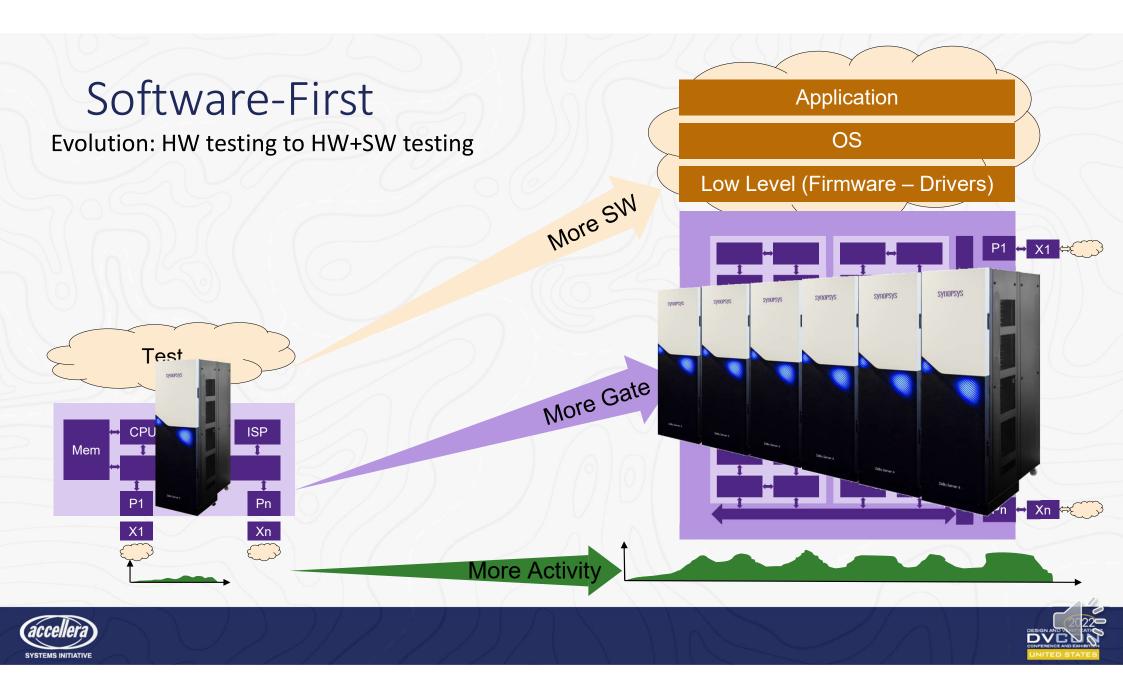

- With the complexity of today's software the length of workloads to validate hardware and software has increased to 100s of billions of cycles.

- As teams adopt a software-first validation strategy, modern emulation and prototyping platforms are needed to enable the highest performance as well highly efficient debug technology.

- In this 2-part tutorial, we will use a multi-processor design case study to illustrate how the latest Emulation and FPGA Prototyping Systems are both ideal platforms to achieve S/W first system validation

- Part 1 : Debug using ZeBu<sup>®</sup> Server emulation system

- Part 2 : Debug using HAPS<sup>®</sup>-100 FPGA prototyping

## System Validation using ZeBu Server emulation system

# Why Software-First

# Debug - High Level View

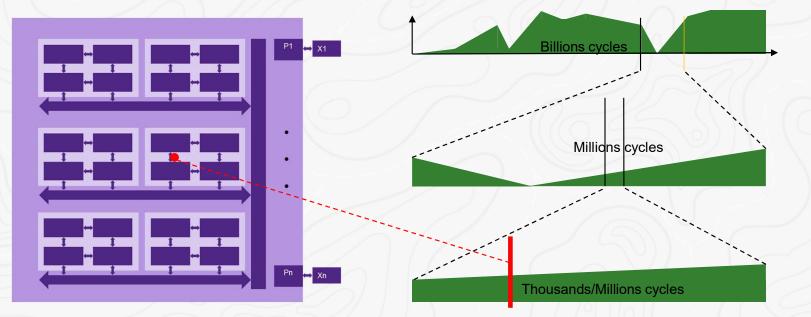

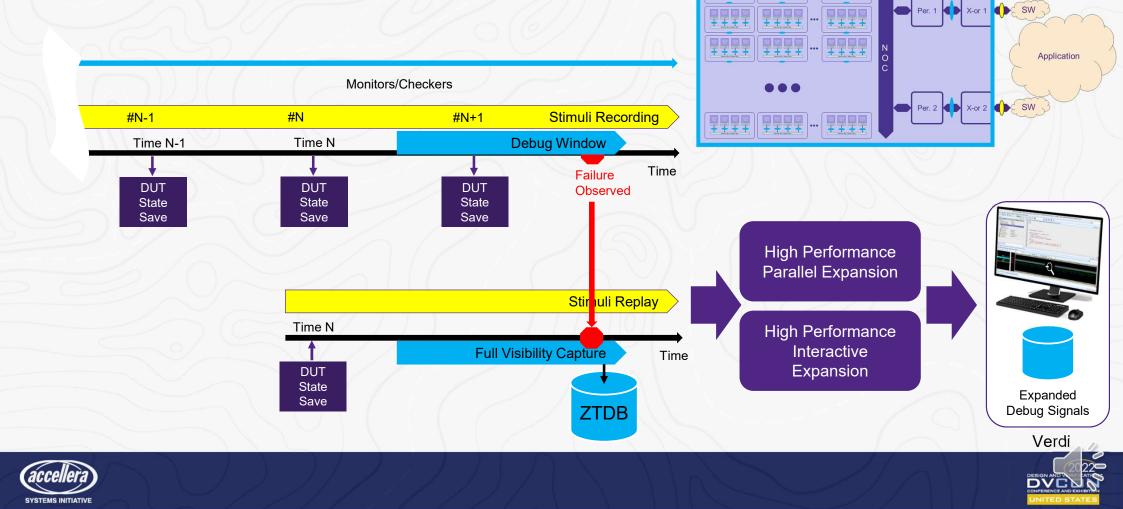

Identify Debug Window

- Monitor and Checker

- Assertions

- Key Signals Waveforms

- Full Visibility Waveforms

General Signals Monitoring – Unlimited Number of Cycles Checkers/Monitor – 1<sup>st</sup> Level RTL Debug

RTL Debug through Waveform

# ZeBu Technologies

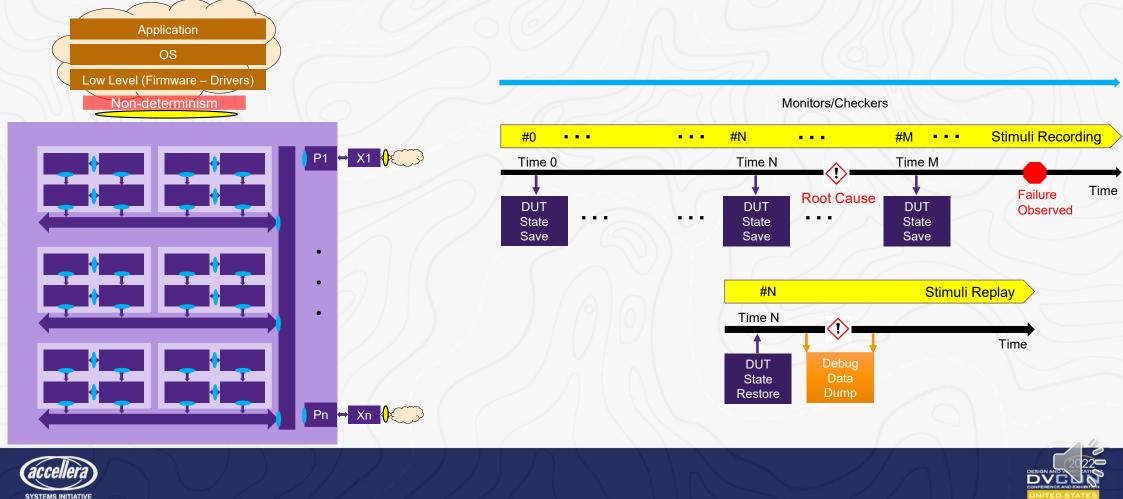

# Monitors/Checkers and Stimuli

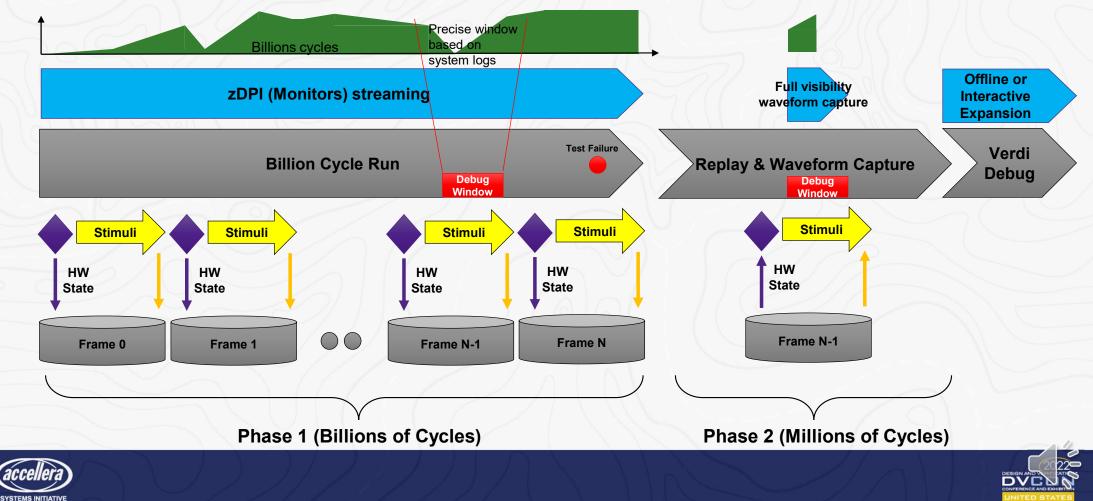

Running Emulation for days/weeks & Isolating Window of Debug

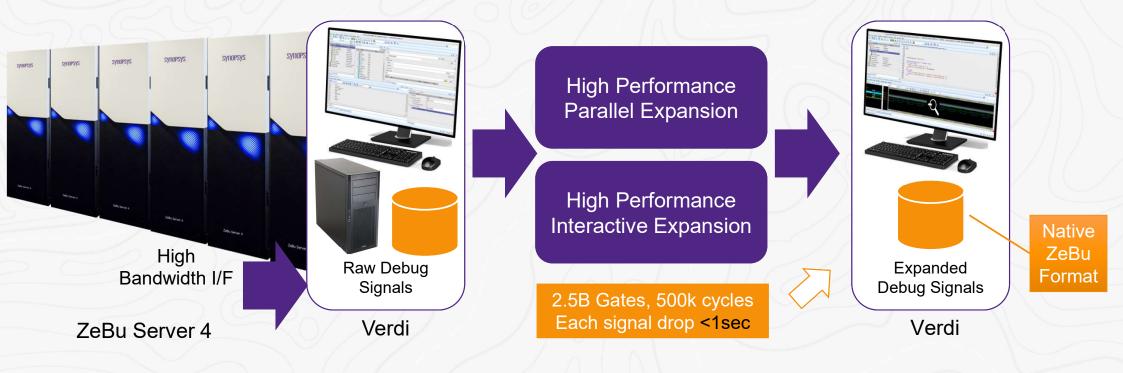

## Faster Waveform Expansion and Debug with ZeBu and Verdi

Next generation tools for waveform-level debug

Scalable solution for complex billion gate SoC waveform-level debug with Verdi

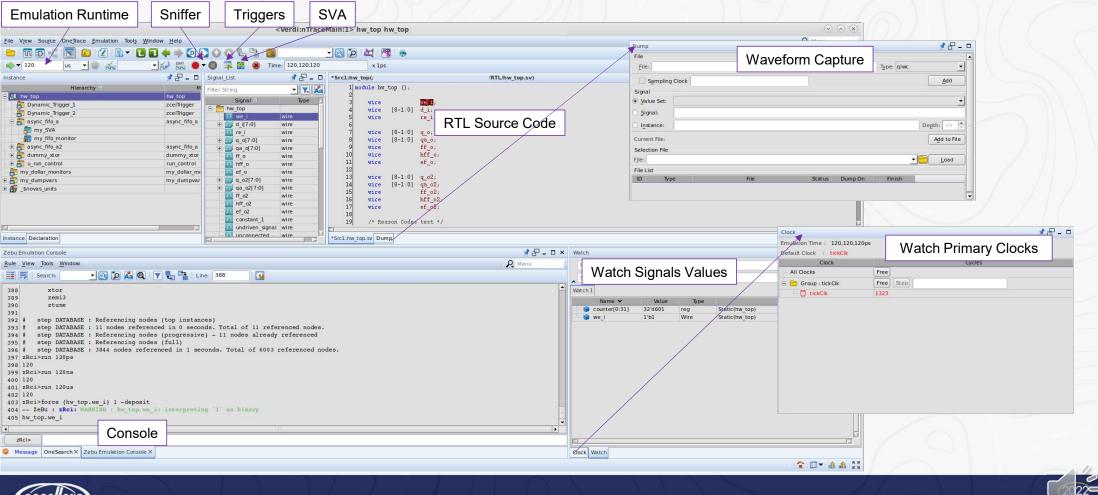

# Emulation Runtime & DUT Debug with Verdi

# ZeBu Case Study

# Multi RISC-V Full SOC

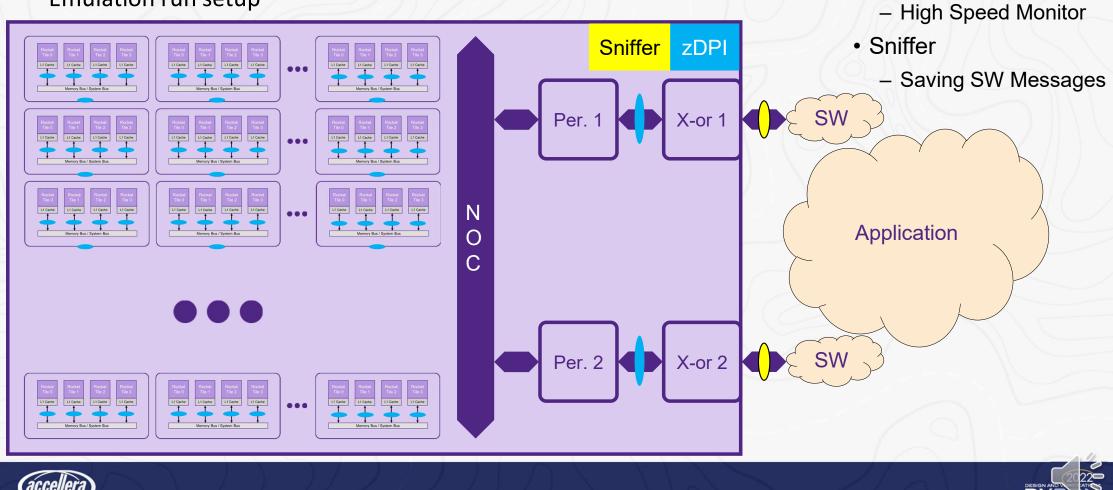

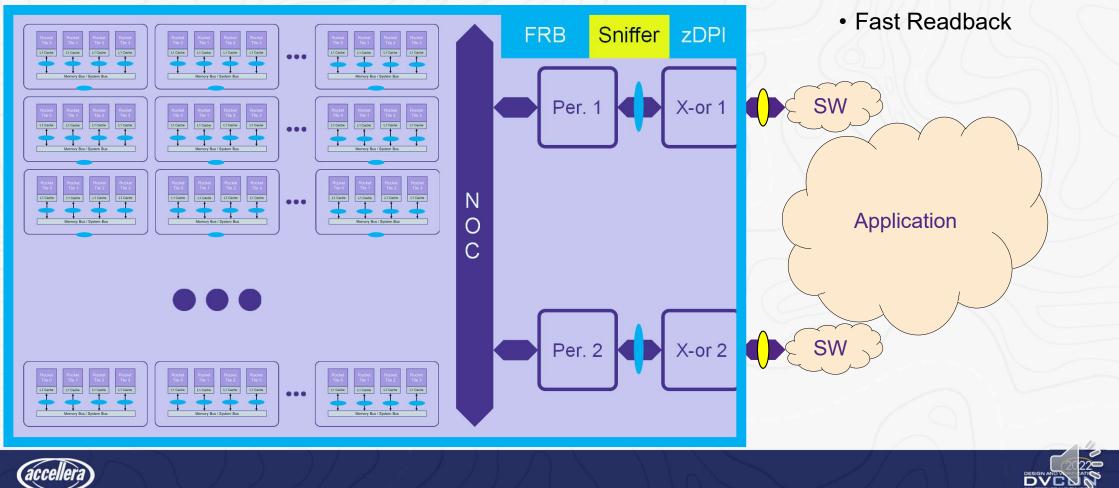

## Emulation run setup

SYSTEMS INITIATIVE

# Multi Risc-V Full SOC

**Full Visibility**

SYSTEMS INITIATIVE

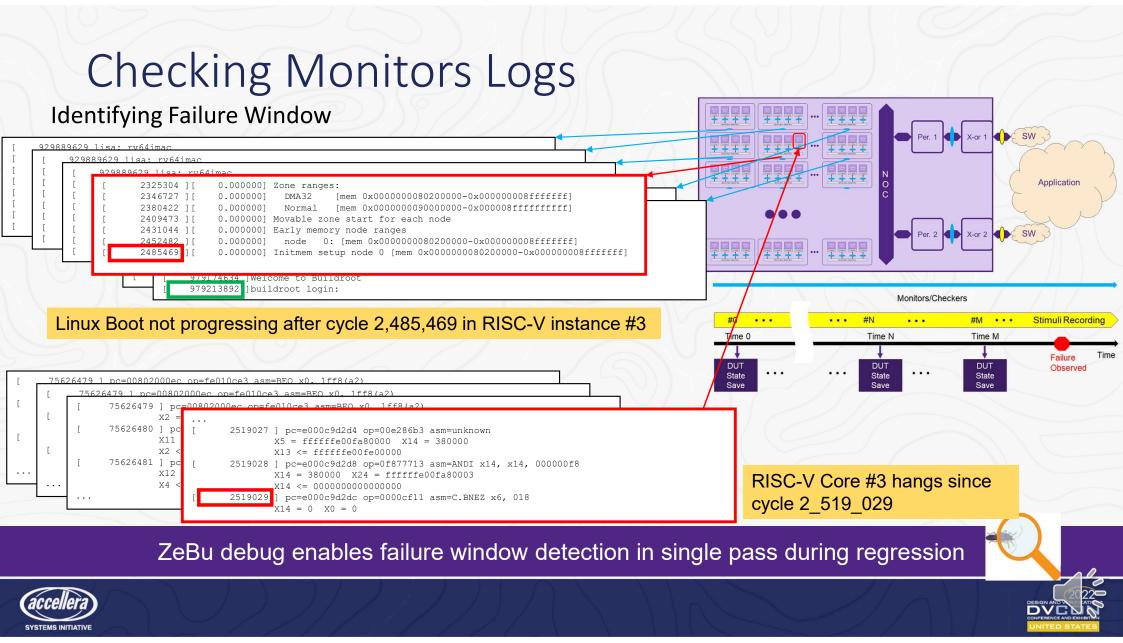

# System-level Debug Using Monitors

Using highly efficient trackers/monitors to identify window for waveform level debug

# Waveform Capture & RTL Debug

· <del>• • • • •</del>

# Debugging Waveforms in Verdi

|                                                                                                               | File View Source One Trace Simulation Emulation Too                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | il <u>s W</u> indow <u>H</u> elp                                                                                                                                                                  |                                                        | R Menu                                    |  |  |

|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-------------------------------------------|--|--|

|                                                                                                               | 🗁 🗊 🗗 📲 📁 🖉 🐘 📲 🗑 🔶 🖓 🖧 🐂 🔛 💆 🖄 🖉 👘                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                   |                                                        |                                           |  |  |

|                                                                                                               | Instance 🦸 🛃 🗕 🖸                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | The state                                                                                                                                                                                         | /SRC/RTL/hw_top.sv)                                    | 018-                                      |  |  |

|                                                                                                               | Hierarchy     Module       Hierarchy     Module       Dynamic_Trigger_1     zceiTrigger       Dynamic_Trigger_2     zceiTrigger       Dynamic_Trigger_3     async_fifo_a       async_fifo_a     async_fifo_a       my fifo monitor     Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 267         else           268         counter_or           269         end           270         wire mix_NC_X           271         wire mix_NC_X           4         272         assign mix_NC |                                                        | it_1;                                     |  |  |

|                                                                                                               | * <nwave:2></nwave:2>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                   |                                                        |                                           |  |  |

| Dumped: Captured in ZTDB                                                                                      | Elle Signal View Waveform Analog Tools Window       Menu         Image: Signal View Waveform Analog Tools Window       Image: Signal View Waveform Analog Tools Window         Image: Signal View Waveform Analog Tools Window       Image: Signal View Waveform Analog Tools Window         Image: Signal View Waveform Analog Tools Window       Image: Signal View Waveform Analog Tools Window         Image: Signal View Waveform Analog Tools Window       Image: Signal View Waveform Analog Tools Window         Image: Signal View Waveform Analog Tools Window       Image: Signal View Waveform Analog Tools Window         Image: Signal View Waveform Analog Tools Window       Image: Signal View Waveform Analog Tools Window         Image: Signal View Waveform Analog Tools Window       Image: Signal View Waveform Analog Tools Window         Image: Signal View Waveform Analog Tools Window       Image: Signal View Waveform Analog Tools Window         Image: Signal View Waveform Analog Tools Window       Image: Signal View Waveform Analog Tools Window         Image: Signal View Waveform Analog Tools Window       Image: Signal View Waveform Analog Tools Window         Image: Signal View Waveform Analog Tools Window       Image: Signal View Waveform Analog Tools Waveform                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                   |                                                        |                                           |  |  |

| Computed: Simulated                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ο                                                                                                                                                                                                 | 12,008 509,000, 12,009,000,000, 12,009,509,000, 12,010 | 0, 009, 000 ,     12, <i>0</i> 10, 509, ( |  |  |

| lixed: Bits having different Reason Codes                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                   | 0                                                      |                                           |  |  |

| constant: Optimized at 1 at compile                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ped) 1                                                                                                                                                                                            |                                                        |                                           |  |  |

| Optimized: Useless Reg. removed at compile                                                                    | - I load_less_signal (Optimiz<br>- IIII load_less_signal (Optimiz<br>- IIIII load_less_signal (Loop) (Loop) - (Loop) - (Loop) - (Loop) - (Optimiz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1 -> x                                                                                                                                                                                            |                                                        |                                           |  |  |

| oop: Simulated – X when oscillating, 0/1 when stable                                                          | Image: Second |                                                                                                                                                                                                   |                                                        |                                           |  |  |

| omputed: Simulated – X coming from oscillating loop                                                           | Image: Second        |                                                                                                                                                                                                   |                                                        |                                           |  |  |

| omputed: Simulated – Gate is useless but still simulated nanks to Graphs (model) defined before optimizations | Message OneSearch × * <nwave:2> full_chip_at_repla</nwave:2>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | y_zwo ×                                                                                                                                                                                           | 12,950,000,000, , ,  13,090,000,000,   ,  13,050       | ),,009,900, , , ,  13)                    |  |  |

|                                                                                                               | Selected:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                   |                                                        | 1 10 - 4 4                                |  |  |

# ZeBu Emulation Scripts

#### my\_dumpvars.v

module my\_dumpvars();

initial begin: Full\_Chip\_VS

(\* qiwc \*) \$dumpvars (0, my\_top\_level)

end

endmodule

my\_vcs\_script.csh

vlogan SRC/RTL/my\_dumpvars.v

vcs my top level my dumpvars

my UTF script.tcl

vcs\_exec\_command my\_vcs\_script.csh architecture\_file -filename .../zse\_configuration.tcl debug -all true debug -offline\_debug\_params {INCL\_XTORS=true} debug -waveform\_reconstruction\_params {SIMZILLA=V2}

#### main\_run.tcl

start\_zebu main\_emulation\_run\_db

sniffer -auto\_create 2000s

ccall -dump\_offline dpi.ztdb

run 1000000000ns

sniffer -stop

ccall -disable

finish

full\_visibility.tcl config db\_path main\_emulation\_run\_db sniffer -restore -at 2000000ns set fid [dump -file full\_chip.ztdb -qiwc] dump -enable -fid \$fid replay 1000000ps dump -close -fid \$fid finish

#### zCui -u my\_UTF\_script.tcl

zRci main\_run.tcl --zebu-work zebu.work

zdpiReport -f list\_of\_dpi\_function -i dpi.ztdb/ -l ./my\_fifo\_monitor.so -z zebu.work |& tee run.log

zRci full visibility.tcl --zebu-work zebu.work

zSimzilla --ztdb full chip.ztdb --zwd full chip zwd

verdi -emulation --zebu-work zebu.work -ssf full chip zwd

# HAPS Technologies

## The Landscape for High Performance FPGA-Based Prototyping

## The Widening Scope

## **Integral Part of IP and SoC verification**

• From early RTL debugging to SoC performance modelling .... and everything in between

## **Primary requirements for FPGA Prototyping**

- High Performance

- Peta cycles for verification coverage

- High Capacity, Scalable and Flexible

- Growing IP and SoC sizes

- Expanded verification tasks

- Visibility Capabilities

- High capacity and at-speed debug

- Highest visibility

- Flexibility to locate the hardest to find bugs

## The Landscape for High Performance FPGA-Based Prototyping

## The Widening Scope

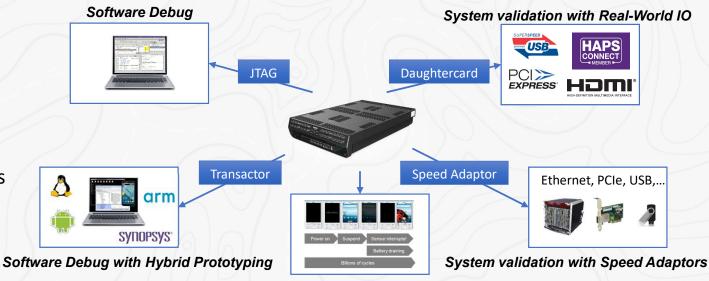

# Prototyping systems offer multiple verification opportunities

- Real-world interfaces for interface validation

- IP level of SoC level

- Links to software debuggers

- Software development

- High-speed transactor-based interfaces

- Hybrid Prototyping

- Speed adaptors for system validation

Software-driven Power Validation

## Highest Capacity and Prototyping Performance with HAPS-100

### Industries Highest Performance and Most Scalable Prototyping System

Scalable to 1B+ gates at 10MHz

### **Built-In Debug for High Performance / Capacity Visibility**

- Dedicated Debug Circuitry and Memory

- Minimal Intrusion to the DUT

#### **High Performance Host Interfaces**

• High-Capacity Data transfer using USB3 and QSFP Interfaces

#### **Designed for Desktop or Data Center Installations**

• Single Form Factor suits all scalable requirements

HAPS-100

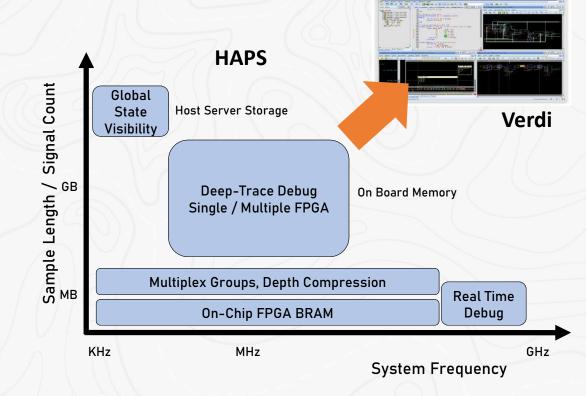

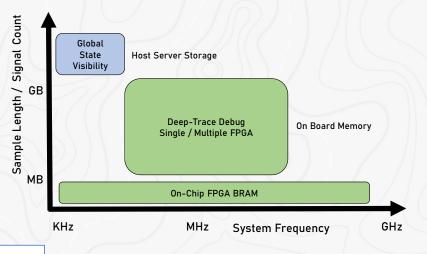

## Debug Capabilities for Deep-Cycle Visibility

## Get to the debug window of interest and provide database for Verdi debug

## Multiple visibility options

- Performance, capacity and intrusion into the DUT

- Real-time, at-speed debugging, full state capture

## Increased visibility capacity and flexibility

- Greater event detection and capture resolution

- Eliminate re-spins to capture the necessary scope

## Different technologies combine to great effect

- First event detection at full speed

- Higher capacity visibility at reduced speeds

- Complete state capture at controlled speeds

# HAPS Case Study

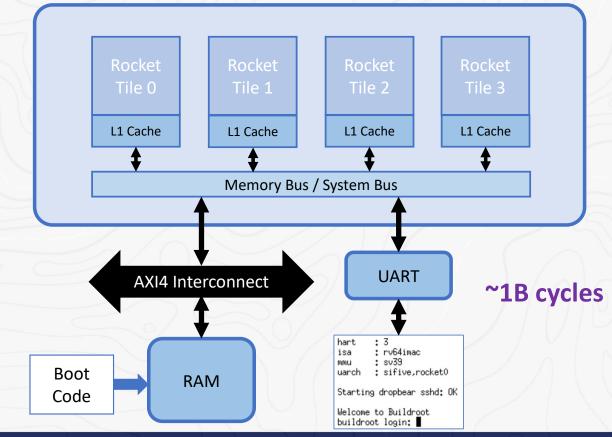

## Case Study : RISC-V Based Processor SoC

### Architecture Overview

### **DUT Architecture**

RISC-V Architecture with 4-Core Processor

#### Software content

• Linux Boot ~ 1 Billon Cycles

### **Prototyping Requirements**

- Single RISC-V In Single Xilinx VU19PFPGA

- RAM to be replaced with external DDR4

- Maximum system performance for 1B cycles

- Stand Alone DUT

- Self stimulating from Boot Code

- Monitor UART : Real World or Transactor Based

- Enable debug to detect and capture activity

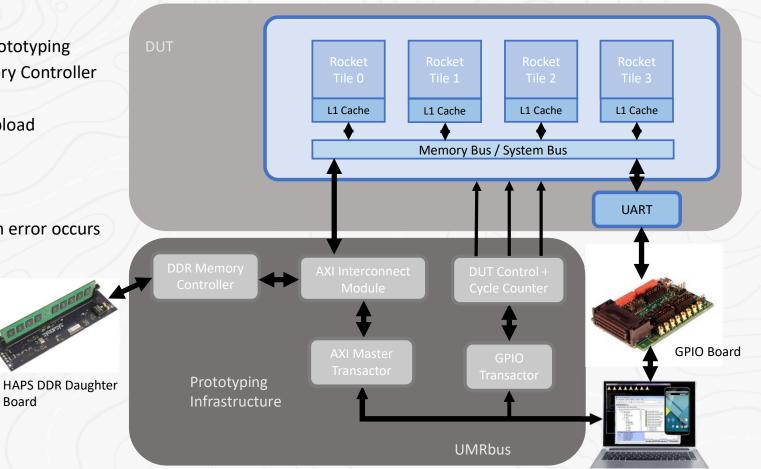

## Prototyping Preparation : Stand-Alone DUT @ 100MHz

### **FPGA Prototyping Infrastructure**

- Addition of modules for standalone prototyping

- AXI Interconnect and DDR Memory Controller

- To replace DUT RAM

- AXI Transactors for Boot Code Upload

- "Backdoor" Load Approach

- GPIO Transactor for DUT Control

- Clocks, Reset and Monitor

- Cycle counter to track when error occurs

- Addition of HAPS Daughter Boards

- DDR for Boot Code Store

- GPIO for UART to Host PC

### DUT Clocked @ 100MHz

## Prototyping Preparation : Debug Enablement

#### Enable multiple Debug Capabilities

- BRAM and DTD based Debug to monitor AXI Transactions

- On-Chip BRAM for AXI Traffic between DUT and DDR3 Memory

- Off-Chip DTD for all AXI Traffic between XTORs, DUT and DDR3 Memory

- Debug capacity available to maximize visibility

#### RTL \$dumpvars used to select debug signals

| \$dumpvars(1, | rocket_system_HAPS100.M1_AWREADY[0]);                 |

|---------------|-------------------------------------------------------|

| \$dumpvars(1, | rocket_system_HAPS100.M1_AWVALID[0]);                 |

| \$dumpvars(1, | rocket_system_HAPS100.M1_AWID[1*AXI_M_ID_WIDTH-1:0]); |

| \$dumpvars(1, | rocket_system_HAPS100.M1_AWADDR[M_AXI_AW-1:0]);       |

| \$dumpvars(1, | rocket system HAPS100.M1 AWLEN[7:0]);                 |

| \$dumpvars(1, | rocket_system_HAPS100.M1_AWSIZE[2:0]);                |

| \$dumpvars(1, | rocket system HAPS100.M1 AWBURST[1:0]);               |

| \$dumpvars(1, | rocket_system_HAPS100.M1_AWLOCK[0]);                  |

| \$dumpvars(1, | rocket system HAPS100.M1 AWCACHE[3:0]);               |

| \$dumpvars(1, | rocket system HAPS100.M1 AWPROT[2:0]);                |

| \$dumpvars(1, | rocket system HAPS100.M1 AWQOS[3:0]);                 |

| \$dumpvars(1, | rocket system HAPS100.M1 AWREADY[0]);                 |

| \$dumpvars(1, | rocket_system_HAPS100.M1_AWVALID[0]);                 |

| \$dumpvars(1, | rocket system HAPS100.M1 WDATA[M AXI DW-1:0]);        |

| \$dumpvars(1, | rocket system HAPS100.M1 WSTRB[M AXI DW/8-1:0]);      |

| \$dumpvars(1, | rocket_system_HAPS100.M1_WLAST[0]);                   |

| \$dumpvars(1, | rocket system HAPS100.M1 BREADY[0]);                  |

| \$dumpvars(1, | rocket system HAPS100.M1 BVALID[0]);                  |

| \$dumpvars(1, | rocket_system HAPS100.M1_BID[1*AXI_M_ID_WIDTH-1:0]);  |

| \$dumpvars(1, | rocket system HAPS100.M1 BRESP[1:0]);                 |

| \$dumpvars(1, | rocket system HAPS100.M1 ARREADY[0]);                 |

| \$dumpvars(1, | rocket system HAPS100.M1 ARVALID[0]);                 |

| \$dumpvars(1, | rocket system HAPS100.M1 ARID[1*AXI M ID WIDTH-1:0]); |

| \$dumpvars(1, | rocket system HAPS100.M1 ARADDR[M AXI AW-1:0]);       |

| \$dumpvars(1, | rocket system HAPS100.M1 ARLEN[7:0]);                 |

| \$dumpvars(1, | rocket system HAPS100.M1 ARSIZE[2:0]);                |

| \$dumpvars(1, | rocket system HAPS100.M1 ARBURST[1:0]);               |

| \$dumpvars(1, | rocket system HAPS100.M1 ARLOCK[0]);                  |

| \$dumpvars(1, | rocket system HAPS100.M1 ARCACHE[3:0]);               |

| \$dumpvars(1, | rocket system HAPS100.M1 ARPROT[2:0]);                |

| \$dumpvars(1, | rocket system HAPS100.M1 ARQOS[3:0]);                 |

| \$dumpvars(1, | rocket system HAPS100.M1 RREADY[0]);                  |

| \$dumpvars(1, | rocket system HAPS100.M1 RVALID[0]);                  |

| \$dumpvars(1, | rocket system HAPS100.M1 RID[1*AXI M ID WIDTH-1:0]);  |

| \$dumpvars(1, | rocket_system_HAPS100.M1_RDATA[M_AXI_DW-1:0]);        |

| \$dumpvars(1, | rocket system HAPS100.M1 RRESP[1:0]);                 |

| \$dumpvars(1, | rocket system HAPS100.M1 RLAST[0]);                   |

|               |                                                       |

#### Define BRAM and DTD configuration

device jtagport umrbus iice new {idx} -type regular iice controller -iice {idx} none iice controller -iice {idx} -triggerstates 4 iice controller -iice {idx} -triggerstates 4 iice controller -iice {idx} -triggerconditions 8 iice sompler -iice {idx} haps100\_DTD\_builtin iice sampler -iice {idx} -depth 5000000 iice sampler -iice {idx} -qpip 3 iice sampler -iice {idx} -pipe 3 iice sampler -iice {idx} -pipe 3

device jtagport umrbus lice new {iice\_bram} -type regular iice controller -iice {iice\_bram} statemachine iice controller -iice {iice\_bram} -triggerstates 4 lice controller -iice {iice\_bram} -cniggerconditions 8 iice controller -iice {iice\_bram} -counterwidth 8 iice sampler -iice {iice\_bram} -depth 512 iice sampler -iice {iice\_bram} -pipe 3 lice sampler -iice {iice\_bram} -always\_armed 1

iice clock -iice {idxA} -edge positive {rocket\_system\_HAPS100.M3\_AXI\_ACLK}

iice clock -iice {iice\_bram} -edge positive {rocket\_system\_HAPS100.M3\_AXI\_ACLK}

# Check Resource Usage and Sample Rates from Implementation Logs

Current instrumentation information: IICE=idxA FPGA=FB1.uA

Total instrumentation in bits: Sample Only 0, Trigger Only 0, Sample and trigger 282 Instrumentation in bits:

Sample Only 0, Sample and trigger 282. All sampled 282 of 8192 signals allowed for DDR4 memory type Maximum sample clock frequency: 160.0000 MHz ITC==ice bram

CE=iice\_bram FPGA=FB1.uA

Total instrumentation in bits: Sample Only 0, Trigger Only 0, Sample and trigger 844 Instrumentation in bits:

- Sample Only  $\theta$ , Sample and trigger 844

- Maximum sample clock frequency is same as maximum user clock frequency (as reported by P&R)

## Prototyping Preparation : Debug Enablement

### Enable multiple Debug Capabilities

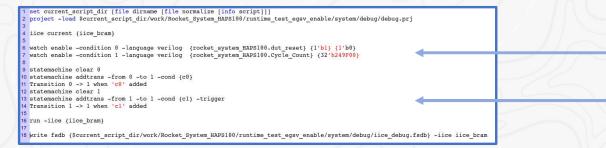

## Prototyping Debug Flow : Initial Error Detect Run

#### **Check for Error Condition on Initial Run**

- Upload the Boot Code to the external DDR device via the Transactors "Back Door" approach

- Rocket System DUT is held in a reset state

- Boot Code Uploaded and re-read to allow for off-line check

Release DUT Reset and check for output from the UART

|        | [18:59:44] [ | 000002123628 | ][ 0.000000] | bootconsole [early0] enabled^M                                  |

|--------|--------------|--------------|--------------|-----------------------------------------------------------------|

|        | [18:59:45] [ | 000002148804 | ][ 0.000000] | Initial ramdisk at: 0x (ptrval) (9929728 bytes)^M               |

|        | [18:59:56] [ | 000002325314 | ][ 0.000000] | Zone ranges:^M                                                  |

| -      | [18:59:56] [ | 000002346737 | ][ 0.000000] | DMA32 [mem 0x000000080200000-0x00000008fffffff]^M               |

| _      | [18:59:56] [ | 000002380432 | ][ 0.000000] | Normal [mem 0x0000000000000000000000000000000000                |

|        | [18:59:57] [ | 000002409483 | ][ 0.000000] | Movable zone start for each node <sup>M</sup>                   |

| -      | [18:59:57] [ | 000002431054 |              | Early memory node ranges <sup>M</sup>                           |

| $\leq$ | [18:59:58] [ | 000002452492 |              | node 0: [mem 0x000000080200000-0x00000008ffffff]^M              |

|        | [18:59:58] [ | 000002485479 | ][ 0.000000] | Initmem setup node 0 [mem 0x000000080200000-0x00000008ffffff]^M |

- See error state occur after cycle 2,485,479 from reset

- 25mS to reach error condition @ 100MHz

UART locked at Cycle 2,485479

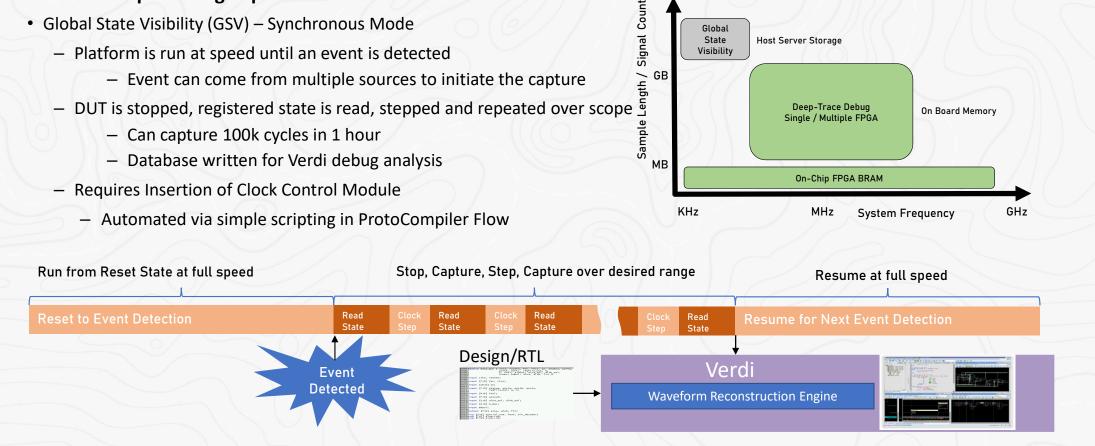

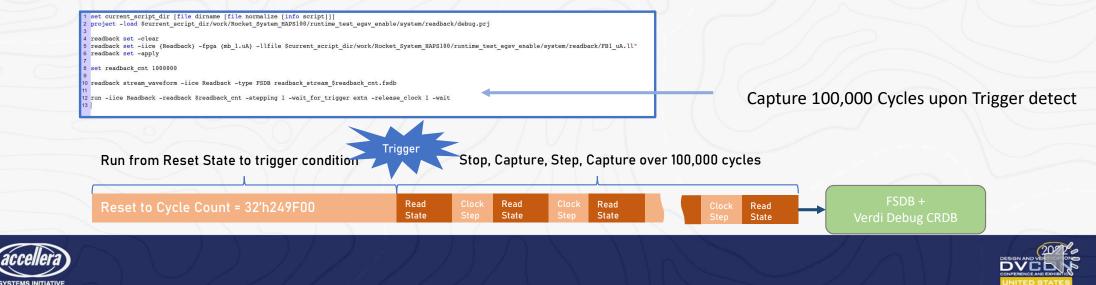

## Prototyping Debug Flow : Debug Database Capture Run

### Configure and Initiate the On-Chip Debug and GSV Capture

• Debug run with on-Chip BRAM Debug trigger at Cycle Count minus 50,000 Cycles

Condition 0 : DUT Reset de-assert Condition 1 : Cycle Count = 2,400,000

State Machine Based Triggering Condition 0 followed by Condition 1

• Global State Visibility armed to capture 100,000 cycles on trigger condition

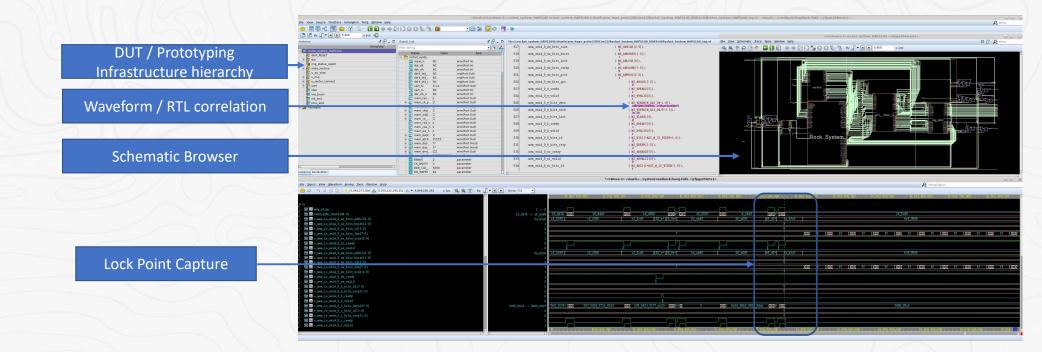

## Off-line Verdi Debug Environment

#### **Complete Debug Environment for Multiple Offline Debug Session**

• Verdi CRDB created using generated scripts

% rocket\_system\_HAPS100\_run\_verdi -crdbgen -rtldbdir \$HAPS\_PRJ\_DIR/work/Rocket\_System\_HAPS100/pcs\_uc/simv.daidir/ -dtop Rocket\_System\_HAPS100

- Complete debug environment exported as fully contained package

- Can be run on any remote network with tool access

- Allows multiple users in all world-wide locations to debug at RTL level with waveform expansion

## Case Study : RISC-V Based Processor Chip

#### **Debugging the Rocket Chip Implementation**

- GSV capture provides full visibility around the error point i.e. Cycle 2,485,479

- Design knowledge is generally required to locate and track the source of the bug

- Deep Cycle Visibility : Real world waveforms with expansion and correlation to RTL throughout DUT hierarchy over 100,000 cycles

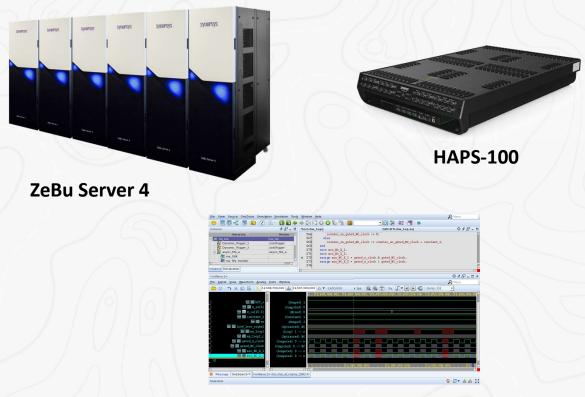

# Summary

## Finding Hidden Bugs In Deep Cycles

## ZeBu Server 4

- Large designs

- DPI/Monitors

- Stimuli Replay

- Fast Readback

## HAPS-100

- Highest Performance

- Deep Tracing

- Global State Visibility

## Verdi

- Industry standard debug

- ZeBu/HAPS outputs natively integrated

Verdi