# Fast and Furious Quick Innovation from Idea to Real Prototype

Simone Fontanesi, Infineon Technologies Austria AG, Villach, Austria Gaetano Formato, Infineon Technologies Austria AG, Villach, Austria Thomas Arndt, COSEDA Technologies GmbH, Dresden, Germany Andrea Monterastelli, Infineon Technologies Austria AG, Villach, Austria

- Motivation

- Methodology

- Results and Conclusions

- Motivation

- Methodology

- Results and Conclusions

## Selling an idea with a prototype

#### A possible approach...

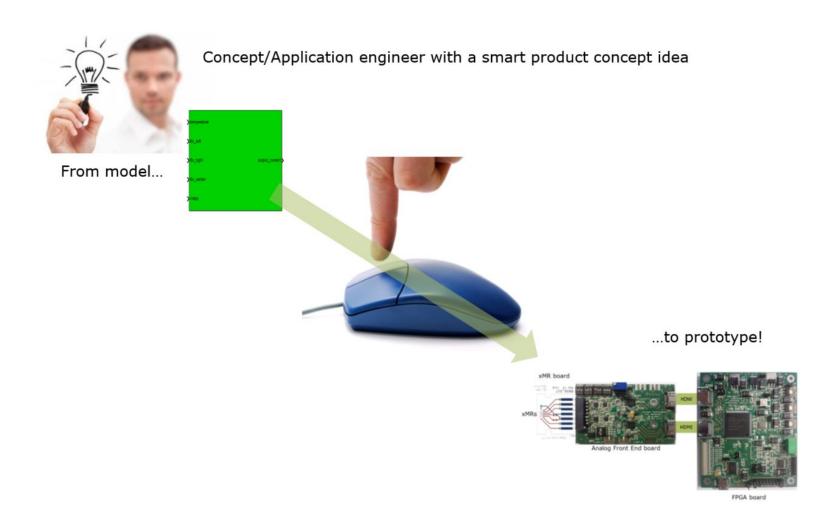

#### ...Our vision!

- Motivation

- Methodology

- Results and Conclusions

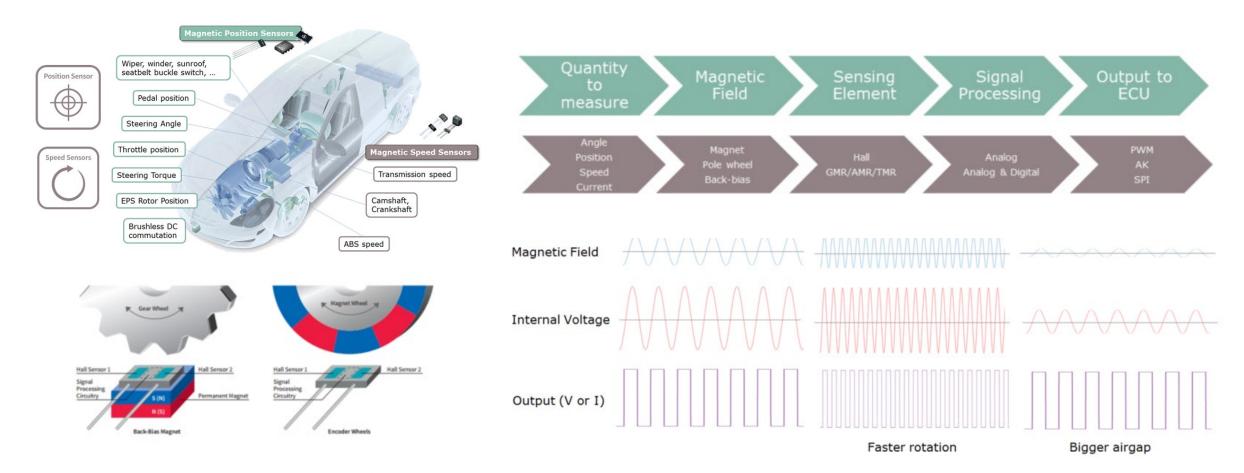

#### Magnetic sensors for automotive applications

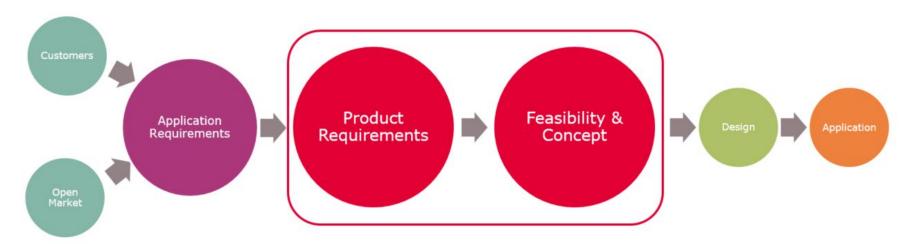

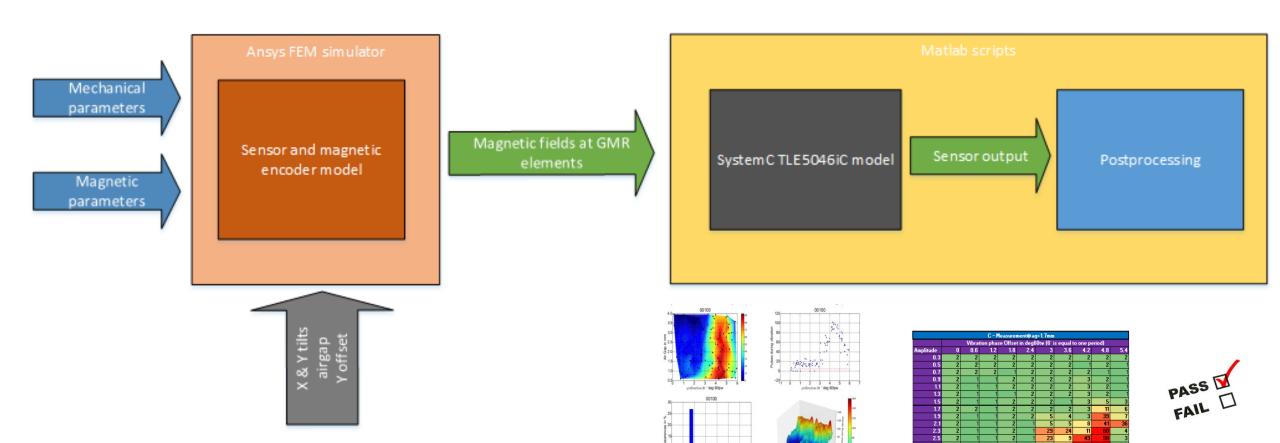

#### Virtual prototyping for concept definition

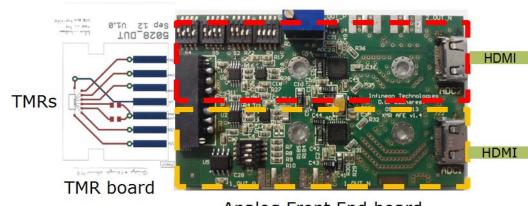

#### From simulation to real HW

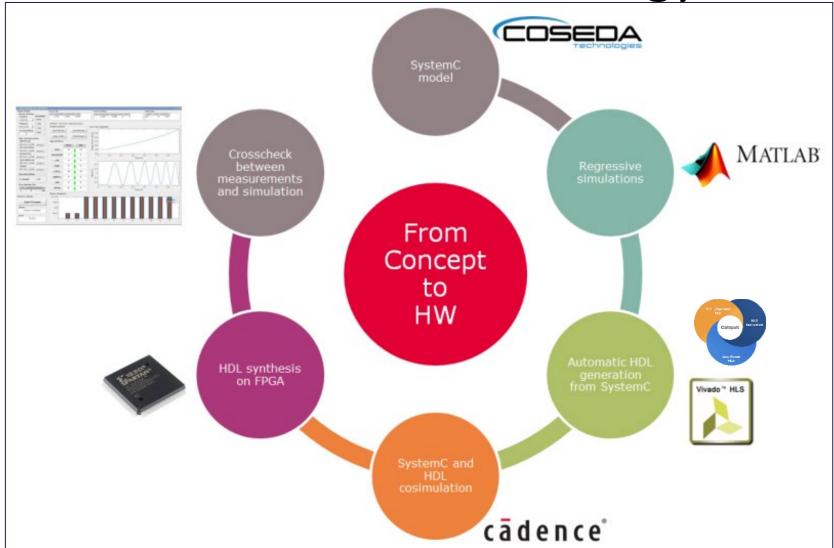

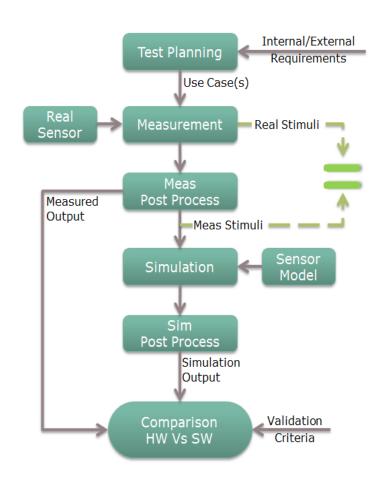

Fast & Furious: the methodology in a nutshell

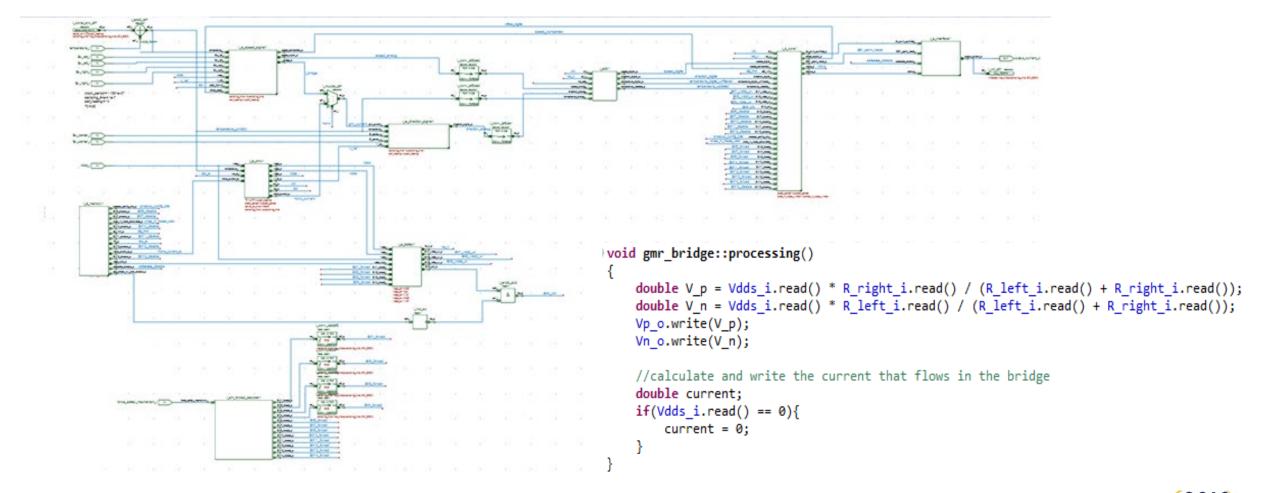

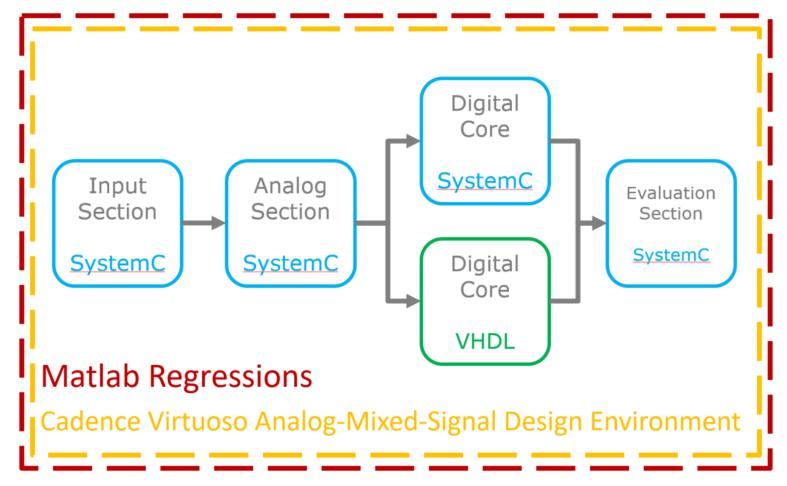

#### SystemC Modeling

- SystemC "clean" netlist from COSIDE®

- Conversion of each SystemC module

- Conversion of top-level

- High level synthesis

- Vivado HLS

- Mentor Catapult

VIDEO SHOWING THE AUTOMATIC CONVERSION PROCESS

I CANNOT PUT IT INTO THE SLIDES

BECAUSE OTHERWISE THE FILE

GETS TOO BIG AND CANNOT

UPLOAD IT. FOR THE CONFERENCE

I WILL BRING THE PPTX ON A USB

STICK

<sup>\*</sup>Note: Mentor Catapult would also allow cosimulation in an integrated environment

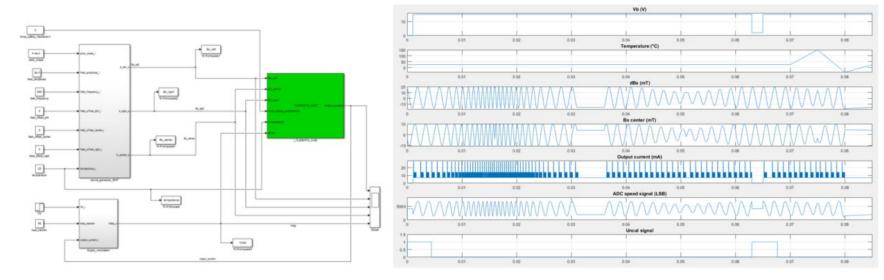

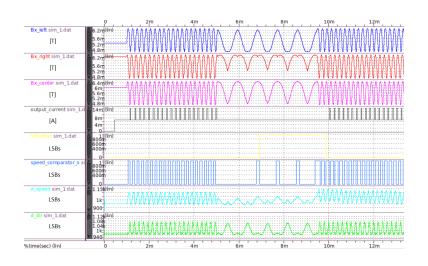

#### **Direction Signal Path**

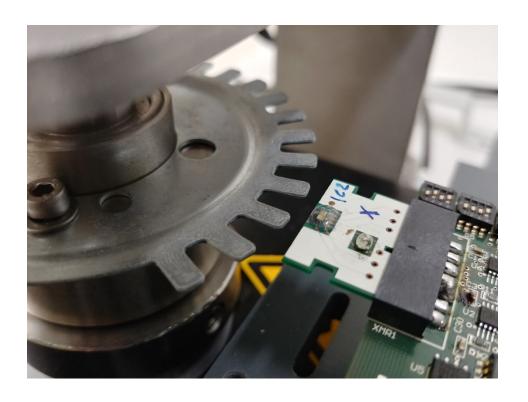

Analog Front End board

Speed Signal Path

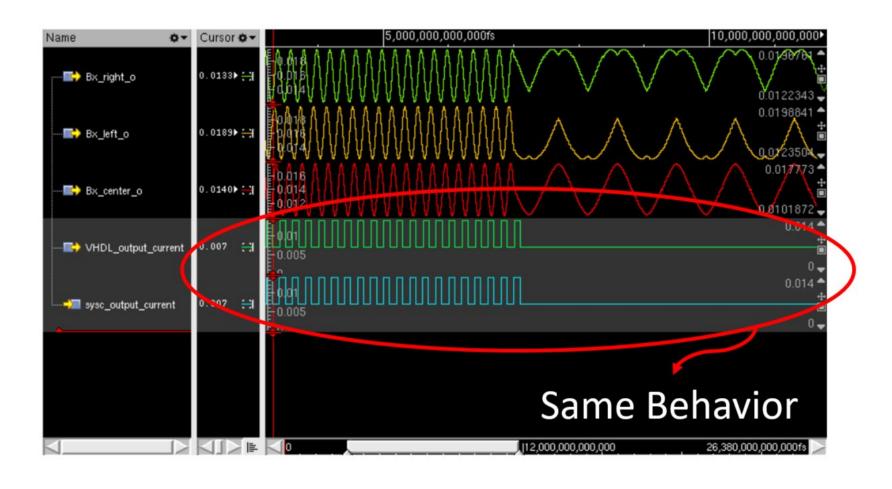

#### Digital core

FPGA board

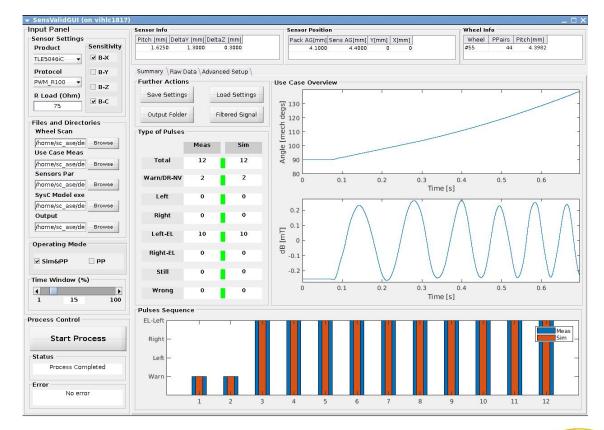

#### Measurement-simulation crosscheck

- Motivation

- Methodology

- Results and Conclusions

#### Results and Conclusion (1/3)

How much effort was spent for the different steps in the flow?

- Modeling: 1 month if concept available (SysC reuse) / up to 1 year if concept has to be developed

- Simulation setup: straightforward, just the parameter sweeps and their steps have to be defined

- SysC to HDL conversion: achieved with a one-click approach using Mentor Catapult software

- SysC & HDL cosimulation: made possible by Coseda-Cadence-Bridge (CCB) with one click export

- Synthesis on FPGA possible without any need of modifications, using Xilinx ISE synthesizer

#### Results and Conclusion (2/3)

- How much time was saved by this methodology?

- From virtual to real HW prototype: 3 to 6 man / months faster!

- What is the simulation speed of SysC vs. Matlab vs. SysC/HDL co-sim?

- SystemC: 1ms of simulation → ca. 5 s in the real world

- Matlab: does not affect the simulation speed, only used to handle the regression

- SystemC / HDL co-simulation: around 6 times slower than SystemC due to RTL simulation time (dominant)

#### Results and Conclusion (3/3)

- One-click conversion finally possible

- HDL and SystemC match 1:1 in cosimulation

- Measurements ongoing, correct functionality already observed

- High level synthesis approach

- Saves development resources and time

- Increase reuse and speed

- Rapid prototyping approach

- Increase design confidence

- Allow better customers interaction

#### **Questions & Answers**

Any questions?